Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения высокопроизводительных систем, систем управления, АСУТП и других систем, удовлетворяющих высоким требованиям к безотказной работе.

Известно устройство для перестройки матричной процессорной структуры, содержащее три элемента ИЛИ, два элемента И и один элемент запрета (Сами М., Стефанелли Р. "Перестраиваемые архитектуры матричных процессорных СБИС" // ТИИЭР, - 1986. - №5. - с.107-118).

Недостатком известного устройства является низкое быстродействие и высокая вероятность возникновения ситуация фатального отказа, для которых невозможна перестройка.

Наиболее близкой к предлагаемому устройству по технической сущности является ячейка однородной среды процессорных элементов, содержащая восемь элементов ИЛИ, двенадцать элементов И, четыре элемента запрета, элемент ИЛИ-НЕ, три элемента И-ИЛИ, четыре триггера, одновибратор (патент РФ 2177169, G 05 В 19/18, G 06 F 7/00, опубл. 20.12.2001, Бюл. №35). Недостатком известного устройства является низкое быстродействие однородной среды, обусловленное размещением резервных элементов в одном столбце и соответственно большое число перенастраиваемых связей между элементами.

Технической задачей изобретения является расширение области применения за счет введения технических средств, позволяющих снизить число перенастраиваемых ячеек и соответственно время, требуемое на полную перенастройку системы при рациональном расположении резервных процессорных элементов.

Техническая задача решается тем, что в ячейку однородной процессорной среды, предназначенную для настройки процессорного элемента на один из алгоритмов функционирования в зависимости от комбинации отказов процессорных элементов в однородной среде, дополнительно введены селектор максимальной континуальной величины, селектор минимальной континуальной величины, блок определения изолированного узла, четыре резистора R1, R2, R3, R4, шесть элементов коммутации, четыре блока управления элементом коммутации, причем первый вход ячейки однородной процессорной среды соединен со вторыми входами с первого по четвертый блоков управления элементами коммутации, вторым входом восьмого элемента И и входом седьмого элемента НЕ, выход которого соединен со вторым входом девятого элемента И, второй вход ячейки однородной процессорной среды соединен с третьими входами с первого по четвертый блоков управления элементами коммутации, входом шестого элемента НЕ, первым входом девятого элемента И, выход которого соединен управляющим входом шестого элемента коммутации, третий вход ячейки однородной процессорной среды соединен с четвертыми входами с первого по четвертый блоков управления элементами коммутации, первый выход четвертого блока управления элементом коммутации соединен с шестым выходом ячейки однородной процессорной среды, четвертый вход ячейки однородной процессорной среды соединен с пятыми входами с первого по четвертый блоков управления элементами коммутации, второй выход четвертого блока управления элементом коммутации соединен с десятыми входами с первого по третий блоков управления элементом коммутации, первый выход третьего блока управления элементом коммутации соединен с пятнадцатым входом четвертого блока управления элементом коммутации, третий выход которого соединен с управляющим входом четвертого элемента коммутации, информационный выход четвертого элемента коммутации соединен с четвертым выходом ячейки однородной процессорной среды, пятый вход ячейки однородной процессорной среды соединен с шестым входом блока определения изолированного узла, шестыми входами с первого по четвертый блоков управления элементами коммутации, второй выход третьего блока управления элементом коммутации соединен с одиннадцатым входом первого блока управления элементом коммутации и одиннадцатым входом второго блока управления элементом коммутации, первый выход которого соединен с четырнадцатыми входами третьего и четвертого блоков управления элементом коммутации, шестой вход ячейки однородной процессорной среды соединен с шестнадцатыми входами с первого по четвертый блоков управления элементами коммутации, третий выход третьего блока управления элементом коммутации соединен с управляющим входом третьего элемента коммутации, информационный выход которого соединен с третьим выходом ячейки однородной процессорной среды, седьмой вход ячейки однородной процессорной среды соединен с пятым входом блока определения изолированного узла, восемнадцатыми входами с первого по четвертый блоков управления элементами коммутации и информационным входом шестого элемента коммутации, восьмой вход ячейки однородной процессорной среды соединен с тринадцатым, четырнадцатым, пятнадцатым входами первого блока управления элементом коммутации, десятым, одиннадцатым, двенадцатым входами четвертого блока управления элементом коммутации, одиннадцатым, двенадцатым и пятнадцатым входами третьего блока управления элементом коммутации, информационным входом пятого элемента коммутации и с двенадцатым, четырнадцатым, пятнадцатым входами второго блока управления элементом коммутации, второй выход которого соединен с двенадцатым входом первого блока управления элементом коммутации, первый выход которого соединен с тринадцатыми входами со второго по четвертый блоков управления элементами коммутации, третий выход второго блока управления элементом коммутации соединен с управляющим входом второго элемента коммутации, информационный выход которого соединен со вторым выходом ячейки однородной процессорной среды, девятый вход ячейки однородной процессорной среды соединен с первым входом селектора максимальной континуальной величины, первым входом селектора минимальной континуальной величины, первым входом первого блока управления элементом коммутации и первым входом блока определения изолированного узла, выход которого соединен с девятыми входами с первого по четвертый блоков управления элементами коммутации, второй выход первого блока управления элементом коммутации соединен с пятым выходом ячейки однородной процессорной среды, десятый вход ячейки однородной процессорной среды соединен со вторым входом блока определения изолированного узла, вторым входом селектора минимальной континуальной величины, первым входом второго блока управления элементом коммутации и вторым входом селектора максимальной континуальной величины, выход которого соединен с седьмыми входами с первого по четвертый блоков управления элементами коммутации, третий выход первого блока управления элементом коммутации соединен с управляющим входом первого элемента коммутации, информационный выход которого соединен с первым выходом ячейки однородной процессорной среды, одиннадцатый вход ячейки однородной процессорной среды соединен с третьим входом селектора максимальной континуальной величины, третьим входом блока определения изолированного узла, первым входом третьего блока управления элементом коммутации и третьим входом селектора минимальной континуальной величины, выход которого соединен с восьмыми входами с первого по четвертый блоков управления элементами коммутации, двенадцатый вход ячейки однородной процессорной среды соединен с четвертыми входами селектора максимальной континуальной величины, селектора минимальной континуальной величины, блока определения изолированного узла и первым входом четвертого блока управления элементом коммутации, тринадцатый вход ячейки однородной процессорной среды соединен с семнадцатыми входами с первого по четвертый блоков управления элементами коммутации, выход шестого элемента НЕ соединен с первым входом восьмого элемента И, выход которого соединен с управляющим входом пятого элемента коммутации, информационный выход шестого элемента коммутации соединен с информационным выходом пятого элемента коммутации и через резистор R1 с информационным входом первого элемента коммутации и девятым входом ячейки однородной процессорной среды, через резистор R2 с информационным входом второго элемента коммутации и десятым входом ячейки однородной процессорной среды, через резистор R3 с информационным входом третьего элемента коммутации и одиннадцатым входом ячейки однородной процессорной среды, через резистор R4 с информационным входом четвертого элемента коммутации и двенадцатым входом ячейки однородной процессорной среды, четвертый выход первого блока управления элементом коммутации соединен с седьмым выходом ячейки однородной процессорной среды, пятый выход первого блока управления элементом коммутации соединен с восьмым выходом ячейки однородной процессорной среды, четвертый выход второго блока управления элементом коммутации соединен с девятым выходом ячейки однородной процессорной среды, пятый выход второго блока управления элементом коммутации соединен с десятым выходом ячейки однородной процессорной среды, четвертый выход третьего блока управления элементом коммутации соединен с одиннадцатым выходом ячейки однородной процессорной среды, пятый выход третьего блока управления элементом коммутации соединен с двенадцатым выходом ячейки однородной процессорной среды, четвертый выход четвертого блока управления элементом коммутации соединен с тринадцатым выходом ячейки однородной процессорной среды, пятый выход четвертого блока управления элементом коммутации соединен с четырнадцатым выходом ячейки однородной процессорной среды.

Сущность изобретения заключается в следующем.

Все ячейки однородной процессорной среды являются элементами настройки матрицы из N*M процессорных элементов. Местоположение ПЭ и соответствующей ему ячейки однородной процессорной среды определяется ее физическим адресом (ФА)-(i,j), где  - номер строки,

- номер строки,  - номер столбца матрицы процессорных элементов.

- номер столбца матрицы процессорных элементов.

Каждая ячейка однородной процессорной среды (i,j) настраивает соответствующий процессорный элемент (i,j) на один из алгоритмов функционирования: собственный (i,j)-й, верхний (i-1,j)-й, нижний (i+1,j)-й, правый (i,j+1)-й, левый (i,j-1)-й в зависимости от возникающих комбинаций отказов ПЭ в среде.

Алгоритм функционирования (i,j), на который настроен (i,j)-й ПЭ, называется виртуальным адресом (В A) (i,j)-го ПЭ.

Первоначально (при отсутствии отказов) все ПЭ, за исключением резервных, имеют ВА, равный ФА. Резервные элементы назначаются произвольно и первоначально имеют ВА=(0,0), т.е. не выполняют никакого алгоритма функционирования. При возникновении отказов ПЭ множество взаимодействующих ячеек однородной процессорной среды перенастраивает работоспособные ПЭ (в том числе и резервные) на новые ВА.

При отсутствии отказов однородная процессорная среда находится в состоянии покоя, так как нет источников возбуждения, которыми являются отказавшие ПЭ.

В исходном состоянии все ключи однородной процессорной среды являются замкнутыми. При отказе ПЭ системы он инициирует логический сигнал отказа (Х0=1), который в свою очередь подается в соответствующий узел однородной процессорной среды и устанавливает его потенциал в Е1>0. Так как узлы однородной процессорной среды, соответствующие резервным ПЭ, имеют потенциал Е0=0, то в среде возникает разность потенциалов, которая приводит к тому, что от узлов однородной процессорной среды, соответствующих отказавшим ПЭ (высокий потенциал), к узлам однородной процессорной среды, соответствующим резервным ПЭ (низкий потенциал), через узлы, соответствующие работоспособным ПЭ, начинают протекать токи. Причем, чем ближе резервный элемент находится к источнику возмущения, тем больше величина тока. Ячейка однородной процессорной среды на каждом из четырех направлений имеет резистор и ключ. Падение напряжения на резисторе используется для определения величины тока и выделения его максимальных и минимальных значений, а ключ используется для размыкания направления, в случае его несоответствия кратчайшему пути до резерва. При возникновении равных по модулю максимальных или минимальных значений напряжения на нескольких направлениях выбирается направление, которое имеет высший приоритет в следующей последовательности: вправо, вверх, влево, вниз. Цикл построения маршрута разделен на три такта, следующих один за другим в соответствии с последовательностью синхроимпульсов, изображенных на (фиг.9). На такте τ0 производится поиск максимального вытекающего из узла тока. При этом ключ, соответствующий этому направлению, остается замкнутым и вырабатывается сигнал перенастройки соседнего ПЭ на алгоритм, который выполнялся данной ПЭ, а на всех остальных направлениях, где токи вытекают из узла, ключи размыкаются. Аналогичная операция производится на такте τ1, но с втекающими в узел токами. Если в результате первых двух тактов образуется изолированный узел (сумма всех токов равна нулю), соответствующий работоспособному ПЭ, то на такте τ2 все ключи такой ячейки однородной процессорной среды замыкаются, и она снова участвует в поиске маршрутов.

При поступлении в одну ячейку однородной процессорной среды двух и более сигналов перенастройки (втекающих токов) возникает конфликтная ситуация, так как каждый ПЭ может переключиться на один из алгоритмов соседних ПЭ. Конфликтная ситуация разрешается путем размыкания ключей, соответствующих более длинным маршрутам, так как ток на этих направлениях будет значительно меньше, чем на направлении, соответствующем кратчайшему маршруту. В результате может возникнуть изоляция некоторых источников. В этом случае требуется частичное восстановление соответствующих ключей решетки, заключающееся в замыкании ключей ячеек не включенных в созданные маршруты. Эта операция реализуется на такте τ2.

Фатальный отказ в системе возникает только в том случае, если узлы, соответствующие отказавшему и резервному ПЭ, изолируются друг от друга маршрутами, построенными в более короткий промежуток времени. Если отказавший ПЭ является в то же время и резервным, то такая ситуация фатальным отказом не является.

Введение селектора максимальной континуальной величины позволяет определить максимальное напряжение среди тех направлений, где токи вытекают из узла однородной процессорной среды, т.е. U>0.

Введение селектора минимальной континуальной величины позволяет определить максимальное напряжение среди тех направлений, где токи втекают в узел однородной процессорной среды, т.е. U<0.

Введение блока определения изолированного узла необходимо для выделения узлов однородной процессорной среды, в которых сумма всех токов равна нулю.

Введение блока сравнения с максимальной континуальной величиной позволяет выделить логическую функцию максимума на кратчайшем направлении среди вытекающих токов и установить приоритет этого направления главным.

Введение блока сравнения с минимальной континуальной величиной позволяет выделить логическую функцию минимума на кратчайшем направлении среди втекающих токов и установить приоритет этого направления главным.

Введение блока формирования управляющего сигнала по τ0 позволяет формировать сигналы управления состоянием ключей для всех направлений ячейки, соответствующих вытекающим токам, и сигналы перенастройки ПЭ на этих направлениях.

Введение блока формирования управляющего сигнала по τ1 позволяет формировать сигналы управления состоянием ключей для всех направлений ячейки, соответствующих втекающим токам, и сигналы перенастройки ПЭ на этих направлениях.

Введение блока хранения управляющего сигнала позволяет хранить сигналы управления состоянием ключей и синхронизировать работу всей однородной процессорной среды.

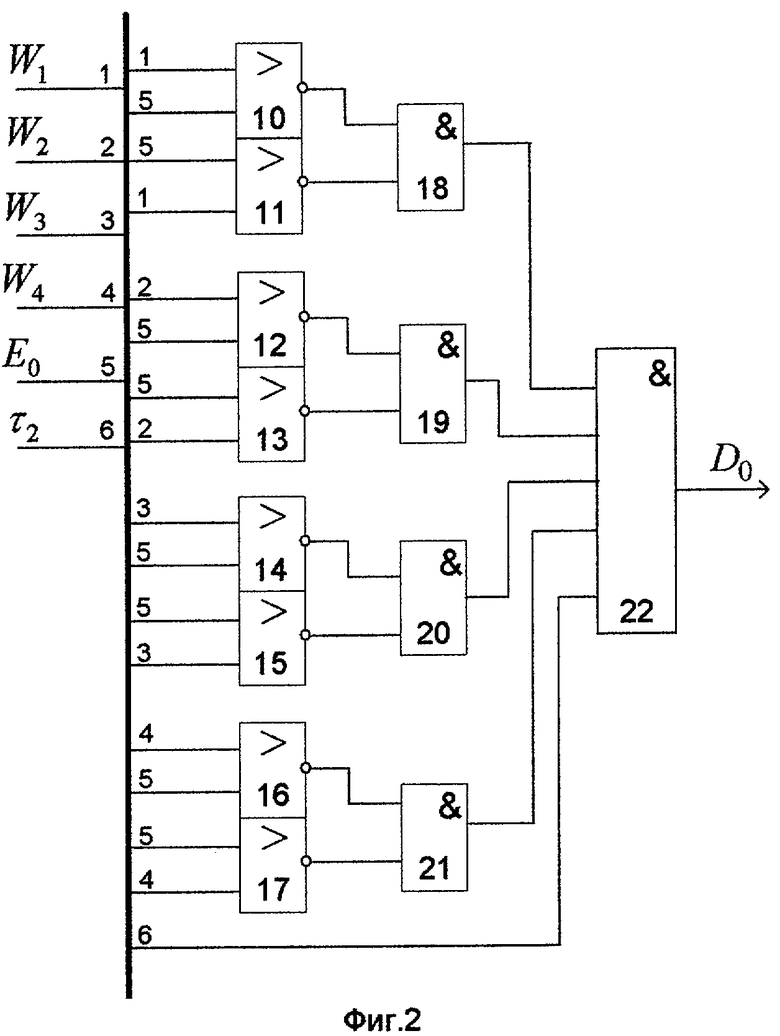

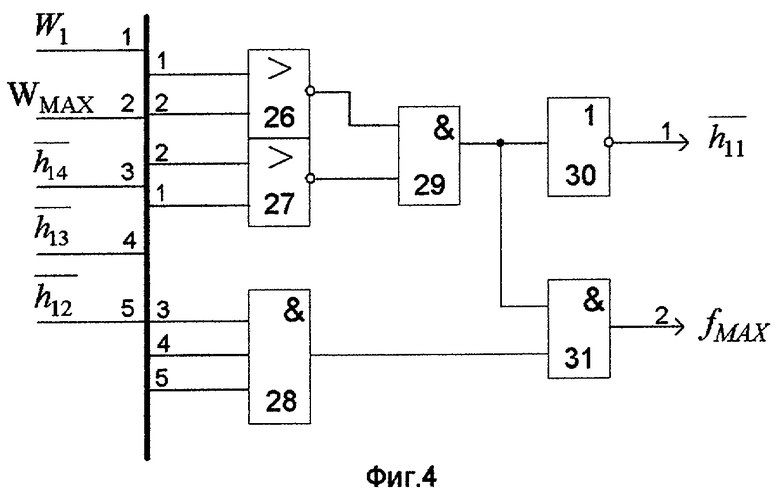

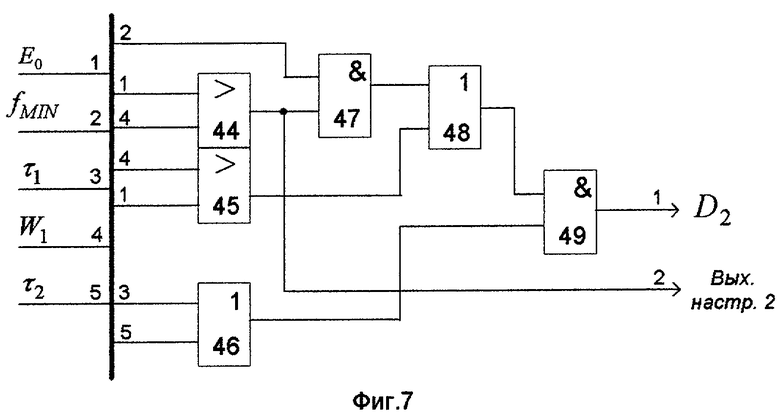

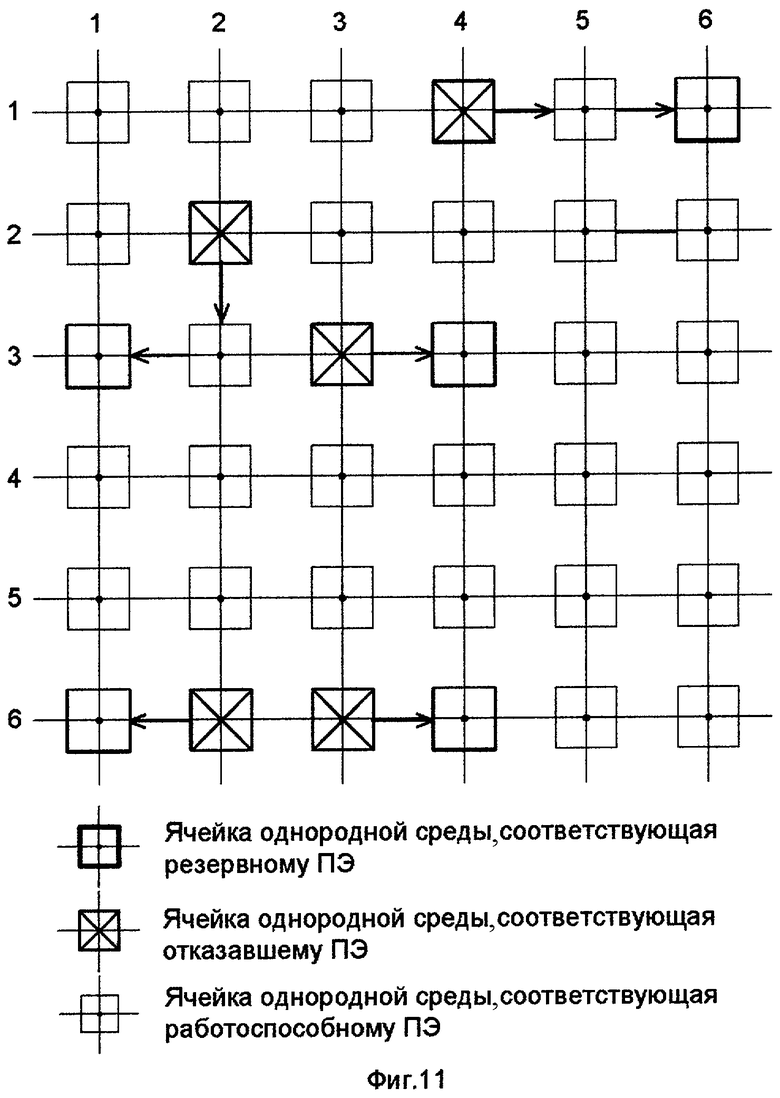

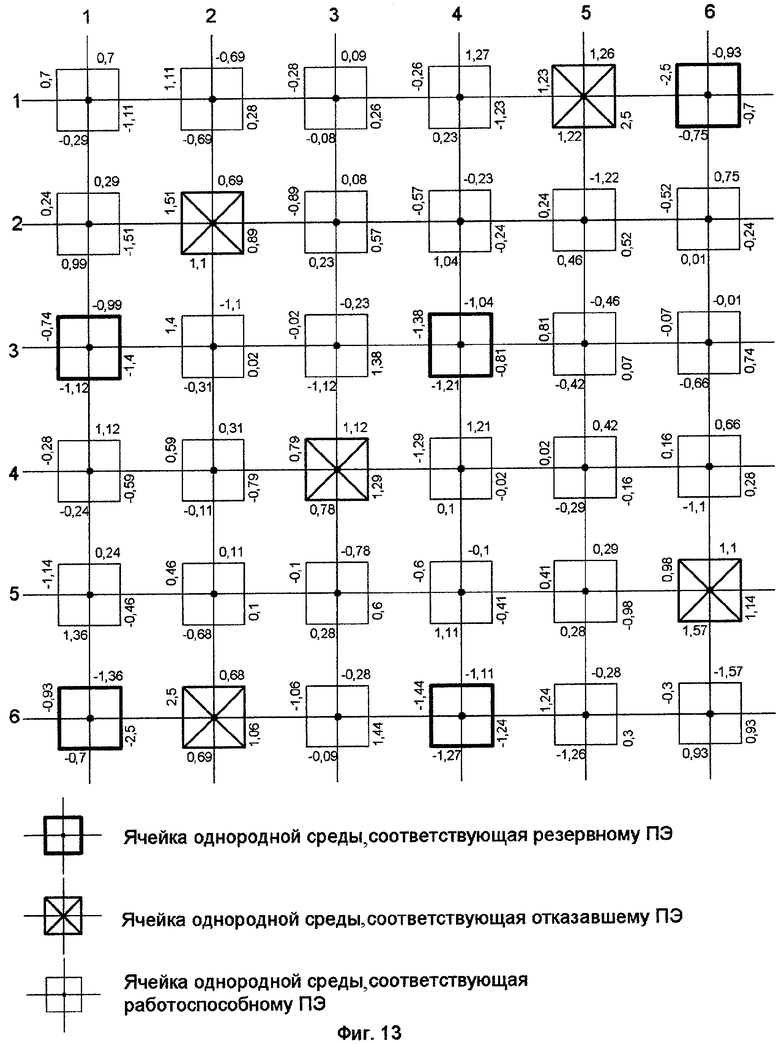

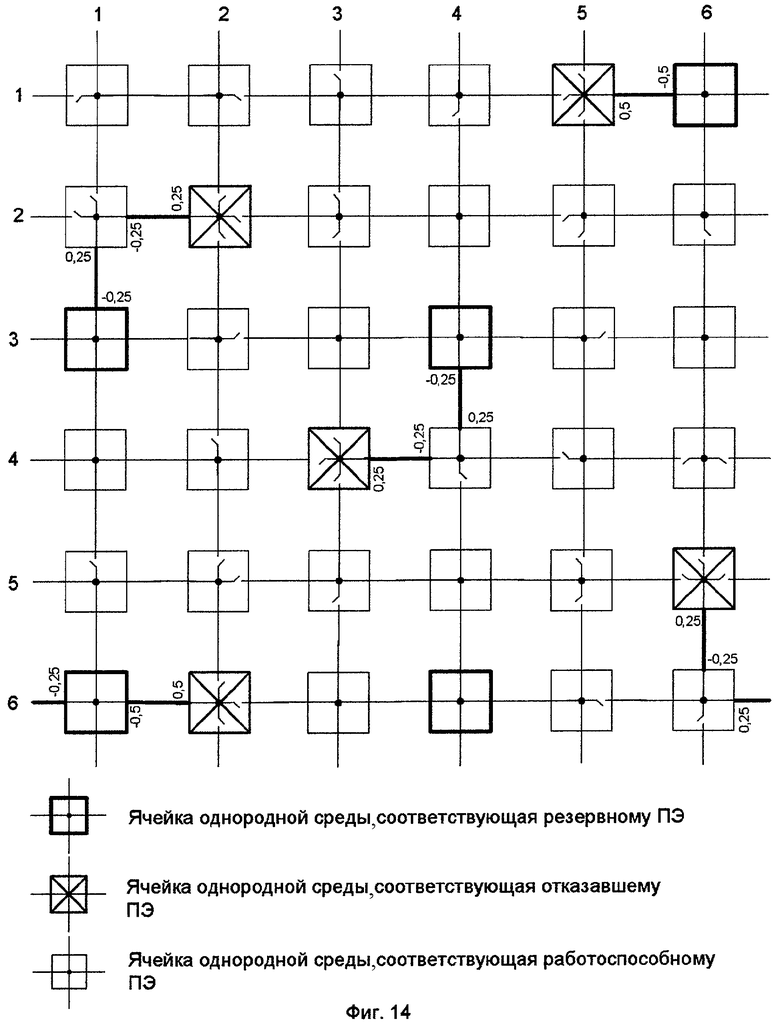

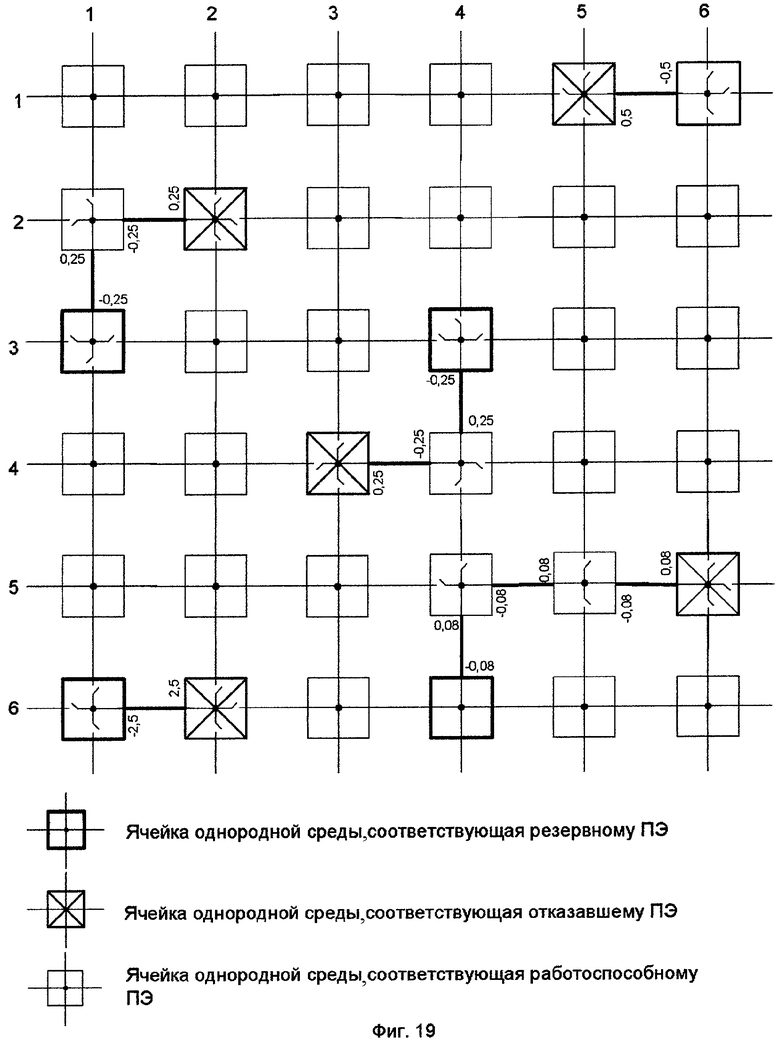

Сущность изобретения поясняется чертежами, где на фиг.1 показана функциональная схема ячейки однородной процессорной среды; на фиг.2 - функциональная схема блока определения изолированного узла; на фиг.3 - функциональная схема блока управления элементом коммутации; на фиг.4 - функциональная схема блока сравнения с максимальной континуальной величиной; на фиг.5 - функциональная схема сравнения с минимальной континуальной величиной; на фиг.6 - функциональная схема блока формирования управляющего сигнала по τ0; на фиг.7 - функциональная схема блока формирования управляющего сигнала по τ1; на фиг.8 - функциональная схема блока хранения управляющего сигнала; на фиг.9 - последовательность синхроимпульсов, необходимых для работы однородной процессорной среды; на фиг.10 - схема реконфигурации однородной процессорной среды для трех отказов; на фиг.11 - схема реконфигурации однородной процессорной среды при оптимальном распределении резервных элементов; на фиг.12 - схема реконфигурации однородной процессорной среды при большом удалении резервного ПЭ от отказавшего ПЭ; на фиг.13 - схема распределения токов перед началом реконфигурации; на фиг.14 - схема распределения токов и состояния ключей на такте τ0 первого цикла; на фиг.15 - схема распределения токов и состояния ключей на такте τ1 первого цикла; на фиг.16 - схема распределения токов и состояния ключей на такте τ2 первого цикла; на фиг.17 - схема распределения токов и состояния ключей на такте τ0 второго цикла; на фиг.18 - схема распределения токов и состояния ключей на такте τ1 второго цикла; на фиг.19 - схема распределения токов и состояния ключей на такте τ2 второго цикла.

Ячейка однородной процессорной среды, предназначенная для настройки процессорного элемента на один из алгоритмов функционирования в зависимости от комбинации отказов процессорных элементов в однородной среде (фиг.1), содержит селектор максимальной континуальной величины 1, селектор минимальной континуальной величины 2, блок определения изолированного узла 3, четыре резистора R1, R2, R3, R4, шесть элементов коммутации 5.1, 5.2, 5.3, 5.4, 5.5, 5.6, первый 4.1, второй 4.2, третий 4.3 и четвертый 4.4 блоки управления элементом коммутации, каждый из которых включает в себя блок сравнения с максимальной континуальной величиной 23.1, блок сравнения с минимальной континуальной величиной 23.2, блок формирования управляющего сигнала по τ0 24.1, блок формирования управляющего сигнала по τ1 24.2 и блок хранения управляющего сигнала 25, причем первый вход ячейки однородной процессорной среды соединен со вторыми входами блоков управления элементами коммутации 4.1, 4.2, 4.3 и 4.4, вторым входом элемента И 8 и входом элемента НЕ 7, выход которого соединен со вторым входом элемента И 9, второй вход ячейки однородной процессорной среды соединен с третьими входами блоков управления элементами коммутации 4.1, 4.2, 4.3 и 4.4, входом элемента НЕ 6, первым входом элемента И 9, выход которого соединен управляющим входом элемента коммутации 5.6, третий вход ячейки однородной процессорной среды соединен с четвертыми входами блоков управления элементами коммутации 4.1, 4.2, 4.3 и 4.4, первый выход четвертого блока управления элементом коммутации 4.4 соединен с шестым выходом ячейки однородной процессорной среды, четвертый вход ячейки однородной процессорной среды соединен с пятыми входами блоков управления элементами коммутации 4.1, 4.2,4.3 и 4.4, второй выход блока управления элементом коммутации 4.4 соединен с десятыми входами блоков управления элементом коммутации 4.1, 4.2 и 4.3, первый выход блока управления элементом коммутации 4.3 соединен с пятнадцатым входом блока управления элементом коммутации 4.4, третий выход которого соединен с управляющим входом элемента коммутации 5.4, информационный выход элемента коммутации 5.4 соединен с четвертым выходом ячейки однородной процессорной среды, пятый вход ячейки однородной процессорной среды соединен с шестым входом блока определения изолированного узла 3, шестыми входами блоков управления элементами коммутации 4.1, 4.2, 4.3 и 4.4, второй выход блока управления элементом коммутации 4.3 соединен с одиннадцатым входом блока управления элементом коммутации 4.1 и одиннадцатым входом блока управления элементом коммутации 4.2, первый выход которого соединен с четырнадцатыми входами блоков управления элементом коммутации 4.3 и 4.4, шестой вход ячейки однородной процессорной среды соединен с шестнадцатыми входами блоков управления элементами коммутации 4.1, 4.2, 4.3 и 4.4, третий выход блока управления элементом коммутации 4.3 соединен с управляющим входом элемента коммутации 5.3, информационный выход которого соединен с третьим выходом ячейки однородной процессорной среды, седьмой вход ячейки однородной процессорной среды соединен с пятым входом блока определения изолированного узла 3, восемнадцатыми входами блоков управления элементами коммутации 4.1, 4.2, 4.3, 4.4 и информационным входом элемента коммутации 5.6, восьмой вход ячейки однородной процессорной среды соединен с тринадцатым, четырнадцатым, пятнадцатым входами блока управления элементом коммутации 4.1, десятым, одиннадцатым, двенадцатым входами блока управления элементом коммутации 4.4, одиннадцатым, двенадцатым и пятнадцатым входами блока управления элементом коммутации 4.3, информационным входом элемента коммутации 5.5 и с двенадцатым, четырнадцатым, пятнадцатым входами блока управления элементом коммутации 4.2, второй выход которого соединен с двенадцатым входом блока управления элементом коммутации 4.1, первый выход которого соединен с тринадцатыми входами блоков управления элементами коммутации 4.2, 4.3 и 4.4, третий выход блока управления элементом коммутации 4.2 соединен с управляющим входом элемента коммутации 5.2, информационный выход которого соединен со вторым выходом ячейки однородной процессорной среды, девятый вход ячейки однородной процессорной среды соединен с первым входом селектора максимальной континуальной величины 1, первым входом селектора минимальной континуальной величины 2, первым входом блока управления элементом коммутации 4.1 и первым входом блока определения изолированного узла 3, выход которого соединен с девятыми входами блоков управления элементами коммутации 4.1, 4.2, 4.3 и 4.4, второй выход блока управления элементом коммутации 4.1 соединен с пятым выходом ячейки однородной процессорной среды, десятый вход ячейки однородной процессорной среды соединен со вторым входом блока определения изолированного узла 3, вторым входом селектора минимальной континуальной величины 2, первым входом блока управления элементом коммутации 4.2 и вторым входом селектора максимальной континуальной величины 1, выход которого соединен с седьмыми входами блоков управления элементами коммутации 4.1, 4.2, 4.3 и 4.4, третий выход блока управления элементом коммутации 4.1 соединен с управляющим входом элемента коммутации 5.1, информационный выход которого соединен с первым выходом ячейки однородной процессорной среды, одиннадцатый вход ячейки однородной процессорной среды соединен с третьим входом селектора максимальной континуальной величины 1, третьим входом блока определения изолированного узла 3, первым входом блока управления элементом коммутации 4.3 и третьим входом селектора минимальной континуальной величины 2, выход которого соединен с восьмыми входами блоков управления элементами коммутации 4.1, 4.2, 4.3 и 4.4, двенадцатый вход ячейки однородной процессорной среды соединен с четвертыми входами селектора максимальной континуальной величины 1, селектора минимальной континуальной величины 2, блока определения изолированного узла 3 и первым входом блока управления элементом коммутации 4.4, тринадцатый вход ячейки однородной процессорной среды соединен с семнадцатыми входами блоков управления элементами коммутации 4.1, 4.2, 4.3 и 4.4, выход элемента НЕ 6 соединен с первым входом элемента И 8, выход которого соединен с управляющим входом элемента коммутации 5.5, информационный выход элемента коммутации 5.6 соединен с информационным выходом элемента коммутации 5.5 и через резистор R1 с информационным входом элемента коммутации 5.1 и девятым входом ячейки однородной процессорной среды, через резистор R2 с информационным входом элемента коммутации 5.2 и десятым входом ячейки однородной процессорной среды, через резистор R3 с информационным входом элемента коммутации 5.3 и одиннадцатым входом ячейки однородной процессорной среды, через резистор R4 с информационным входом элемента коммутации 5.4 и двенадцатым входом ячейки однородной процессорной среды, четвертый выход блока управления элементом коммутации 4.1 соединен с седьмым выходом ячейки однородной процессорной среды, пятый выход блока управления элементом коммутации 4.1 соединен с восьмым выходом ячейки однородной процессорной среды, четвертый выход блока управления элементом коммутации 4.2 соединен с девятым выходом ячейки однородной процессорной среды, пятый выход блока управления элементом коммутации 4.2 соединен с десятым выходом ячейки однородной процессорной среды, четвертый выход блока управления элементом коммутации 4.3 соединен с одиннадцатым выходом ячейки однородной процессорной среды, пятый выход блока управления элементом коммутации 4.3 соединен с двенадцатым выходом ячейки однородной процессорной среды, четвертый выход блока управления элементом коммутации 4.4 соединен с тринадцатым выходом ячейки однородной процессорной среды, пятый выход блока управления элементом коммутации 4.4 соединен с четырнадцатым выходом ячейки однородной процессорной среды.

Блок определения изолированного узла 3 (фиг.2) содержит группу компараторов 10-17 и группу элементов И 18-22, причем первый вход блока соединен с первым входом компаратора 10 и вторым входом компаратора 11, второй вход блока соединен с первым входом компаратора 12 и вторым входом компаратора 13, третий вход блока соединен с первым входом компаратора 14 и вторым входом компаратора 15, четвертый вход блока соединен с первым входом компаратора 16 и вторым входом компаратора 17, пятый вход блока соединен со вторыми входами компараторов 10, 12, 14, 16 и первыми входами компараторов 11, 13, 15, 17, шестой вход блока соединен с пятым входом элемента И 22, инверсный выход компаратора 10 соединен с первым входом элемента И 18, инверсный выход компаратора 11 соединен со вторым входом элемента И 18, выход которого соединен с первым входом элемента И 22, инверсный выход компаратора 12 соединен с первым входом элемента И 19, инверсный выход компаратора 13 соединен со вторым входом элемента И 19, выход которого соединен со вторым входом элемента И 22, инверсный выход компаратора 14 соединен с первым входом элемента И 20, инверсный выход компаратора 15 соединен со вторым входом элемента И 20, выход которого соединен с третьим входом элемента И 22, инверсный выход компаратора 16 соединен с первым входом элемента И 21, инверсный выход компаратора 17 соединен со вторым входом элемента И 21, выход которого соединен с четвертым входом элемента И 22, выход которого является выходом блока.

Первый 4.1, второй 4.2, третий 4.3 и четвертый 4.4 блоки управления элементами коммутации (фиг.3) состоят из блока сравнения с максимальной континуальной величиной 23.1, блока сравнения с минимальной континуальной величиной 23.2, блока формирования управляющего сигнала по τ0 24.1, блока формирования управляющего сигнала по τ1 24.2, блока хранения управляющего сигнала 25, причем первый вход блока соединен с первым входом блока сравнения с максимальной континуальной величиной 23.1, вторым входом блока сравнения с минимальной континуальной величиной 23.2, первым входом блока формирования управляющего сигнала по τ0 24.1, четвертым входом блока формирования управляющего сигнала по τ1 24.2, второй вход блока соединен с девятым входом блока хранения управляющего сигнала 25, третий вход блока соединен с десятым входом блока хранения управляющего сигнала 25, четвертый вход блока соединен с третьим входом блока формирования управляющего сигнала по τ0 24.1 и вторым входом блока хранения управляющего сигнала 25, пятый вход блока соединен с третьими входами блоков формирования управляющего сигнала по τ1 24.2 и хранения управляющего сигнала 25, шестой вход блока соединен с пятыми входами блоков формирования управляющего сигнала по τ0 24.1 и формирования управляющего сигнала по τ1 24.2 и четвертым входом блока хранения управляющего сигнала 25, седьмой вход блока соединен со вторым входом блока сравнения с максимальной континуальной величиной 23.1, восьмой вход блока соединен с первым входом блока сравнения с минимальной континуальной величиной 23.2, девятый вход блока соединен с пятым входом блока хранения управляющего сигнала 25, десятый вход блока соединен с третьим входом блока сравнения с максимальной континуальной величиной 23.1, одиннадцатый вход блока соединен с четвертым входом блока сравнения с максимальной континуальной величиной 23.1, двенадцатый вход блока соединен с пятым входом блока сравнения с максимальной континуальной величиной 23.1, тринадцатый вход блока соединен с третьим входом блока сравнения с минимальной континуальной величиной 23.2, четырнадцатый вход блока соединен с четвертым входом блока сравнения с минимальной континуальной величиной 23.2, пятнадцатый вход блока соединен с пятым входом блока сравнения с минимальной континуальной величиной 23.2, шестнадцатый вход блока соединен с седьмым входом блока хранения управляющего сигнала 25, семнадцатый вход блока соединен с восьмым входом блока хранения управляющего сигнала 25, восемнадцатый вход блока соединен с четвертым входом блока формирования управляющего сигнала по τ0 24.1 и первым входом блока формирования управляющего сигнала по τ1 24.2, второй выход блока сравнения с максимальной континуальной величиной 23.1 соединен со вторым входом блока формирования управляющего сигнала по τ0 24.1, второй выход блока сравнения с минимальной континуальной величиной 23.2 соединен со вторым входом блока формирования управляющего сигнала по τ1 24.2, первый выход блока формирования управляющего сигнала по τ0 24.1 соединен с первым входом блока хранения управляющего сигнала 25, первый выход блока формирования управляющего сигнала по τ1 24.2 соединен с шестым входом блока хранения управляющего сигнала 25, первый выход блока сравнения с максимальной континуальной величиной 23.1 соединен с первым выходом блока, первый выход блока сравнения с минимальной континуальной величиной 23.2 соединен со вторым выходом блока, второй выход блока формирования управляющего сигнала по τ0 24.1 соединен с четвертым выходом блока, второй выход блока формирования управляющего сигнала по τ1 24.2 соединен с пятым выходом блока, выход блока хранения управляющего сигнала 25 соединен с третьим выходом блока.

Блок сравнения с максимальной континуальной величиной 23.1 (фиг.4) содержит два компаратора 26 и 27, группу элементов И 28, 29 и 31, элемент НЕ 30, причем первый вход блока соединен с первым входом компаратора 26 и вторым входом компаратора 27, второй вход блока соединен со вторым входом компаратора 26 и первым входом компаратора 27, третий вход блока соединен с первым входом элемента И 28, четвертый вход блока соединен со вторым входом элемента И 28, пятый вход блока соединен с третьим входом элемента И 28, инверсный выход компаратора 26 соединен с первым входом элемента И 29, выход которого соединен с входом элемента НЕ 30 и первым входом элемента И 31, инверсный выход компаратора 27 соединен со вторым входом элемента И 29, выход элемента И 28 соединен со вторым входом элемента И 31, выход элемента НЕ 30 соединен с первым выходом блока, выход элемента И 31 соединен со вторым выходом блока.

Блок сравнения с минимальной континуальной величиной 23.2 (фиг.5) содержит два компаратора 32 и 33, группу элементов И 34, 35, 37 и элемент НЕ 36, причем первый вход блока соединен с первым входом компаратора 32 и вторым входом компаратора 33, второй вход блока соединен со вторым входом компаратора 32 и первым входом компаратора 33, третий вход блока соединен с первым входом элемента И 34, четвертый вход блока соединен со вторым входом элемента И 34, пятый вход блока соединен с третьим входом элемента И 34, инверсный выход компаратора 32 соединен с первым входом элемента И 35, выход которого соединен с входом элемента НЕ 36 и первым входом элемента И 37, инверсный выход компаратора 33 соединен со вторым входом элемента И 35, выход элемента И 34 соединен со вторым входом элемента И 37, выход элемента НЕ 36 соединен с первым выходом блока, выход элемента И 37 соединен со вторым выходом блока.

Блок формирования управляющего сигнала по τ0 24.1 (фиг.6) содержит два компаратора 38 и 39, два элемента ИЛИ 40 и 42, два элемента И 41 и 43, причем первый вход блока соединен с первым входом компаратора 38 и вторым входом компаратора 39, второй вход блока соединен с первым входом элемента И 41, третий вход блока соединен с первым входом элемента ИЛИ 40, четвертый вход блока соединен со вторым входом компаратора 38 и первым входом компаратора 39, пятый вход блока соединен со вторым входом элемента ИЛИ 40, выход компаратора 38 соединен со вторым входом элемента И 41 и вторым выходом блока, выход элемента И 41 соединен с первым входом элемента ИЛИ 42, выход которого соединен с первым входом элемента И 43, выход которого соединен с первым выходом блока, выход компаратора 39 соединен со вторым входом элемента ИЛИ 42, выход элемента ИЛИ 40 соединен со вторым входом элемента И 43.

Блок формирования управляющего сигнала по τ1 24.2 (фиг.7) содержит два компаратора 44 и 45, два элемента ИЛИ 46 и 48, два элемента И 47 и 49, причем первый вход блока соединен с первым входом компаратора 44 и вторым входом компаратора 45, второй вход блока соединен с первым входом элемента И 47, третий вход блока соединен с первым входом элемента ИЛИ 46, четвертый вход блока соединен со вторым входом компаратора 44 и первым входом компаратора 45, пятый вход блока соединен со вторым входом элемента ИЛИ 46, выход компаратора 44 соединен со вторым входом элемента И 47 и вторым выходом блока, выход элемента И 47 соединен с первым входом элемента ИЛИ 48, выход которого соединен с первым входом элемента И 49, выход которого соединен с первым выходом блока, выход компаратора 45 соединен со вторым входом элемента ИЛИ 48, выход элемента ИЛИ 46 соединен со вторым входом элемента И 49.

Блок хранения управляющего сигнала 25 (фиг.8) содержит два элемента ИЛИ 50 и 52, элемент И-НЕ 51, элемент И 53 и D-триггер 54, причем первый вход блока соединен с первым входом элемента ИЛИ 50, второй вход блока соединен с первым входом элемента ИЛИ 52, третий вход блока соединен со вторым входом элемента ИЛИ 52, четвертый вход блока соединен с третьим входом элемента ИЛИ 52, пятый вход блока соединен со вторым входом элемента ИЛИ 50, шестой вход блока соединен с третьим входом элемента ИЛИ 50, седьмой вход блока соединен с S-входом триггера 54, восьмой вход блока соединен с инверсным R-входом триггера 54, девятый вход блока соединен с первым входом элемента И-НЕ 51, десятый вход блока соединен со вторым входом элемента И-НЕ 51, выход элемента ИЛИ 50 соединен с первым входом элемента И 53, выход которого соединен с D-входом триггера 54, выход элемента И-НЕ 51 соединен со вторым входом элемента И 53, выход элемента ИЛИ 52 соединен с С-входом триггера 54, выход триггера 54 соединен с выходом блока.

Селекторы максимальной и минимальной континуальной величины 1 и 2 (Волгин Л.И. "Реляторные нейропроцессоры и коммуникационно-логические преобразователи аналоговых сигналов с кодированием номера канала", Ульяновск: УлГТУ, 1996, с.12) функционируют следующим образом. На входы 1, 2, 3 и 4 подаются напряжения с резисторов соответствующих направлений. Селектор максимальной континуальной величины из всех U>0 выбирает максимальное значение, которое подается на его выход, а селектор минимальной континуальной величины из всех U<0 выбирает минимальное значение (т.е. значение, большее по модулю среди втекающих токов) и подает его на выход.

Элементы коммутации 5.1, 5.2, 5.3, 5.4, 5.5 и 5.6 могут быть реализованы в виде реляторного элемента (Волгин Л.И. "Релятор и реляторная схемотехника: логико-алгебраические основы и применения", Тольятти, 2003, с.74-87). Каждый элемент коммутации имеет управляющий вход, информационный вход и информационный выход. В том случае, если на управляющем входе присутствует сигнал логической единицы, то информационный вход и информационный выход элемента коммутации замыкаются между собой (ЭК в замкнутом состоянии). Если же на управляющем входе присутствует сигнал логического нуля, то информационный вход и выход разомкнуты (ЭК в разомкнутом состоянии).

Для организации однородной процессорной среды ячейки соединены следующим образом: выход 1 j-й ячейки i-й строки соединен с выходом 4 (j+1)-й ячейки i-й строки, выход 2 j-й ячейки i-й строки соединен с выходом 3 j-й ячейки (i-1)-й строки, выход 3 j-й ячейки i-й строки соединен с выходом 2 j-й ячейки (i+1)-й строки, выход 4 j-й ячейки i-й строки соединен с выходом 1 (j-1)-й ячейки i-й строки. Выходы 5 и 6 ячеек однородной процессорной среды использованы как информационные логические выходы системы приоритетов, а выходы 7, 9, 11 и 13 использованы для проверки правильности перенастройки ПЭ. Вход 1 всех ячеек соединен с матрицей процессорных элементов, информирующей о возникновении отказа в (i,j) ПЭ. Вход 2 всех ячеек используется для программирования резервных элементов однородной процессорной среды. Входы 3, 4, 5, 6 и 13 всех ячеек соединены с внешним генератором, формирующим последовательность синхроимпульсов, представленную на (фиг.9). Вход 7 всех ячеек заземлен, а вход 8 используется для подачи напряжения U.

Рассмотрим работу (i,j)-й ячейки однородной процессорной среды.

Когда все процессорные элементы матрицы находятся в работоспособном состоянии, на входах 1, 3, 4, 5, 6 и 13 соответствующих им ячеек однородной среды присутствуют нулевые сигналы, которые свидетельствуют об отсутствии необходимости в перенастройке матрицы. При возникновении отказа матрица ПЭ формирует логический сигнал на входе 1 соответствующей ячейки однородной процессорной среды. В результате элемент коммутации 5.5 замыкается и соответствующий узел однородной процессорной среды приобретает высокий потенциал E1>0. Одновременно с этим матрица ПЭ формирует сигнал запуска генератора синхроимпульсов. Первый синхроимпульс подается на вход 6 всех ячеек и поступает на S-вход триггера блока хранения управляющего сигнала 25. В результате все триггеры принудительно переходят в состояние логической единицы и переключают элементы коммутации 5.1, 5.2, 5.3 и 5.4 в замкнутое состояние, формируя тем самым связи между ячейками однородной процессорной среды во всех направлениях. Так как резервные ячейки имеют нулевой потенциал Е0=0 (заземлены через элемент коммутации 5.6 на этапе программирования резерва), то от ячеек, соответствующих отказавшим ПЭ, к ячейкам, соответствующим резервным ПЭ, начинают протекать токи. Напряжение с резисторов R1, R2, R3 и R4 каждой ячейки однородной процессорной среды подается на входы селектора максимальной континуальной величины 1, селектора минимальной континуальной величины 2, блока определения изолированного узла 3 и на первые входы соответствующих блоков управления элементами коммутации.

Блок определения изолированного узла функционирует следующим образом.

На входы 1, 2, 3 и 4 подаются напряжения с резисторов R1, R2, R3 и R4 соответствующих направлений. На вход 5 подается нулевой потенциал. Компараторы 10-17 сравнивают текущее значение напряжения на резисторах R1, R2, R3 и R4 с нулевым потенциалом. В том случае, если на всех направлениях напряжение равно нулю и на входе 6 блока присутствует синхроимпульс τ2, то на выходе блока будет логическая единица, свидетельствующая о том, что элементы коммутации на всех направлениях такой ячейки необходимо замкнуть, т.е. установить в исходное состояние. На всех остальных тактах работы ячейки однородной процессорной среды на выходе блока будет сигнал логического нуля.

Для перехода от непрерывных физических величин к логическим величинам служит блок сравнения с максимальной континуальной величиной 23.1 и блок сравнения с минимальной континуальной величиной 23.2.

Блок сравнения с максимальной континуальной величиной 23.1 (фиг.4) функционирует следующим образом.

На вход 1 блока подается напряжение с резистора соответствующего направления. На вход 2 блока подается максимальное напряжение, выбранное среди направлений, по которым токи вытекают из данной ячейки. Этот максимум формирует селектор максимальной континуальной величины 1. Компараторы 26 и 27 сравнивают эти значения напряжений и в том случае, если они равны, на выходе 1 блока устанавливается значение логического нуля, что соответствует приоритету направления, на котором имеется максимум. В том случае, если на других направлениях вытекающие токи меньше, то их приоритеты будут находится в состоянии логической единицы, что соответствует отсутствию максимума на них. В результате на входах 3, 4 и 5 будет логическая единица, а на выходе 2 блока формируется логическая функция максимума. Если максимальные значения напряжений существуют на нескольких направлениях, то в силу вступает система приоритетов. Для вытекающих токов приоритеты направлений назначаются в порядке, обратном нумерации, при этом четвертое направление имеет наивысший приоритет.

Блок сравнения с минимальной континуальной величиной 23.2 (фиг.5) функционирует аналогичным образом.

На вход 1 блока подается напряжение с резистора соответствующего направления. На вход 2 блока подается минимальное напряжение, выбранное среди направлений, по которым токи втекают в данную ячейку. Этот минимум формирует селектор минимальной континуальной величины 2. Компараторы 32 и 33 сравнивают эти значения напряжений и в том случае, если они равны, на выходе 1 блока устанавливается значение логического нуля, что соответствует приоритету направления, на котором имеется минимум. В том случае, если на других направлениях втекающие токи имеют более близкое значение к нулю, то их приоритеты будут находится в состоянии логической единицы, что соответствует отсутствию минимума на них. В результате на входах 3, 4 и 5 будет логическая единица, а на выходе 2 блока формируется логическая функция минимума. Если минимальные значения напряжений существуют на нескольких направлениях, то в силу вступает система приоритетов. Для втекающих токов приоритеты назначаются в порядке нумерации направлений, при этом первое направление имеет наивысший приоритет.

Блок формирования управляющего сигнала по τ0 24.1 (фиг.6) функционирует следующим образом.

Компаратор 38 сравнивает значение напряжения с резистора соответствующего направления с нулевым потенциалом. Если он больше нуля и является максимумом, то на выходе 1 блока формируется значение логической единицы, т.е. элемент коммутации на данном направлении должен оставаться замкнутым. Одновременно формируется и логическая единица на выходе 2, которая позволяет определить на какой алгоритм функционирования необходимо настроить соседний ПЭ в данном направлении после построения кратчайших маршрутов. Данный блок формирует значение управляющего сигнала только для тех направлений, по которым токи вытекают из ячейки. Значения управляющих сигналов, формирующих замыкание элементов коммутации на других тактах работы однородной процессорной среды, должны оставаться неизменными. Поэтому, если напряжение на текущем направлении ниже нуля, срабатывает компаратор 39, который через элементы ИЛИ 42, 40 и элемент И 43 поддерживает текущее состояние управляющего сигнала для триггера на тактах τ0 и τ2.

Блок формирования управляющего сигнала по τ1 24.2 (фиг.7) функционирует следующим образом.

Компаратор 44 сравнивает значение нулевого потенциала с напряжением на резисторе соответствующего направления. Если это напряжение меньше нуля (ток втекает в ячейку) и является минимумом, то на выходе 1 блока формируется значение логической единицы, т.е. элемент коммутации на данном направлении должен оставаться замкнутым. Одновременно формируется и логическая единица на выходе 2, которая позволяет определить на какой алгоритм функционирования необходимо настроить соответствующий ПЭ после построения кратчайших маршрутов. Данный блок формирует значение управляющего сигнала только для тех направлений, по которым токи втекают в ячейки. Значения управляющих сигналов, формирующих замыкание элементов коммутации на других тактах работы однородной процессорной среды, должны оставаться неизменными. Поэтому, если напряжение на текущем направлении выше нуля, срабатывает компаратор 45, который через элементы ИЛИ 48, 46 и элемент И 49 поддерживает текущее состояние управляющего сигнала для триггера на тактах τ1 и τ2.

Блок хранения управляющего сигнала 25 функционирует следующим образом.

При возникновении отказавших ПЭ на вход 7 блока подается единичный сигнал "Начальная установка", который устанавливает триггер в "1", что соответствует началу реконфигурации. Так как выход триггера управляет состоянием соответствующего элемента коммутации, то данный элемент коммутации будет находиться в замкнутом (начальном) состоянии. Процесс реконфигурации разделен на три такта, следующих один за другим в соответствии с последовательностью синхроимпульсов, изображенных на (фиг.9). Синхроимпульсы τ0, τ1 и τ2 подаются соответственно на второй, третий и четвертый входы блока, объединенные элементом ИЛИ 52, выход которого и управляет переключением триггера. Значения состояния триггера, в которое он будет переключаться, формируются блоком формирования управляющего сигнала по τ0, блоком определения изолированного узла и блоком формирования управляющего сигнала по τ1, которые подаются соответственно на первый, пятый и шестой входы блока, объединенные элементом ИЛИ 50. В том случае, если в матрице ПЭ возникает отказавший резервный ПЭ, то элемент И-НЕ 51 и элемент И 53 обеспечивают установку триггера в нуль на всех тактах работы однородной процессорной среды. Таким образом такая ячейка изолируется по всем направлениям. В остальных случаях сигнал с выхода элемента ИЛИ 50 через элемент И 53 поступает на вход D-вход триггера без изменений, обеспечивая установку триггера в заданное значение. По окончании реконфигурации на вход 8 блока поступает единичный сигнал "Сброс среды", поступающий на инверсный R-вход триггера и принудительно сбрасывающий его в нуль.

Таким образом, если в матрице процессорных элементов отказывает хотя бы один ПЭ, то в однородной процессорной среде начинается процесс реконфигурации, состоящий из трех тактов: τ0, τ1 и τ2, следующих один за другим в соответствии с последовательностью синхроимпульсов (фиг.9).

Рассмотрим процесс реконфигурации.

На вход 1 ячейки однородной процессорной среды, соответствующей отказавшему ПЭ, поступает единичный сигнал. В результате элемент коммутации 5.5 переключается в замкнутое состояние. Одновременно на вход 6 с генератора поступает синхроимпульс "Н.уст". В результате все триггеры принудительно переходят в состояние логической единицы и переключают элементы коммутации 5.1, 5.2, 5.3 и 5.4 в замкнутое состояние, формируя тем самым связи между ячейками однородной процессорной среды во всех направлениях. Напряжения с резисторов R1, R2, R3 и R4 поступают на входы 9, 10, 11 и 12 каждой ячейки однородной процессорной среды соответственно. Через промежуток времени, достаточный для того, чтобы все связи между ячейками были сформированы, генератор вырабатывает синхроимпульс τ0, соответствующий первому такту работы однородной процессорной среды. Напряжения со входов каждой ячейки подается на входы селекторов максимальной и минимальной континуальных величин, блока определения изолированного узла и на первые входы соответствующих блоков управления элементами коммутации. Селектор максимальной континуальной величины формирует на выходе максимальное значение напряжения для всех U>0. Селектор минимальной континуальной величины формирует на выходе минимальное значение для всех U<0. Полученные сигналы с селекторов поступают на входы всех блоков управления элементами коммутации. На такте τ0 производится анализ вытекающих из ячейки токов с помощью блоков 23.1, 24.1 и 25, поэтому рассмотрим их работу. Блоки 23.1 сравнивают значения напряжений на каждом направлении с напряжением с селектора максимальной континуальной величины. В результате на одном из направлений, где токи вытекают из ячейки и являются максимальными, на выходе 1 блока будет нулевой сигнал, соответствующий приоритету максимума, на выходе 2 блока будет единичный сигнал, соответствующий логической функции максимума. Для остальных направлений, где токи вытекают из ячейки, на выходе 1 будет единица, на выходе 2 - нуль. Сигналы с выходов 2 блоков 23.1 поступают на входы соответствующих блоков 24.1 на всех направлениях. В результате на выходах блоков 24.1 формируются единичные сигналы на том направлении, где есть максимум, и нулевые сигналы, где максимум отсутствует. Сигналы с выхода 1 блоков 24.1 поступают на вход блоков 25 по соответствующим направлениям. Полученные сигналы поддерживают триггер в единичном состоянии на том направлении, где напряжение максимально, и переключают триггеры в нуль на всех остальных направлениях, где токи вытекают из ячейки. Таким образом, элементы коммутации на неоптимальных направлениях с вытекающими токами размыкаются. Через промежуток времени, достаточный для переключения элементов коммутации, генератор формирует синхроимпульс τ1. На этом такте работы однородной процессорной среды производится анализ втекающих в ячейку токов с помощью блоков 23.2, 24.2 и 25.

Рассмотрим их работу.

Блоки 23.2 сравнивают значения напряжений на каждом направлении с напряжением с селектора минимальной континуальной величины. В результате на одном из направлений, где токи втекают в ячейку и являются минимальными (т.е. максимальными по модулю среди втекающих токов), на выходе 1 блока будет нулевой сигнал, соответствующий приоритету минимума, на выходе 2 блока будет единичный сигнал, соответствующий логической функции минимума. Для остальных направлений, где токи втекают в ячейку, на выходе 1 будет единица, на выходе 2 - нуль. Сигналы с выходов 2 блоков 23.2 поступают на входы соответствующих блоков 24.2, которые формируют на своих выходах единичные сигналы на направлении, где есть минимум, и нулевые сигналы, где минимум отсутствует. Сигнал с выхода 1 блоков 24.2 поступает на вход блоков 25 на соответствующих направлениях. Полученные сигналы поддерживают триггер в единичном состоянии на том направлении, где напряжение минимально, и переключают триггеры в нуль на всех остальных направлениях, где токи втекают в ячейку. Таким образом, элементы коммутации на неоптимальных направлениях с втекающими токами размыкаются. Через промежуток времени, достаточный для переключения элементов коммутации, генератор формирует синхроимпульс τ2. На этом такте функционируют блоки 3 и 25. Если сумма токов по всем направлениям ячейки равна нулю, то на выходе блока 3 присутствует единичный сигнал, который поступает на вход блоков 25 всех направлений такой ячейки и переключает принудительно все триггеры в единицу, тем самым замыкая элементы коммутации во всех направлениях. В том случае, если сумма токов не равна нулю, то на выходе данного блока будет нулевой сигнал, а триггеры на всех направлениях останутся в прежнем состоянии.

Непересекающиеся маршруты однородная процессорная среда, организованная таким образом, построит всего за один цикл работы, т.е. за одну тройку синхроимпульсов: τ0, τ1 и τ2. Если же возникнет конфликтная ситуация, то потребуется несколько циклов работы. После того, как непересекающиеся маршруты построены, на выходах 8, 10, 12 и 14 ячеек, принадлежащих маршрутам перестройки, будут присутствовать единичные сигналы, показывающие на какой алгоритм функционирования необходимо настроить соответствующий ПЭ (Таблица 1). Через промежуток времени, достаточный для перенастройки ПЭ, генератор синхроимпульсов вырабатывает сигнал "Сброс среды", и все триггеры принудительно переходят нуль, тем самым размыкая связи между ячейками однородной процессорной среды по всем направлениям. После этого генератор синхроимпульсов отключается матрицей ПЭ.

Рассмотрим процесс реконфигурации однородной процессорной среды для примера на фиг.10. ПЭ с физическими адресами (1,2), (2,3) и (4,3) являются отказавшими. В результате на входах 1 соответствующих им ячеек однородной процессорной среды присутствуют единичные сигналы. ПЭ с физическими адресами (2,1), (2,4) и (5,4) являются резервными, на входах 2 соответствующих им ячеек однородной процессорной среды присутствуют единичные сигналы. После того, как маршруты построены, на выходе 10 ячейки с ФА (2,2) присутствует единичный сигнал, поступающий в матрицу процессорных элементов, которая изменяет виртуальный адрес ячейки с ФА (2,2) на (1,2). На выходе 14 ячейки с ФА (2,4) присутствует единичный сигнал, поступающий в матрицу процессорных элементов, которая изменяет виртуальный адрес ячейки с ФА (2,4) на (2,3). На входе 14 ячейки с ФА (4,4) также присутствует единичный сигнал, поступающий в матрицу процессорных элементов, которая изменяет виртуальный адрес ячейки с ФА (4,4) на (4,3). На выходе 8 ячейки с ФА (2,1) присутствует единичный сигнал, поступающий в матрицу процессорных элементов, которая изменяет виртуальный адрес ячейки с ФА (2,1) на (2,2). На выходе 10 ячейки с ФА (5,4) присутствует единичный сигнал, поступающий в матрицу процессорных элементов, которая изменяет виртуальный адрес ячейки с ФА (5,4) на (4,4). Реконфигурация однородной процессорной среды завершена.

Для сравнения предложенного устройства с аналогом рассмотрим расположение отказавших ПЭ и соответствующих им ячеек однородной процессорной среды, представленное на фиг.11. Для метода реконфигурации с резервным столбцом, используемого в аналоге, число перенастраиваемых ПЭ равно 12. Благодаря возможности произвольно назначать резервные ПЭ, число перенастраиваемых ПЭ для предложенного устройства уменьшилось до 7. Таким образом, введение дополнительных технических средств позволяет обеспечить реконфигурацию однородной процессорной среды при существенном уменьшении числа перенастраиваемых ПЭ и соответственно времени реконфигурации.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЯЧЕЙКА МАРШРУТИЗАЦИИ ОДНОРОДНОЙ СРЕДЫ ПРОЦЕССОРНЫХ ЭЛЕМЕНТОВ | 2004 |

|

RU2273876C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ОТКАЗОУСТОЙЧИВОЙ СРЕДЫ ПРОЦЕССОРНЫХ ЭЛЕМЕНТОВ | 2003 |

|

RU2256212C2 |

| ЯЧЕЙКА ОДНОРОДНОЙ СРЕДЫ | 2001 |

|

RU2197745C2 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА НА БАЗЕ МАТРИЦЫ ПРОЦЕССОРНЫХ ЭЛЕМЕНТОВ | 1998 |

|

RU2117326C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ СРЕДЫ ПРОЦЕССОРНЫХ ЭЛЕМЕНТОВ | 2000 |

|

RU2177169C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 2004 |

|

RU2280278C1 |

| СПОСОБ СЛЕЖЕНИЯ ЗА ВРЕМЕННОЙ ЗАДЕРЖКОЙ СИГНАЛА И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 1999 |

|

RU2157593C1 |

| Спиральная однородная вычислительная структура | 1990 |

|

SU1741165A2 |

| ЯЧЕЙКА ОДНОРОДНОЙ СРЕДЫ | 2003 |

|

RU2251141C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения высокопроизводительных систем, систем управления, АСУТП и других систем, удовлетворяющих высоким требованиям к безотказной работе. Техническим результатом является расширение области применения за счет снижения перенастраиваемых ячеек и соответственно времени, требуемого на полную перенастройку системы при рациональном расположении резервных процессорных элементов. Устройство содержит селектор максимальной континуальной величины, селектор минимальной континуальной величины, блок определения изолированного узла, резисторы, элементы коммутации, блоки управления элементом коммутации. 7 з.п. ф-лы, 19 ил. 1 табл.

| ГИРОСКОП | 2001 |

|

RU2197715C1 |

Авторы

Даты

2005-12-27—Публикация

2004-02-16—Подача