О5 Ю

СО GD СО

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство | 1978 |

|

SU720539A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1133623A2 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ РЕЗЕРВИРОВАНИЯ РАДИОСТАНЦИЙ | 1990 |

|

RU2018939C1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU911627A2 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU1010659A2 |

| УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2001 |

|

RU2207616C2 |

| Микропрограммное устройство управления | 1982 |

|

SU1065855A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU1018152A1 |

| Резервированное многоканальное запоминающее устройство | 1980 |

|

SU942142A1 |

Изобретение отиосигся к гычисли- тельиой технике, в частиости к полупроводниковым лапоми)1а1о:гим yc i juM iCT- вам. Цель изобретелгия - полмпк Л ис; надежности запомзгиаюидего ycTpoiicTita. Иостаппслиля даль достиглетг.л тем, что устп1,1;гс гио содержит ро истр кои- трс лыгпгс) a.ijieca 24, упрапления резерпированийм 2 i, Олок пам.яти кон- тро. гя 25, бло ппчяти aripera 3ahtcine- ипя 26, caneivTop, даиш.к 14,15, схему сравиеиия 1 ). коитролыплЧ ре; истр даншлх 17, фортптт опатоль Т ремениого интернала 19, Tpitrrep контроля 20, ;v c;Meirr il . j ipcTnii O.ioic сум1-(аторов no моду.тпо juia 1 1 с соотпстстлующнми связями. Перечисленная сорокупност ь чрнзнакои позгюляст повысить вероятность oeirapVA QinD кода отказавшей ЯЧ.СЙКИ памяти накопителей 1, 2. Отказавшаяся ячейка заменяется на ячейку из резервного накопителя 3. В результате повьпиаеч ся надежность работы всего запоминающего устройства. 2 ил, 1 табл. со сл е

г- -4 JT

-lIlLJ4Й/2/

Изобретение относится к вычисли- тельнор технике, в частчости к полупроводниковым запоминающим устройствам (ЗУ).

Цель изобретения - повьш ение надежности ЗУ.

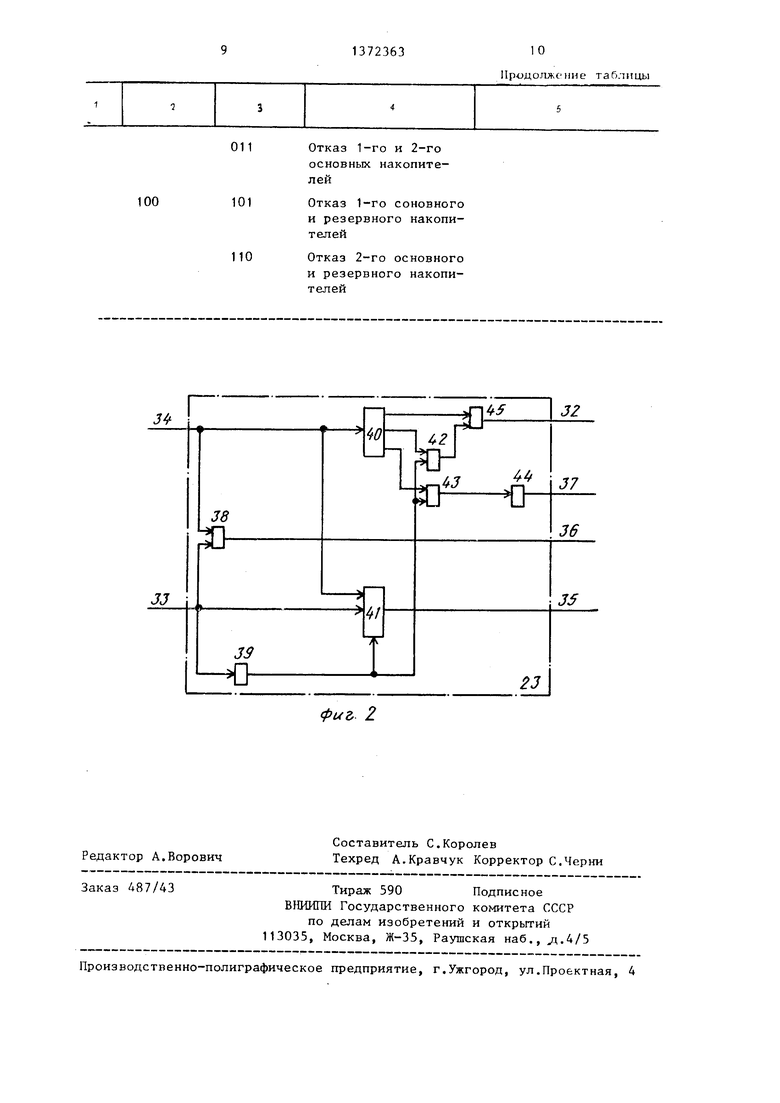

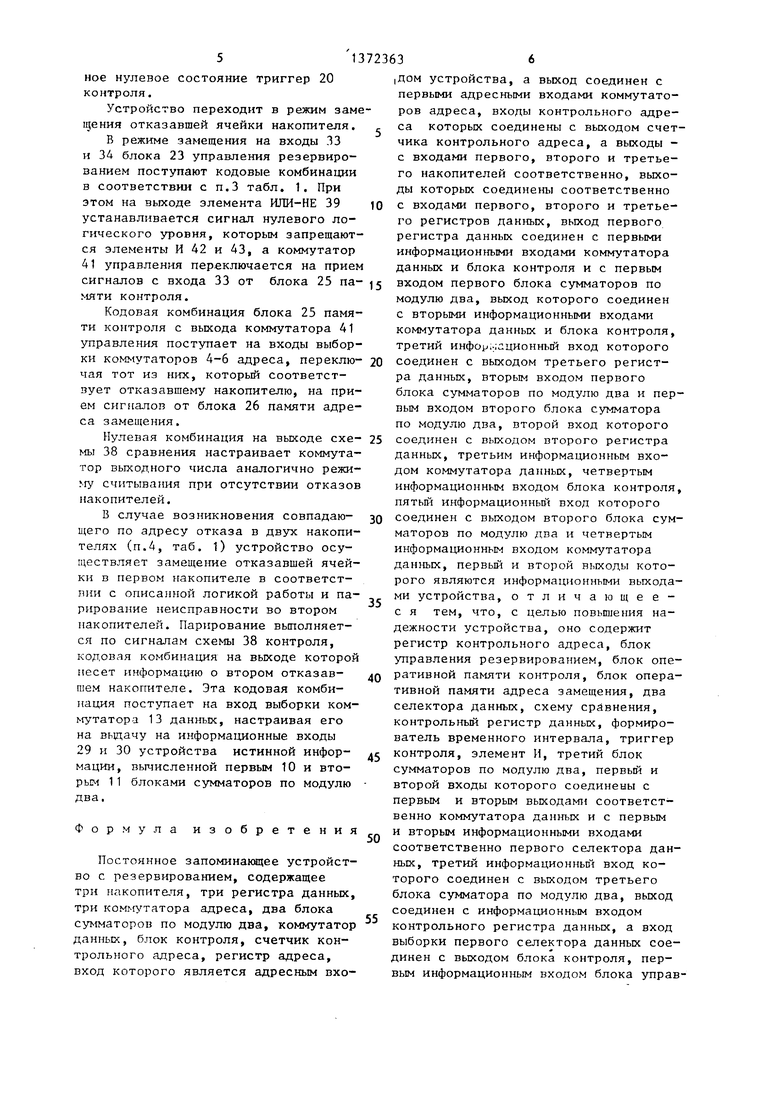

Па фиг. 1 представлена схема ЗУ с резервированием; на фиг. 2 - пример выполнения блока управления резе вированием.

ЗУ содержит 1, 2 и резервный 3 накопители, первый 4, второй 5 и третий 6 коммутаторы адреса, первый 7, второй 8 и третий 9 регистры данных, первый 10, второй 11, третий 12 блоки сумматоров по модулю два, коммутатор 13 , nepBbDi 14 и второй 15 селекторы данных, блок 16 контроля, контрольньш регистр 17, схему 18 сравнения, формирователь 19 временного интервала, триггер 20 конт- |роля, элемент И 21, регистр 22 адреса, бло1с 23 управления резервированием, регистр 24 контрольного адреса блок 25 оперативной памяти контроля, блок 26 оперативной памяти адреса замещения и счетчик 27 контрольного адреса.

Устройство имеет адресньй вход 28, 30 ступают от блока 25 накопителя и от

информационные выходы 29 и 30, вход 31 синхронизации и выход 32 контроля

Блок 23 управления резервирова- Ш1ем имеет входы 33 и 34 и выходы 32, 35-37 и содержит схему 38 сравнения, элемент HJIli-HE 39, дешифратор 40 сигналов контроля, коммутатор 41 сигналов управления, элементы И 42 и 43, формирователь 44 временных интервалов и элемент I-UIH 45.

Коммутаторы 4-6 адреса, селекторы 14 и 15 данных, коммутатор 13 данных коммутатор 41 сигналов управления могут быть выполнены на базе управляемых мультиплексоров серии К155.

Блок 16 контроля может быть выполнен в виде совокупности схем контроля, реализуюии1х: один из известных способов обнаружения отказов и выходных регистров, в которые в каждом такте обращения заносится результат контроля всех накопителей.

Дешифратор 40 сигналов контроля может быть выполнен, например, на

базе обычного дешифратора 3 - 8 и двух треквходовых элементов И-НЕ.

Выход дешифратора 3 - 8, соответствующий кодовой комбинации III на его входе, является третьим вы-

ходом дешифратора 40 сигналов отказа и подключен к одному из входов элемента ИЛИ 45.

Устройство работает в трех режимах: режим считывания при отсутствии отказов накопителей, режим самоконтроля отказавшегося накопителя и режим замещения отказавших ячеек накопителя.

Начальное состояние всех ячеек блоков 25 и 26 оперативной памяти и триггера 20 контроля соответствует нулевому логическому уровню и устанавливается сигналом (не показан) начальной установки.

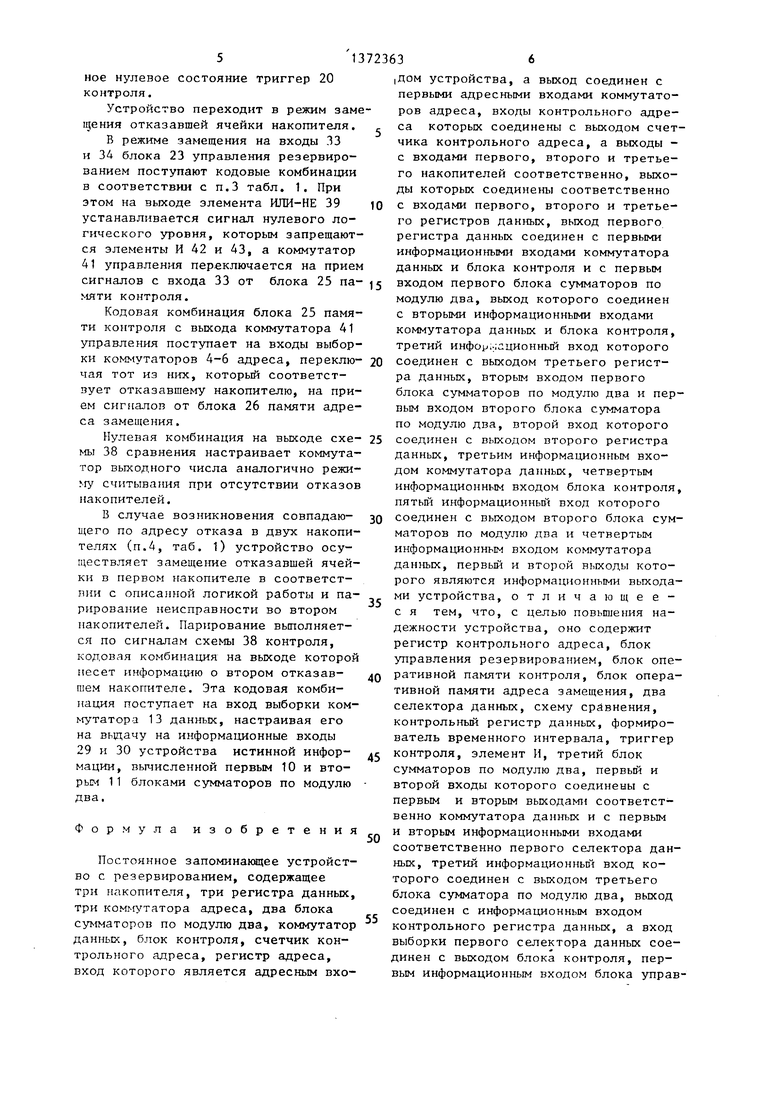

Управление режимами работы устройства осуществляется блоком 23 управления резервированием в зависимости от соотношения кодовых комбинаций, поступаюитх на ее входы 33 и 34 соответственно от блока 25 памяти контроля и блока 16 контроля. Возможные кодовые комбинации по входам 33 и 34 блока 23 и реализуемые при этом режимы работы устройства приведены в таблице.

При отсутствии отказов в накопителях на входы 33 и 34 блока 23 по5

0

5

0

5

блока 16 контроля исходные нулевые комбинации трехразрядного кода. Нулевая кодовая комбинация, поступающая с входа 33 на вход элемента ИЛИ-НЕ 39, устанавливает на его выходе сигнал единичного логического уровня. Этот сигнал переключает коммутатор 41 управления на прием сигналов с входа 34 от блока 16 контроля, а также разрешает прохождение сигналов от дешифратора 40 сигналов отказа через элементы И 42 и 43. Нулевая кодовая комбинация с выхода коммутатора 4l управления поступает на входы выборки ком гутаторов 4-6 адреса, переключая их на прием сигналов от регистра 22 адреса. Нулевая кодовая комбинация на выходе схемы

38 сравнения, свидетельствующая о поразрядном совпадении кодовых комбинаций на входах 33 и 34 блока 23 управления резервированием, поступает на вход выборки коммутатора 13 данных, настраивая его на прием и вьма- чу на информационные выходы 29 и 30 устройства, информации первого 1 и второго 2 рабочих накопителей с выходов первого 7 и второго 8 регистров данных.

Сигналом нулевого логического уровня с выхода триггера 20 контроля разрешена запись текущего адреса в регистр 24 контрольного адреса, запись сигналов контроля в выходные регистры блока 16 контроля, удерживается (блокируется) счетчик 27 контрольного адреса, запрещается прохождение на его вход сигналов с входа 31 синхронизации устройства через элемент И 21.

При возникновении отказа в одном из накопителей с выхода блока 16 контроля на вход 34 блока управления резервированием поступает кодовая комбинация, несущая информацию об отказавшем накопителе (п.2, табл.1).

Кодовая комбинация, поступающая через коммутатор 41 управления на входы выборки коммутаторов 4-6 адреса, переключает тот из них, который соответствует отказавшему накопителю на прием сигналов от счетчика 27 контрольного адреса.

Кодовая комбинация с выхода схемы 38 сравнения, полученная в результате поразрядного сравнения кодовых комбинаций на входах 33 и 34 (в данном случае она повторяет код на входе 34), поступает на вход выборки коммутатора 13 данных, настраивая его на прием и выдачу на информационные выходы 29 и 30 устройства вычисленной с помощью блоков сумматоров 10 и 11 истинной информации отказавшего накопителя.

Кодовая комбинация блока 16 контроля с входа 34 блока 23 управления резервированием подается на вход дещифратора 40 сигналов отказа. Сигнал единичного логического уровня с первого выхода дешифратора 40 через разрешенный элемент И 43 поступает на вход формирователя 44 временного интервала.

При одновременном отказе двух или трех накопителей сигнал единичного логического уровня поступает с второго выхода дешифратора 40 через разрешенный элемент И 42 на первьй вход элемента ИЛИ 45 и третьего выхода дешифратора 40 на второй вход элемента ИЛИ 45. Сигнал с выхода элемента ИЛИ 45 поступает на контрол ный выход 32 устройства, свидетельствуя об отказе устройства.

Сигналом с выхода формирователя 44 временного интервала триггера 20

0

5

0

5

0

5

0

5

контроля устанавливается в единичное состояние и в контрольный регистр 17 записывается истинная информация отказавшего накопителя, которая поступает через управляемый сигналами блока 16 контроля первый селектор 14 данных с выходов коммутатора 13 данных при отказе рабочих накопителей 1 и 2 или с выхода третьего блока сумматоров по модулю два 12 при отказе резервного накопителя 3.

Сигнал единичного логического уровня с выхода триггера 20 контроля блокирует запись текущего адреса в регистр 24 контрольного адреса и запись сигналов контроля отказавшего накопителя в выходной регистр блока 16 контроля, а также разрешает работу счетчика 27 контрольного адреса и прохождение на его вход сигналов с входа 31 синхронизации устройства через элемент И 21.

Устройство переходит в режим самоконтроля отказавшего накопителя, при этом вьщача истинной информации потребителю по команде обращения к устройству не приостанавливается.

Режим самоконтроля отказавшего накопителя заключается последовательном обходе массива адреса этого накопителя в поисках информации, идентичной истинной информации отказавшей ячейки.

Истинная информация отказавшей ячейки хранится в контрольном регистре 17 и поступает с его выхода на один из входов схемы 18 сравнения, на второй вход которой подается через управляемый сигналами блока 16 контроля второй селектор 15 данных информация отказавшего накопителя с выхода одного из регистров 7-9 чис- .ла.

При достижении адреса ячейки, информация которой идентична истинной информации отказавшей ячейки, схема 18 сравнения выдает сигнал, поступающий на вход формирователя 19 времен- ,ного интервала.

Сигналом с выхода формирователя 19 временного интервала производится запись в блоки 25 и 26 по адресу отказавшей ячейки соответственно кодовой комбинации сигналов блока 16 контроля и адреса ячейки замещения с выхода счетчика 27 контрольного адреса, а также устанавливается в исходное нулевое состояние триггер 20 контроля.

Устройство переходит в режим замещения отказавшей ячейки накопителя.

В режиме замещения на входы 33 и 34 блока 23 управления резервированием поступают кодовые комбинации в соответствии с п.З табл. 1. При этом на выходе элемента ИЛИ-НЕ 39 устанавливается сигнал нулевого логического уровня, которым запрещаются элементы И 42 и 43, а коммутатор 41 управления переключается на прием

сигналов с входа 33 от блока 25 па- входом первого блока сумматоров по

мяти контроля.

Кодовая комбинация блока 25 памяти контроля с выхода коммутатора 41 управления поступает на входы выборки коммутаторов 4-6 адреса, переклю- чая тот из них, который соответствует отказавшему накопителю, на прием сигналов от блока 26 памяти адреса замещения.

Нулевая комбинация на выходе схе- мы 38 сравнения настраивает коммутатор выходного числа аналогично режиму считывания при отсутствии отказов накопителей.

В случае возникновения совпадающего по адресу отказа в двух накопителях (п.4, таб. 1) устройство осуществляет замеще1тое отказавшей ячейки в первом накопителе в соответст- пии с описанной логикой работы и парирование неисправности во втором накопителей. Парирование выполняется по сигналам схемы 38 контроля, кодовая комбинация на выходе которой несет информагшю о втором отказавшем накопителе. Эта кодовая комбинация поступает на вход выборки ком- NryTaTopa 13 данных, настраивая его на вьщачу на информационные входы 29 и 30 устройства истинной информации, вычисленной первым 10 и вторым 11 блоками сумматоров по модулю два.

Формула изобретения

Постоянное запоминающее устройство с резервированием, содержащее три накопителя, три регистра данных, три коммутатора адреса, два блока сумматоров по модулю два, коммутатор данных, блок контроля, счетчик контрольного адреса, регистр адреса, вход которого является адресным вхо13723636

|Дом устройства, а выход соединен с

первыми адресными входами коммутаторов адреса, входы контрольного адреса которых соединены с выходом счетчика контрольного адреса, а выходы - с входами первого, второго и третьего накопителей соответственно, выходы которых соединены соответственно с входами первого, второго и третьего регистров данных, выход первого регистра данных соединен с первыми информационными входами коммутатора данных и блока контроля и с первым

0

0

5

5

0

5

0

5

модулю два, выход которого соединен с вторыми информационными входами коммутатора данных и блока контроля, третий инфор;:;ационный вход которого соединен с выходом третьего регистра данных, вторым входом первого блока сумматоров по модулю два и первым входом второго блока сумматора по модулю два, второй вход которого соединен с выходом второго регистра данных, третьим информационным входом коммутатора данных, четвертым информационным входом блока контроля, пятьй информационньп вход которого соединен с выходом второго блока сумматоров по модулю два и четвертым информационным входом коммутатора данных, первый и второй выходы которого являются информационными выходами устройства, отличающее- с я тем, что, с целью повышения надежности устройства, оно содержит регистр контрольного адреса, блок управления резервированием, блок оперативной памяти контроля, блок оперативной памяти адреса замещения, два селектора данных, схему сравнения, контрольный регистр данных, формирователь временного интервала, триггер контроля, элемент И, третий блок сумматоров по модулю два, первый и второй входы которого соединены с первым и вторым выходами соответственно коммутатора данных и с первым и вторым информационными входами соответственно первого селектора данных, третий информационньп вход которого соединен с выходом третьего блока сумматора по модулю два, выход соединен с информационным входом контрольного регистра данных, а вход выборки первого селектора данных соединен с выходом блока контроля, первым информационным входом блока управления резервированием, с информационным входом блока оперативной памяти контроля и входом выборки второго селектора данных, три информационных входа которого соединены с выходами первого, второго и третьего регистров данных соответственно, а выход соединен с первым информационным входом схемы сравнения, выход которой соединен с входом формирователя временного интервала, а второй инфор- мационньй вход - с выходом контрольного регистра данных, вход выборки которого соединен с выходом установки блока управления резервированием, входом установки триггера контроля, вход сброса которого соединен с выходом формирователя временного интервала и с входами выборки блоков оперативной памяти контроля и адреса замещения, выход триггера контроля соединен с первым входом элемента И, с входами выборки счетчика контрольного адреса, блока контроля и конт

000

001 010 100

001 010 100

Отказов нет

Отказ 1-го основного накопителя

Отказ 2-го основного накопителя

Отказ резервного накопителя

Отказ 1-го основного накопителя Отказ 2-го основного накопителя Отказ резервного накопителя

001

101

011

Замещение отказавшей .ячейки и парирование

Отказ 1-го основного и резервного накопителейОтказ 1-го и 2-го основных накопителей совпадающего по адресу

110

Отказ 2-го основного и резервного накопителей

0

5

0

5

рольного регистра адреса, информаци- онньй вход которого соединен с входом регистра адреса, а выход соединен с информационным входом блока оперативной памяти адреса замещения и адресным входом блока оперативной памяти контроля, выход которого соединен с вторым информационным входом блока управления резервированием, контрольньп выход которого является контрольным выходом устройства, выход сравнения соединен с входом выборки коммутатора данных, а информационный выход соединен с входами выборки коммутаторов адреса, вторые адресные входы которых соединены с выходами блока оперативной памяти адреса замещения, адресный вход которого соединен с выходом счетчика контрольного адреса, счетный вход которого соединен с выходом элемента И, второй вход которого шляет- ся входом синхронизапии устройства .

Считывание при отсутствии отказов накопителей

Самоконтроль отказавшего

накопителя

Замещение

отказавшей

ячейки

Замещение отказавшей .ячейки и парирование

совпадающего по адрес

отказа двух накопителей

00

011

101

110

Отказ 1-го и 2-го основных накопителей

Отказ 1-го соновного и резервного накопителей

Отказ 2-го основного и резервного накопителей

фиг,. 2

Продолжение таблицы

| Запоминающее устройство с блокировкой неисправных ячеек | 1983 |

|

SU1115108A1 |

| Солесос | 1922 |

|

SU29A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-02-07—Публикация

1986-08-27—Подача