4

Ь 00 hO 00 Ы

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ФОТОМЕТРИРОВАНИЯ ИЗОБРАЖЕНИЙ С ВЫРАЖЕННЫМ МАКСИМУМОМ ПРОСТРАНСТВЕННОГО РАСПРЕДЕЛЕНИЯ ОСВЕЩЕННОСТИ | 1995 |

|

RU2084842C1 |

| Многоканальный фотометр | 1988 |

|

SU1569584A1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ ТЕМНОВОГО СИГНАЛА МНОГОЭЛЕМЕНТНЫХ ФОТОДИОДНЫХ ПРИЕМНИКОВ | 1995 |

|

RU2102837C1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ РАЗЛИЧИЙ В ЧУВСТВИТЕЛЬНОСТИ ЭЛЕМЕНТОВ МАТРИЦЫ ФОТОПРИЕМНИКОВ | 1995 |

|

RU2108685C1 |

| Многоканальный спектрометр | 1988 |

|

SU1627865A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1992 |

|

RU2045781C1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

| Устройство для определения углового положения указателя стрелочных приборов | 1987 |

|

SU1532812A1 |

| Устройство для считывания графической информации | 1986 |

|

SU1377882A1 |

| Устройство для отображения информации | 1991 |

|

SU1809460A1 |

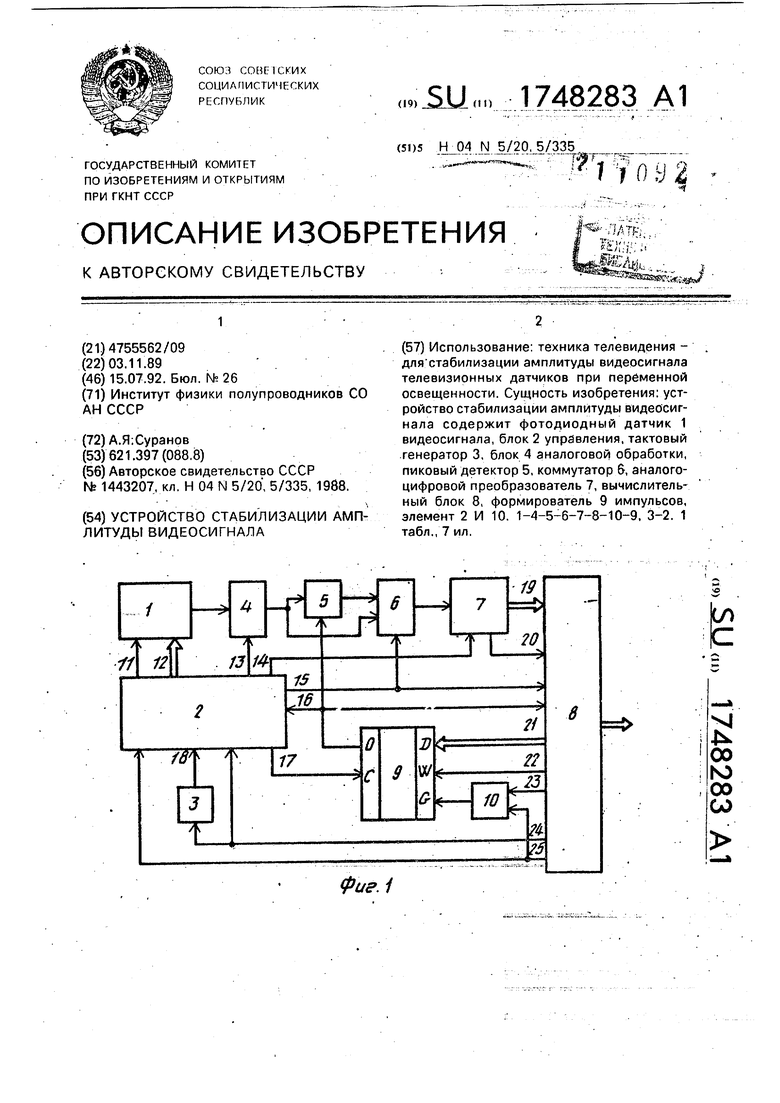

Использование техника телевидения - для стабилизации амплитуды видеосигнала телевизионных датчиков при переменной освещенности. Сущность изобретения: устройство стабилизации амплитуды видеосигнала содержит фотодиодный датчик 1 видеосигнала, блок 2 управления,тактовый генератор 3, блок 4 аналоговой обработки, пиковый детектор 5, коммутатор б, аналого- цифровой преобразователь 7, вычислительный блок 8, формирователь 9 импульсов, элемент 2 И 10. 1-4-5-6-7-8-10-9, 3-2. 1 табл., 7 ил.

Фие.1

Изобретение относится к телевизионной технике, в частности к устройствам, предназначенным для автоматического регулирования амплитуды видеосигнала и может быть использовано в цифровых телевизионных передающих камерах с датчиками изображения на основе фотодиодных аинеек или матриц, допускающих неразрушающее считывание сигнала.

Известно устройство стабилизации амплитуды видеосигнала, содержащее датчик рассогласования, RS-триггер, счетчики длины строки (кадра) и задержки экспозиции, а также ряд элементов и 2И-НЕ, в котором стабилизация амплитуды видеосигнала осуществляется путем уменьшения или увеличения числа тактовых импульсов, поступающих на счетчик задержки экспозиции на время накопления. Однако такое устройство не обеспечивает высокой скорости стабилизации амплитуды видеосигнала при существенных перепадах освещенности и в начальный момент времени после включения устройства. Снижение скорости стабилизации в первом случае происходит за счет того, что величина изменения времени накопления выбирается пропорциональной самому времени накопления, а не величине изменения входной освещенности, которое и вызвйло существующее изменение видеосигнала. Во втором случае фазировка счетчика задержки экспозиции относительно счетчика длины строки является неопределенной, что может потребовать большего числа шагов стабилизации.

Наиболее близким к изобретению является устройство стабилизации амплитуды видеосигнала, содержащее датчик изображения на приборе с зарядовой связью (ПЗС), в котором сигнал после считывания не сохраняется, блок управления, управляемый одновибратор, последовательно включенные видеоусилитель, пиковый детектор со сбросом, блок вычитания с источником опорного напряжения, аналого-цифровой преобразователь (АЦП) и вычислительный блок. Данное устройство в конце каждого интервала считывания по измеренному максимальному сигналу и известному времени накопления рассчитывает и устанавливает величину оптимального времени накопления, при котором уровень мак- симального сигнала будет находиться вблизи Оптимального уровня U0 независимо от изменения уровня входной освещенности. Указанный способ регулирования по- зволя ет существенно повысить быстродействие устройства, однако при резком изменении освещенности или в начале работы устройства ему необходимо выполнить как минимум два цикла накопления сигнала (один для определения максимальной освещённости, другой - для регистрации сигнала), что приводит к потере

регистрируемой информации.

Целью изобретения является повышение точности стабилизации при резких изменениях освещенности.

Поставленная цель достигается тем, что

0 в устройство стабилизации амплитуды видеосигнала, содержащее последовательно соединенные фотодиодный датчик и блок аналоговой обработки, пиковый детектор, аналого-цифровой преобразователь, блок

5 управления и вычислительный блок, первый выход которого является выходом устройства стабилизации амплитуды видеосигнала, введены коммутатор, первый и второй информационные входы которого соединены с

0 выходами блока аналоговой обработки и пикового детектора соответственно, а выход - соединен с информационным входом аналого-цифрового преобразователя выход которого соединен с информационным входом

5 вычислительного блока, элемент2И, первый вход которого соединен со вторым выходом вычислительного блока, формирователь импульсов, первый, второй, третий и четвертый входы которого соединены соответ0 ственно с третьим и четвертым выходами вычислительного блока с выходом элемента 2И и с первым выходом блока управления, а выход соединен с входом сброса пикового детектора, а также тактовый генератор, вход

5 управления которого соединен с -первым входом блока управления и с пятым выходом вычислительного блока, а выход соединен с вторым входом блока управления, третий вход которого соединен с шестым

0 выходом вычислительного блока и со вторым входом элемента 2И, четвертый вход блока управления соединен с выходом формирователя импульсов и с первым управляющим входом вычислительного блока, а

5 первый, второй, третий, четвертый и пятый выходы соединены соответственно с первым и вторым входами фотодиодного датчика видеосигнала, с управляющим входом блока аналоговой обработки, с тактовым

0 входом аналого-цифрового преобразователя, с объединенными управляющими входом коммутатора и вторым управляющим входом вычислительного блока, третий управляющий вход которого соединен с выхо5 дом аналого-цифрового преобразователя.. В электронике известны функциональные элементы, введенные в схему устройства стабилизации амплитуды видеосигнала. Однако наличие новых связей между ними обусловило появление у предлагаемого устройства возможности выбора оптимального времени накопления за один цикл накопления сигнала при резком изменении входной освещенности или в начале работы устройства.. Это качество не является результатом суммирования положительных эффектов, достигаемых от введения новых Элементов или использования готовых технических решений и достигается именно за счет наличия между элементами новых связей.

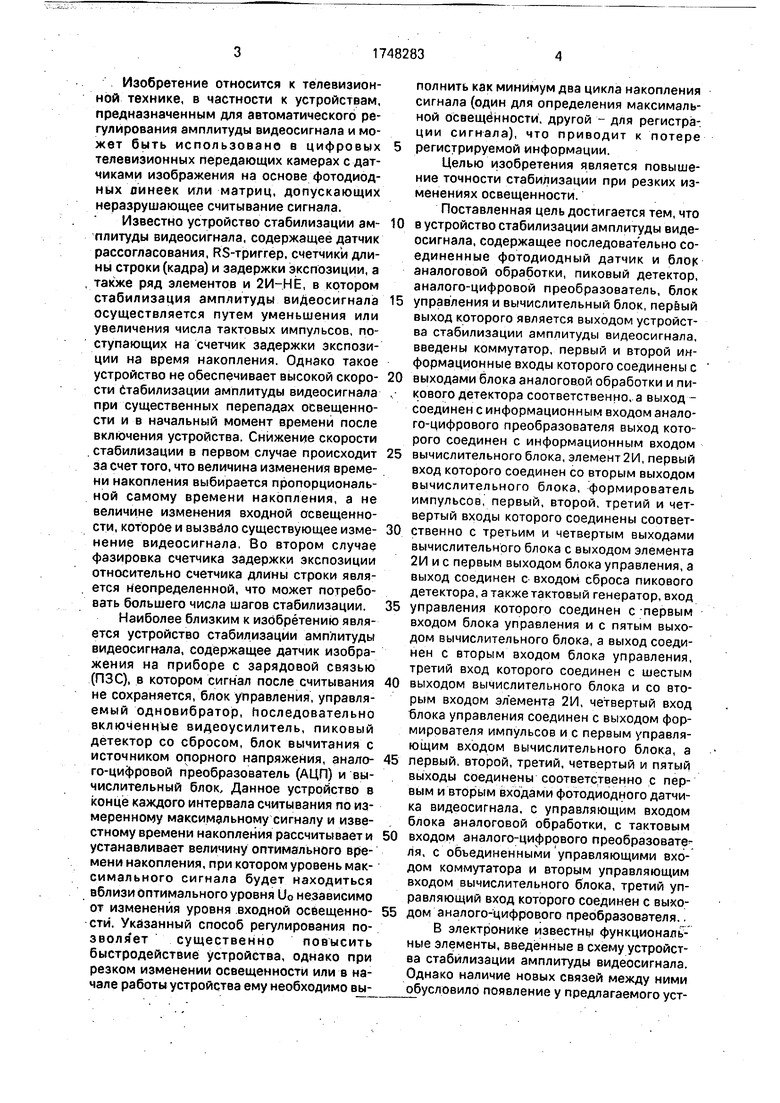

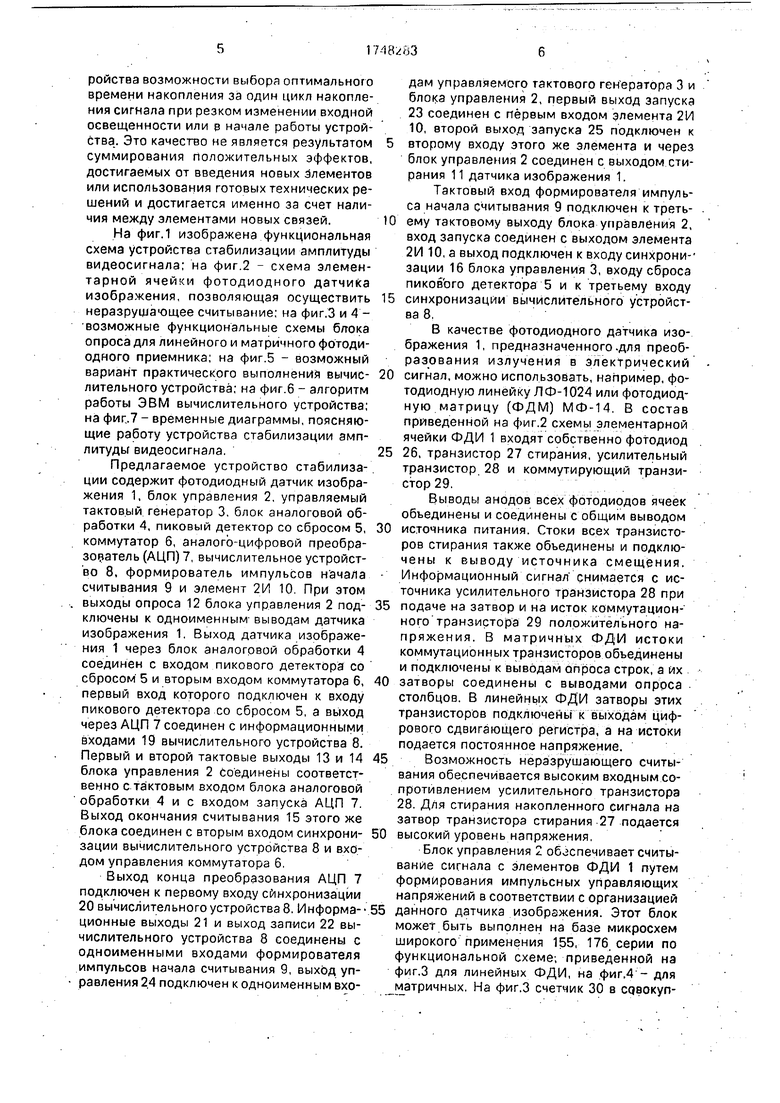

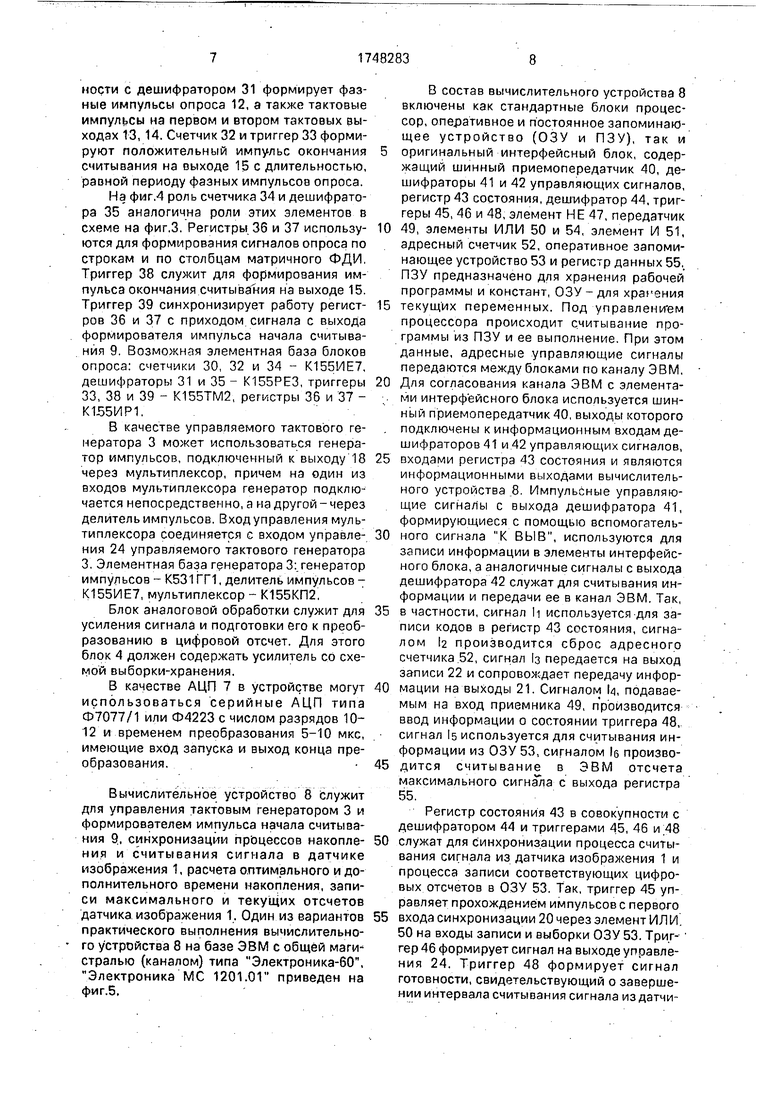

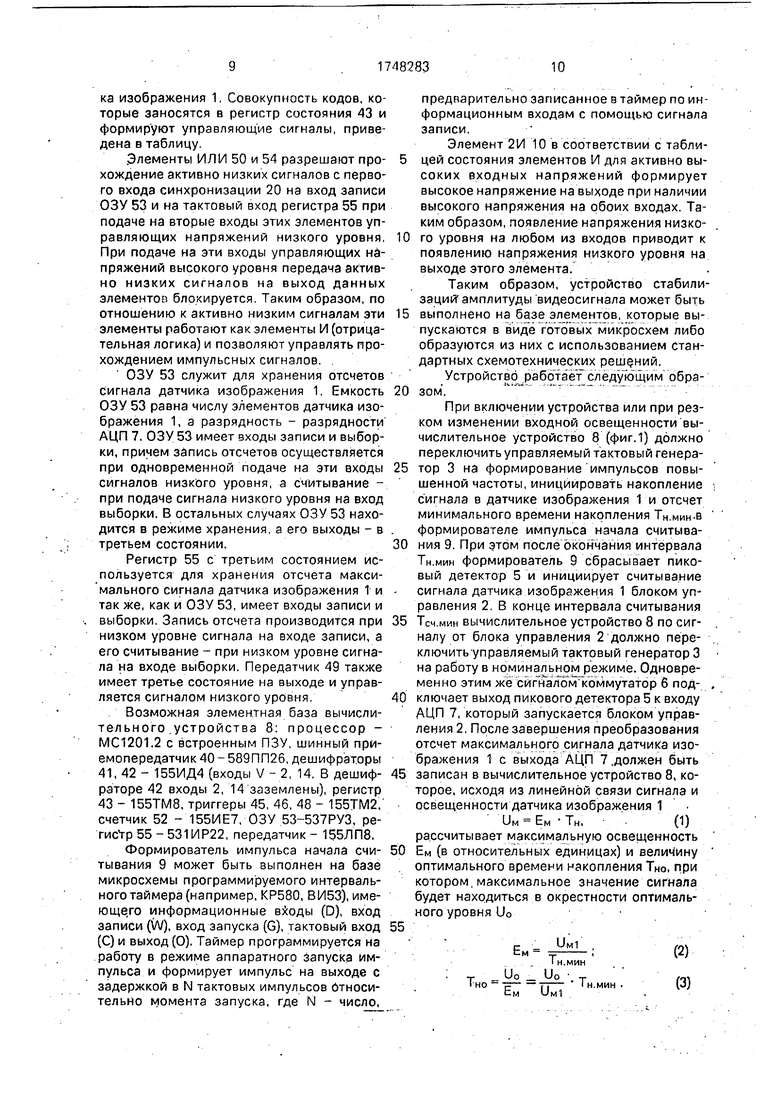

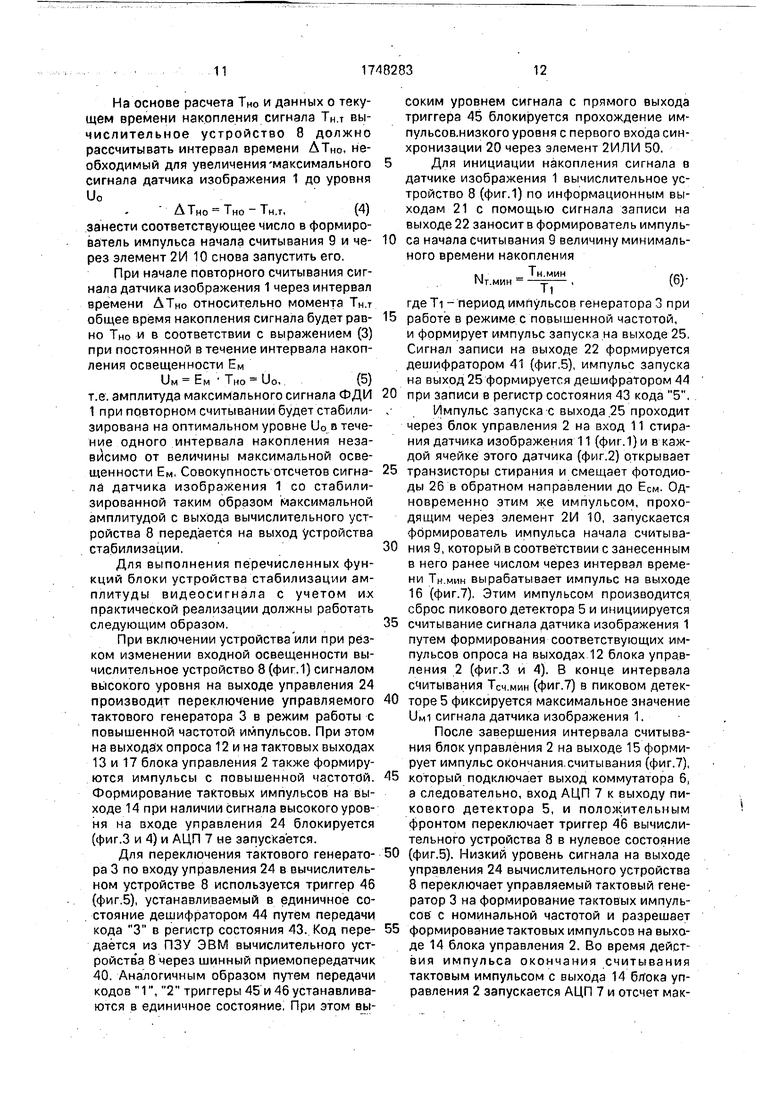

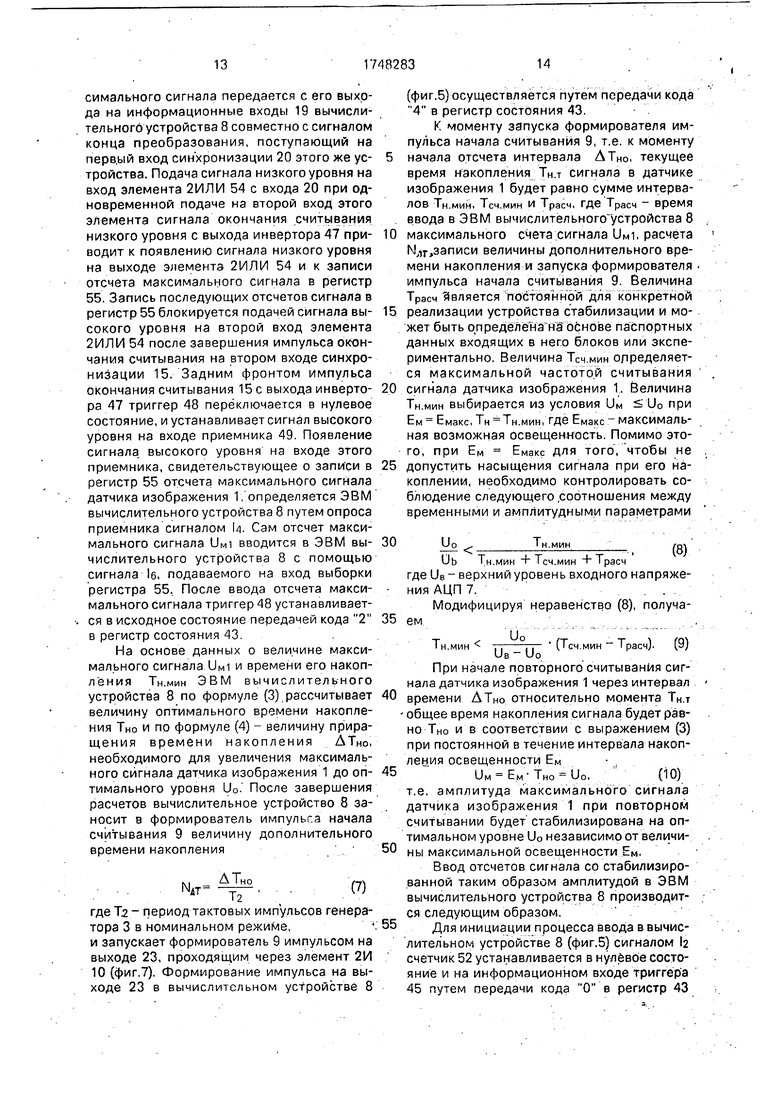

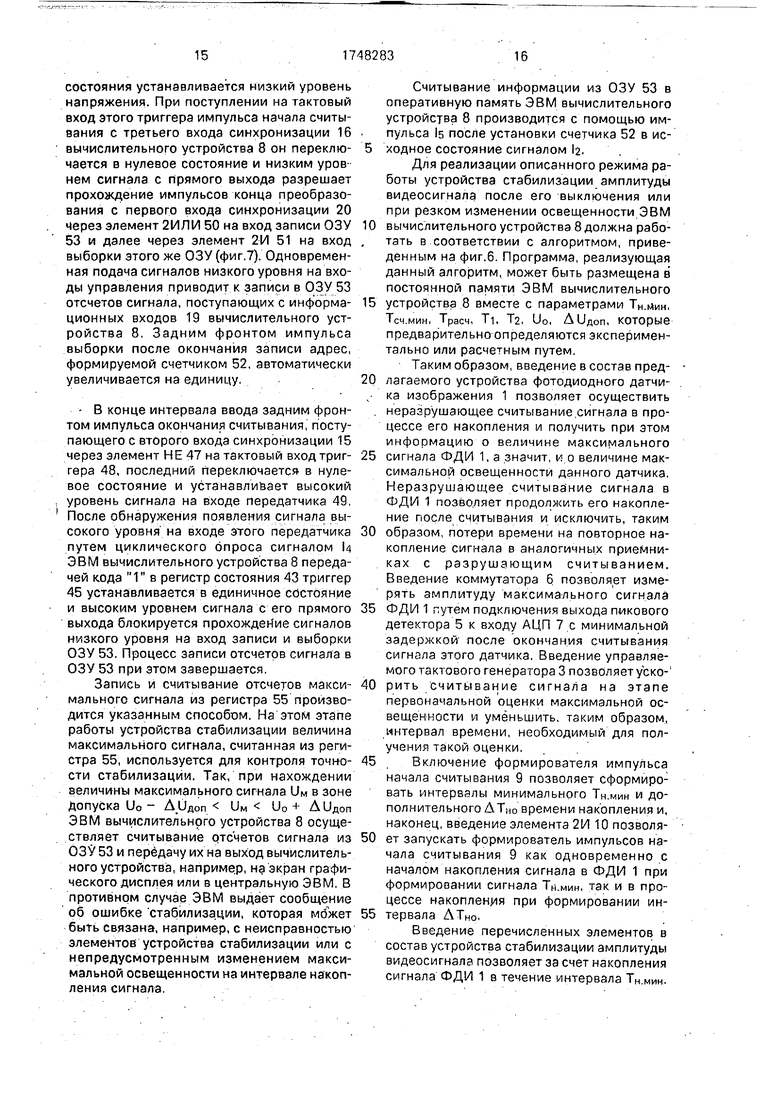

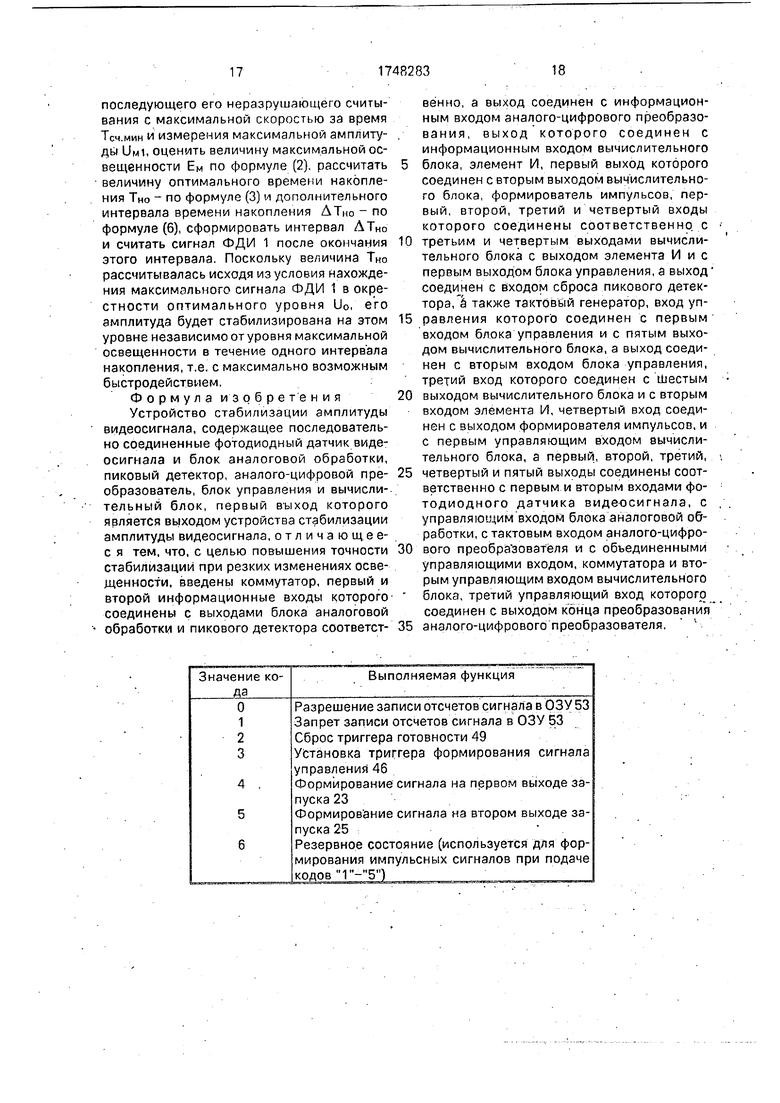

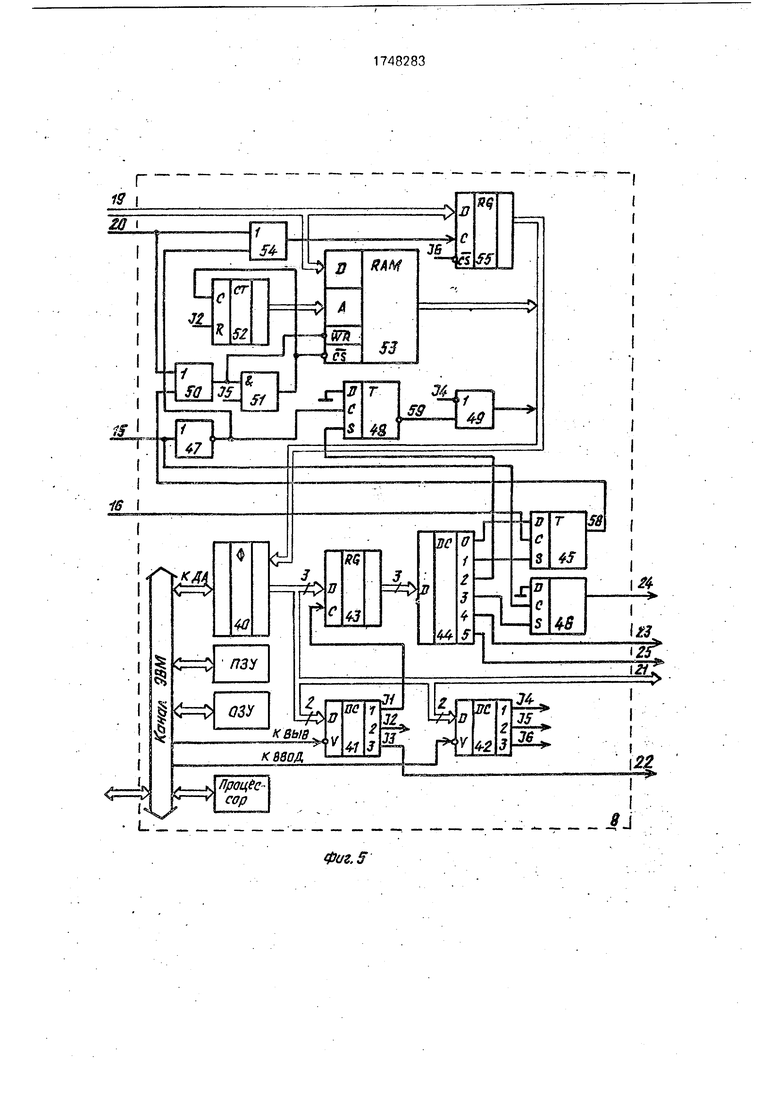

На фиг.1 изображена функциональная схема устройства стабилизации амплитуды видеосигнала; на фиг.2 - схема элементарной ячейки фотодиодного датчика изображения, позволяющая осуществить неразрушающее считывание; на фиг.З и 4 - возможные функциональные схемы блока опроса для линейного и матричного фотодиодного приемника; на фиг.5 - возможный вариант практического выполнения вычислительного устройства; на фиг.6 - алгоритм работы ЭВМ вычислительного устройства; на фиг.7 - временные диаграммы, поясняющие работу устройства стабилизации амплитуды видеосигнала.

Предлагаемое устройство стабилизации содержит фотодиодный датчик изображения 1, блок управления 2, управляемый тактовый генератор 3, блок аналоговой обработки 4, пиковый детектор со сбросом 5, коммутатор б, аналого-цифровой преобразователь (АЦП) 7, вычислительное устройство 8, формирователь импульсов начала считывания 9 и элемент 2И 10 При этом выходы опроса 12 блока управления 2 подключены к одноименным выводам датчика изображения 1. Выход датчика изображения 1 через блок аналоговой обработки 4 соединен с входом пикового детектора со сбросом 5 и вторым входом коммутатора 6, первый вход которого подключен к входу пикового детектора со сбросом 5, а выход через АЦП 7 соединен с информационными входами 19 вычислительного устройства 8. Первый и второй тактовые выходы 13 и 14 блока управления 2 соединены соответственно с тактовым входом блока аналоговой обработки 4 и с входом запуска АЦП 7. Выход окончания считывания 15 этого же блока соединен с вторым входом синхронизации вычислительного устройства 8 и входом управления коммутатора 6.

Выход конца преобразования АЦП 7 подключен к первому входу синхронизации 20 вычислительного устройства 8. Информа- ционные выходы 21 и выход записи 22 вычислительного устройства 8 соединены с одноименными входами формирователя импульсов начала считывания 9, выход управления 24 подключен к одноименным входам управляемого тактового генератора 3 и блока управления 2, первый выход запуска 23 соединен с первым входом элемента 2И 10, второй выход запуска 25 подключен к 5 второму входу этого же элемента и через блок управления 2 соединен с выходом стирания 11 датчика изображения 1.

Тактовый вход формирователя импульса начала считывания 9 подключен к треть- 0 ему тактовому выходу блока управления 2, вход запуска соединен с выходом элемента 2И 10, а выход подключен к входу синхронизации 16 блока управления 3, входу сброса пикового детектора 5 и к третьему входу

5 синхронизации вычислительного устройства 8,

В качестве фотодиодного датчика изображения 1, предназначенного .для преобразования излучения в электрический

0 сигнал, можно использовать, например, фотодиодную линейку Л Ф-1024 или фотодиодную матрицу (ФДМ) МФ-14, В состав приведенной на фиг.2 схемы элементарной ячейки ФДИ 1 входят собственно фотодиод

5 26, транзистор 27 стирания, усилительный транзистор 28 и коммутирующий транзистор 29.

Выводы анодов всех фотодиодов ячеек объединены и соединены с общим выводом

0 источника питания. Стоки всех транзисторов стирания также объединены и подключены к выводу источника смещения. Информационный сигнал снимается с источника усилительного транзистора 28 при

5 подаче на затвор и на исток коммутационного транзистора 29 положительного напряжения. В матричных ФДИ истоки коммутационных транзисторов объединены и подключены к выводам опроса строк, а их

0 затворы соединены с выводами опроса столбцов. В линейных ФДИ затворы этих транзисторов подключены к выходам цифрового сдвигающего регистра, а на истоки подается постоянное напряжение.

5 Возможность неразрушающего считывания обеспечивается высоким входным сопротивлением усилительного транзистора 28. Для стирания накопленного сигнала на затвор транзистора стирания 27 подается

0 высокий уровень напряжения,

Блок управления 2 обеспечивает считывание сигнала с элементов ФДИ 1 путем формирования импульсных управляющих напряжений в соответствии с организацией

5 данного датчика изображения. Этот блок может быть выполнен на базе микросхем широкого применения 155, 176 серии по функциональной схеме; приведенной на фиг.З для линейных ФДИ, на фиг.4 - для матричных. На фиг.З счетчик 30 в савокупности с дешифратором 31 формирует фазные импульсы опроса 12, а также тактовые импульсы на первом и втором тактовых выходах 13, 14. Счетчик 32 и триггер 33 формируют положительный импульс окончания считывания на выходе 15 с длительностью, равной периоду фазных импульсов опроса.

На фиг.4 роль счетчика 34 и дешифратора 35 аналогична роли этих элементов в схеме на фиг.З. Регистры 36 и 37 используются для формирования сигналов опроса по строкам и по столбцам матричного ФДИ, Триггер 38 служит для формирования импульса окончания считывания на выходе 15. Триггер 39 синхронизирует работу регистров 36 и 37 с приходом сигнала с выхода формирователя импульса начала считывания 9. Возможная элементная база блоков опроса: счетчики 30, 32 и 34 - К155ИЕ7, дешифраторы 31 и 35 - К155РЕЗ, триггеры 33, 38 и 39 - К155ТМ2, регистры 36 и 37 - К155ИР1.

В качестве управляемого тактового генератора 3 может использоваться генератор импульсов, подключенный к выходу 18 через мультиплексор, причем на один из входов мультиплексора генератор подключается непосредственно, а на другой - через делитель импульсов. Вход управления мультиплексора соединяется с входом управления 24 управляемого тактового генератора 3. Элементная база генератора 3:.генератор импульсов - К531ГГ1, делитель импульсов - К155ИЕ7, мультиплексор - К155КП2,

Блок аналоговой обработки служит для усиления сигнала и подготовки его к преобразованию в цифровой отсчет. Для этого блок 4 должен содержать усилитель со схемой выборки-хранения.

В качестве АЦП 7 в устройстве могут использоваться серийные АЦП типа Ф7077/1 или Ф4223 с числом разрядов 10- 12 и временем преобразования 5-10 мкс, имеющие вход запуска и выход конца преобразования.

Вычислительное устройство 8 служит для управления тактовым генератором 3 и формирователем импульса начала считывания 9, синхронизации процессов накопления и считывания сигнала в датчике изображения 1, расчета оптимального и дополнительного времени накопления, записи максимального и текущих отсчетов датчика изображения 1. Один из вариантов практического выполнения вычислительного устройства 8 на базе ЭВМ с общей магистралью (каналом) типа Электроника-60, Электроника МС 1201.01 приведен на фиг.5.

В состав вычислительного устройства 8 включены как стандартные блоки процессор, оперативное и постоянное запоминающее устройство (ОЗУ и ПЗУ), так и

оригинальный интерфейсный блок, содержащий шинный приемопередатчик 40, дешифраторы 41 и 42 управляющих сигналов, регистр 43 состояния, дешифратор 44, триггеры 45, 46 и 48, элемент НЕ 47, передатчик

0 49, элементы ИЛИ 50 и 54, элемент И 51, адресный счетчик 52, оперативное запоминающее устройство 53 и регистр данных 55, ПЗУ предназначено для хранения рабочей программы и констант, ОЗУ - для хранения

5 текущих переменных. Под управлением процессора происходит считывание программы из ПЗУ и ее выполнение. При этом данные, адресные управляющие сигналы передаются между блоками по каналу ЭВМ.

0 Для согласования канала ЭВМ с элементами интерфейсного блока используется шинный приемопередатчик 40, выходы которого подключены к информационным входам дешифраторов 41 и 42 управляющих сигналов,

5 входами регистра 43 состояния и являются информационными выходами вычислительного устройства 8. Импульсные управляющие сигналы с выхода дешифратора 41, формирующиеся с помощью вспомогатель0 ного сигнала К ВЫВ, используются для записи информации в элементы интерфейсного блока, а аналогичные сигналы с выхода дешифратора 42 служат для считывания информации и передачи ее в канал ЭВМ. Так,

5 в частности, сигнал h используется для записи кодов в регистр 43 состояния, сигналом 2 производится сброс адресного счетчика 52, сигнал з передается на выход записи 22 и сопровождает передачу инфор0 мации на выходы 21. Сигналом 14, подаваемым на вход приемника 49, производится ввод информации о состоянии триггера 48, сигнал Is используется для считывания информации из ОЗУ 53, сигналом 1е произво5 дится считывание в ЭВМ отсчета максимального сигнала с выхода регистра 55.

Регистр состояния 43 в совокупности с дешифратором 44 и триггерами 45, 46 и 48

0 служат для синхронизации процесса считывания сигнала из датчика изображения 1 и процесса записи соответствующих цифровых отсчетов в ОЗУ 53. Так, триггер 45 управляет прохождением импульсов с первого

5 входа синхронизации 20 через элемент ИЛ И, 50 на входы записи и выборки ОЗУ 53. Триг- гер 46 формирует сигнал на выходе управле- ния 24. Триггер 48 формирует сигнал готовности, свидетельствующий о завершении интервала считывания сигнала из датчика изображения 1, Совокупность кодов, которые заносятся в регистр состояния 43 и формируют управляющие сигналы, приведена в таблицу.

Элементы ИЛИ 50 и 54 разрешают про- хождение активно низких сигналов с первого входа синхронизации 20 на вход записи ОЗУ 53 и на тактовый вход регистра 55 при подаче на вторые входы этих элементов управляющих напряжений низкого уровня, При подаче на эти входы управляющих напряжений высокого уровня передача активно низких сигналов на выход данных элементов блокируется Таким образом, по отношению к активно низким сигналам эти элементы работают как элементы И (отрицательная логика) и позволяют управлять прохождением импульсных сигналов.

ОЗУ 53 служит для хранения отсчетов сигнала датчика изображения 1. Емкость ОЗУ 53 равна числу элементов датчика изображения 1, а разрядность - разрядности АЦП 7. ОЗУ 53 имеет входы записи и выборки, причем запись отсчетов осуществляется при одновременной подаче на эти входы сигналов низкого уровня, а считывание - при подаче сигнала низкого уровня на вход выборки. В остальных случаях ОЗУ 53 находится в режиме хранения, а его выходы - в третьем состоянии.

Регистр 55 с третьим состоянием используется для хранения отсчета максимального сигнала датчика изображения 1 и так же, как и ОЗУ 53, имеет входы записи и выборки. Запись отсчета производится при низком уровне сигнала на входе записи, а его считывание - при низком уровне сигнала на входе выборки. Передатчик 49 также имеет третье состояние на выходе и управляется сигналом низкого уровня.

Возможная элементная база вычислительного устройства 8: процессор - МС1201.2 с встроенным ПЗУ, шинный приемопередатчик 40 - 589ПП26, дешифраторы 41, 42 - 155ИД4 (входы V - 2, 14. В дешиф- раторе 42 входы 2, 14 заземлены), регистр 43 - 155ТМ8, триггеры 45, 46, 48 - 155ТМ2, счетчик 52 - 155ИЕ7, ОЗУ 53-537РУЗ, регистр 55 - 531И Р22, передатчик- 155ЛП8.

Формирователь импульса начала счи- тывания 9 может быть выполнен на базе микросхемы программируемого интервального таймера (например, КР580, ВИ53), имеющего информационные входы (D), вход записи (W), вход запуска (G), тактовый вход (С) и выход (О), Таймер программируется на работу в режиме аппаратного запуска импульса и формирует импульс на выходе с задержкой в N тактовых импульсов Относительно момента запуска, где N - число,

предварительно записанное в таймер по информационным входам с помощью сигнала записи.

Элемент 2И 10 в соответствии с таблицей состояния элементов И для активно высоких входных напряжений формирует высокое напряжение на выходе при наличии высокого напряжения на обоих входах. Таким образом, появление напряжения низкого уровня на любом из входов приводит к появлению напряжения низкого уровня на выходе этого элемента.

Таким образом, устройство стабилизации амплитуды видеосигнала может быть выполнено на базе элементов, которые выпускаются в виде готовых микросхем либо образуются из них с использованием стандартных схемотехнических решений.

Устройство следующим образом.

При включении устройства или при резком изменении входной освещенности вычислительное устройство 8 (фиг.1) должно переключить управляемый тактовый генератор 3 на формирование импульсов повышенной частоты, инициировать накопление сигнала в датчике изображения 1 и отсчет минимального времени накопления Тн мин-в формирователе импульса начала считывания 9. При этом после окончания интервала Тн мин формирователь 9 сбрасывает пиковый детектор 5 и инициирует считывание сигнала датчика изображения 1 блоком управления 2 В конце интервала считывания ТСч мин вычислительное устройство 8 по сигналу от блока управления 2 должно переключить управляемый тактовый генератор 3 на работу в номинальном режиме. Одновременно этим же сигналом коммутатор б подключает выход пикового детектора 5 к входу АЦП 7, который запускается блоком управления 2. После завершения преобразования отсчет максимального сигнала датчика изображения 1 с выхода АЦП 7.должен быть записан в вычислительное устройство 8, которое, исходя из линейной связи сигнала и освещенности датчика изображения 1

UM Ем Тн,(1)

рассчитывает максимальную освещенность Ем (в относительных единицах) и величину оптимального времени накопления Тно, при котором максимальное значение сигнала будет находиться в окрестности оптимального уровня U0

Ем

UM1

,

но

Тн.МИН Up Up

Ем UM1

Тн

мин

(2) (3)

На основе расчета ТНо и данных о текущем времени накопления сигнала Тн.т вычислительное устройство 8 должно рассчитывать интервал времени ДТНо, необходимый для увеличения-максимального сигнала датчика изображения 1 до уровня

U0

ДТно Тно-Тн.т,(4)

занести соответствующее число в формирователь импульса начала считывания 9 и через элемент 2И 10 снова запустить его.

При начале повторного считывания сигнала датчика изображения 1 через интервал времени ДТно относительно момента Тн.т общее время накопления сигнала будет равно Тно и в соответствии с выражением (3) при постоянной в течение интервала накопления освещенности Ем

Км Ем Тно Uo,(5)

т.е. амплитуда максимального сигнала ФДИ 1 при повторном считывании будет стабилизирована на оптимальном уровне Do в течение одного интервала накопления независимо от величины максимальной освещенности Ем, Совокупность отсчетов сигнала датчика изображения 1 со стабилизированной таким образом максимальной амплитудой с выхода вычислительного устройства 8 передается на выход устройства стабилизации.

Для выполнения перечисленных функций блоки устройства стабилизации амплитуды видеосигнала с учетом их практической реализации должны работать следующим образом.

При включении устройства или при резком изменении входной освещенности вычислительное устройство 8 (фиг.1) сигналом высокого уровня на выходе управления 24 производит переключение управляемого тактового генератора 3 в режим работы с повышенной частотой импульсов. При этом на выходах опроса 12 и на тактовых выходах 13 и 17 блока управления 2 также формируются импульсы с повышенной частотой. Формирование тактовых импульсов на выходе 14 при наличии сигнала высокого уровня на входе управления 24 блокируется (фиг.З и 4) и АЦП 7 не запускается.

Для переключения тактового генератора 3 по входу управления 24 в вычислительном устройстве 8 используется триггер 46 (фиг.5), устанавливаемый в единичное состояние дешифратором 44 путем передачи кода 3 в регистр состояния 43. Код передаётся из ПЗУ ЭВМ вычислительного устройства 8 через шинный приемопередатчик 40. Аналогичным образом путем передачи кодов 1, 2 триггеры 45 и 46 устанавливаются в единичное состояние, При этом высоким уровнем сигнала с прямого выхода триггера 45 блокируется прохождение им- пульсов.низкого уровня с первого входа синхронизации 20 через элемент 2ИЛИ 50.

Для инициации накопления сигнала в

датчике изображения 1 вычислительное устройство 8 (фиг.1) по информационным выходам 21 с помощью сигнала записи на выходе 22 заносит в формирователь импульса начала считывания 9 величину минимального времени накопления

м Тн.мин/-ч

Мт.мину,(о)

где Ti - период импульсов генератора 3 при

работе в режиме с повышенной частотой, и формирует импульс запуска на выходе 25. Сигнал записи на выходе 22 формируется дешифратором 41 (фиг,5), импульс запуска на выход 25 формируется дешифратором 44

при записи в регистр состояния 43 кода 5. Импульс запуска с выхода 25 проходит через блок управления 2 на вход 11 стирания датчика изображения 11 (фиг.1) и в каждой ячейке этого датчика (фиг.2) открывает

транзисторы стирания и смещает фотодиоды 26 в обратном направлении до ЕСм. Одновременно этим же импульсом, проходящим через элемент 2И 10, запускается формирователь импульса начала считывания 9, который в соответствии с занесенным в него ранее числом через интервал времени Тн мин вырабатывает импульс на выходе 16 (фиг.7), Этим импульсом производится сброс пикового детектора 5 и инициируется

считывание сигнала датчика изображения 1 путем формирования соответствующих импульсов опроса на выходах 12 блока управления 2 (фиг.З и 4). В конце интервала считывания Тсч.мин (фиг.7) в пиковом детекторе 5 фиксируется максимальное значение UM1 сигнала датчика изображения 1.

После завершения интервала считывания блок управления 2 на выходе 15 формирует импульс окончания считывания (фиг.7),

который подключает выход коммутатора 6, а следовательно, вход АЦП 7 к выходу пикового детектора 5, и положительным фронтом переключает триггер 46 вычислительного устройства 8 в нулевое состояние

(фиг,5). Низкий уровень сигнала на выходе управления 24 вычислительного устройства 8 переключает управляемый тактовый генератор 3 на формирование тактовых импульсов с номинальной частотой и разрешает

формирование тактовых импульсов на выходе 14 блока управления 2. Во время действия импульса окончания считывания тактовым импульсом с выхода 14 бл ока управления 2 запускается АЦП 7 и отсчет максимального сигнала передается с его выхода на информационные входы 19 вычислительного устройства 8 совместно с сигналом конца преобразования, поступающий на первый вход синхронизации 20 этого же устройства. Подача сигнала низкого уровня на вход элемента 2ИЛИ 54 с входа 20 при одновременной подаче на второй вход этого элемента сигнала окончания считывания низкого уровня с выхода инвертора 47 приводит к появлению сигнала низкого уровня на выходе элемента 2ИЛИ 54 и к записи отсчета максимального сигнала в регистр 55. Запись последующих отсчетов сигнала в регистр 55 блокируется подачей сигнала высокого уровня на второй вход элемента 2ИЛИ 54 после завершения импульса окончания считывания на втором входе синхронизации 15. Задним фронтом импульса окончания считывания 15с выхода инвертора 47 триггер 48 переключается в нулевое состояние, и устанавливает сигнал высокого уровня на входе приемника 49 Появление сигнала высокого уровня на входе этого приемника, свидетельствующее о записи в регистр 55 отсчета максимального сигнала датчика изображения 1 определяется ЭВМ вычислительного устройства 8 путем опроса приемника сигналом Ц Сам отсчет максимального сигнала UM1 вводится в ЭВМ вычислительного устройства 8 с помощью сигнала б, подаваемого на вход выборки регистра 55. После ввода отсчета максимального сигнала триггер 48 устанавливается в исходное состояние передачей кода 2 в регистр состояния 43

На основе данных о величине максимального сигнала UM1 и времени его накопления Тн мин ЭВМ вычислительного устройства 8 по формуле (3) рассчитывает величину оптимального времени накопления Тно и по формуле (4) - величину приращения времени накопления АТНо, необходимого для увеличения максимального сигнала датчика изображения 1 до оптимального уровня Uo После завершения расчетов вычислительное устройство 8 заносит в формирователь импульса начала считывания 9 величину дополнительного времени накопления

%

АТН Т2

(7)

где Та - период тактовых имп ульсов генератора 3 в номинальном режиме, и запускает формирователь 9 импульсом на выходе 23, проходящим через элемент 2И 10 (фиг.7). Формирование импульса на выходе 23 в вычислительном устройстве 8

(фиг.5) осуществляется путем передачи кода 4 в регистр состояния 43

К моменту запуска формирователя импульса начала считывания 9, т.е. к моменту

начала отсчета интервала ДТНо, текущее время накопления Тнт сигнала в датчике изображения 1 будет равно сумме интервалов Тн мин, Тсч мин и Трасч, где Трасч время ввода в ЭВМ вычислительного устройства 8

0 максимального счета сигнала UM1, расчета М,1Т,записи величины дополнительного времени накопления и запуска формирователя импульса начала считывания 9 Величина Трасч Является постоянной для конкретной

5 реализации устройства стабилизации и может быть определена нЗ основе паспортных данных входящих в него блоков или экспериментально. Величина ТСч мин определяется максимальной частотой считывания

0 сигнала датчика изображения 1. Величина Тн мин выбирается из условия UM Do при Ем Емакс, Тн-Тн мин, где ЕМакс максималь- ная возможная освещенность Помимо этого, при Ем Емакс для того, чтобы не

5 допустить насыщения сигнала при его накоплении, необходимо контролировать соблюдение следующего соотношения между временными и амплитудными параметрами

Uo

Тн

(8)

Ub Тн мин Н Тсч мин Ь Трасч где UB верхний уровень входного напряжения АЦП 7.

Модифицируя неравенство (8), получа- ем

Тн мин -г-.- .. (Тсч мин Трасч). (9) UB - Uo

При начале повторного считывания сигнала датчика изображения 1 через интервал

времени АТНо относительно момента ТНт общее время накопления сигнала будет равно Тно и в соответствии с выражением (3) при постоянной в течение интервала накопления освещенности Ем

им Ем-Тно и0,(10)

т.е. амплитуда максимального сигнала датчика изображения 1 при повторном считывании будет стабилизирована на оптимальном уровне Uo независимо от величины максимальной освещенности Ем.

Ввод отсчетов сигнала со стабилизированной таким образом амплитудой в ЭВМ вычислительного устройства 8 производится следующим образом.

55 Для инициации процесса ввода в вычислительном устройстве 8 (фиг.5) сигналом 2 счетчик 52 устанавливается в нулевое состояние и на информационном входе триггера 45 путем передачи кода О в регистр 43

состояния устанавливается низкий уровень напряжения. При поступлении на тактовый вход этого триггера импульса начала считывания с третьего входа синхронизации 16 вычислительного устройства 8 он переключается в нулевое состояние и низким уровнем сигнала с прямого выхода разрешает прохождение импульсов конца преобразования с первого входа синхронизации 20 через элемент 2ИЛИ 50 на вход записи ОЗУ 53 и далее через элемент 2И 51 на вход выборки этого же ОЗУ (фиг.7). Одновременная подача сигналов низкого уровня на входы управления приводит к записи в ОЗУ 53 отсчетов сигнала, поступающих с информационных входов 19 вычислительного устройства 8. Задним фронтом импульса выборки после окончания записи адрес, формируемой счетчиком 52, автоматически увеличивается на единицу,

В конце интервала ввода задним фронтом импульса окончания считывания, поступающего с второго входа синхронизации 15 через элемент НЕ 47 на тактовый вход триггера 48, последний переключается в нулевое состояние и устанавливает высокий уровень сигнала на входе передатчика 49, После обнаружения появления сигнала высокого уровня на входе этого передатчика путем циклического опроса сигналом М ЭВМ вычислительного устройства 8 передачей кода 1 в регистр состояния 43 триггер 45 устанавливается в единичное состояние и высоким уровнем сигнала с его прямого выхода блокируется прохождение сигналов низкого уровня на вход записи и выборки ОЗУ 53. Процесс записи отсчетов сигнала в ОЗУ 53 при этом завершается.

Запись и считывание отсчетов максимального сигнала из регистра 55 производится указанным способом. На этом этапе работы устройства стабилизации величина максимального сигнала, считанная из регистра 55, используется для контроля точности стабилизации. Так, при нахождении величины максимального сигнала UM в зоне допуска U0 - А.иДоп UM U0 - АиДОп ЭВМ вычислительного устройства 8 осуществляет считывание отсчетов сигнала из ОЗУ 53 и передачу их на выход вычислительного устройства, например, на экран графического дисплея или в центральную ЭВМ. В противном случае ЭВМ выдает сообщение об ошибке стабилизации, которая мбжет быть связана, например, с неисправностью элементов устройства стабилизации или с непредусмотренным изменением максимальной освещенности на интервале накопления сигнала.

Считывание информации из ОЗУ 53 в оперативную память ЭВМ вычислительного устройства 8 производится с помощью импульса Is после установки счетчика 52 в исходное состояние сигналом 2,

Для реализации описанного режима работы устройства стабилизации амплитуды видеосигнала после его выключения или при резком изменении освещенности ЭВМ

вычислительного устройства 8 должна работать в соответствии с алгоритмом, приведенным на фиг.6. Программа, реализующая данный алгоритм, может быть размещена в постоянной памяти ЭВМ вычислительного

устройства 8 вместе с параметрами Тн.мин, ТСч мин, Трасч, TL T2, U0, ДУдоп, которые предварительно определяются экспериментально или расчетным путем.

Таким образом, введение в состав предлатаемого устройства фотодиодного датчика изображения 1 позволяет осуществить неразрушающее считывание сигнала в процессе его накопления и получить при этом инфоомацию о величине максимального

сигнала ФДИ 1, а значит, и о величине максимальной освещенности данного датчика. Неразрушающее считывание сигнала в ФДИ 1 позволяет продолжить его накопление после считывания и исключить, таким

образом, потери времени на повторное накопление сигнала в аналогичных приемниках с разрушающим считыванием. Введение коммутатора 6 позволяет измерять амплитуду максимального сигнала

ФДИ 1 путем подключения выхода пмкового детектора 5 к входу АЦП 7 с минимальной задержкой после окончания считывания сигнала этого датчика, Введение управляемого тактового генератора 3 позволяет ускорить считывание сигнала на этапе первоначальной оценки максимальной освещенности и уменьшить, таким образом, интервал времени, необходимый для получения такой оценки.

Включение формирователя импульса начала считывания 9 позволяет сформировать интервалы минимального Тн мин и дополнительного ДТно времени накопления и, наконец, введение элемента 2И 10 позволяет запускать формирователь импульсов начала считывания 9 как одновременно с началом накопления сигнала в ФДИ 1 при формировании сигнала Тн.мин, так и в процессе накопления при формировании интервала ЛТно.

Введение перечисленных элементов в состав устройства стабилизации амплитуды видеосигнала позволяет за счет накопления сигнала ФДИ 1 в течение интервала Тн мин.

последующего его неразрушающего считывания с максимальной скоростью за время ТСч мин и измерения максимальной амплитуды UMI, оценить величину максимальной освещенности Ем по формуле () рассчитать величину оптимального времени накопления Тно по формуле (3) и дополнительного интервала времени накопления АТно - по формуле (6), сформировать интервал АТНо и считать сигнал ФДИ 1 после окончания этого интервала Поскольку величина ТНо рассчитывалась исходя из условия нахождения максимального сигнала ФДИ 1 в окрестности оптимального уровня U0, его амплитуда будет стабилизирована на этом уровне независимо отуровня максимальной освещенности в течение одного интервала накопления, т.е. с максимально возможным быстродействием

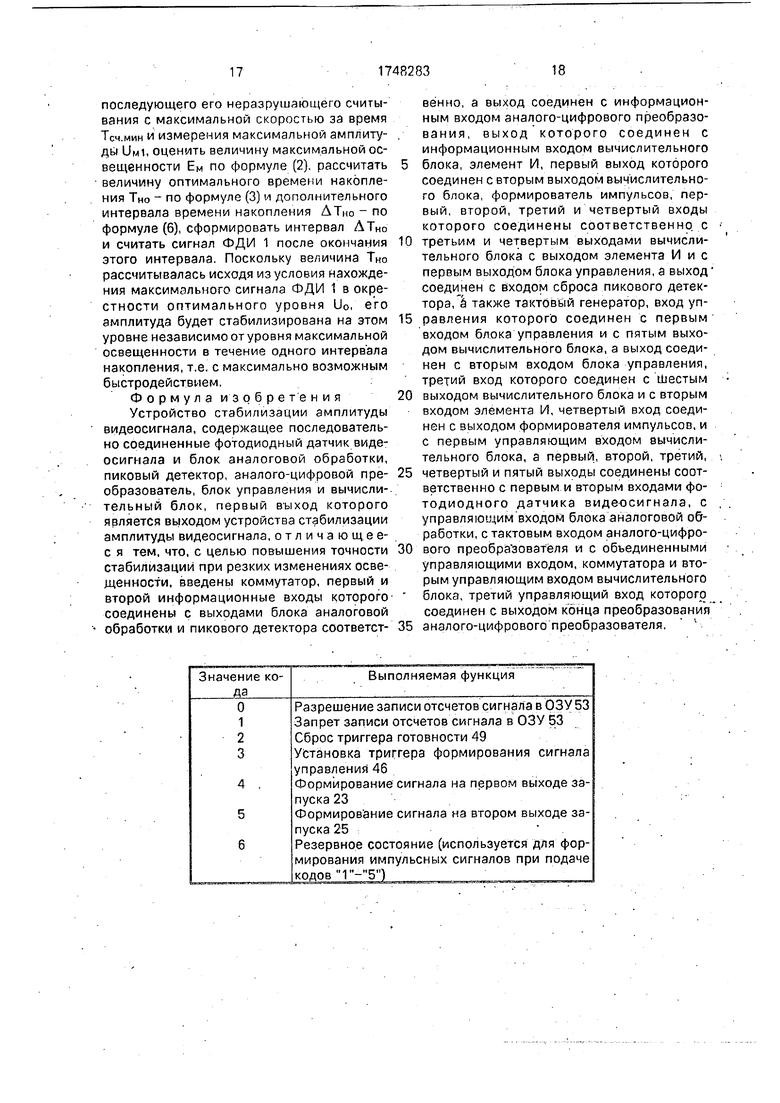

Формула изобретения

Устройство стабилизации амплитуды видеосигнала, содержащее последовательно соединенные фотодиодный датчик видеосигнала и блок аналоговой обработки, пиковый детектор, аналого-цифровой пре- образователь, блок управления и вычислительный блок, первый выход которого является выходом устройства стабилизации амплитуды видеосигнала, отличающее- с я тем, что, с целью повышения точности стабилизации при резких изменениях освещенности, введены коммутатор, первый и второй информационные входы которого соединены с выходами блока аналоговой обработки и пикового детектора соответст-

Значение кода

Разрешение записи отсчетов сигнала в ОЗУ 53 Запрет записи отсчетов сигнала в ОЗУ 53 Сброс триггера готовности 49 Установка триггера формирования сигнала управления 46

Формирование сигнала на первом выходе запуска 23

Формирование сигнала на втором выходе запуска 25

Резервное состояние (используется для формирования импульсных сигналов при подаче кодов )

венно, а выход соединен с информационным входом аналого-цифрового преобразования, выход которого соединен с информационным входом вычислительного блока, элемент И, первый выход которого соединен с вторым выходом вычислительного блока формирователь импульсов, первый второй, третий и четвертый входы которого соединены соответственно с третьим и четвертым выходами вычислительного блока с выходом элемента И и с первым выходом блока управления, а выход соединен с входом сброса пикового детектора, а также тактовый генератор, вход управления которого соединен с первым входом блока управления и с пятым выходом вычислительного блока, а выход соединен с вторым входом блока управления, третий вход которого соединен с Шестым выходом вычислительного блока и с вторым входом элемента И, четвертый вход соединен с выходом формирователя импульсов, и с первым управляющим входом вычислительного блока, а первый, второй, третий, четвертый и пятый выходы соединены соответственно с первым и вторым входами фотодиодного датчика видеосигнала, с управляющим входом блока аналоговой обработки, с тактовым входом аналого-цифрового преобра зователя и с объединенными управляющими входом, коммутатора и вторым управляющим входом вычислительного блока, третий управляющий вход которого соединен с выходом конца преобразования аналого-цифрового преобразователя v

Выполняемая функция

+ fcM

S.t/Ј4/t/frf

о

Фиг. 2

+Ј

фиг. 4

t 20 i

ПЗУ

ОЗУ

К8Ы8

н

к ввод,

4-1

1ч

L

Фаг.$

4-2

36

2Z

J

( Начало

Передам коды, Z, Г6 регистр 43

±

Записать число NT. мин. $ формирователь 9

±

Передать ков У В регистр 43

дсг

Принять число ifMJ из регистра ff

Рассчитать ёеличину оптимального бремени накопления Тио и приращения времени дТно

±

Записать уисло &Нгё формирователь ff

i

Передать коды % 0 о регистр 45. Обнулить счетчик 52.

Флаг

готоб ости (прием м1К.43)устаноо- ен

да

Принять число UM из регистра 85

{конец, ) Фиг. 6

нет

| Устройство стабилизации амплитуды видеосигнала | 1987 |

|

SU1443207A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-07-15—Публикация

1989-11-03—Подача