а

о о

fc

| название | год | авторы | номер документа |

|---|---|---|---|

| СЕЛЕКТОР ИМПУЛЬСОВ | 1992 |

|

RU2010423C1 |

| Селектор импульсов | 1988 |

|

SU1598140A1 |

| АНАЛИЗАТОР СПЕКТРА | 1992 |

|

RU2054682C1 |

| СПОСОБ ГЕОЭЛЕКТРОРАЗВЕДКИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2006886C1 |

| МНОГОКАНАЛЬНАЯ АКУСТИКО-ЭМИССИОННАЯ СИСТЕМА ДИАГНОСТИКИ КОНСТРУКЦИЙ | 2017 |

|

RU2664795C1 |

| СПОСОБ ДИАГНОСТИРОВАНИЯ МЕТАЛЛИЧЕСКИХ КОНСТРУКЦИЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2339938C1 |

| УСТРОЙСТВО ДЛЯ ВОЗБУЖДЕНИЯ УДАРНЫХ ИМПУЛЬСОВ | 1993 |

|

RU2019795C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАМЕТРОВ | 1990 |

|

RU2062502C1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| СИСТЕМА СПУТНИКОВОЙ СВЯЗИ | 2004 |

|

RU2279762C2 |

Изобретение относится к импульсной технике и может быть использовано для выделения импульсных периодических сигналов из помех Селектор импульсов содержит аналого-цифровой преобразователь 1 коммутаторы 2 5 и 10, блок 3 выбора наименьшего значения, ключевой блок 4, блок б задержки таймер 7 источник 8 регулируемого опорного уровня, компаратор 9, шину 11 установки количества импульсных последовательностей, шину 12 установки времени задержки шину 13 тактовых импульсов, шину 14 запуска устройства, шину 15 запуска АЦП сигнальную шину 16 выходную шину 17 Уменьшение искажений формы импульсов позволяет повысить точность селекции 5 ил

Фиг.1

Изобретение относится к импульсной технике и может быть использовано для выделения импульсных периодических сигналов из помех.

Известно устройство селекции импульсов, состоящее из п параллельно соединенных линий задержки и схемы совпадения п импульсов,

Основным недостатком данного устройства является ограничение, накладываемое на форму входных сигналов схемой совпадения,

Известно также устройство накопления сигнала (рециркулятор), содержащее сумматор, устройство согласования коэффициента передачи и устройство задержки.

Основными недостатками этого устройства являются длительность процесса устранения помех из-за необходимости проведения многих циклов суммирования сигналов для достижения приемлимого отношения между уровнями полезных сигналов и помех, а также невозможность работы устройства при изменении периода следования сигнала.

Наиболее близким к предлагаемому по технической сущности является селектор импульсов, содержащий АЦП, два коммутатора, устройство выбора наименьшего значения сигнала, ключевое устройство, устройство задержки, таймер.

Основным недостатком известного устройства является высокое требование к стабильности временного расположения импульсов в последовательностях. Даже небольшие временные смещения импульсов друг относительно друга в импульсных последовательностях (что имеет место, например, в радиолокации, когда интервалы времени между периодическими посылками сигнала в направлении быстро движущейся цели и откликами от неё изменяются) или незначительные вариации периода Т (в пределах нескольких процентов от Т) повторения принимаемого сигнала приводят к искажению формы компонент принимаемого сигнала.

Цель изобретения - повышение точности селекции путем уменьшения искажений формы импульсов.

Сущность изобретения заключается в том, что в селектор импульсов, содержащий аналого-цифровой преобразователь (АЦП), сигнальный вход которого соединен с сигнальной шиной, а выход - с входом первого коммутатора, управляющий вход которого соединен с управляющим входом второго коммутатора и первым выходом таймера, а первый выход - с первым входом блока выбора наименьшего значения, второй вход

которого соединен с выходом блока задер жки, а выход - с первым входом второго коммутатора, второй вход которого соединен с вторым выходом первого коммутатора, причем первый вход таймера соединен с шиной запуска устройства, второй вход - с шиной установки количества импульсных последовательностей, третий вход - с шиной тактовых импульсов, четвертый вход - с

0 шиной установки времени задержки и первым входом блока задержки, второй вход которого соединен с входом запуска аналого-цифрового преобразователя и шиной запуска аналого-цифрового преобразователя,

5 причем второй вход таймера соединен с управляющим входом ключевого блока, выход которого соединен с выходной шиной, дополнительно введены компаратор, третий коммутатор и источник регулируемого опор0 ного уровня, выход которого соединен с первым входом компаратора, второй вход которого соединен с выходом второго коммутатора и первым входом третьего коммутатора, а выход - с первым управляющим

5 входом третьего коммутатора, второй управляющий вход которого соединен с первым выходом таймера, второй вход - с первым выходом первого коммутатора, а выход - с сигнальными входами блока за0 держки и ключевого блока.

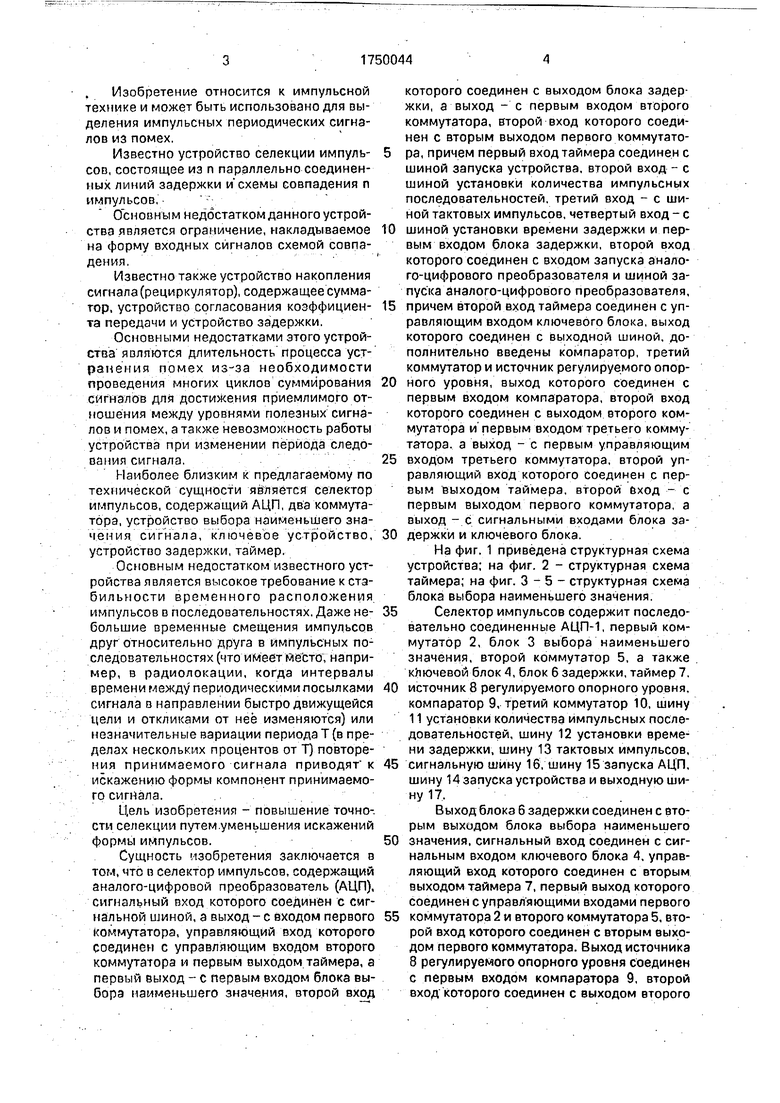

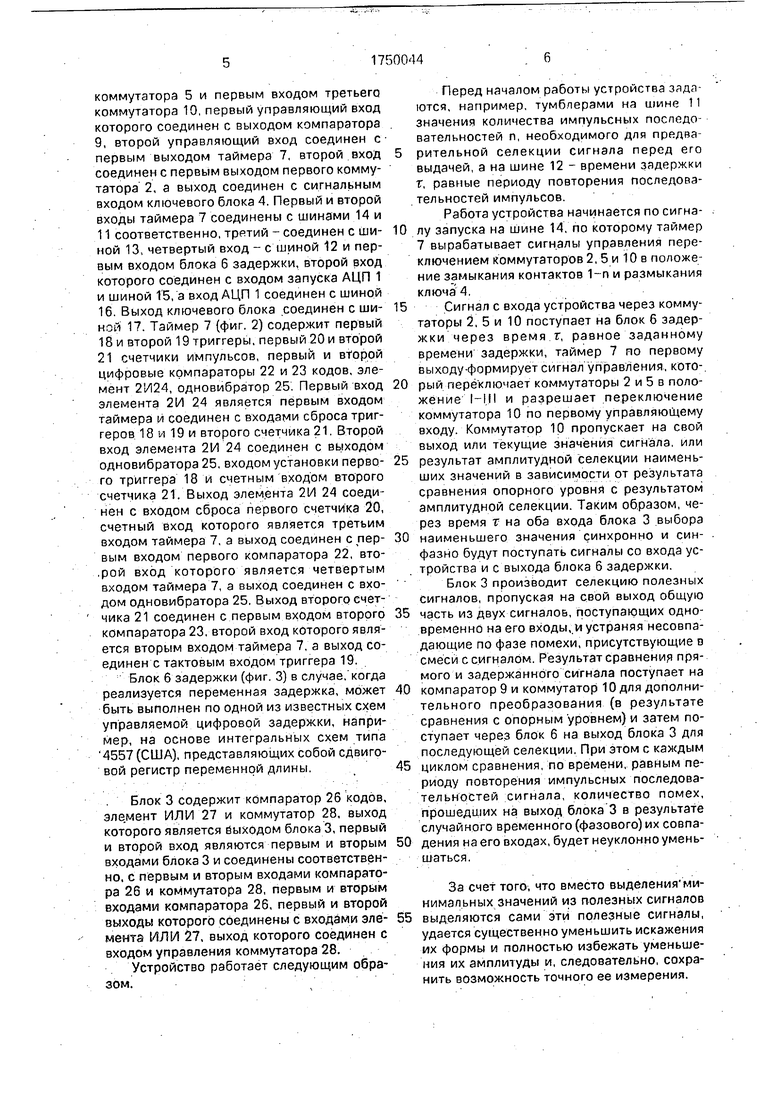

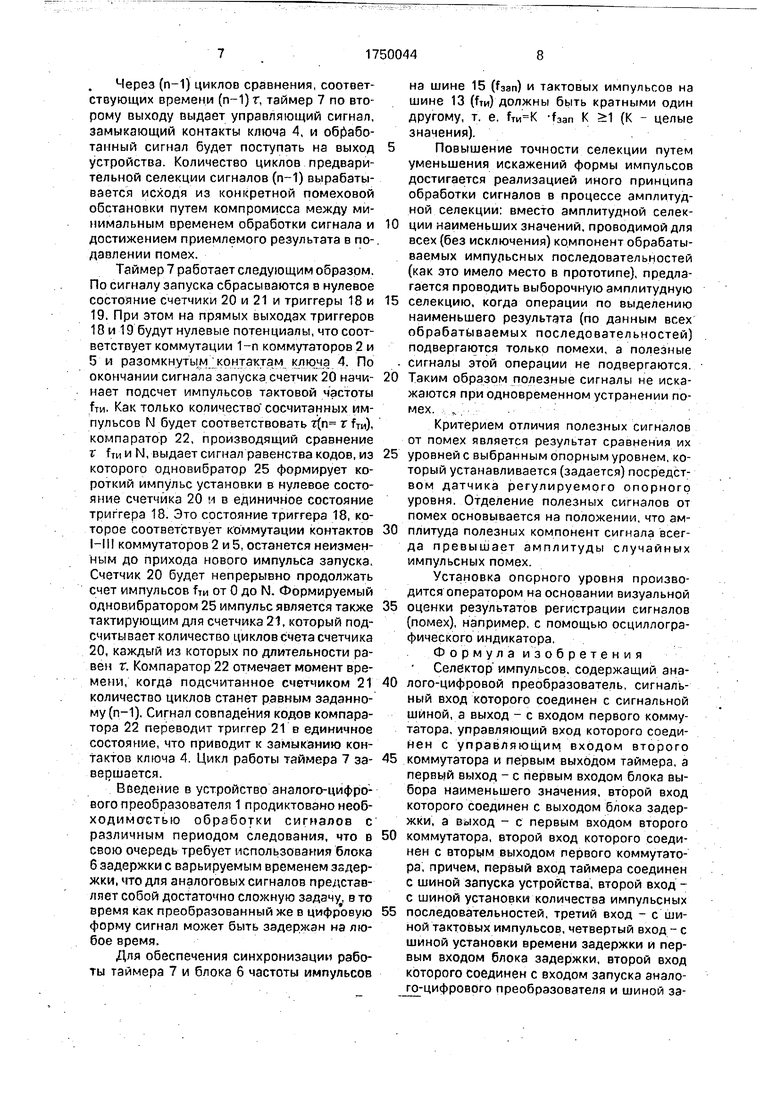

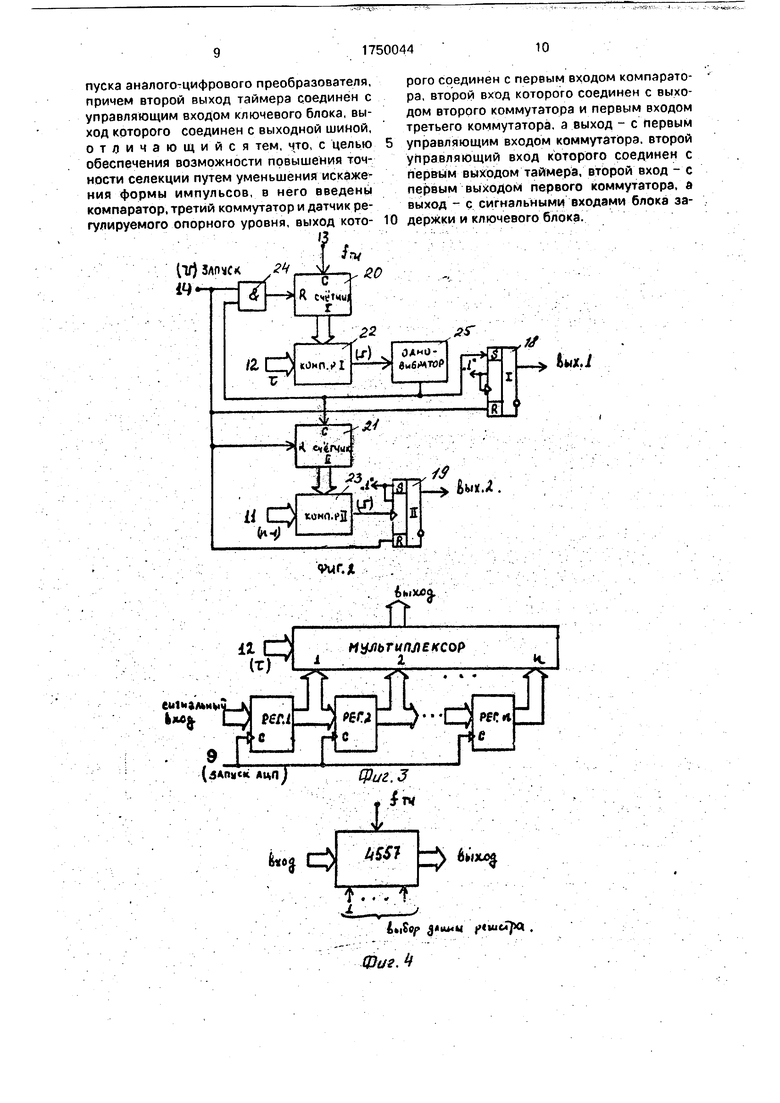

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - структурная схема таймера; на фиг. 3 - 5 - структурная схема блока выбора наименьшего значения.

5 Селектор импульсов содержит последовательно соединенные АЦП-1, первый коммутатор 2, блок 3 выбора наименьшего значения, второй коммутатор 5, а также ключевой блок 4, блок б задержки, таймер 7,

0 источник 8 регулируемого опорного уровня, компаратор 9, третий коммутатор 10, шину 11 установки количества импульсных последовательностей, шину 12 установки времени задержки, шину 13 тактовых импульсов,

5 сигнальную шину 16, шину 15 запуска АЦП, шину 14 запуска устройства и выходную шину 17.

Выход блока 6 задержки соединен с вторым выходом блока выбора наименьшего

0 значения, сигнальный вход соединен с сигнальным входом ключевого блока 4. управляющий вход которого соединен с вторым выходом таймера 7, первый выход которого соединен с управляющими входами первого

5 коммутатора 2 и второго коммутатора 5, второй вход которого соединен с вторым выходом первого коммутатора. Выход источника 8 регулируемого опорного уровня соединен с первым входом компаратора 9, второй вход которого соединен с выходом второго

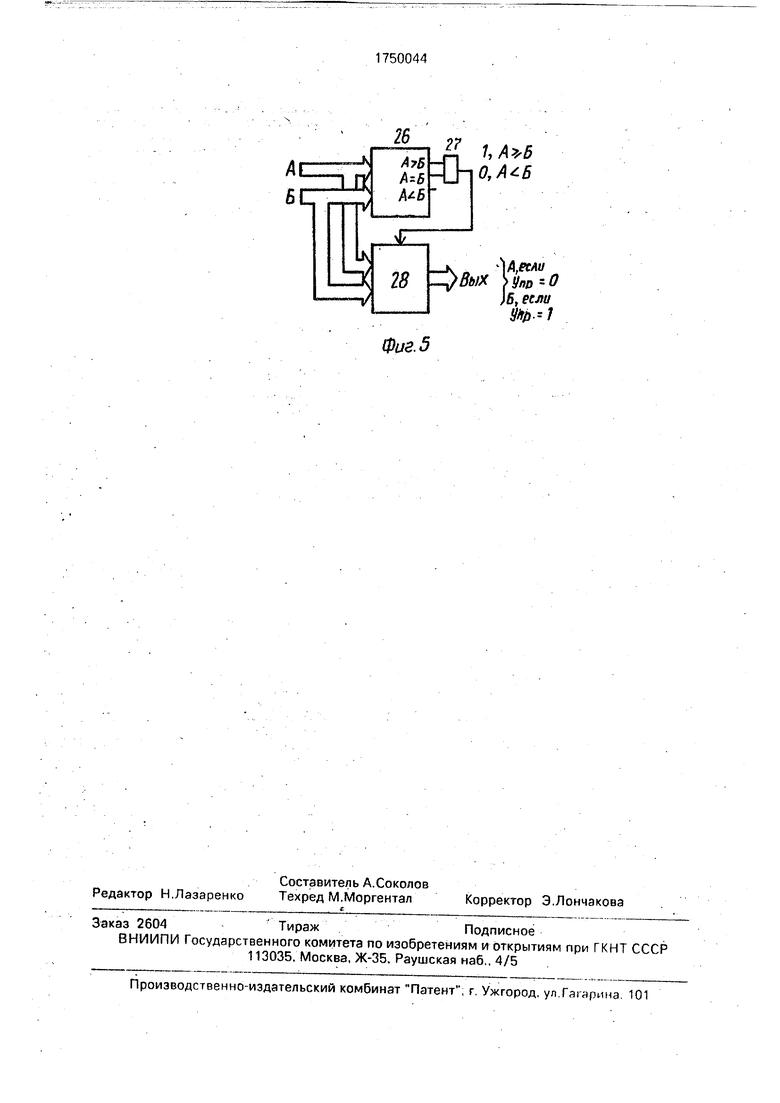

коммутатора 5 и первым входом третьего коммутатора 10, первый управляющий вход которого соединен с выходом компаратора 9, второй управляющий вход соединен с первым выходом таймера 7, второй вход соединен с первым выходом первого коммутатора 2, а выход соединен с сигнальным входом ключевого блока 4. Первый и второй входы таймера 7 соединены с шинами 14 и 11 соответственно, третий - соединен с шиной 13, четвертый вход - с шиной 12 и первым входом блока 6 задержки, второй вход которого соединен с входом запуска АЦП 1 и шиной 15, а вход АЦП 1 соединен с шиной 16. Выход ключевого блока соединен с шиной 17. Таймер 7 (фиг. 2) содержит первый 18 и второй 19 триггеры, первый 20 и второй 21 счетчики импульсов, первый и второй цифровые компараторы 22 и 23 кодов, элемент 2 И24, одновибратор 25. Первый вход элемента 2И 24 является первым входом таймера и соединен с входами сброса триггеров 18 и 19 и второго счетчика 21. Второй вход элемента 2И 24 соединен с выходом одновибратора 25,входом установки первого триггера 18 и счетным входом второго счетчика 21. Выход элемента 2И 24 соединен с входом сброса первого счетчика 20, счетный вход которого является третьим входом таймера 7, а выход соединен с первым входом первого компаратора 22, вто.рой вход которого является четвертым входом таймера 7, а выход соединен с входом одновибратора 25. Выход второго счетчика 21 соединен с первым входом второго компаратора 23, второй вход которого является вторым входом таймера 7, а выход соединен с тактовым входом триггера 19.

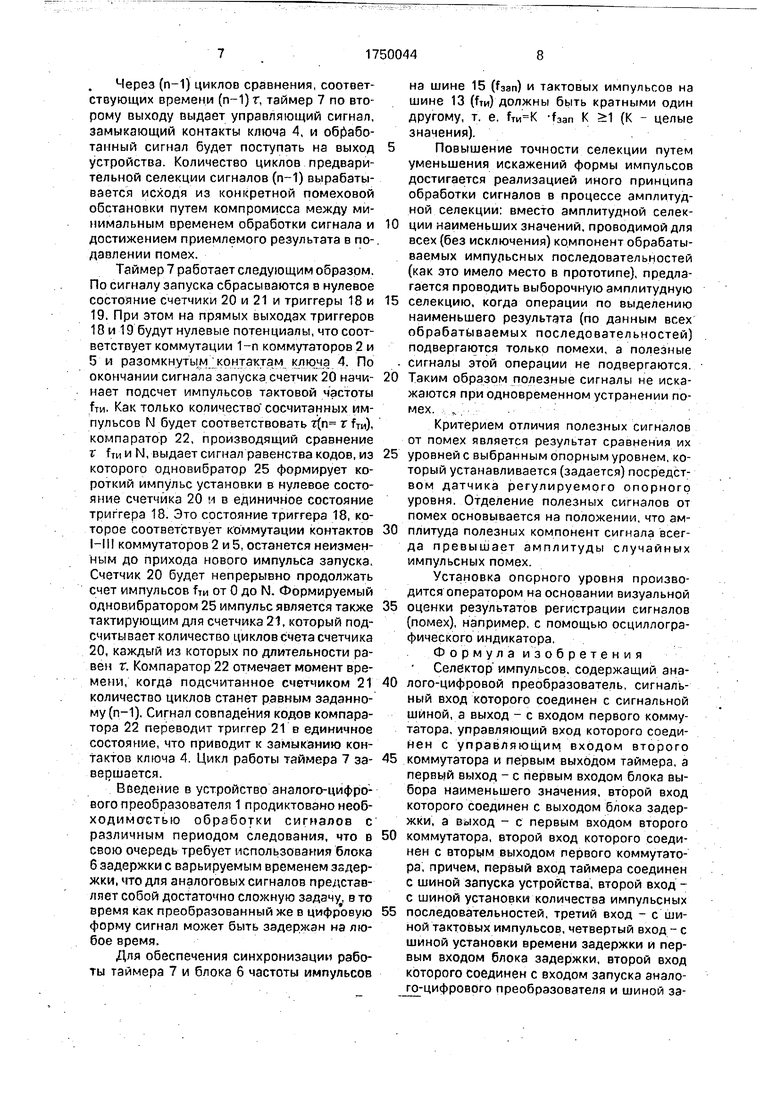

Блок 6 задержки (фиг. 3) в случае, когда реализуется переменная задержка, может быть выполнен по одной из известных схем управляемой цифровой задержки, например, на основе интегральных схем типа

4557 (США), представляющих собой сдвиговой регистр переменной длины.

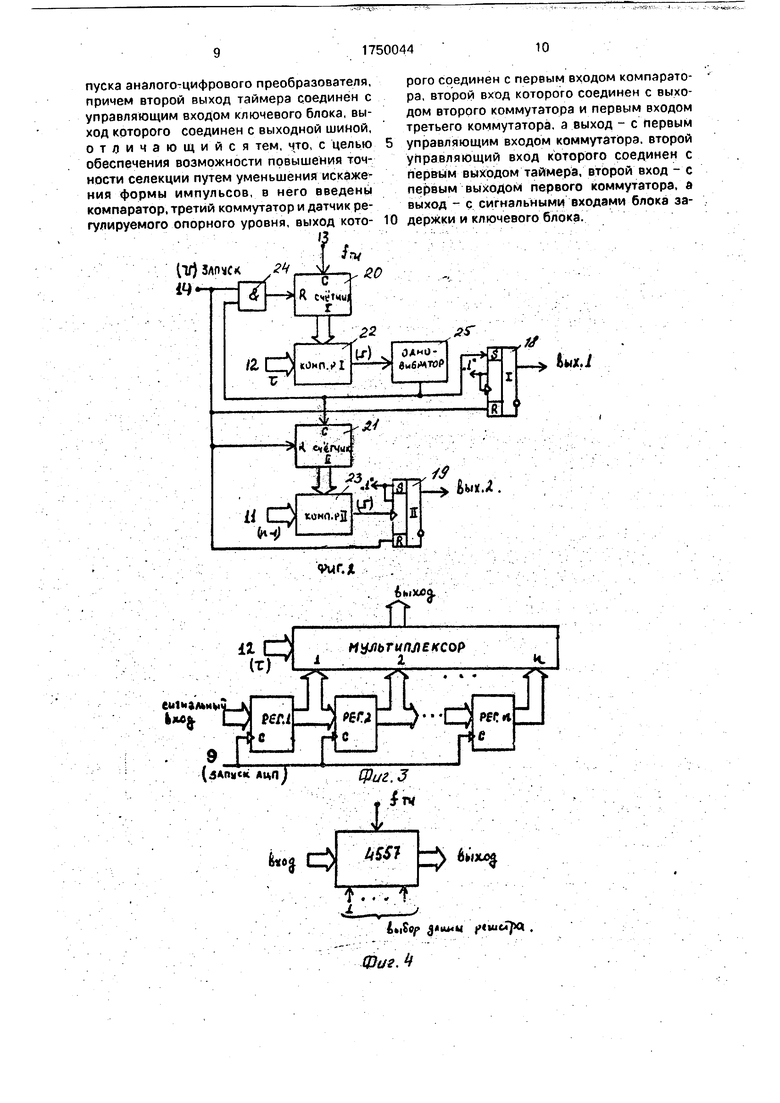

Блок 3 содержит компаратор 26 кодов, элемент ИЛИ 27 и коммутатор 28, выход которого является выходом блока 3, первый и второй вход являются первым и вторым входами блока 3 и соединены соответственно, с первым и вторым входами компаратора 26 и коммутатора 28, первым и вторым входами компаратора 26, первый и второй выходы которого соединены с входами элемента ИЛИ 27, выход которого соединен с входом управления коммутатора 28.

Устройство работает следующим образом.

Перед началом работы устройства задаются, например, тумбперами на шине 11 значения количества импульсных последовательностей п, необходимого для предва- 5 рительной селекции сигнала перед его выдачей, а на шине 12 - времени задержки т, равные периоду повторения последовательностей импульсов.

Работа устройства начинается по сигна0 лу запуска на шине 14, по которому таймер 7 вырабатывает сигналы управления переключением коммутаторов 2, 5 и 10 в положение замыкания контактов 1-п и размыкания ключа 4.

5 Сигнал с входа устройства через коммутаторы 2, 5 и 10 поступает на блок 6 задержки через время г, равное заданному времени задержки, таймер 7 по первому выходу-формирует сигнал управления, кото0 рый переключает коммутаторы 2 и 5 в положение I-III и разрешает переключение коммутатора 10 по первому управляющему входу. Коммутатор 10 пропускает на свой выход или текущие значения сигнала, или

5 результат амплитудной селекции наименьших значений в зависимости от результата сравнения опорного уровня с результатом амплитудной селекции. Таким образом, через время т на оба входа блока 3 выбора

0 наименьшего значения синхронно и син- фазно будут поступать сигналы со входа устройства и с выхода блока 6 задержки.

Блок 3 производит селекцию полезных сигналов, пропуская на свой выход общую

5 часть из двух сигналов, поступающих одновременно на его входы, и устраняя несовпадающие по фазе помехи, присутствующие в смеси с сигналом. Результат сравнения прямого и задержанного сигнала поступает на

0 компаратор 9 и коммутатор 10 для дополнительного преобразования (в результате сравнения с опорным уровнем) и затем поступает через блок 6 на выход блока 3 для последующей селекции, При этом с

5 циклом сравнения, по времени, равным периоду повторения импульсных последовательностей сигнала, количество помех, прошедших на выход блока 3 в результате случайного временного (фазового) их совпа0 дения на его входах, будет неуклонно уменьшаться.

За счет того, что вместо выделения минимальных значений из полезных сигналов 5 выделяются сами эти полезные сигналы, удается существенно уменьшить искажения их формы и полностью избежать уменьшения их амплитуды и, следовательно, сохранить возможность точного ее измерения.

Через (п-1) циклов сравнения, соответствующих времени (п-1) г, таймер 7 по второму выходу выдает управляющий сигнал, замыкающий контакты ключа 4, и обработанный сигнал будет поступать на выход устройства. Количество циклов предварительной селекции сигналов (п-1) вырабатывается исходя из конкретной помеховой обстановки путем компромисса между минимальным временем обработки сигнала и достижением приемлемого результата в подавлении помех.

Таймер 7 работает следующим образом. По сигналу запуска сбрасываются в нулевое состояние счетчики 20 и 21 и триггеры 18 и

20,каждый из которых по длительности равен т. Компаратор 22 отмечает момент времени, когда подсчитанное счетчиком 21 количество циклов станет равным заданному (п-1). Сигнал совпадения кодов компаратора 22 переводит триггер 21 в единичное состояние, что приводит к замыканию контактов ключа 4. Цикл работы таймера 7 завершается.

Введение в устройство аналого-цифрового преобразователя 1 продиктовано необходимостью обработки сигналов с различным периодом следования, что в свою очередь требует использования блока б задержки с варьируемым временем задержки, что для аналоговых сигналов представляет собой достаточно сложную задачу, в то время как преобразованный же в цифровую форму сигнал может быть задержан на любое время.

Для обеспечения синхронизации работы таймера 7 и блока 6 частоты импульсов

на шине 15 (faan) и тактовых импульсов на шине 13 (f™) должны быть кратными один другому, т. е. -faan К 1 (К - целые значения).

Повышение точности селекции путем

уменьшения искажений формы импульсов достигается реализацией иного принципа обработки сигналов в процессе амплитудной селекции: вместо амплитудной селек0 ции наименьших значений, проводимой для всех (без исключения) компонент обрабатываемых импульсных последовательностей (как это имело место в прототипе), предлагается проводить выборочную амплитудную

5 селекцию, когда операции по выделению

наименьшего результата (по данным всех

обрабатываемых последовательностей)

подвергаются только помехи, а полезные

- сигналы этой операции не подвергаются

0 Таким образом полезные сигналы не искажаются при одновременном устранении помех. ..

Критерием отличия полезных сигналов от помех является результат сравнения их

5 уровней с выбранным опорным уровнем, который устанавливается(задается) посредством датчика регулируемого опорного уровня. Отделение полезных сигналов от помех основывается на положении, что ам0 плитуда полезных компонент сигнала всегда превышает амплитуды случайных импульсных помех.

Установка опорного уровня производится оператором на основании визуальной

5 оценки результатов регистрации сигналов (помех), например, с помощью осциллогра- фического индикатора.

Формула изобретения Селектор импульсов, содержащий ана0 лого-цифровой преобразователь, сигнальный вход которого соединен с сигнальной шиной, а выход - с входом первого коммутатора, управляющий вход которого соединен с управляющим входом второго

5 коммутатора и первым выходом таймера, а первый выход - с первым входом блока выбора наименьшего значения, второй вход которого соединен с выходом блока задержки, а выход - с первым входом второго

0 коммутатора, второй вход которого соединен с вторым выходом первого коммутатора, причем, первый вход таймера соединен с шиной запуска устройства, второй вход - с шиной установки количества импульсных

5 последовательностей, третий вход - с шиной тактовых импульсов, четвертый вход - с шиной установки времени задержки и первым входом блока задержки, второй вход которого соединен с входом запуска аналого-цифрового преобразователя и шиной запуска аналого-цифрового преобразователя, причем второй выход таймера соединен с управляющим входом ключевого блока, выход которого соединен с выходной шиной, отличающийся тем, что, с целью обеспечения возможности повышения точности селекции путем уменьшения искажения формы импульсов, в него введены компаратор, третий коммутатор и датчик регулируемого опорного уровня, выход кото(V) ЗЛП« «

М

1

fn

Ј

д

&CZ) тГ

izdi

(гГ

ешмамимч

9

- r-Jtr-Jl r-d

hj РШlj per;V - dJ .

lEpJ

««ьич ftwujx

ШигЛ

0

рого соединен с первым входом компаратора, второй вход которого соединен с выходом второго коммутатора и первым входом третьего коммутатора, а выход - с первым управляющим входом коммутатора, второй управляющий вход которого соединен с первым выходом таймера, второй вход - с первым выходом первого коммутатора, д выход - с сигнальными входами блока задержки и ключевого блока.

Ј0

ssL%

НГГ

i

м

&ЫХ./

&ЫХ.4 .

&M).

ВЦ

Uv

Lb(

26

А:Б

27

Ch

1, 0,

к }А,если Z,)#WX

)5, если $50--7

Фиг. 5

| Селектор импульсов | 1979 |

|

SU785986A1 |

Авторы

Даты

1992-07-23—Публикация

1990-05-15—Подача