Фие.1

Изобретение ото ,шея к измеритель ты i р.нике и может быт ь использовано при построении цифровых вольтметров для же i них условий зн.плуатации

Целью изобретения является повышение точности преобразования в широком диапазоне рабочих температур

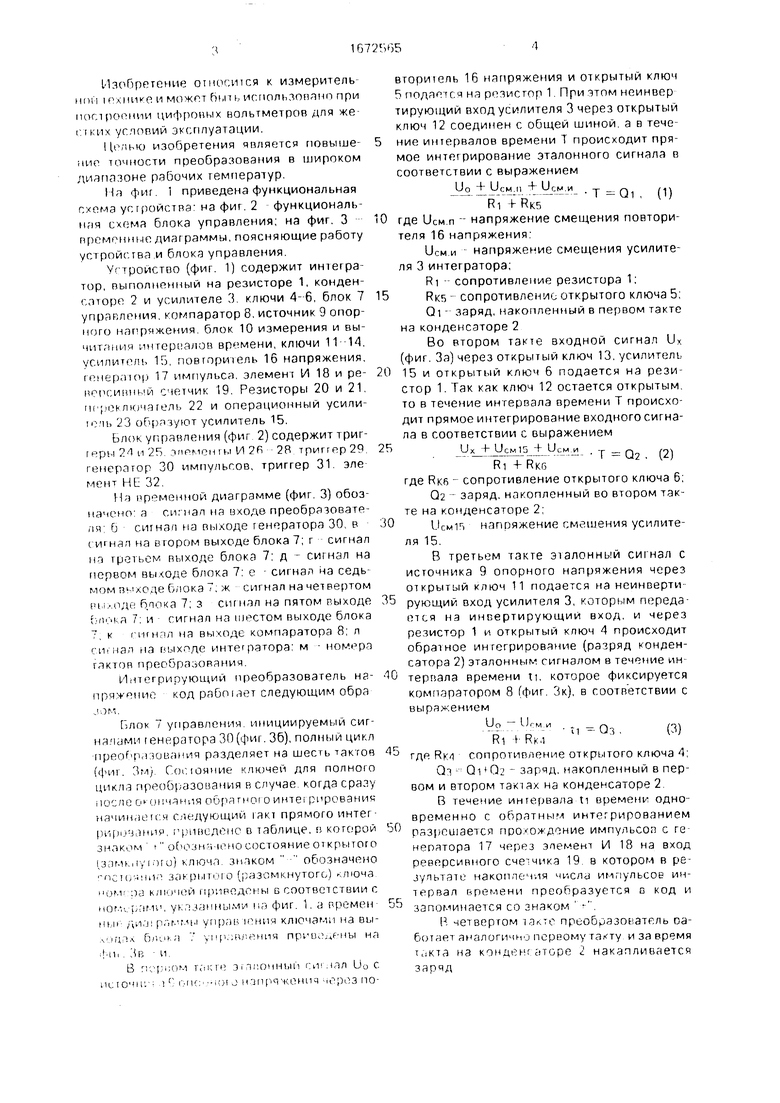

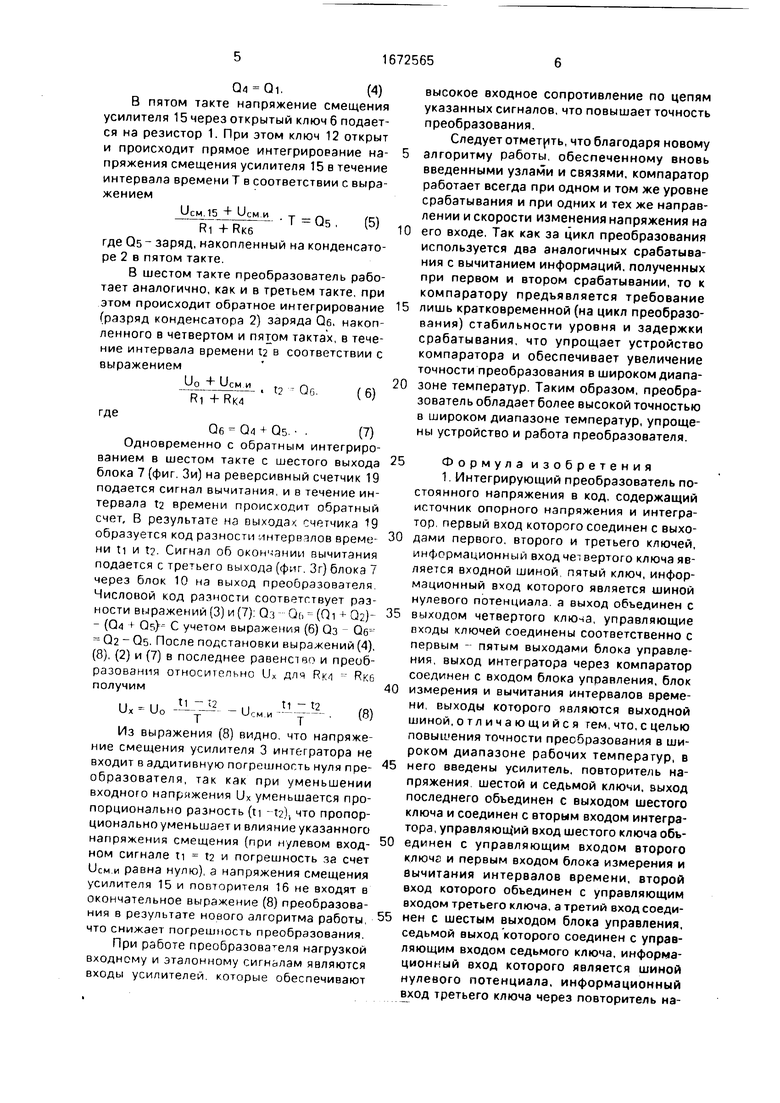

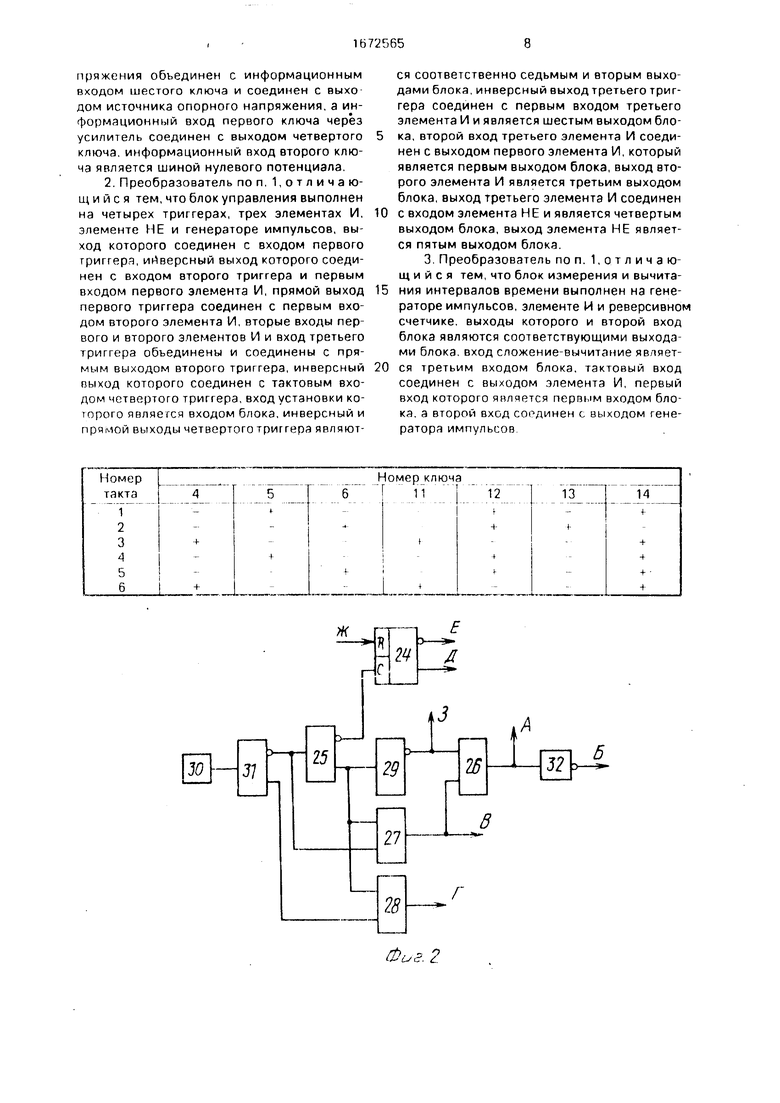

На фиг 1 приведена функциональная схема устройства на фиг 2 функциональная схема блока управления, на фиг. 3 временные диаграммы, поясняющие работу устройства и блока управления

V тройство (фиг 1) содержит интегратор, выполненный на резисторе 1, конден- -лторе 2 и усилителе 3 ключи 4-6, блок 7 управления компаратор 8, источник 9 опорного напряжения блок 10 измерения и вычитания интервалов времени, ключи 11 14 Силитрль 15 повторшель 16 напряжения, гечераюр 17 импульса элемент И 18 и ре- вощинный с (етчик 19 Резисторы 20 и 21 гь лючагель 22 и операционный усили- тр и. 23 образ/ют усилитель 15

Блок управления (фиг 2) содержит триггеры 24112е) тмемРшмИ2Р 2В триггер2с генератор 30 импульсов, триггер 31 эле мент HL 32

На временной диаграмме (фиг 3) обозначено a CLV нал на входе преобразователя 0 сигнзп на выходе генератора 30 в ( И нал на втором выходе блока 7, г сигнал in третьем выходе блока 7 д - сигнал на первом вькоде блока 7 е сигнал на седь мом Глюка 7, ж сигнал на четвертом in i ОДР бппка 7, з сигнал на пятом выходе a 7 и сигнал на шестом выходе блока к г игн 1л на выходе компаратора 8 л и ,(ал ria интегратора м номера тактов преобразования

Интегрирующий преобразователь npq+рние код рабшает следующим обра

I -JVi

Плок 7 управления инициируемый сиг- няпами генератора 30(фщ 36), полный цикл nppof na зования разделяет на шесть такгоч (фш Зм; Coi юяние пючей для полного цикча преобразования в случае когда сразу после н.чанич пира т ног о инте рирования начинаем ч с тедующии 1акт прямого интег рпрм лния .4 пвиденс в таблице, в которой знаком t ofmjH i юно состояние от крытого i з и-н ii, i )го) ключт знчком обозначено P0v, icii-pbiii i о (разомкнутого) Л1оча ом )сЗ к. приведены Б соответствии с но, и ini vb ушными IK) фиг 1 а времен nt u ди i р,.г мы упраь |рния ключами на вы- |Ц GII. г) npi Di 4f ны на

1 Hi В И

В г i on г. i и3 э i чгонныи и1 (ал Uo с LKio.. f пг л -J шпря ненич .гроз по

вторигель 16 напряжения и открытый ключ 5 под ао с чнаррзистор Приэтомнеинвер тирующий вход усилителя 3 через открытый ключ 12 соединен с общей шиной а в тече ние интервалов времени Т происходит прямое интегрирование эталонного сигнала в соответствии с выражением

U0 4- UCM п + UCM и -р ,-./,. | у, j

Hi t- КК5

где UCM n напряжение смещения повторителя 16 напряжения

UCM и напряжение смещения усилителя 3 интегратора,

RI сопротивление резистора 1, RKS - сопротивление открытого ключа 5, Q заряд, накопленный в первом такте на конденсаторе 2

Во втором такте входной сигнал Ux (фиг За) через открытый ключ 13 усилители 15 и открытый ключ 6 подается на рези стор 1 Так как ключ 1 остается открытым то в течение интервала времени Т происходит прямое интегрирование входного сигнала в соответствии с выражением

Ux +JJcMl5 -+ U см

Ri +RKG где RKB сопротивление открытого ключа 6,

Q2 заряд, накопленный во втором такте на конденсаторе 2

UCMiri напряжение смешения усилителя 15

В третьем такте эталонный сшнал с источника 9 опорного напряжения через открытый ключ 11 подается на неинверти рующий вход усилителя 3, которым переда ется нэ инвертирующий вход, и через резистор 1 и открытый ключ 4 происходит обратное ингегриоование (разряд конденсатора 2) эталонным сигналом в течение ин тервала времени ti, которое фиксируется компаратором 8 (фиг Зк), в соответствии с выражением

Uo - UrM И. ъ/п-,

(3)

Г Q2 . (2)

Ri i RM t1 ° где RM сопротивление открытого ключа 4

Ch Qi 02 - заряд, накопленный в первом и втором тактах на конденсаторе 2

В течение интервала ti времени одновременно с обратным интегрированием разрешается прохождение импульсоп с re непатора 17 через элемент И 18 на вход ррверсивного счетчика 19 в котором в ре зучьтате накоплечля числа иг1пульсов интервал времени преобразуется в код и запоминается со знаком Р четвертом прьобмазоватгль оа- ботает аналогичи j перрому гакту и за время тикта на КОНДРНГ с торе I накапливается заряд

Q4 Qi.(4)

В пятом такте напряжение смещения усилителя 15 через открытый ключ 6 подается на резистор 1. При этом ключ 12 открыт и происходит прямое интегрирование на- пряжения смещения усилителя 15 в течение интервала времени Т в соответствии с выражением

UcM.15 t UcM И т nfc

-RTTRir T Qs (5)

где Qs - заряд, накопленный на конденсаторе 2 в пятом такте.

В шестом такте преобразователь работает аналогично, как и в третьем такте, при этом происходит обратное интегрирование (разряд конденсатора 2) заряда Об, накопленного в четвертом и пятом тактах, в течение интервала времени t2 в соответствии с выражением

Uo +11сми

Ri +RK4

. t2 - QG.

(6)

где

Об QA + Qs. (7)

Одновременно с обратным интегрированием в шестом такте с шестого выхода блока 7 (фиг. Зи) на реверсивный счетчик 19 подается сигнал вычитания, и в течение интервала t2 времени происходит обратный счет, В результате на выходах счетчика 19 образуется код разности интервалов времени ti и t. Сигнал об окончании вычитания подается с третьего выхода (фиг. Зг) блока 7 через блок 10 на выход преобразователя Числовой код разности соответствует разности выражений (3) и (7): Оз- Q( -(0i + 02)- - (04 - Qs) С учетом выражения (6) Оз - Об 02 Об. После подстановки выражений (4). (8). (2) и (7) в последнее равенство и преобразования относительно Ux для - R«6 получим

II - II t1 t2 II t1 - 12,m

Ux - UrM и -- .(О)

Из выражения (8) видно, что напряжение смещения усилителя 3 интегратора не входит в аддитивную погрешность нуля преобразователя, так как при уменьшении входного напряжения Ux уменьшается пропорционально разность (ti -12). что пропорционально уменьшает и влияние указанного напряжения смещения (при нулевом входном сигнале ti t2 и погрешность за счет UCM и равна нулю), а напряжения смещения усилителя 15 и повторителя 16 не входят в окончательное выражение (8) преобразования в результате нового алгоритма работы, что снижает погрешность преобразования.

При работе преобразователя нагрузкой входному и эталонному сигналам являются входы усилителей, которые обеспечивают

5

10

15

20

25

30

35

40

45

50

55

высокое входное сопротивление по цепям указанных сигналов, что повышает точность преобразования.

Следует отметить, что благодаря новому алгоритму работы, обеспеченному вновь введенными узлами и связями, компаратор работает всегда при одном и том же уровне срабатывания и при одних и тех же направлении и скорости изменения напряжения на его входе. Так как за цикл преобразования используется два аналогичных срабатывания с вычитанием информации, полученных при первом и втором срабатывании, то к компаратору предъявляется требование лишь кратковременной (на цикл преобразования) стабильности уровня и задержки срабатывания, что упрощает устройство компаратора и обеспечивает увеличение точности преобразования в широком диапазоне температур. Таким образом, преобразователь обладает более высокой точностью в широком диапазоне температур, упрощены устройство и работа преобразователя.

Формула изобретения 1. Интегрирующий преобразователь постоянного напряжения в код, содержащий источник опорного напряжения и интегратор, первый вход которого соединен с выходами первого, второго и третьего ключей, информационный вход четвертого ключа является входной шиной, пятый ключ, информационный вход которого является шиной нулевого потенциала, а выход обьединен с выходом четвертого ключа, управляющие входы ключей соединены соответственно с первым - пятым выходами блока управления, выход интегратора через компаратор соединен с входом блока управления, блок измерения и вычитания интервалов времени, выходы которого являются выходной шиной, отличающийся гем, что, с целью повышения точности преобразования в широком диапазоне рабочих температур, в него введены усилитель, повторитель напряжения шестой и седьмой ключи, выход последнего объединен с выходом шестого ключа и соединен с вторым входом интегратора, управляющей вход шестого ключа объединен с управляющим входом второго ключа и первым входом блока измерения и вычитания интервалов времени, второй вход которого объединен с управляющим входом третьего ключа, а третий вход соединен с шестым выходом блока управления, седьмой выход которого соединен с управляющим входом седьмого ключа, информационный вход которого является шиной нулевого потенциала, информационный вход третьего ключа через повторитель напряжения объединен с информационным входом шестого ключа и соединен с выходом источника опорного напряжения, а информационный вход первого ключа через усилитель соединен с выходом четвертого ключа, информационный вход второго ключа является шиной нулевого потенциала.

2. Преобразователь по п. отличающийся тем, что блок управления выполнен на четырех триггерах, трех элементах И, элементе НЕ и генераторе импульсов, выход которого соединен с входом первого триггера, инверсный выход которого соединен с входом второго триггера и первым входом первого элемента И, прямой выход первого триггера соединен с первым входом второго элемента И, вторые входы первого и второго элементов И и вход третьего триггера объединены и соединены с прямым выходом второго триггера, инверсный выход которого соединен с тактовым входом четвертого триггера, вход установки которого является входом блока, инверсный и прямой выходы четвертого триггера являются соответственно седьмым и вторым выходами блока, инверсный выход третьего триггера соединен с первым входом третьего элемента И и является шестым выходом блока, второй вход третьего элемента И соединен с выходом первого элемента И, который является первым выходом блока, выход второго элемента И является третьим выходом блока, выход третьего элемента И соединен

с входом элемента НЕ и является четвертым выходом блока, выход элемента НЕ является пятым выходом блока.

3. Преобразователь по п. 1, о т л и ч а ю- щ и и с я тем, что блок измерения и вычитания интервалов времени выполнен на генераторе импульсов, элементе И и реверсивном счетчике, выходы которого и второй вход блока являются соответствующими выходами блока, вход сложение-вычитание является третьим входом блока, тактовый вход соединен с выходом элемента И, первый вход которого является первым входом блока, а второй вход соединен с выходом генератора импульсов

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегрирующий аналого-цифровой преобразователь | 1988 |

|

SU1681384A1 |

| Преобразователь напряжения в интервал времени | 1988 |

|

SU1649662A1 |

| Измеритель параметров комплексных сопротивлений | 1989 |

|

SU1751690A1 |

| Устройство для измерения рассогласования между углом и кодом | 1985 |

|

SU1277397A1 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1988 |

|

SU1615888A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012131C1 |

| Цифровой омметр | 1982 |

|

SU1167529A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1246376A1 |

| Низкочастотный цифровой фазометр | 1990 |

|

SU1784924A1 |

| МНОГОКАНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ СИГНАЛОВ РЕЗИСТИВНЫХ ДАТЧИКОВ ВО ВРЕМЕННОЙ ИНТЕРВАЛ | 1994 |

|

RU2097777C1 |

Изобретение относится к измерительной технике и может быть использовано в универсальных цифровых вольтметрах для преобразования постоянного напряжения в код. Цель изобретения - повышение точности преобразования в широком диапазоне рабочих температур. Это достигается тем, что в преобразователь, содержащий интегратор, выполненный на усилителе 3, резисторе 1 и конденсаторе 2, блок 7 управления, блок 10 измерения и вычитания интервалов времени, компаратор 8, источник 9 опорного напряжения, ключи 13, 14, 4, 6, 11, введены усилитель 15, повторитель 16 напряжения и ключи 5, 12. Благодаря наличию усилителя 15, повторителя 16 напряжения, системы ключей 4 - 6, 11 - 14 и совокупности связей между всеми перечисленными блоками в преобразователе обеспечивается алгоритм работы, повышающий точность преобразования в широком диапазоне температур. 2 з.п. ф-лы, 3 ил.

Е

э«Д

А

В

Г

| Прянишников В.А | |||

| Интегрирующие цифровые вольтметры постоянного тока | |||

| - Л.: Энергия, 1976, с | |||

| Способ изготовления звездочек для французской бороны-катка | 1922 |

|

SU46A1 |

| Интегрирующий преобразователь напряжение-код | 1976 |

|

SU764120A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-08-23—Публикация

1988-10-03—Подача