Изобретение относится к области вычислительной техники и предназначено для построения систем цифровой обработки сигналов.

Целью изобретения является снижение аппаратурных затрат, а также расширение функциональных возможностей за счет вычисления фильтрп 2п-го порядка.

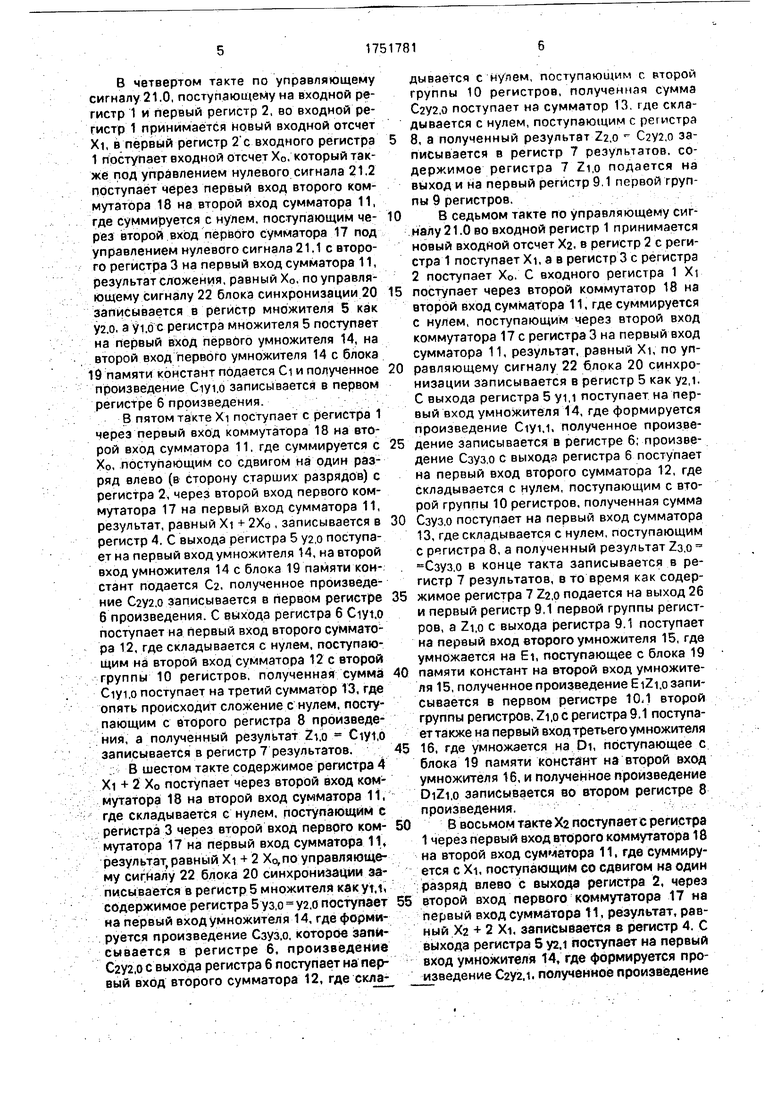

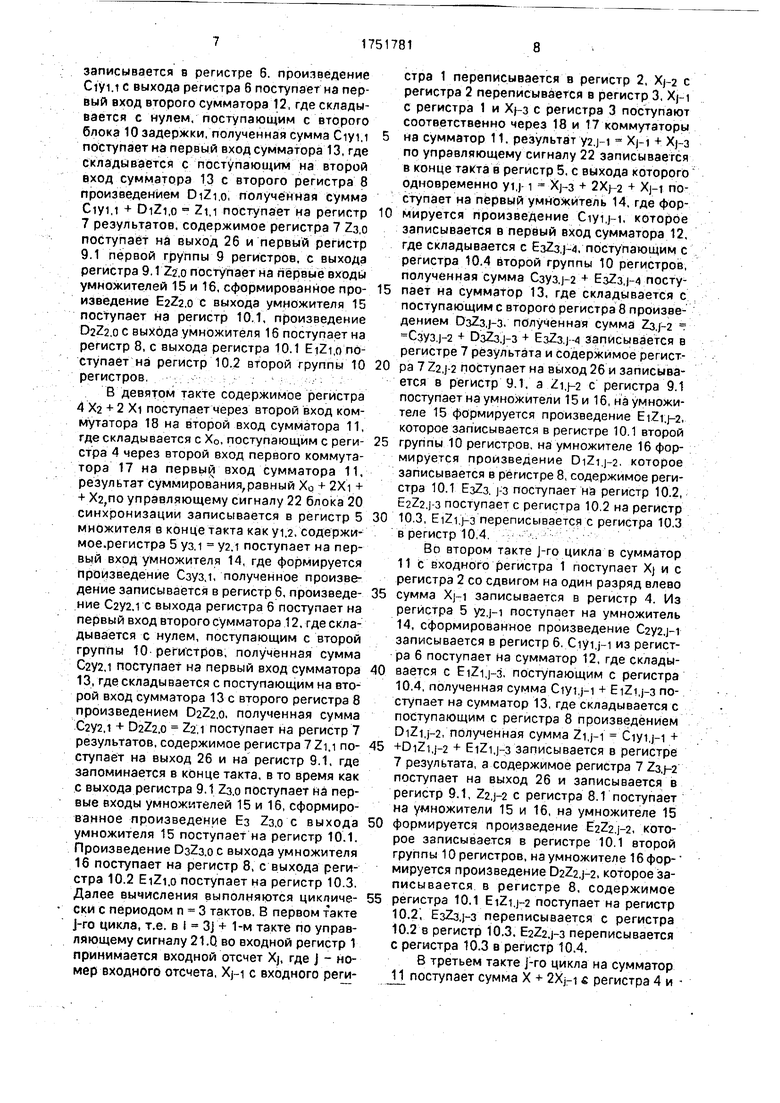

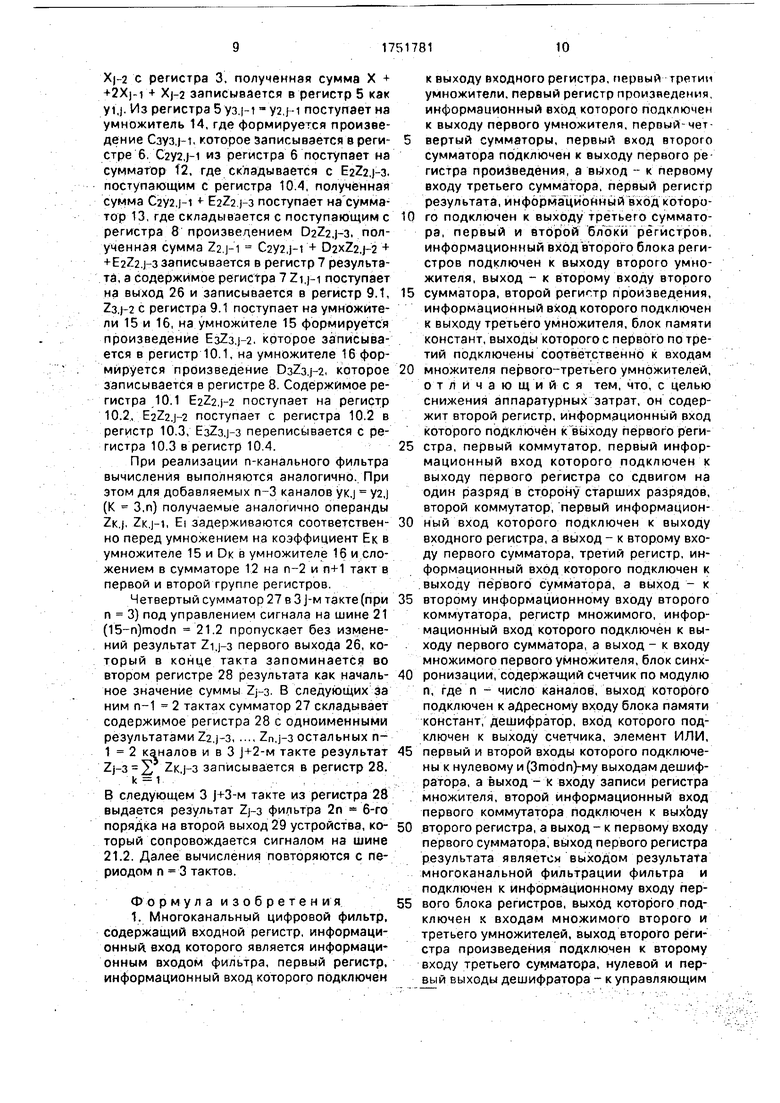

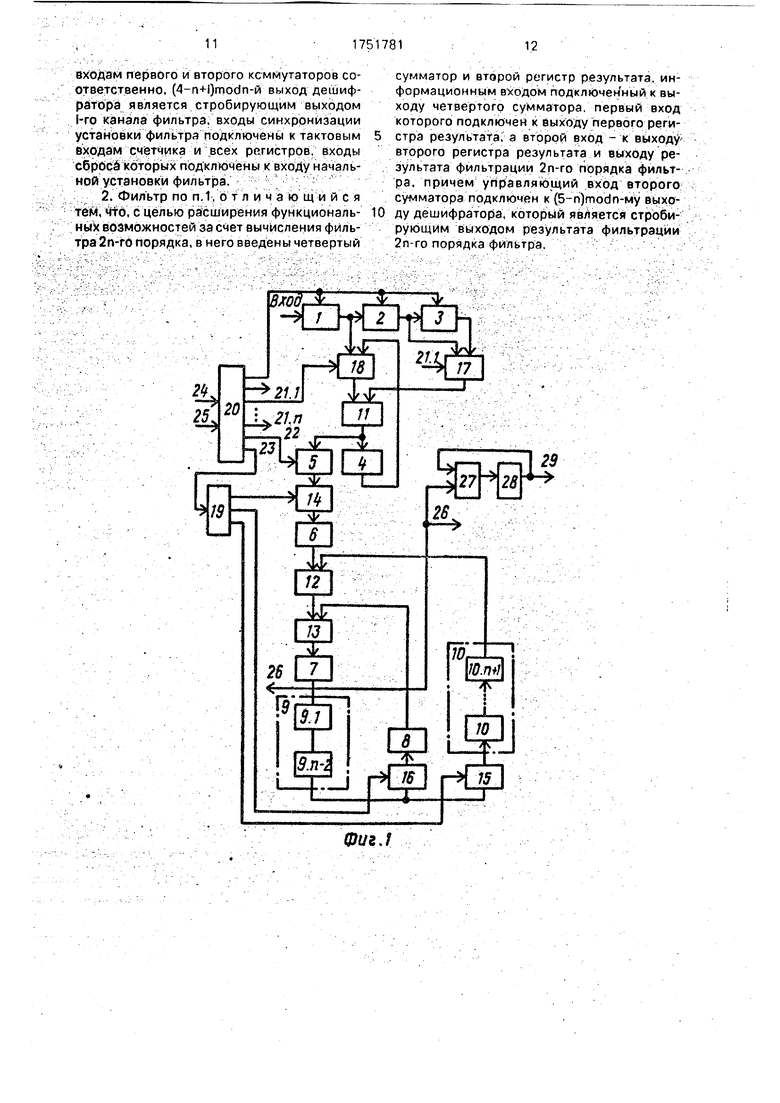

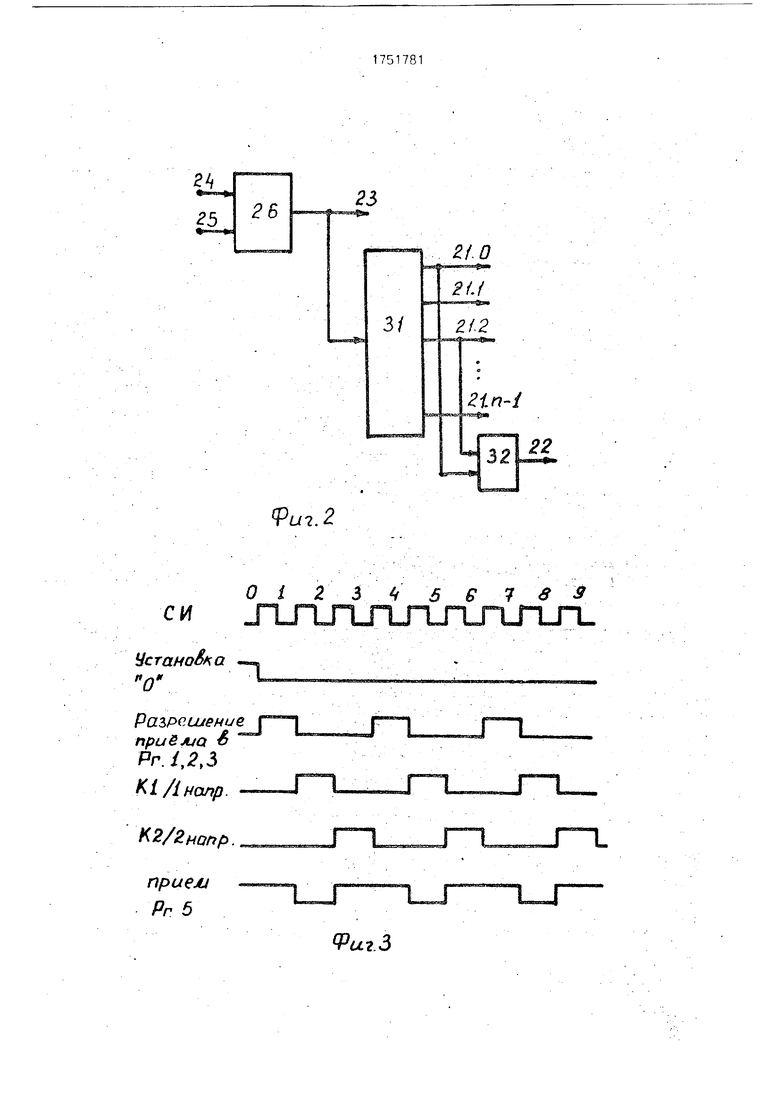

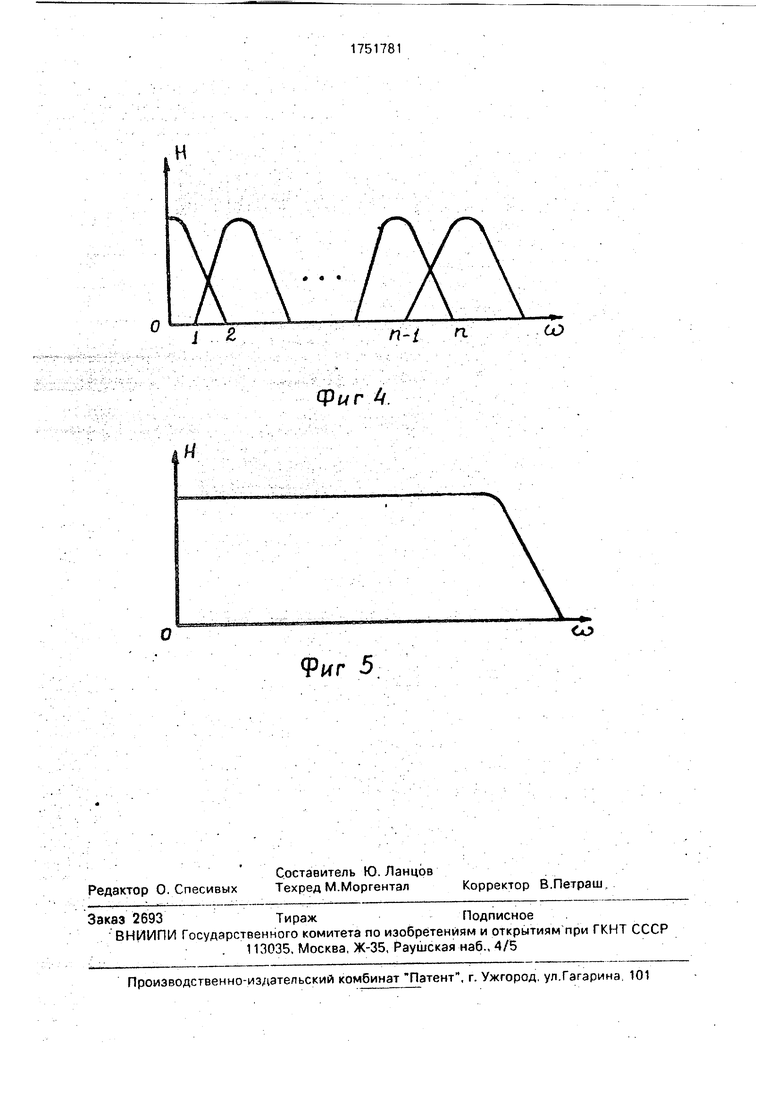

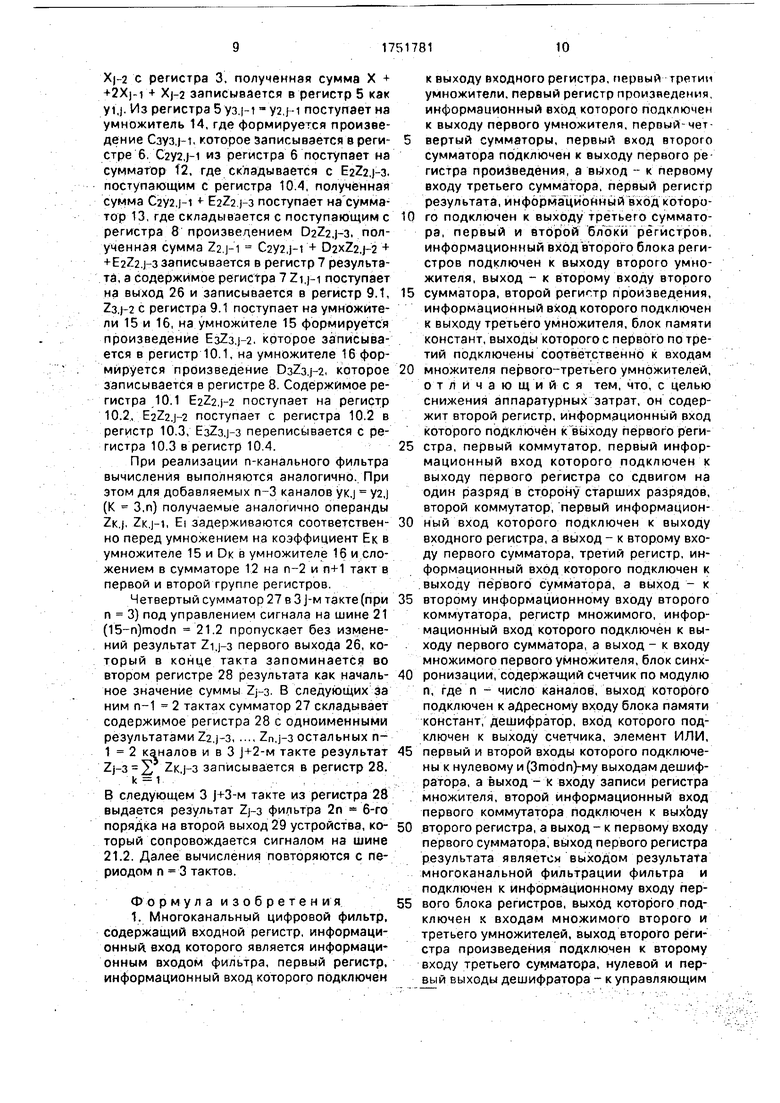

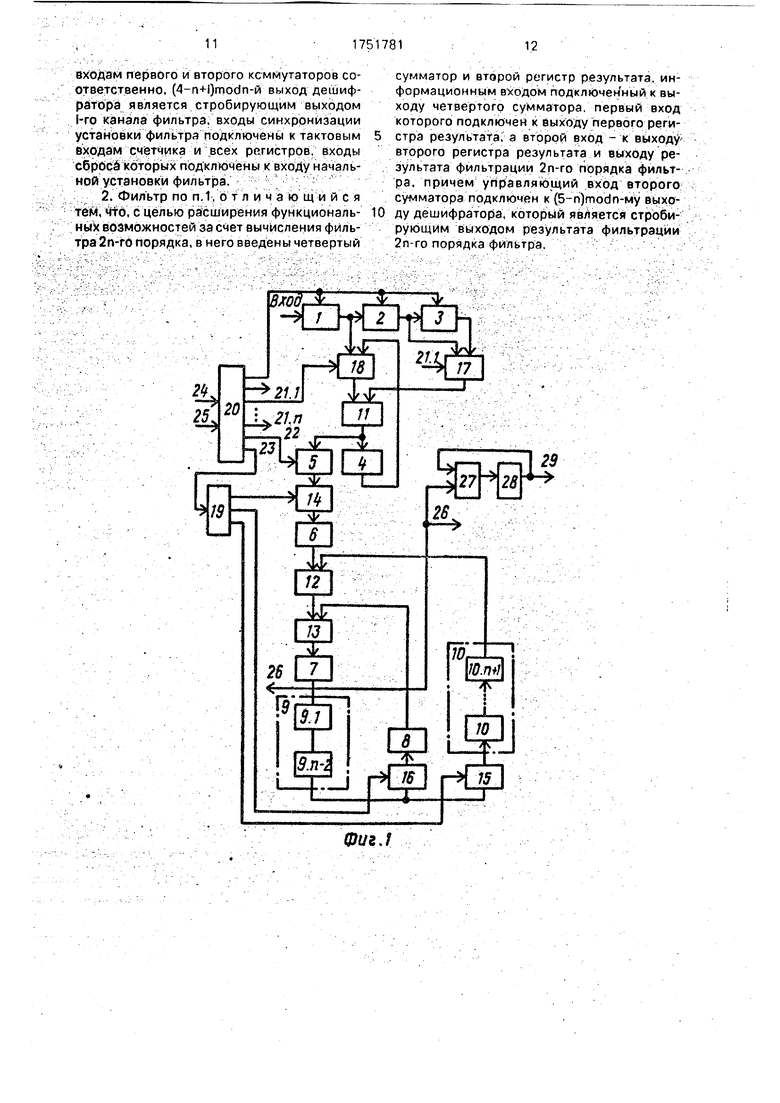

На фиг, 1 представлена структурная схема многоканального цифрового фильтра; на фиг.2 - структурная схема блока синхронизации; на фиг.З - временная диаграмма работы блока синхронизации; на фиг.4 и 5 - амплитудно-частотные характеристики, соответственно п каналов фильтра и фильтра 2п-го порядка

Многоканальный цифровой фильтр (фиг.1) содержит входной регистр 1, первый регистр 2. второй регистр 3, третий регистр 4, регистр множимого 5, первый регистр произведения 6. первый регистр результата 7, второй регистр произведения 8. первый блок регистров 9 из п-2 последовательно включенных регистров, второй блок регистров 10, состоящий из п+1 последовательно включенных регистров, первый сумматор П. второй сумматор 12. третий сумматор 13, первый умножитель 14, второй умножитель 15. третий умножитель 16, первый коммутатор 17, второй коммутатор 18, блок памяти констант 19, блок синхронизации 20. выходы 21.0...21.п-1 блока синхронизации 20,

VI

СЛ

vj 00

выходы 22,23 блока синхронизации, вход 24 синхросигнала блока синхронизации 20, вход 25 начальной установки, выход 26 результата многоканальной фильтрации четвертый сумматор 27, второй регистр результата 28, выход 29 результата фильтрации п-го порядка. Блок синхронизации 20 содержит счетчик 30, дешифратор 31 и элемент ИЛИ 32.

Перечисленные функционэльныеузлы и блоки цифрового фильтра могут быть реализованы на следующих микросхемах. Регистры 1-4, 7, 9.1-9.П-2, 10.2-10.П+1 - на микросхемах 1804Р2, умножитель 14 вместе с регистром 5 и б, умножитель 15 вместе с регистром 10.1 и умножитель 16 вместе с регистром 8 - на микросхемах К 1802ВР5, сумматоры 11-13 и 27 - на К155ИПЗ, коммутаторы 17 и 18-наК531 КП 11.

Многоканальный цифровой фильтр вычисляет п параллельных рекурсивных фильтров второго порядка (п каналов) от одного потока данных (одного сигнала), причем нулевой фильтр - фильтр низких частот, а остальные п-1 фильтров - полосовые (см. фиг.4).

Фильтр низких частот вычисляется по формулам

yi,j xj-2 + 2xj-i + xj,

Zij Ciyij + DiZi,j-i + EiZi,j-2.

Полосовые фильтры вычисляют по формулам:

УК. XJ - Xj-2,

ZK,J Скук + DKZKJ-I + EiZi,j-2.

n K 1, n 3,

где К - номер канала, К 2,3,...,n, j - номер данного.

Фильтр 2п-го порядка вычисляется сложением результатов параллельных каналов фильтра по формуле

Zj JZKJ

k 1

с получением амплитудно-частотной характеристики, равной сумме характеристик этих каналов (фиг.5).

В устройстве применяется одноразрядная синхронизация. При этом момент конца }-го такта (или начала 1+1-го такта) равен моменту фронта i+1-го синхроимпульса на входе 24 (переходу из нуля в единицу), нулевой уровень синхроимпульса в i-м такте разрешает запись в t-й регистр и, таким образом, эта информация на входе этого регистра в момент фронта синхроимпульса оказывается записанной в нем. Эта информация появляется на выходе 1-го регистра в t+1-м такте с некоторой задержкой относительно фронта синхроимпульса, пренебрежимо малой по сравнению с длительностью

такта (задержкой в умножителе, сумматоре) и сохраняется на этом выходе в течение всего 1+1-го такта, в конце которого она в соответствии со структурой устройства,

пройдя логические схемы (умножитель, сумматор, коммутатор), записывается в q-й регистр (l.q - 1,2,...).

По сигналу начальной установки на входе 25 все регистры и счетчик 30 устройства

в конце такта (по фронту первого синхроимпульса) устанавливаются в ноль, следующий такт после сигнала начальной установки считается первым тактом. Состояние счетчика 30 на его выходе остается неизменным до конца такта, меняется с каждым тактом по фронту синхроимпульса (кроме начальной установки) и в i-м такте равно (l- l)modn. Отрицательный уровень сигнала на управляющих входах регистров 1, 2,

3, 5 запрещает запись информации в эти регистры и записанная в них ранее информация сохраняется На выходе 21 I дешифратора 31 устанавливается единичный сигнал в тактах с номером 3j-n м, j 0.1

1 0,1, .., п-1.

Рассмотрим работу устройства для случая п 3. Перед началом работы все регистры установлены в ноль. Входные данные xj поступают каждый третий такт, начиная с

первого.

В первом такте при подаче единичного управляющего сигнала 21.0, поступающего с блока синхронизации 20 на входной регистр 1 с информационного входа 26 устройства, во входной регистр 1 принимается входной отсчет Х0.

Во втором такте входной отсчет Х0 с входного регистра 1 через первый вход второго коммутатора 18, управляемого нулевым уровнем сигнала на шине 21.2, поступает на второй вход первого сумматора 11 где он суммируется с нулем, который поступает с первого регистра 2, через первый вход первого коммутатора 17 по едииичному управляющему сигналу 21.2 на первый вход первого сумматора 11, результат сложения Х0 записывается в третий регистр 4.

В третьем такте Х0 поступает с третьего

регистра 4 через второй вход второго коммутатора 18 под управлением единичного сигнала 21,2 блока синхронизации 20 на- второй вход сумматора 11, где складывается с нулем, поступающим с второго регистра 3

через второй вход первого коммутатора 17, управляемого нулевым сигналом 21.1, на первый вход сумматора 11, результат, равный Х0, по единичному управляющему сигналу 22 записывается в регистр множителя

5 каку1,о.

В четвертом такте по управляющему игналу 21.0, поступающему на входной регистр 1 и первый регистр 2, во входной регистр 1 принимается новый входной отсчет XL в первый регистр 2 с входного регистра 5 1 поступает входной отсчет Х0, который также под управлением нулевого сигнала 21.2 поступает через первый вход второго коммутатора 18 на второй вход сумматора 11, где суммируется с нулем, поступающим че- 10 рез второй вход первого сумматора 17 под правлением нулевого сигнала 21.1 с второго регистра 3 на первый вход сумматора 11, результат сложения, равный Х0, по управляющему сигналу 22 блока синхронизации 20 15 записывается в регистр множителя 5 как 2.о, a yi,o с регистра множителя 5 поступает на первый вход первого умножителя 14, на второй вход первого умножителя 14 с блока 9 памяти констант подается Ci и полученное 20 произведение Ciyi.o записывается в первом регистре 6 произведения.

В пятом такте Xi поступает с регистра 1 через первый вход коммутатора 18 на второй вход сумматора 11, где суммируется с 25 Хо, поступающим со сдвигом на один разряд влево (в сторону старших разрядов) с регистра 2, через второй вход первого коммутатора 17 на первый вход сумматора 11, результат, равный Xi + 2Х0 , записывается в 30 регистр 4. С выхода регистра 5 у2,о поступает на первый вход умножителя 14, на второй вход умножителя 14 с блока 19 памяти констант подается Са. полученное произведение Сауа.о записывается в первом регистре 35 6 произведения. С выхода регистра б Ciyi.o поступает на первый вход второго сумматора 12, где складывается с нулем, поступающим на второй вход сумматора 12 с второй группы 10 регистров, полученная сумма 40 Ciyi.o поступает на третий сумматор 13, где опять происходит сложение с нулем, поступающим с второго регистра 8 произведения, а полученный результат Zi,o Ciyi.o записывается в регистр 7 результатов.45

В шестом такте содержимое регистра 4 Xi + 2 Хо поступает через второй вход коммутатора 18 на второй вход сумматора 11, где складывается с нулем, поступающим с регистра 3 через второй вход первого ком- 50 мутатора 17 на первый вход сумматора 11, результат,равный Xi + 2 Хо,по управляющеу сигналу 22 блока 20 синхронизации записывается в регистр 5 множителя как ум, содержимое регистра 5 уз.о У2,о поступает 55 на первый вход умножителя 14, где формируется произведение Сзузд которое запиывается в регистре 6, произведение Сау2,о с выхода регистра 6 поступает на первый вход второго сумматора 12, где складывается с нулем, поступающим с второй группы 10 регистров, полученная сумма С2У2,о поступает на сумматор 13. где складывается с нулем, поступающим с регистра 8, а полученный результат 2г,о - С2У2.0 записывается в регистр 7 результатов, содержимое регистра 7 Zi,o подается на выход и на первый регистр 9.1 первой группы 9 регистров.

В седьмом такте по управляющему сигналу 21.0 во входной регистр 1 принимается новый входной отсчет Ха, в регистр 2 с регистра 1 поступает Xi, а в регистр 3 с регистра 2 поступает Х0. С входного регистра 1 Xi поступает через второй коммутатор 18 на второй вход сумматора 11, где суммируется с нулем, поступающим через второй вход коммутатора 17с регистра 3 на первый вход сумматора 11, результат, равный Xi, no управляющему сигналу 22 блока 20 синхронизации записывается в регистр 5 как у2,1, С выхода регистра 5 yi,i поступает на первый вход умножителя 14, где формируется произведение Ciyi,i, полученное произведение записывается в регистре 6; произведение Сзуз.о с выхода регистра 6 поступает на первый вход второго сумматора 12, где складывается с нулем, поступающим с второй группы 10 регистров, полученная сумма Сзуз.о поступает на первый вход сумматора 13, где складывается с нулем, поступающим с регистра 8, а полученный результат Zs.o Сзуз.о в конце такта записывается в регистр 7 результатов, в то время как содержимое регистра 7 Z2,o подается на выход 26 и первый регистр 9,1 первой группы регистров, a Zi,o с выхода регистра 9.1 поступает на первый вход второго умножителя 15, где умножается на EI, поступающее с блока 19 памяти констант на второй вход умножителя 15, полученное произведение EiZi.o записывается в первом регистре 10,1 второй группы регистров, Zi,o с регистра 9.1 поступает также на первый вход третьего умножителя 16, где умножается на DI, поступающее с блока 19 памяти констант на второй вход умножителя 16, и полученное произведение DiZi.o записывается во втором регистре 8 произведения.

В восьмом тактеХ2 поступаете регистра 1 через первый вход второго коммутатора 18 на второй вход сумматора 11, где суммируется с Xi, поступающим со сдвигом на один разряд влево с выхода регистра 2, через второй вход первого коммутатора 17 на первый вход сумматора 11, результат, равный Хг + 2 Xi, записывается в регистр 4. С выхода регистра 5 У2.1 поступает на первый вход умножителя 14, где формируется произведение С2У2.1. полученное произведение

записывается в регистре 6. произведение Ciyi.i с выхода регистра б поступает на первый вход второго сумматора 12, где складывается с нулем, поступающим с второго блока 10 задержки, полученная сумма Ciyi.i поступает на первый вход сумматора 13, где складывается с поступающим на второй вход сумматора 13 с второго регистра 8 произведением DiZi.o, полученная сумма Ciyi.i + DiZi.o Zi,i поступает на регистр 7 результатов, содержимое регистра 7 2з,о поступает на выход 26 и первый регистр 9.1 первой группы 9 регистров, с выхода регистра 9.1 Z2,o поступает на первые входы умножителей 15 и 16, сформированное произведение EaZa.o с выхода умножителя 15 поступает на регистр 10.1, произведение D2Z2.0 с выхода умножителя 16 поступает на регистр 8, с выхода регистра 10.1 EiZi,o поступает на регистр 10.2 второй группы 10 регистров,

В девятом такте содержимое регистра 4 Ха + 2 Xi поступает через второй вход коммутатора 18 на второй вход сумматора 11, где складывается с Х0, поступающим с регистра 4 через второй вход первого коммутатора 17 на первый вход сумматора 11. результат суммирования,равный Х0 + 2Xi + + Х2,по управляющему сигналу 22 блока 20 синхронизации записывается в регистр 5 множителя в конце такта как yi,2, содержи- мое.регистрэ 5 уз.1 У2.1 поступает на первый вход умножителя 14, где формируется произведение Сзуз,1, полученное произведение записывается в регистр 6, произведение С2У2.1 с выхода регистра б поступает на первый вход второго сумматора 12, где складывается с нулем, поступающим с второй группы 10 регистров, полученная сумма С2У2И поступает на первый вход сумматора 13, где складывается с поступающим на второй вход сумматора 13с второго регистра 8 произведением D2Z2,o, полученная сумма С2У2.1 + D2Z2.0 Z2.1 поступает на регистр 7 результатов, содержимое регистра 7Zi.i поступает на выход 26 и на регистр 9.1, где запоминается в конце такта, в то время как с выхода регистра 9.1 Тз.о поступает на первые входы умножителей 15 и 16, сформированное произведение Ез Za.o с выхода умножителя 15 поступает на регистр 10.1. Произведение DaZs.o с выхода умножителя 16 поступает на регистр 8, с выхода регистра 10.2 EiZi.o поступает на регистр 10.3. Далее вычисления выполняются циклически с периодом п 3 тактов. В первом такте j-ro цикла, т.е. в f 3j + 1-м такте по управляющему сигналу 21.0. во входной регистр 1 принимается входной отсчет Xj, где j - номер входного отсчета, Xj-1 с входного регистра 1 переписывается в регистр 2, Xj-2 с регистра 2 переписывается в регистр 3, Xj-i с регистра 1 и с регистра 3 поступают соответственно через 18 и 17 коммутаторы

на сумматор 11. результат y2.j-i Xj-i + Xj-з по управляющему сигналу 22 записывается в конце такта в регистр 5, с выхода которого одновременно yi.j-1 Xj-з + 2Xj-2 + Xj-i поступает на первый умножитель 14. где фор0 мируется произведение Ciyij-i, которое записывается в первый вход сумматора 12, где складывается с E3Z3J-4, поступающим с регистра 10.4 второй группы 10 регистров, полученная сумма Сзуз.-2 + Ез2з.-4 посту5 лает на сумматор 13, где складывается с поступающим с второго регистра 8 произведением D3Z3J-3, полученная сумма Z3,j-2 Сзуз)-2 + D3Z3.J-3 + EaZ3j-4 записывается в регистре 7 результата и содержимое регист0 ра 7 Z2,j-2 поступает на выход 26 и записывается в регистр 9.1. a Zi,f-2 с регистра 9.1 поступает на умножители 15 и 16, на умножителе 15 формируется произведение EiZi.j-2, которое записывается в регистре 10.1 второй

5 группы 10 регистров, на умножителе 16 формируется произведение DiZij-2. которое записывается в регистре 8, содержимое регистра 10.1 EaZs. j-з поступает на регистр 10.2, E2Z2.J-3 поступает с регистра 10 2 на регистр

0 10.3, EiZi j-з переписывается с регистра 10.3 в регистр 10,4

Во втором такте J-ro цикла в сумматор 11 с входного регистра 1 поступает X и с регистра 2 со сдвигом на один разряд влево

5 сумма Xj-i записывается в регистр 4. Из регистра 5 у2,н поступает на умножитель 14, сформированное произведение C2y2.j-i записывается в регистр 6. Ciyi,j-i из регистра 6 поступает на сумматор 12, где склады0 вается с EiZi,j-3, поступающим с регистра 10.4, полученная сумма Ciyij-1 + EiZi.j-з поступает на сумматор 13, где складывается с поступающим с регистра 8 произведением DiZi,j-2, полученная сумма Zij-1 Ciyi,j-i +

5 +DiZi,j-2 + EiZi,j-3 записывается в регистре 7 результата, а содержимое регистра 7 Z3.J-2 поступает на выход 26 и записывается в регистр 9.1, Z2.J-2 с регистра 8.1 поступает на умножители 15 и 16, на умножителе 15

0 формируется произведение E2Z2.J-2, которое записывается в регистре 10.1 второй группы 10 регистров, на умножителе 16 фор- мируется произведение D2Z2J-2, которое за- писывается в регистре 8, содержимое

5 регистра 10.1 EiZij-2 поступает на регистр 10.2, E3Z3.J-3 переписывается с регистра 10.2 в регистр 10.3. E2Z2J-3 переписывается с регистра 10.3 в регистр 10.4.

В третьем такте j-ro цикла на сумматор 11 поступает сумма X + 2ХГ1 & регистра 4 и

Xj-2 с регистра 3, полученная сумма X + +2Xj-i + Xj-2 записывается в регистр 5 как yi,j. Из регистра 5 уз.и - У2,н поступает на умножитель 14, где формируется произведение Сэуз.н, которое записывается в регистре 6. С2У2,н из регистра 6 поступает на сумматор f2, где складывается с E2Z2.J-3. поступающим с регистра 10.4, полученная сумма С2У2.Н E2Z2 j-з поступает на сумма- тор 13, где складывается с поступающим с регистра 8 произведением D2Z2.J-3, полученная Сумма Z2J-1 С2У2,Н + D2XZ2.J-2 + +E2Z2.J-3 записывается в регистр 7 результата, а содержимое регистра 7 Zi.j-i поступает на выход 26 и записывается в регистр 9.1, Z3.J-2 с регистра 9.1 поступает на умножители 15 и 16, на умножителе 15 формируется произведение E3Z3.J-2. которое записывается в регистр 10.1, на умножителе 16 формируется произведение D3Z3J-2, которое записывается в регистре 8. Содержимое регистра 10.1 E2Z2.J-2 поступает на регистр 10.2, E2Z2J-2 поступает с регистра 10.2 в регистр 10.3, EsZs.j-s переписывается с регистра 10.3 в регистр 10.4.

При реализации n-канального фильтра вычисления выполняются аналогично. При этом для добавляемых n-З каналов y«,j y2,j (К 3,п) получаемые аналогично операнды ZK.J, ZK.J-I, Ei задерживаются соответственно перед умножением на коэффициент Ек в умножителе 15 и DK в умножителе 16 и сложением в сумматоре 12 на п-2 и п+1 такт в первой и второй группе регистров.

Четвертый сумматор 27 в 3 J-м такте (при п 3) под управлением сигнала на шине 21 (15-n)modn 21.2 пропускает без изменений результат Zi.j-з первого выхода 26, который в конце такта запоминается во втором регистре 28 результата как начальное значение суммы Zj-з. В следующих за ним п-1 2 тактах сумматор 27 складывает содержимое регистра 28 с одноименными

результатами Z2.J-3Znj-3 остальных каналов и в 3 j+2-м такте результат

Zj-3 X ZK.J-S записывается в регистр 28. k 1

В следующем 3 j+3-м такте из регистра 28 выдается результат Zj-з фильтра 2п 6-го порядка на второй выход 29 устройства, который сопровождается сигналом на шине 21.2. Далее вычисления повторяются с периодом п 3 тактов.

Формула изобретения 1. Многоканальный цифровой фильтр, содержащий входной регистр, информационный, вход которого является информационным входом фильтра, первый регистр, информационный вход которого подключен

к выходу входного регистра, первый третий умножители, первый регистр произведения, информационный вход которого подключен к выходу первого умножителя, первый-чет- 5 вертый сумматоры, первый вход второго сумматора подключен к выходу первого регистра произведения, а выход - к первому входу третьего сумматора, первый регистр результата, информационный вход которо0 го подключен к выходу третьего сумматора, первый и второй блоки регистров, информационный вход второго блока регистров подключен к выходу второго умножителя, выход - к второму входу второго

5 сумматора, второй регистр произведения, информационный вход которого подключен к выходу третьего умножителя, блок памяти констант, выходы которого с первого по третий подключены соответственно к входам

0 множителя первого-третьего умножителей, отличающийся тем, что, с целью снижения аппаратурных затрат, он содержит второй регистр, информационный вход которого подключён к выходу первого реги5 стра, первый коммутатор, первый информационный вход которого подключен к выходу первого регистра со сдвигом на один разряд в сторону старших разрядов, второй коммутатор, первый информацион0 ный вход которого подключен к выходу входного регистра, а выход - к второму входу первого сумматора, третий регистр, информационный вход которого подключен к выходу первого сумматора, а выход - к

5 второму информационному входу второго коммутатора, регистр множимого, информационный вход которого подключен к выходу первого сумматора, а выход - к входу множимого первого умножителя, блок синх0 ронизации, содержащий счетчик по модулю п, где п - число каналов, выход которого подключен к адресному входу блока памяти констант, дешифратор, вход которого подключен к выходу счетчика, элемент ИЛИ,

5 первый и второй входы которого подключены к нулевому и (3modn)-My выходам дешифратора, а выход - к входу записи регистра множителя, второй информационный вход первого коммутатора подключен к выходу

0 второго регистра, а выход - к первому входу первого сумматора, выход первого регистра результата является выходом результата многоканальной фильтрации фильтра и подключен к информационному входу пер5 вого блока регистров, выход которого подключен к входам множимого второго и третьего умножителей, выход второго регистра произведения подключен к второму входу третьего сумматора, нулевой и первый выходы дешифратора - к управляющим

входам первого и второго коммутаторов соответственно. (4-n-H)modn-u выход дешифратора является стробирующим выходом 1-го канала фильтра, входы синхронизации установки фильтра подключены к тактовым Ёходам счетчика и всех регистров, входы сброса которых подключены к входу начальной установки фильтра.

2. Фильтр по п. 1,отличающийся тем, что, с целью расширения функциональных возможностей за счет вычисления фильтра 2п-го порядка, в него введены четвертый

сумматор и второй регистр результата, информационным входом подключенный к выходу четвертого сумматора первый вход которого подключен к выходу первого регистра результата, а второй вход - к выходу второго регистра результата и выходу результата фильтрации 2п-го порядка фильтра, причем управляющий вход второго сумматора подключен к (S-n)modn-My выходу дешифратора, который является стробирующим выходом результата фильтрации 2п-го порядка фильтра,

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр | 1986 |

|

SU1348981A1 |

| Рекурсивный цифровой фильтр | 1989 |

|

SU1640711A1 |

| Устройство для цифровой фильтрации | 1986 |

|

SU1377872A1 |

| Цифровой фильтр | 1987 |

|

SU1501088A1 |

| Процессор для цифровой обработки сигналов | 1985 |

|

SU1257662A1 |

| Устройство для перемножения матриц | 1989 |

|

SU1839262A1 |

| Цифровой фильтр | 1986 |

|

SU1357976A1 |

| Устройство для вычисления свертки | 1986 |

|

SU1319045A1 |

| Устройство для перемножения матриц | 1989 |

|

SU1705836A1 |

| Устройство для вычисления скользящего спектра | 1987 |

|

SU1427386A1 |

Изобретение относится к области вычислительной техники и предназначено для построения системы цифровой обработки сигналов. Цель изобретения - снижение аппаратурных затрат (за счет исключения дополнительных умножителей, сумматора. блоков регистров), а также расширение функциональных возможностей за счет вычисления фильтра 2п-го порядка. Многоканальный цифровой фильтр содержит регистры 1-8, блоки регистров 9 и 10, сумматоры 11, 12, 13, умножители 14, 15. 16, коммутаторы 17, 18, сумматор 27 и регистр 28, блок 30 синхронизации. Устройство вычисляет п параллельных рекурсивных фильтров второго порядка (п каналов) от одного потока данных, причем нулевой фильтр является фильтром низких частот, а остальные п-1 фильтров - полосовыми Входные отсчеты поступают на информационный вход регистра 1 каждый n-й такт, начиная с первого, а результаты выдаются в каждом такте с выхода 26 устройства. Каждый n-й такт с выхода 29 устройства выдаются результаты вычисления параллельного фильтра 2п-го порядка. 1 з.п. ф-лы. 5 ил.

Фиг.

Si

25

26

Pu.2

СИ Установка

Qi23 i56ie3

Разрешен и приёма 6 Рг. 1,2,3

Ki/tnanp. --К2/2напр.

прием Рг 5

ФигЗ

23

Ф

3/

212

иве

Ztn-i

l Ј

Фиг Ц.

Фиг 5

n-i гг

со

| Цифровой рекурсивный полосовой фильтр | 1984 |

|

SU1224980A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Многоканальный цифровой фильтр | 1978 |

|

SU783796A2 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-07-30—Публикация

1990-10-19—Подача