(21)4204744/24-24

(22)02.03.87

(46) 30.09.88. Бюл. № 36

(71)Киевский политехнический институт им. 50-летия Великой Октябрьской социалистической революции

(72)Ю.С.Каневский, Н.Е.Куц, Л.М.Логинова и Ф.В.Самофалова

(53)681.32(088.8)

(56)Авторское свидетельство СССР

№ 1027733, кл. G 06 F 15/332, 1983.

Измерительная техника, 1981, № 7, с. 22.

(54)УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СКОЛЬЗЯЩЕГО СПЕКТРА

(57)Изобретение относится к вычислительной технике, предназначено для вычисления скользящего спектра сигна- лов и может быть использовано в анализаторах спектра, работающих в реальном масштабе времени, при цифровой обработке сейсмических и других сигналов. Цель изобретения - повышение точности. Поставленная цель достигается за счет того, что в состав устройства входят информационный вход 1, регистры 2, 3, вычитатель 4, регистр 5, блок памяти 6, умножитель 7, блок 8 постоянной памяти, блок синхронизации 9, информационный выход 10, регистр 11, сумматор 12, регистр 13, вход 14 задания режима, элемент И 15, тактовый вход 16, выходы 17-23 блока синхронизации, KOTOpbtfi содержит генератор 24 тактовых импульсов, регистр 25, счетчик тактов 26, счетчик операций 27, дешифратор 28, элемент ИЛИ 29, узел постоянной памяти 30, сумматор 31, элемент И 32. 1 з.п. ф-лы, 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления скользящего спектра | 1986 |

|

SU1363240A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1254506A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1381541A1 |

| Устройство для вычисления скользящего спектра | 1988 |

|

SU1527642A1 |

| Устройство для вычисления скользящего спектра | 1987 |

|

SU1418746A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Цифровой фильтр | 1986 |

|

SU1387015A1 |

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

| Процессор для цифровой обработки сигналов | 1985 |

|

SU1257662A1 |

| Устройство для матричных операций | 1989 |

|

SU1777154A1 |

4 «М

СО 00

Изобргетение относится к вычислительной технике, предназначено для вычисления скользящего спектра сигналов и может быть использовано в ана лизаторах спектра, работающих в реальном масштабе времени при цифровой обработке сейсмических и других сигналов .

Целью изобретения является повьшение точности (оценки спектральных составляющих сигнала) устройства.

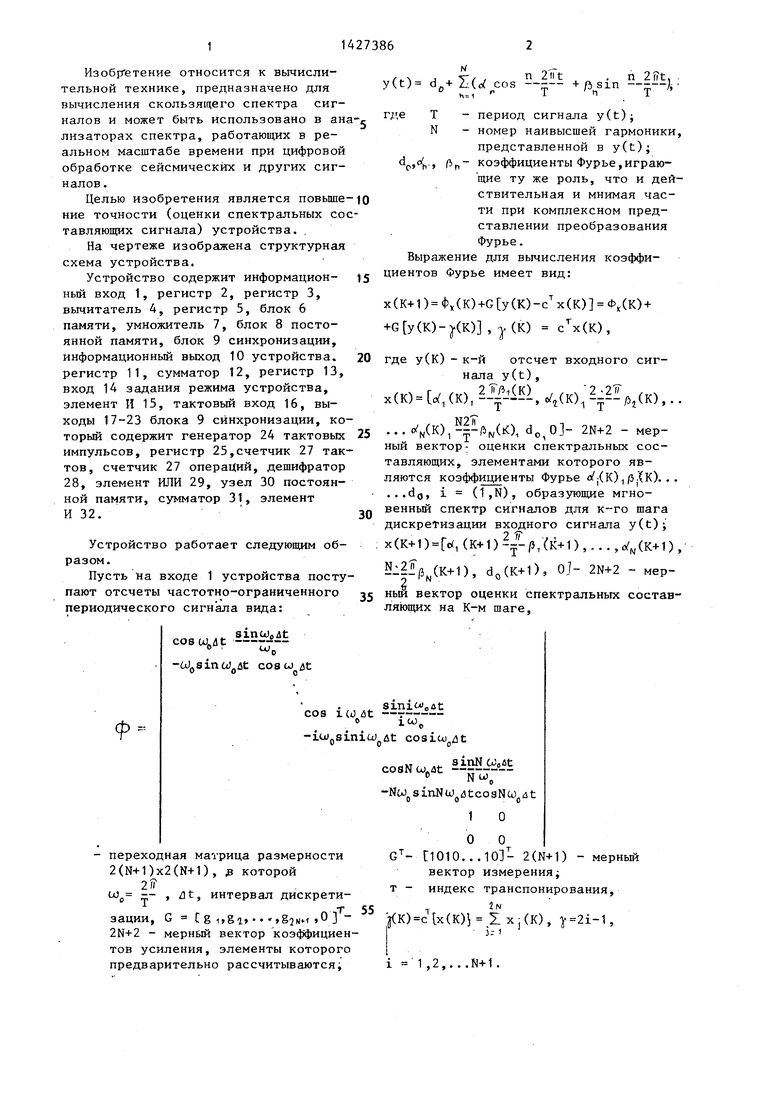

На чертеже изображена структурная схема устройства.

Устройство содержит информацион- ный вход 1, регистр 2, регистр 3, вычитатель 4, регистр 5, блок 6 памяти, умножитель 7, блок 8 постоянной памяти, блок 9 синхронизации, информационный выход 10 устройства. регистр 11, сумматор 12, регистр 13, вход 14 задания режима устройства, элемент И 15, тактовый вход 16, выходы 17-23 блока 9 синхронизации, который содержит генератор 24 тактовых импульсов, регистр 25,счетчик 27 тактов, счетчик 27 операций, дешифратор 28, элемент ИЛИ 29, узел 30 постоянной памяти, сумматор 31, элемент И 32.

Устройство работает следующим образом.

Пусть На входе 1 устройства поступают отсчеты частотно-ограниченного периодического сигнала вида:

cosH.tSin.

-(jJ ainoigut cosco/st

cos 1w ut

0

iuT

-iujpsiniojput cosico t

sinN Wo fit

cosN cjpdt

переходная матрица размерности 2(N+1)x2(N+1), p которой

2ff U)g -- , t, интервал дискретит 55

зации, G С g i,ga, .,g2NH 0

2N+2 - мерный вектор коэффициентов усиления, элементы которого предварительно рассчитываются;

/.х 1 V/ , п 2iit . п 2(t. . y(t) (cos --- ---),

где Т - период сигнала y(t);

N - номер наивысшей гармоники,

представленной в y(t); dp,o(., - коэффициенты Фурье,играющие ту же роль, что и действительная и мнимая части при комплексном представлении преобразования Фурье.

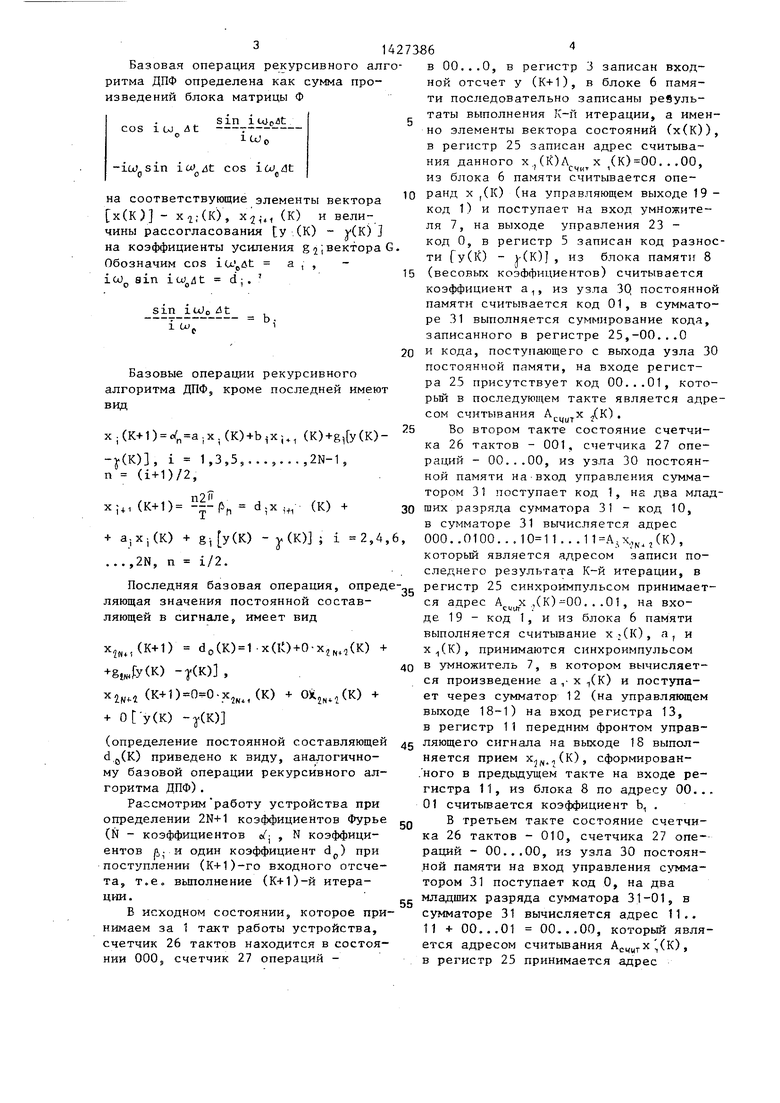

Выражение для вычисления коэффициентов Фурье имеет вид:

х(К+1)Ф,(К)(К)(К) Ф,(К) + (K)-|(K),(K) с х(К),

где у(к) - к-й отсчет входного сигнала y(t) ,

fv TV С1ГЛ (K) ,/,.ч 2-2 Г х(К)1о, (К), -, 6/j(K) ---/5j(K), . .

...,(К),(КХ 2N+2 - мерный вектор- оценки спектральных составляющих, элементами которого являются коэффициенты Фурье о1 (К) ), . . ...d0, i (1,N), образующие мгновенный спектр сигналов для к-го шага дискретизации входного сигнала y(t);

х(К+1) Гс/, (К+О ---/з;(к+1) , . . . ,с(К-И) , (K+i), ), Oj- 2N+2 - мерНЫИ вектор оценки спектральных составляющих на К-м шаге.

iuT

sinN W

cosN cjpdt

Ми)„

-NWjjSinNw dtcosNWg t

О О 1010... 101- 2(N+1) - мерный

вектор измеренияi т - индекс транспонирования,

2N

3(K)(K)i Zxj(K), , i 1,2,...N+1.

Базовая операция рекурсивного алгоритма ДПФ определена как сумма произведений блока матрицы Ф

cos 1 UI 4t

S in 1 .

-lCi sin COS

на соответствующие элементы вектора х(К) - (К), х (к) и величины рассогласования у (К) - (К) на коэффициенты усиления g ;вектора G Обозначим cos а , , dj.

icOp sin

sin

i U).

b,

Базовые операции рекурсивного алгоритма ДПФ, кроме последней имеют вид

Xj(K-H) .(K)+biXi., (K)+g,y(K)-у(К), i 1,3,5,...,...,2N-1, n (i+1)/2.

25

n2 i

(K)

30

Bo втором такте состояние счетчика 26 тактов - 001, счетчика 27 операций - 00...00, из узла 30 постоянной памяти на-вход управления сумматором 31 поступает код 1, на два младших разряда сумматора 31 - код 10, в сумматоре 31 вычисляется адрес 000..0100. . . 1 . . .1 ,,.,(К), который является адресом записи последнего результата К-й итерации, в Последняя базовая операция, опреде- регистр 25 синхроимпульсом принимается адрес А X .,(К) 00. . .01, на вхох;,, (К+1) -|-(Ь, d,x,

+ а,х., (К) + (K) -y(K)J; i 2,4,6 ..,,2N, п i/2.

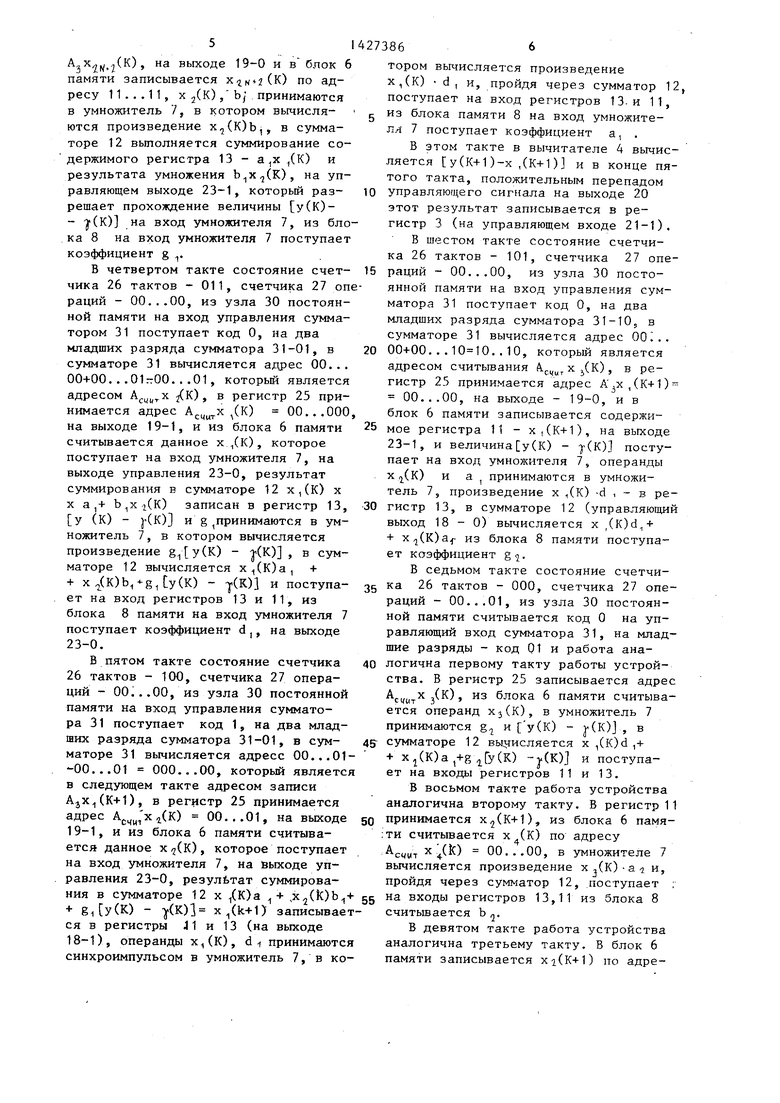

ляющая значения постоянной составляющей в сигнале, имеет вид

де 19 - код 1, и из блока 6 памяти выполняется считывание XjdO, а, и х(К), принимаются синхроимпульсом

Xj,.(K+1) do(K) 1-x(lO + 0-Xj,,(K) + ) -j.(K) ,

x,,, ().x,,(K) - OAj,,,(K) 4 -H (K) -j(K)

де 19 - код 1, и из блока 6 памяти выполняется считывание XjdO, а, и х(К), принимаются синхроимпульсом

40

В умножитель 7, в котором вычисляется произведение а,-Хт(К) и поступает через сумматор 12 (на управляющем выходе 18-1) на вход регистра 13, в регистр 11 передним фронтом управ(определение постоянной составляющей g ляющего сигнала на выходе 18 выполняется прием х(К), сформирован- . ного в предьщущем такте на входе регистра 11, из блока 8 по адресу 00,.. 01 считывается коэффициент Ь, .

50

d (j(K) приведено к виду, аналогичному базовой операции рекурсивного алгоритма ДПФ) ,

Рассмотрим работу устройства при определении 2N+1 коэффициентов Фурье (N - коэффициентов e/j , N коэффициентов л,- и один коэффициент d) при поступлении (К+1)-го входного отсчета, т.е. выполнение (К+1)-й итерации,

В исходном состоянии, которое принимаем за 1 такт работы устройства, счетчик 26 тактов находится в состоянии 000, счетчик 27 операций В третьем такте состояние счетчика 26 тактов - 010, счетчика 27 операций - 00...00, из узла 30 постоянной памяти на вход управления сумматором 31 поступает код О, на два gg младших разряда сумматора 31-01, в сумматоре 31 вычисляется адрес 11.. 11 + 00...01 00,..00, который является адресом считьшания А ц т-х /К), в регистр 25 принимается адрес

в 00.,.О, в регистр 3 записан входной отсчет у (К+1), в блоке 6 памяти последовательно записаны ревуль- таты выполнения К-й итерации, а именно элементы вектора состояний (х(К)), в регистр 25 записан адрес считывания данного X., (К) (К)00. . .00, из блока 6 памяти считывается опе0 ранд X ,(К) (на управляющем выходе 19 - код 1) и поступает на вход умножителя 7, на выходе управления 23 - код О, в регистр 5 записан код разности ГУ(К) - }-(К) , из блока памяти 8

5 (весовых коэффициентов) считывается коэффициент а,, из узла 3Q постоянной памяти считывается код 01, в сумматоре 31 выполняется суммирование кода, записанного в регистре 25,-00...О

0 и кода, поступающего с выхода узла 30 постоянной памяти, на входе регистра 25 присутствует код 00...01, кото- рьй в последующем такте является адре

COM считывания A x /K).

Bo втором такте состоя ка 26 тактов - 001, счетч раций - 00...00, из узла ной памяти на-вход управл тором 31 поступает код 1, ших разряда сумматора 31 в сумматоре 31 вычисляетс 000..0100. . . 1 . . .1 1 Лкоторый является адресом следнего результата К-й и регистр 25 синхроимпульсо ся адрес А X .,(К) 00. . .01

30

де 19 - код 1, и из блока 6 памяти выполняется считывание XjdO, а, и х(К), принимаются синхроимпульсом

40

В третьем такте состояние счетчика 26 тактов - 010, счетчика 27 операций - 00...00, из узла 30 постоянной памяти на вход управления сумматором 31 поступает код О, на два младших разряда сумматора 31-01, в сумматоре 31 вычисляется адрес 11.. 11 + 00...01 00,..00, который является адресом считьшания А ц т-х /К), в регистр 25 принимается адрес

А x,,j(K), на выходе 19-0 и в блок 6 памяти записывается ) по адресу 11...11, X (K), Ь; принимаются в умножитель 7, в котором вычисляются произведение х,(К)Ь,, в сумматоре 12 вьтолняется суммирование со- держимого регистра 13 - /К) и результата умножения (К), на управляющем выходе 23-1, который разрешает прохождение величины у(К)- - 7(к) на вход умножителя 7, из блока 8 на вход умножителя 7 поступает коэффициент g .

В четвертом такте состояние счет- 15 раций - 00.,.00, из узла 30 посто- чика 26 тактов - 011, счетчика 27 one- янной памяти на вход управления сум- раций - 00...00, из узла 30 постоян- матора 31 поступает код О, на два

тором вычисляется произведение х,(К) d, и, пройдя через сумматор 12 поступает на вход регистров 13. и 11, g из блока памяти 8 на вход умножителя 7 поступает коэффициент а, .

В этом такте в вычитателе 4 вычисляется у(К+1)-х ,(К+1) и в конце пятого такта, положительным перепадом управляющего сигнала на выходе 20 этот результат записывается в регистр 3 (на управляющем входе 21-1). В шестом такте состояние счетчика 26 тактов - 101, счетчика 27 опе

10

ной памяти на вход управления сумматором 31 поступает код О, на два младших разряда сумматора 31-01, в сумматоре 31 вычисляется адрес 00... 00+00...OlrOO...01, который является адресом j(K), в регистр 25 принимается адрес A(, ,(К) 00.,.000, на выходе 19-1, и из блока 6 памяти считывается данное х /К), которое поступает на вход умножителя 7, на выходе управления 23-0, результат суммирования в сумматоре 12 х,(К) х X а,+ (K) записан в регистр 13, у (к) - j CK) и g принимаются в умножитель 7, в котором вычисляется произведение (K) - |(К) , в сумматоре 12 вычисляется х(К)а, +

младших разряда сумматора 31-10; в сумматоре 31 вычисляется адрес 00..

20 00+00.,...10, который является адресом считывания А.., х ,,(К), в регистр 25 принимается адрес А .х ,(К+1 ) 00...00, на выходе - 19-0, и в блок 6 памяти записывается содержи25 мое регистра 11 - х,(К+1), на выходе 23-1, и величина у(К) - y(K)j поступает на вход умножителя 7, операнды ) и а принимаются в умножитель 7, произведение х (К) -d i - в ре30 гистр 13, в сумматоре 12 (управляющий выход 18 - 0) вычисляется х ,(K) + х(К) из блока 8 памяти поступает коэффициент .

В седьмом такте состояние счетчи+ X (К) Ду(К) - T(K) и поступа- 35 тактов - 000, счетчика 27 опеет на вход регистров 13 и 11, из блока 8 памяти на вход умножителя 7 поступает коэффициент d,, на выходе 23-0.

В пятом такте состояние счетчика 26 тактов - 100, счетчика 27 операций - 00...00, из узла 30 постоянной памяти на вход управления сумматора 31 поступает код 1, на два младших разряда сумматора 31-01, в сумматоре 31 вычисляется адресе 00...01- -00...01 000,0.00, которьй является в следующем такте адресом записи AjX(K+1), в регистр 25 принимается адрес (К) 00..,01, на выходе

40

19-1, и из блока 6 памяти считывается данное ), которое поступает на вход умножителя 7, на выходе управления 23-0, результат суммирования в сумматоре 12 х /К)а + ,Х2(К) gg (K) - -(3 x(k+1) записывается в регистры J1 и 13 (на выходе 18-1), операнды х(К), d принимаются синхроимпульсом в умножитель 7, в кораций - 00,..01, из узла 30 постоянной памяти считывается код О на управляющий вход сумматора 31, на младшие разряды - код 01 и работа аналогична первому такту работы устройства, В регистр 25 записывается адрес Aj, ,(К), из блока 6 памяти считывается операнд Хз(К), в умножитель 7 принимаются g и у(К) - j (K) , в 45- сумматоре 12 вычисляется х ,(K)d ,+ + Xj(K)a,+g ,у(К) j.(K)J и поступает на входы регистров 11 и 13,

В восьмом та:кте работа устройства аналогична второму такту. В регистр 11 принимается Х2(К+1), из блока 6 памяти считывается х (К) по адресу

счмт X 00,.,00, в умножителе 7 вычисляется произведение х,(К)-а1И, пройдя через сумматор 12, поступает ; на входы регистров 13,11 из блока 8 считьшается b ,j.

В девятом такте работа устройства аналогична третьему такту, В блок 6 памяти записывается xi(K+1) по адре50

тором вычисляется произведение х,(К) d, и, пройдя через сумматор 12, поступает на вход регистров 13. и 11, из блока памяти 8 на вход умножителя 7 поступает коэффициент а, .

В этом такте в вычитателе 4 вычисляется у(К+1)-х ,(К+1) и в конце пятого такта, положительным перепадом управляющего сигнала на выходе 20 этот результат записывается в регистр 3 (на управляющем входе 21-1). В шестом такте состояние счетчика 26 тактов - 101, счетчика 27 опе

младших разряда сумматора 31-10; в сумматоре 31 вычисляется адрес 00..

00+00.,...10, который является адресом считывания А.., х ,,(К), в регистр 25 принимается адрес А .х ,(К+1 ) 00...00, на выходе - 19-0, и в блок 6 памяти записывается содержимое регистра 11 - х,(К+1), на выходе 23-1, и величина у(К) - y(K)j поступает на вход умножителя 7, операнды ) и а принимаются в умножитель 7, произведение х (К) -d i - в регистр 13, в сумматоре 12 (управляющий выход 18 - 0) вычисляется х ,(K) + х(К) из блока 8 памяти поступает коэффициент .

В седьмом такте состояние счетчи0

g

раций - 00,..01, из узла 30 постоянной памяти считывается код О на управляющий вход сумматора 31, на младшие разряды - код 01 и работа аналогична первому такту работы устройства, В регистр 25 записывается адрес Aj, ,(К), из блока 6 памяти считывается операнд Хз(К), в умножитель 7 принимаются g и у(К) - j (K) , в 5- сумматоре 12 вычисляется х ,(K)d ,+ + Xj(K)a,+g ,у(К) j.(K)J и поступает на входы регистров 11 и 13,

В восьмом та:кте работа устройства аналогична второму такту. В регистр 11 принимается Х2(К+1), из блока 6 памяти считывается х (К) по адресу

счмт X 00,.,00, в умножителе 7 вычисляется произведение х,(К)-а1И, пройдя через сумматор 12, поступает ; на входы регистров 13,11 из блока 8 считьшается b ,j.

В девятом такте работа устройства аналогична третьему такту, В блок 6 памяти записывается xi(K+1) по адре0

су AjX ,j(K+1 )00. , .01, в умножителе 7 вычисляется произведение Ь, на сумматоре 12 - х (К) ,(К)а,из регистра 5 операнд у(К) - (К)} поступает на вход умножителя 7, из блока 8 памяти считывается gj.

Далее работа устройства аналогична.

В течение выполнения итерации на информационный вход 1 устройства поступает отсчет у(К+2) и, если на входе 14 присутствует 1, синхроимпульс приема входного данного, поступающий по входу 16, запишет (К+2) в регистр 2.

После вьтолнения (Ы+1)-й базовой операции сигнал переполнения

которого подключен к первому информ ционному входу умножителя, выход ко торого подключен к первому информационному входу сумматора, выход кот рого подключен к информационному вх ду первого регистра, выход которого является информационным выходом уст ройства и подключен к информационно входу блока памяти, выход которого подключен к второму информационному входу умножителя, первый выход блок синхронизации подключен к входу син хронизации умножителя, вход синхро- 15 низации сумматора соединен с входо синхронизации первого регистра и под ключен к второму выходу блока синхр низации, третий выход которого подключен к входу управления записьюс. выхода счетчика 27 операций запишет

в регистр 5 вычисленную разность 20 Считыванием блока памяти, адресные

уСК+О- -СК+О , а с помощью нулевого входы которого подключены к выходам

значения на управляющем выходе 21 и

синхросигнала на выходе 20, значение

у(К+2) запишется в регистр 3, и выпервой группы блока синхронизации, выходы второй группы которого подклю чены к адресным входам блока постоян

числение коэффициентов фурье на К+2 шаге для скользящего спектра повторяется.

Если требуется устранить ошибки, вызванные усечением или округлением вычислений при получении элементов вектора Сх(К+1), необходимо вьтол- нять повторное вычисление вектора х(К+1) согласно выражению (1), в котором в качестве исходного вектора состояний х(К) взят вычисленный вектор х(К+1), а значение входного отсчета не изменяется.

Таким образом, если на входе 14 присутствует нулевой уровень, то

запрещается запись следующего входно- до выход блока памяти подключен к инфор- го отсчета у(К+2) в регистр 2, в ре- мационному входу четвертого регистра, гистр 3 выполняется повторная запись выход сумматора подключен к информа- у(К+1) из регистра 2, в регистр 5 за- ционному входу пятого регистра, выписывается разность fу(К+1)-У(К+1) ход которого подключен к второму ин- и вычисления повторяются согласно 45 Формационному входу сумматора, вход указанной работе устройства. В регист- ре 3 вьтисляется разность (К+1)-(К+2), которая в следующей итерации участвует в коррекции вектора состояний

синхронизации пятого регистра подключен к первому выходу блока синхронизации, четвертый выход которого под ключен к входу синхронизаг ии третьего регистра, вход разрешения приема которого подключен к пятому выходу блока синхронизации, шестой и седьмой выходы которого подключены соответ- ветственно к входу синхронизации и входу разрешения приема четвертого регистра, информационный вход второго регистра является информационным входом устройства, входом задания режима и тактовым входом которого явК+2,

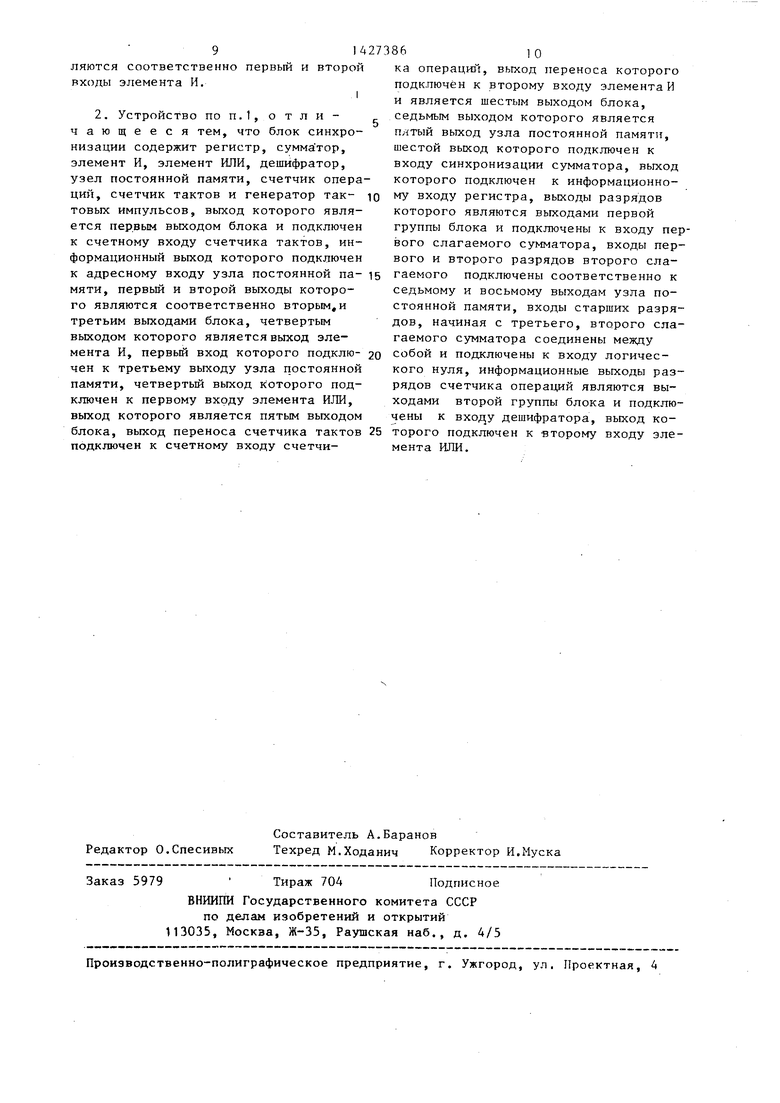

Формула изобретения

которого подключен к первому информационному входу умножителя, выход которого подключен к первому информационному входу сумматора, выход которого подключен к информационному входу первого регистра, выход которого является информационным выходом устройства и подключен к информационному входу блока памяти, выход которого подключен к второму информационному входу умножителя, первый выход блока синхронизации подключен к входу синхронизации умножителя, вход синхро- низации сумматора соединен с входом синхронизации первого регистра и подключен к второму выходу блока синхронизации, третий выход которого подключен к входу управления записью

входы которого подключены к выходам

первой группы блока синхронизации, выходы второй группы которого подключены к адресным входам блока постоянной памяти, отличающееся тем, что, с целью повьш1ения точное- ти вычислений, в него введены второй, третий, четвертьй и пятый регистры и элемент И, выход которого подключен к входу синхронизации второго регистра, выход которого подключен к первому информационному входу третьего регистра, выход которого соединен с выходом четвертого регистра и

подключен к первому входу вычитателя, выход которого подключен к второму информационному входу третьего регистра, выход первого регистра подключен к второму входу вычитателя.

о выход блока памяти подключен к инфор- мационному входу четвертого регистра, выход сумматора подключен к информа- ционному входу пятого регистра, выход которого подключен к второму ин- 45 Формационному входу сумматора, вход

0

5

синхронизации пятого регистра подключен к первому выходу блока синхронизации, четвертый выход которого подключен к входу синхронизаг ии третьего регистра, вход разрешения приема которого подключен к пятому выходу блока синхронизации, шестой и седьмой выходы которого подключены соответ- ветственно к входу синхронизации и входу разрешения приема четвертого регистра, информационный вход второго регистра является информационным входом устройства, входом задания режима и тактовым входом которого являются соответственно рходы элемента И,

первый и второй

0

5

ка операций, выход переноса которого подключен к второму входу элемента И и является шестым выходом блока, седьмым выходом которого является пятый выход узла постоянной памяти, шестой выход которого подключен к входу синхронизации сумматора, выход которого подключен к информационному входу регистра, выходы разрядов которого являются выходами первой группы блока и подключены к входу первого слагаемого сумматора, входы первого и второго разрядов второго слагаемого подключены соответственно к седьмому и восьмому выходам узла постоянной памяти, входы старших разрядов, начиная с третьего, второго слагаемого сумматора соединены между собой и подключены к входу логического нуля, информационные выходы разрядов счетчика операций являются выходами второй группы блока и подключены к дешифратора, выход которого подключен к второму входу элемента ИЛИ.

Авторы

Даты

1988-09-30—Публикация

1987-03-02—Подача