Изобретение относится к микроэлектронике и вычислительной технике, а именно к схемам линий задержки, широко применяемым для обеспечения синхронизации между электронными системами различного назначения.

Известны гибридные линии задержки, в которых наряду с бескорпусной ИС.исполь- зуемой как входной и выходные буферы, монтируются конденсаторы, катушки индуктивности, резисторы, имитирующие характеристики длинных кабельных линий.

Недостатками этих схем являются низкая надежность, связанная с применением навесного монтажа пассивных элементов невысокая точность задания величины задержки, связанная с разбросом параметров

навесных элементов от одной ячейки линии задержки к другой.

Наиболее близким техническим решением к изобретению является линия задержки, содержащая вход, десять ячеек задержки, включающих выходные инверторы, выходы которых подключены к соответствующим выходам линии задержки, каждая ячейка включает навесные времязадающие элементы - конденсатор и индуктивность, вход линии задержки рез входной инвертор подключен к первой ячейке, навесные времязадающие элементы ячеек соединены между собой последовательно.

При поступлении сигнала на вход линии задержки он передается на выходы с опреч ел

о ю

деленной временной задержкой, соответствующей данному выходу.

Недостатком известной пинии является низкая надежность схемы, связанная с наличием навесных времязадзющчх элементов (конденсаторов и индуктивмостей) а каждой ячейке линии задержки. Кроме того, разброс параметров навесных элементов от ячейки к ячейке приводит к снижению точности задания величины задержки.

Цель изобретения - повышение надежности схемы и точности задания величины задержки.

Указанная цель достигается тем, что в схему линии задержки, содержащую вход, п ячеек задержки, каждая из которых содержит выходной инвертор, выходы инверторов соединены с соответствующими п выходами линии задержки, первый и второй времязадающие конденсаторы, первые выводы которых соединены с общей шиной, согласно изобретению в каждой из п ячеек введены элемент 2ИЛИ-НЕ, элемент 2И с прямым и инверсным входами, первый и второй переключатели тока, шина опорного напряжения, двойной инвертор с прямым и инверсным выходами, элемент НЕ, первый и второй транзисторы, первый и второй диоды, первый и второй резисторы. Выход элемента 2ИЛИ-НЕ подключен к входу выходного инвертора, первый вход элемента 2ИЛИ-НЕ соединен с выходом элемента 2И, а второй вход - с прямым выходом первого переключателя тока, прямой вход элемента 2И соединен с выходом элемента НЕ, а инверсный вход - с прямым выходом второго переключателя тока, вход первого переключателя тока подключен к прямому выходу двойного инвертора, а вход второго переключателя тока - к инверсному выходу двойного инвертора, вход двойного инвертора соединен с входом элемента НЕ и подключен к входу ячейки задержки, шина опорного напряжения подключена к первому и второму переключателям тока. Эмиттер первого транзистора соединен с прямым выходом двойного инвертора, его база соединена с анодом первого диода и через первый резистор с шиной питания, коллектор первого транзистора соединен с вторым выводом первого времязадающего конденсатора, катод первого диода - с выходом элемента 2ИЛИ-НЕ, эмиттер второго транзистора - с инверсным выходом двойного инвертора, его база - с анодом второго диода и через второй резистор с шиной питания, коллектор второго транзистора соединен с вторым выводом второго времязадающего конденсатора, катод второго диода подключен к выходу выходного

инвертора, С второй по n-ю ячейки задержки введены также в ячейки задержки третий и четвертый диоды, причем анод третьего диода подключен к аноду первого диода, а

анод четвертого диода - к аноду второго диода, катод третьего диода n-й ячейки соединен с выходом выходного инвертора (п- 1)-й ячейки, а катод четвертого диода п-й ячейки - с выходом элемента 2ИЛИ-НЕ

(п-1)-й ячейки, выход (п-1)-1 ячейки соединен с входом n-й ячейки, вход линии задержки - с входом первой ячейки,

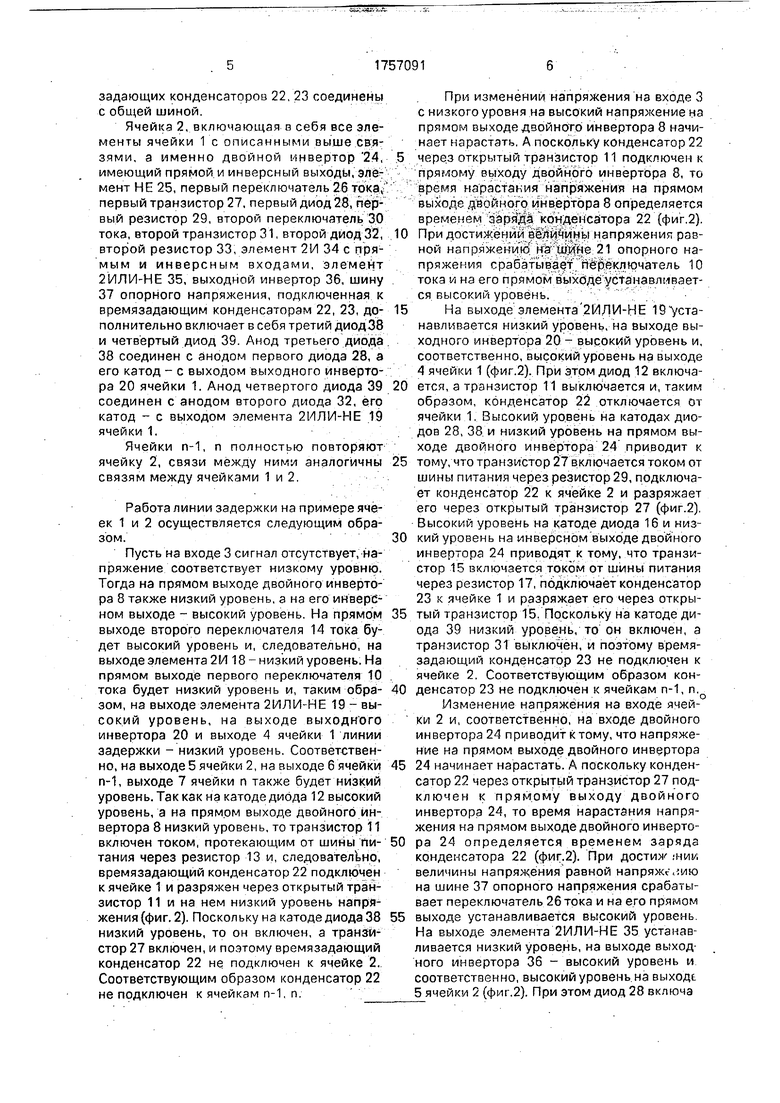

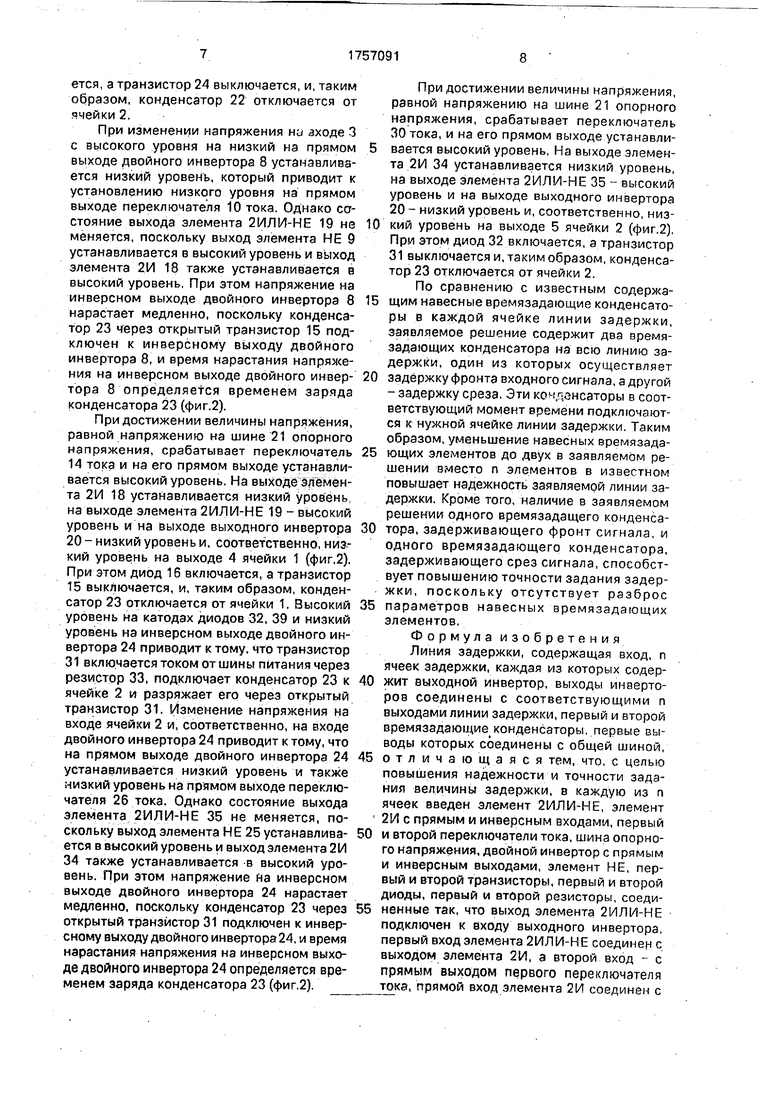

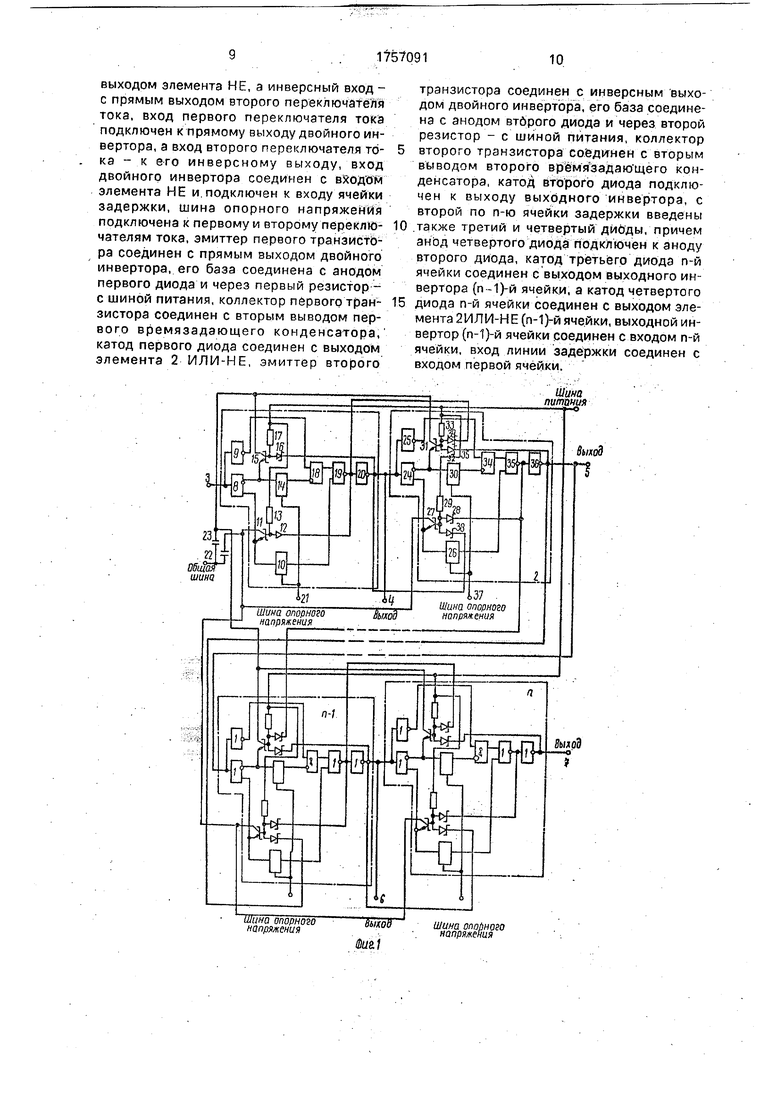

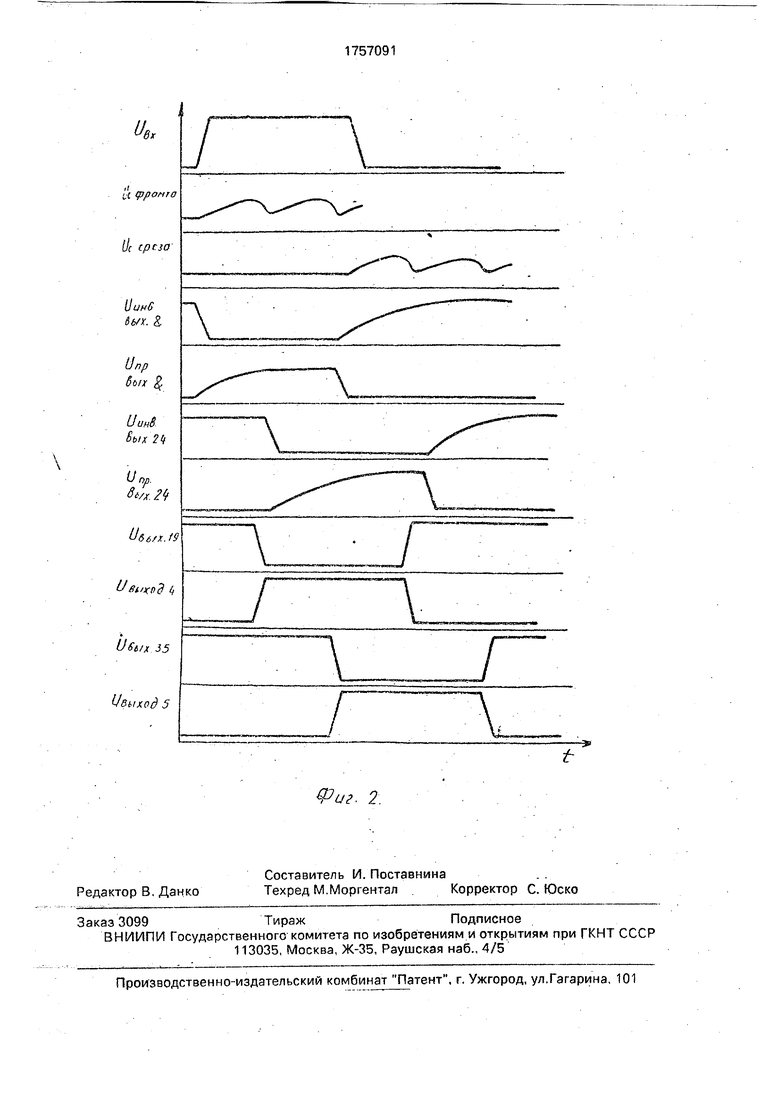

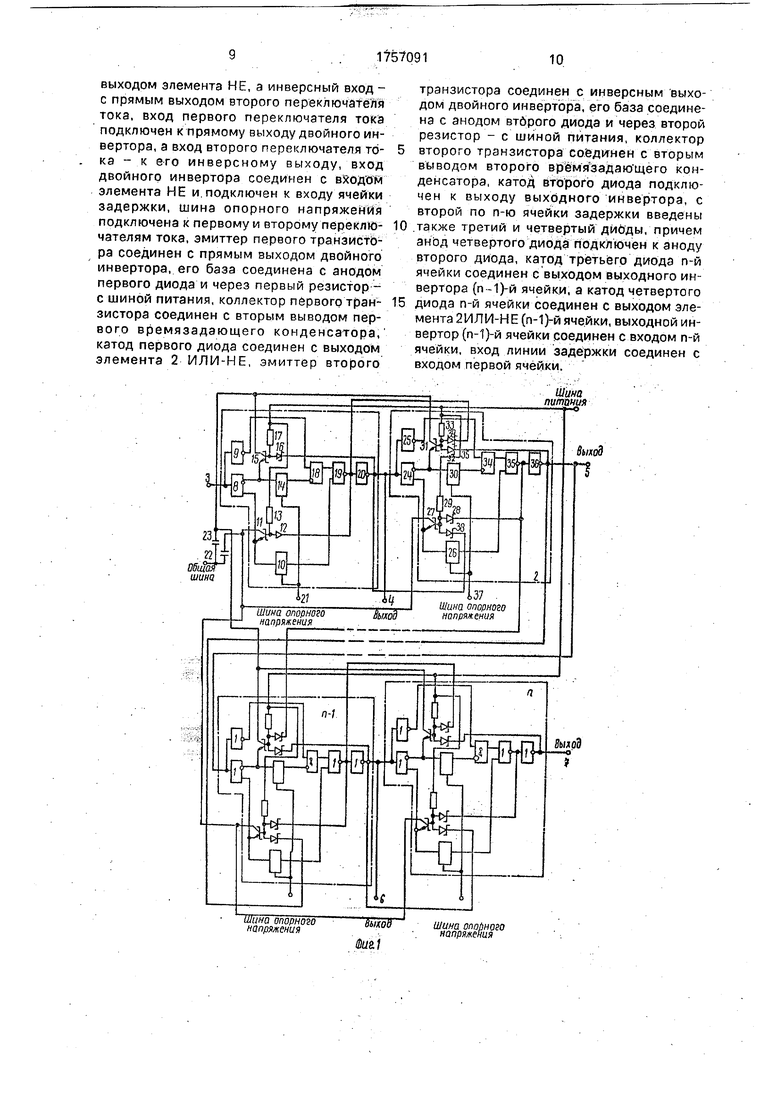

На фиг. 1 представлена схема линии задержки; на фиг. 2 - эпюры напряжений, поясняющие работу схемы.

Линия задержки включает в себя п последовательно соединенных ячеек задержки: выход ячейки 1 соединен с входом

ячейки 2, выход ячейки 2-е входом ячейки п-1, выход ячейки п-1 - с входом ячейки п. Вход ячейки 1 образует вход линии 3 задержки. Выходы ячеек 1, 2, п-1, п задержки образуют соответствующие выходы 4-7 линии задержки. Ячейка 1 состоит из двойного инвертора 8, имеющего прямой и инверсный выходы, вход которого соединен с входом элемента НЕ 9 и образует вход ячейки задержки, прямой выход двойного инвертора 8 соединен с входом первого переключателя 10 тока и эмиттером первого транзистора 11, база которого подключена к аноду первого диода 12 и через первый резистор 13 к шине питания, инверсный выход двойного инвертора соединен с входом второго переключателя 14 тока и эмиттером второго транзистора 15, база которого подключена к аноду второго диода 16 и через второй резистор 17 к шине питания Прямой

выход второго переключателя 14 тока подключен к инверсному входу элемента 2И 18, прямой вход которого соединен с выходом элемента НЕ 9. Выход элемента 2И 18 соединен с первым входом элемента 2ИЛИ-НЕ

19, второй вход которого соединен с прямым выходом первого переключателя 10 тока. Выход элемента 2ИЛИ-НЕ 19 соединен с входом выходного инвертора 20 и катодом первого диода 12, выход выходного инвертора 20 соединен с катодом второго диода 1 б и образует выход ячейки задержки. Шина 21 опорного напряжения подключена к первому 10 и второму 14 переключателям тока. Ячейка 1 подключена к времязадающим

конденсаторам 22, 23. Коллектор первого транзистора 11 соединен с вторым выводом первого времязадающего конденсатора 22, коллектор второго транзистора 15 - с вторым выводом второго времязадающего конденсатора 23, первые выводы времязадающих конденсаторов 22, 23 соединены с общей шиной.

Ячейка 2, включающая в себя все элементы ячейки 1 с описанными выше связями, а именно двойной инвертор 24, имеющий прямой и инверсный выходы, элемент НЕ 25, первый переключатель 26 тока, первый транзистор 27, первый диод 28, первый резистор 29, второй переключатель 30 тока, второй транзистор 31, второй диод 32, второй резистор 33, элемент 2И 34 с прямым и инверсным входами, элемент 2ИЛИ-НЕ 35, выходной инвертор 36, шину

37опорного напряжения, подключенная к времязадающим конденсаторам 22, 23, дополнительно включает в себя третий диод38 и четвертый диод 39. Анод третьего диода

38соединен с анодом первого диода 28, а его катод - с выходом выходного инвертора 20 ячейки 1. Анод четвертого диода 39 соединен с анодом второго диода 32, его катод - с выходом элемента 2ИЛИ-НЕ 19 ячейки 1.

Ячейки n-1, n полностью повторяют ячейку 2, связи между ними аналогичны связям между ячейками 1 и 2.

Работа линии задержки на примере ячеек 1 и 2 осуществляется следующим образом.

Пусть на входе 3 сигнал отсутствует, напряжение соответствует низкому уровню. Тогда на прямом выходе двойного инвертора 8 также низкий уровень, а на его инверсном выходе - высокий уровень. На прямом выходе второго переключателя 14 тока будет высокий уровень и, следовательно, на выходе элемента 2И 18 - низкий уровень. На прямом выходе первого переключателя 10 тока будет низкий уровень и, таким образом, на выходе элемента 2ИЛИ-НЕ 19 - высокий уровень, на выходе выходного инвертора 20 и выходе 4 ячейки 1 линии задержки - низкий уровень. Соответственно, на выходе 5 ячейки 2, на выходе 6 ячейки п-1, выходе 7 ячейки n также будет низкий уровень. Так как на катоде диода 12 высокий уровень, а на прямом выходе двойного инвертора 8 низкий уровень, то транзистор 11 включен током, протекающим от шины питания через резистор 13 и, следовательно, времязадающий конденсатор 22 подключен к ячейке 1 и разряжен через открытый транзистор 11 и на нем низкий уровень напряжения (фиг. 2). Поскольку на катоде диода 38 низкий уровень, то он включен, а транзистор 27 включен, и поэтому времязадающий конденсатор 22 не подключен к ячейке 2. Соответствующим образом конденсатор 22 не подключен к ячейкам n-1, n

При изменении напряжения на входе 3 с низкого уровня на высокий напряжение на прямом выходе двойного инвертора 8 начинает нарастать, А поскольку конденсатор 22

5 через открытый транзистор 11 подключен к прямому выходу двойного инвертора 8, то время нарастания напряжения на прямом выходе двойного инвертора 8 определяется временем заряда Конденсатора 22 (фиг.2).

0 При достижении величины напряжения равной напряжению ка шине 21 опорного напряжения срабатывает переключатель 10 тока и на его прямом выходе устанавливается высокий уровень.

5 На выходе элемента 2ИЛИ-НЕ 19VCT3- навливается низкий уровень, на выходе выходного инвертора 20 - высокий уровень и, соответственно, высокий уровень на выходе

4ячейки 1 (фиг.2). При этом диод 12 включа- 0 ется, а транзистор 11 выключается и, таким

образом, конденсатор 22 отключается от ячейки 1 Высокий уровень на катодах диодов 28, 38 и низкий уровень на прямом выходе двойного инвертора 24 приводит к

5 тому, что транзистор 27 включается током от шины питания через резистор 29, подключает конденсатор 22 к ячейке 2 и разряжает его через открытый транзистор 27 (фиг.2) Высокий уровень на катоде диода 16 и низ0 кий уровень на инверсном выходе двойного инвертора 24 приводят к тому, что транзистор 15 включается током от шины питания через резистор 17, подключает конденсатор 23 к ячейке 1 и разряжает его через откры5 тый транзистор 15. Поскольку на катоде диода 39 низкий уровень, то он включен, а транзистор 31 выключен, и поэтому времязадающий конденсатор 23 не подключен к ячейке 2. Соответствующим образом кон0 денсатор 23 не подключен к ячейкам п-1, п. Изменение напряжения на входе ячейки 2 и, соответственно, на входе двойного инвертора 24 приводит к тому, что напряжение на прямом выходе двойного инвертора

5 24 начинает нарастать. А поскольку конденсатор 22 через открытый транзистор 27 под- ключен к прямому выходу двойного инвертора 24, то время нарастания напряжения на прямом выходе двойного инверто0 ра 24 определяется временем заряда конденсатора 22 (фиг.2). При достиж ;нии величины напряжения равной напряжению на шине 37 опорного напряжения срабатывает переключатель 26 тока и на его прямом

5 выходе устанавливается высокий уровень На выходе элемента 2ИЛИ-НЕ 35 устанавливается низкий уровень, на выходе выход ного инвертора 36 - высокий уровень и соответственно, высокий уровень на выходе

5ячейки 2 (фиг .2). При этом диод 28 включэ

ется, а транзистор 24 выключается, и, таким образом, конденсатор 22 отключается от ячейки 2,

При изменении напряжения на зходе 3 с высокого уровня на низкий на прямом выходе двойного инвертора 8 устанавливается низкий уровень, который приводит к установлению низкого уровня на прямом выходе переключателя 10 тока. Однако сег- стояние выхода элемента 2ИЛИ-НЕ 19 не меняется, поскольку выход элемента НЕ 9 устанавливается в высокий уровень и выход элемента 2И 18 также устанавливается в высокий уровень, При этом напряжение на инверсном выходе двойного инвертора 8 нарастает медленно, поскольку конденсатор 23 через открытый транзистор 15 подключен к инверсному выходу двойного инвертора 8, и время нарастания напряжения на инверсном выходе двойного инвертора 8 определяется временем заряда конденсатора 23 (фиг.2).

При достижении величины напряжения, равной напряжению на шине 21 опорного напряжения, срабатывает переключатель

14тока и на его прямом выходе устанавливается высокий уровень. На выходе элемента 2И 18 устанавливается низкий уровень на выходе элемента 2ИЛИ-НЕ 19 - высокий уровень и на выходе выходного инвертора 20 - низкий уровень и, соответственно, низкий уровень на выходе 4 ячейки 1 (фиг,2). При этом диод 16 включается, а транзистор

15выключается, и, таким образом, конденсатор 23 отключается от ячейки 1. Высокий уровень на катодах диодов 32, 39 и низкий уровень на инверсном выходе двойного инвертора 24 приводит к тому, что транзистор 31 включается током от шины питания через резистор 33, подключает конденсатор 23 к ячейке 2 и разряжает его через открытый транзистор 31. Изменение напряжения на входе ячейки 2 и, соответственно, на входе двойного инвертора 24 приводит к тому, что на прямом выходе двойного инвертора 24 устанавливается низкий уровень и также низкий уровень на прямом выходе переключателя 26 тока. Однако состояние выхода элемента 2ИЛИ-НЕ 35 не меняется, поскольку выход элемента НЕ 25 устанавливается в высокий уровень и выход элемента 2И 34 также устанавливается в высокий уровень. При этом напряжение на инверсном выходе двойного инвертора 24 нарастает медленно, поскольку конденсатор 23 через открытый транзистор 31 подключен к инверсному выходу двойного инвертора 24, и время нарастания напряжения на инверсном выходе двойного инвертора 24 определяется временем заряда конденсатора 23 (фиг,2).

При достижении величины напряжения, равной напряжению на шине 21 опорного напряжения, срабатывает переключатель

30тока, и на его прямом выходе устанавли- вается высокий уровень. На выходе элемента 2И 34 устанавливается низкий уровень, на выходе элемента 2ИЛИ-НЕ 35 - высокий уровень и на выходе выходного инвертора 20 - низкий уровень и, соответственно, низ0 кий уровень на выходе 5 ячейки 2 (фиг.2), При этом диод 32 включается, а транзистор

31выключается и, таким образом, конденсатор 23 отключается от ячейки 2.

По сравнению с известным содержэ5 щим навесные времязадающие конденсаторы в каждой ячейке линии задержки, заявляемое решение содержит два время- задающих конденсатора на всю линию задержки, один из которых осуществляет

0 задержку фронта входного сигнала, а другой - задержку среза. Эти компенсаторы в соответствующий момент времени подключаются к нужной ячейке линии задержки. Таким образом, уменьшение навесных времязада5 ющих элементов до двух в заявляемом решении вместо п элементов в известном повышает надежность заявляемой линии задержки. Кроме того, наличие в заявляемом решении одного времязадащего конденса0 тора, задерживающего фронт сигнала, и одного времязадающего конденсатора, задерживающего срез сигнала, способствует повышению точности задания задержки, поскольку отсутствует разброс

5 параметров навесных времязадающих элементов,

Формула изобретения Линия задержки, содержащая вход, п ячеек задержки, каждая из которых содер0 жит выходной инвертор, выходы инверторов соединены с соответствующими п выходами линии задержки, первый и второй времязадающие конденсаторы, первые выводы которых соединены с общей шиной,

5 отличающаяся тем, что, с целью повышения надежности и точности задания величины задержки, в каждую из п ячеек введен элемент 2ИЛИ-НЕ, элемент 1 2И с прямым и инверсным входами, первый

0 и второй переключатели тока, шина опорного напряжения, двойной инвертор с прямым и инверсным выходами, элемент НЕ, первый и второй транзисторы, первый и второй диоды, первый и второй резисторы, соеди5 ненные так, что выход элемента 2ИЛИ-НЕ подключен к входу выходного инвертора, первый вход элемента 2ИЛИ-НЕ соединен с выходом элемента 2И, а второй вход - с прямым выходом первого переключателя тока, прямой вход элемента 2И соединен с

выходом элемента НЕ, а инверсный вход - с прямым выходом второго переключателя тока, вход первого переключателя тока подключен к прямому выходу двойного инвертора, а вход второго переключателя тока - к его инверсному выходу, вход двойного инвертора соединен с входим элемента НЕ и подключен к входу ячейки задержки, шина опорного напряжения подключена к первому и второму переключателям тока, эмиттер первого транзистора соединен с прямым выходом двойного инвертора, его база соединена с анодом первого диода и через первый резистор - с шиной питания, коллектор первого транзистора соединен с вторым выводом первого времязадающего конденсатора, катод первого диода соединен с выходом элемента 2 ИЛИ-НЕ, эмиттер второго

транзистора соединен с инверсным выходом двойного инвертора, его база соединена с анодом второго диода и через второй резистор - с шиной питания, коллектор

второго транзистора соединен с вторым выводом второго времязадающего конденсатора, катод второго диода подключен к выходу выходного инвертора, с второй по п-ю ячейки задержки введены

также третий и четвертый диоды, причем анод четвертого диода подключен к аноду второго диода, катод третьего диода п-й ячейки соединен с выходом выходного инвертора (п 1)-й ячейки, а катод четвертого

диода n-й ячейки соединен с выходом элемента 2ИЛИ-Н Е (п-1)-й ячейки, выходной инвертор (п-1)-й ячейки соединен с входом п-й ячейки, вход линии задержки соединен с входом первой ячейки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Линия задержки | 1990 |

|

SU1750039A1 |

| Устройство задержки | 1989 |

|

SU1793535A1 |

| ЭЛЕКТРОННЫЙ ОКТАН-КОРРЕКТОР | 1995 |

|

RU2117818C1 |

| Электронная приставка к транзисторной системе зажигания | 1991 |

|

SU1800086A1 |

| БИПОЛЯРНЫЙ ГЕНЕРАТОР ИОНОВ | 2005 |

|

RU2303751C2 |

| Универсальная тиристорная система зажигания | 1990 |

|

SU1781447A1 |

| Одновибратор | 1984 |

|

SU1167706A1 |

| Шкальный индикатор | 1990 |

|

SU1767339A1 |

| БИПОЛЯРНЫЙ ГЕНЕРАТОР ИОНОВ | 2005 |

|

RU2287744C1 |

| ЭЛЕКТРОННЫЙ КОРРЕКТОР СИСТЕМЫ ЗАЖИГАНИЯ | 1991 |

|

RU2029883C1 |

Изобретение относится к микроэлектронике и вычислительной технике, а именно к схемам линий задержки, широко применяемым для обеспечения синхронизации между электронными системами различного назначения. Целью изобретения является повышение надежности и точности задания величины задержки. Линия задержки имеет п ячеек задержки, каждая из которых содержит выходной инвертор, первый и второй времязадающие конденсаторы. В каждую ячейку введены элемент 2ИЛИ-НЕ, элемент 2И с прямым и инверсным входами, первый и второй переключатели тока, шина опорного напряжения, двойной инвертор с прямым и инверсным выходами, элемент НЕ, первый и второй транзисторы, первый и второй диоды, первый и второй резисторы. По сравнению с прототипом, имеющим навесные времязадающие конденсаторы в каждой ячейке линии задержки, предлагаемое устройство содержит два времязадающих конденсатора на всю линию задержки, один из которых осуществляет задержку фронта входного сигнала, а другой - задержку среза. 2 ил. (Л

05щая шина

шина опорного напряжения

Шина питания

8ыШ Фи&1

Шит опорного напряжения

| DATA Book | |||

| Digital Integrated Circuits, edition | |||

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

| ПЛУГ С ВРАЩАЮЩИМИСЯ РАБОЧИМИ ПОВЕРХНОСТЯМИ | 1925 |

|

SU432A1 |

Авторы

Даты

1992-08-23—Публикация

1990-06-11—Подача