Изобретение относится к автоматике и вычислительной технике и предназначено для преобразования десятичного кода в двоичный код.

Известен шифратор, преобразующий восьмиразрядный десятичный код в трехразрядный двоичный код, выполненный на элементах И-НЕ, на выходе имеющий три RS-триггера, а также дополнительную логику.

Недостатки этого шифратора следующие.

Он не допускает произвольных значений входного кода, так как в этом случае будет исключен выходной код.

Выходные сигналы должны поступать на входы шифратора последовательно от первого к второму и так далее до восьмого входа с перекрытием по времени соседних каналов.

Возможны произвольные срабатывания триггеров от помех, возникающих в выходных цепях шифратора, так как выходы R триггеров являются также и его входами.

Известен шифратор десятичного кода в двоично-десятичный код, выполненный на пйти элементах 2И-НЕ, двух элементах 4И- НЕ и одном элементе 5И-НЕ.

Основным недостатком этого преобразователя является его низкая помехозащищенность.

При одновременном возбуждении, вух и более входов данного шифратора состояние его выходов неопределенно.

Цель изобретения - повышение помехо- устойчивости шифратора - достигается за счет блокировки его выходов при одновременном воздействии сигналов на два или более входа.

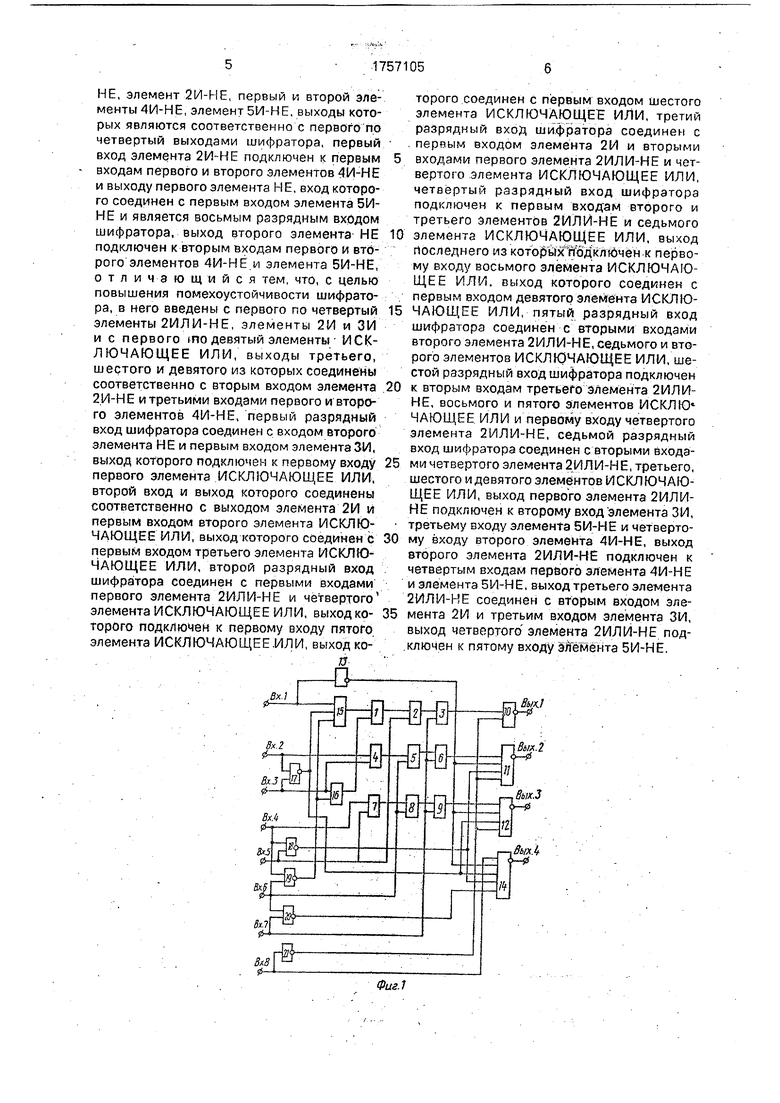

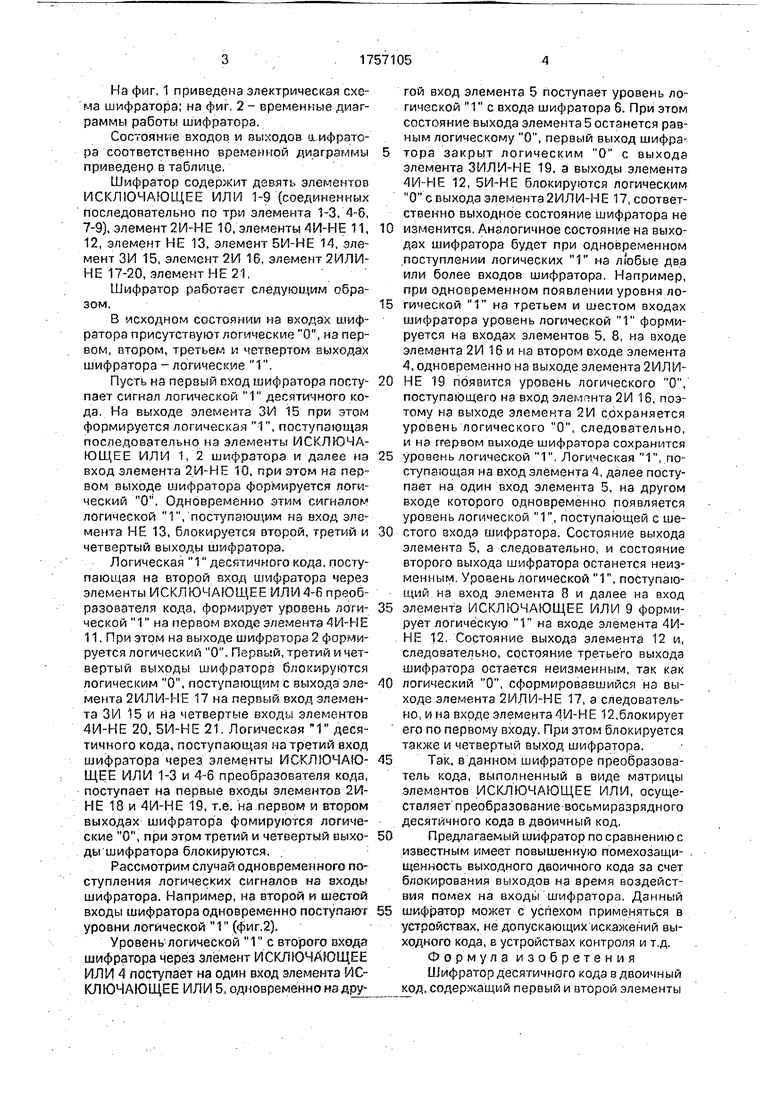

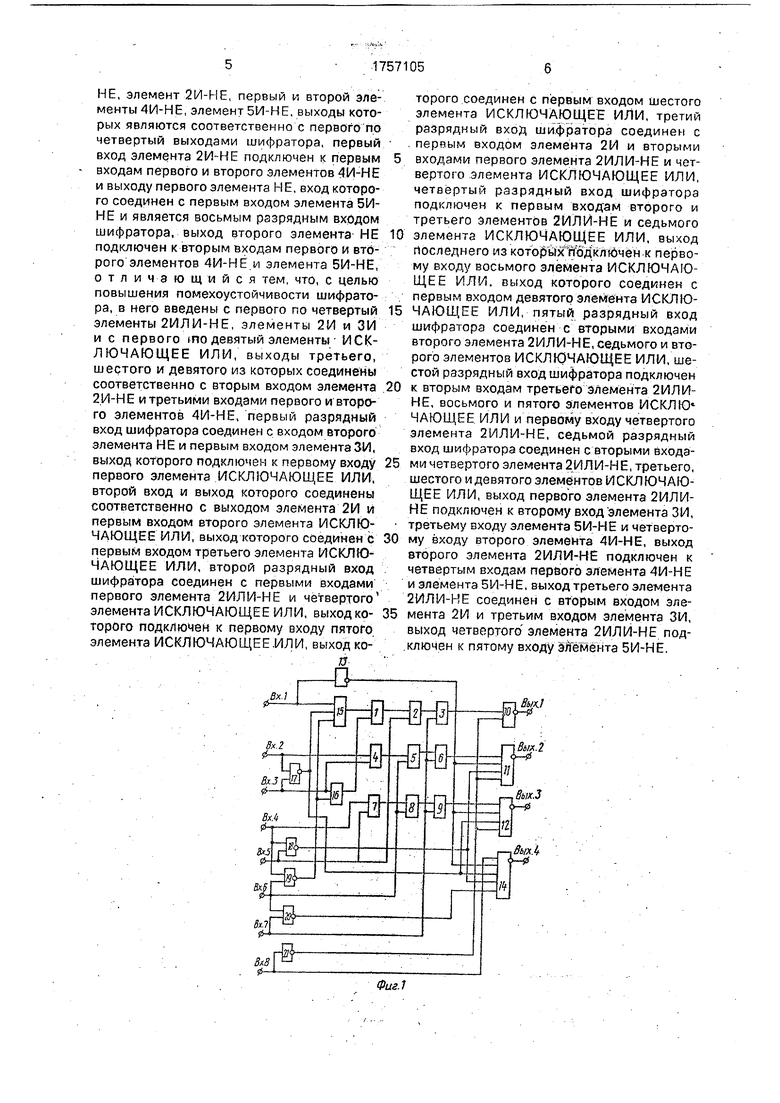

На фиг, 1 приведена электрическая схема шифратора; на фиг, 2 - временные диаграммы работы шифратора.

Состоянье входов и выходов аифрато- ра соответственно временной диаграммы приведено в таблице,

Шифратор содержит девять элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 1-9 (соединенных последовательно по три элемента 1-3, 4-6, 7-9), элемент 2И-НЕ 10, элементы 4И-НЕ 11, 12, элемент НЕ 13, элемент 5И-НЕ 14, элемент ЗИ 15, элемент 2И 16, элемент 2ИЛИ- НЕ 17-20, элемент НЕ 21,

Шифратор работает следующим образом.

В исходном состоянии на входах шифратора присутствуют логические О, на первом, втором, третьем и четвертом выходах шифратора -логические 1.

Пусть на первый сход шифратора поступает сигнал логической 1 десятичного кода, На выходе элемента 15 при этом формируется логическая 1, поступающая последовательно на элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 1, 2 шифратора и далее на вход элемента 2И-НЕ 10, при этом на первом выходе шифратора формируется логический О. Одновременно этим сигналом логической 1, поступающим нз вход элемента НЕ 13, блокируется второй, третий и четвертый выходы шифратора.

Логическая 1 десятичного кода, поступающая на второй вход шифратора через элементы ИСКЛЮЧАЮЩЕЕ ИЛИ4-6 преобразователя кода, формирует уровень логической 1 на первом входе элемента 4И-НЕ 11. При этом на выходе шифратора 2 формируется логический О. Первый, третий и четвертый выходы шифратора блокируются логическим О, поступающим с выхода элемента 2ИЛИ-НЕ 17 на перпый вход элемента 3И 15 и на четвертые входы элементов 4И-НЕ 20, 5И-НЕ 21. Логическая Г десятичного кода, поступающая на третий вход шифратора через элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 1-3 и 4-6 преобразователя кода, поступает на первые входы элементов 2И- НЕ 18 и 4И-НЕ 19, т.е. на первом и втором выходах шифратора фомируются логические О, при этом третий и четвертый выходы шифратора блокируются.

Рассмотрим случай одновременного поступления логических сигналов на эходь шифратора. Например, на второй и шестой входы шифратора одновременно поступают уровни логической 1 (фиг,2).

Уровень логической 1 с второго входа шифратора через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4 поступает на один вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5, одновременно на дру

той вход элемента 5 поступает уровень логической 1 с входа шифратора 6. При этом состояние выхода элемента 5 останется равным логическому О, первый выход шифратора закрыт логическим О с выхода элемента ЗИЛ И-НЕ 19, а выходы элемента 4И-НЕ 12, 5И-НЕ блокируются логическим О с выхода элемента 2ИЛИ-НЕ 17, соответственно выходное состояние шифратора не

0 изменится, Аналогичное состояние на выходах шифратора будет при одновременном поступлении логических 1 на любые два или более входов шифратора. Например, при одновременном появлении уровня ло5 гической 1 на третьем и шестом входах шифратора уровень логической 1 формируется на входах элементов 5, 8, на входе элемента 2И 16 и на втором входе элемента 4, одновременно на выходе элемента 2ИЛ И0 НЕ 19 появится уровень логического О, поступающего на вход элемента 2И 16, поэтому на выходе элемента 2И сохраняется уровень логического О, следовательно, и на ггервом выходе шифратора сохранится

5 уровень логической 1. Логическая 1, поступающая на вход элемента 4, далее поступает на один вход элемента 5, на другом входе которого одновременно появляется уровень логической 1, поступающей с ше0 сто го входа шифратора. Состояние выхода элемента 5, а следовательно, и состояние второго выхода шифратора останется неизменным. Уровень логической 1, поступающий на вход элемента 8 и далее на вход

5 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9 формирует логическую 1 на входе элемента 4И- НЕ 12. Состояние выхода элемента 12 и, следовательно, состояние третьего выхода шифратора остается неизменным, так как

0 логический О, сформировавшийся на выходе элемента 2 ИЛ И-НЕ 17, а следовательно, и на входе элемента 41/1-НЕ 12,блокирует его по первому входу. При этом блокируется также и четвертый выход шифратора.

5 Так, в данном шифраторе преобразователь кода, выполненный в виде матрицы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, осуществляет преобразование восьмиразрядного десятичного кода в двоичный код,

0 Предлагаемый шифратор по сравнению с известным имеет повышенную помехозащищенность выходного двоичного кода за счет блокирования выходов на время воздействия помех на входы шифратора. Данный

5 шифратор может с успехом применяться в устройствах, не допускающих искажений выходного кода, в устройствах контроля и т.д. Формула изобретения Шифратор десятичного кода в двоичный код, содержащий первый и второй элементы

НЕ, элемент 2И-НЕ, первый и второй элементы 4И-НЕ, элемент 5И-НЕ, выходы которых являются соответственно с первого по четвертый выходами шифратора, первый вход элемента 2И-НЕ подключен к первым входам первого и второго элементов 4И-НЕ и выходу первого элемента НЕ, вход которого соединен с первым входом элемента 5И- НЕ и является восьмым разрядным входом шифратора, выход второго элемента НЕ подключен к вторым входам первого и второго элементов 4И-НЕ и элемента 5И-НЕ, отличающийся тем, что, с целью повышения помехоустойчивости шифратора, в него введены с первого по четвертый элементы 2ИЛИ-НЕ, элементы 2И и ЗИ и с первого то девятый элементы - ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы третьего, шестого и девятого из которых соединены соответственно с вторым входом элемента 2И-НЕ и третьими входами первого и второго элементов 4И-НЕ, первый разрядный вход шифратора соединен с входом второго элемента НЕ и первым входом элемента ЗИ, выход которого подключен к первому входу первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход и выход которого соединены соответственно с выходом элемента 2И и первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй разрядный вход шифратора соединен с первыми входами первого элемента 2ИЛИ-НЕ и четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход ко- торого подключен к первому входу пятого элемента ИСКЛЮЧАЮЩЕЕ.ИЛИ, выход ко0

торого соединен с первым входом шестого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, третий разрядный вход шифратора соединен с перпым входом элемента 2И и вторыми входами первого элемента 2ИЛИ-НЕ и четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, четвертый разрядный вход шифратора подключен к первым входам второго и третьего элементов 2ИЛИ-НЕ и седьмого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход последнего из которых подключен к первому входу восьмого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом девятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, пятый разрядный вход шифратора соединен с вторыми входами второго элемента 2ИЛИ-НЕ, седьмого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, шестой разрядный вход шифратора подключен к вторым входам третьего элемента 2ИЛИ- НЕ, восьмого и пятого элементов ИСКЛК ЧАЮЩЕЕ ИЛИ и первому входу четвертого элемента 2ИЛИ-НЕ, седьмой разрядный вход шифратора соединен с вторыми входами четвертого элемента 2ИЛИ-НЕ, третьего, шестого и девятого элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выход первого элемента 2ИЛИ- НЕ подключен к второму вход элемента ЗИ, третьему входу элемента 5И-НЕ и четвертому входу второго элемента 4И-НЕ, выход второго элемента 2ИЛИ-НЕ подключен к четвертым входам первого элемента 4И-НЕ и элемента 5И-НЕ, выход третьего элемента 2ИЛИ-НЕ соединен с вторым входом элемента 2И и третьим входом элемента ЗИ, выход четвертого элемента 2ИЛИ-НЕ подключен к пятому входу эл емента 5И-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Малогабаритный цифровой твердомер | 1984 |

|

SU1359716A1 |

| Устройство для формирования пачек импульсов | 1991 |

|

SU1812617A1 |

| Функциональный преобразователь угла поворота вала в код | 1984 |

|

SU1218465A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Устройство для управления положением исполнительных элементов | 1983 |

|

SU1226413A2 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ПОРЯДКА ПРИ НОРМАЛИЗАЦИИ ЧИСЕЛ | 2017 |

|

RU2638724C1 |

| Электронные часы | 1985 |

|

SU1262445A1 |

| Реверсивный распределитель импульсов | 1981 |

|

SU953728A1 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

| Устройство для измерения девиации частоты линейно-частотно-модулированного колебания | 1989 |

|

SU1711087A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики, управления и контроля. Цель изобретения - повышение помехоустойчивости. Логические сигналы десятичного кода, поступающие на входы, формируются в преобразователе, соединенном в виде матрицы из девяти элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, включенных по три элемента последовательно, в четырехразрядный двоичный код. При поступлении логических уровней на два или более входов на выходах шифратора формируется нулевой код, т.е. выходы блокируются. Блокировка выходов происходит и в то м случае, если в данный момент на этих выходах согласно алгоритму преобразователя нет информации. Для этого на входы шифратора включена дополнительная логика, управляющая его выходами. 2 ил.

Вых.1

| Шифратор | 1983 |

|

SU1127088A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Энергия, 1980, с | |||

| БОРОННАЯ РАМА-ЗИГЗАГ | 1914 |

|

SU683A1 |

Авторы

Даты

1992-08-23—Публикация

1990-11-26—Подача