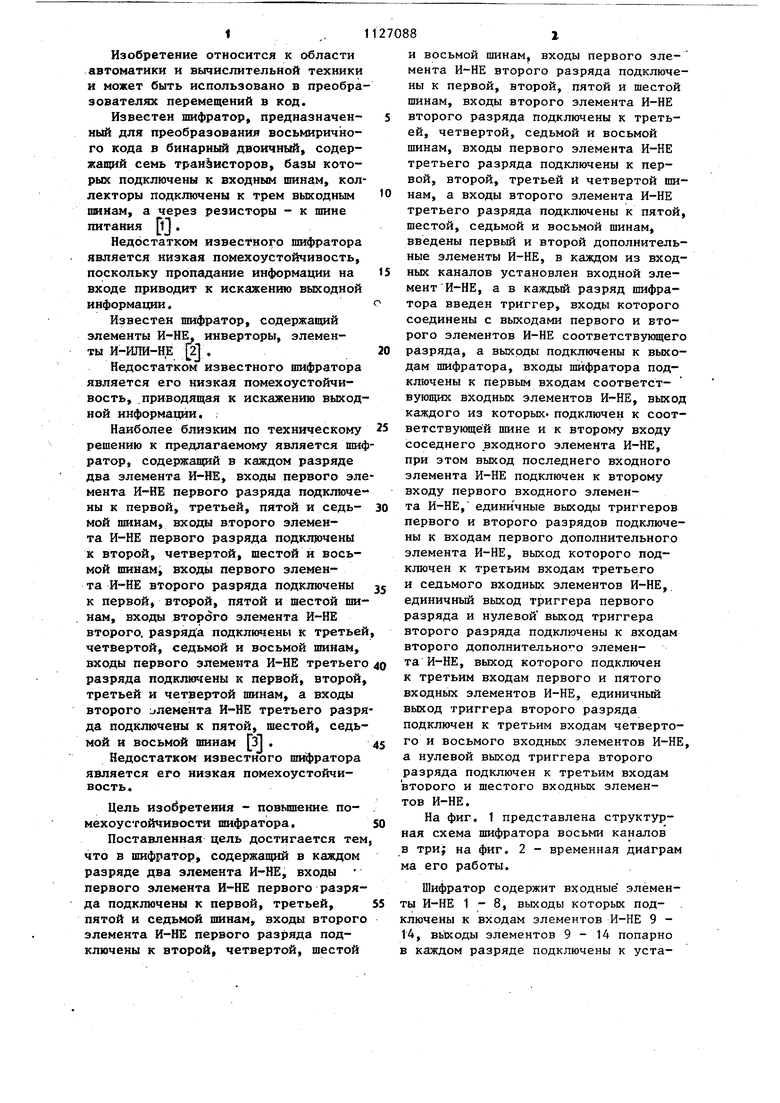

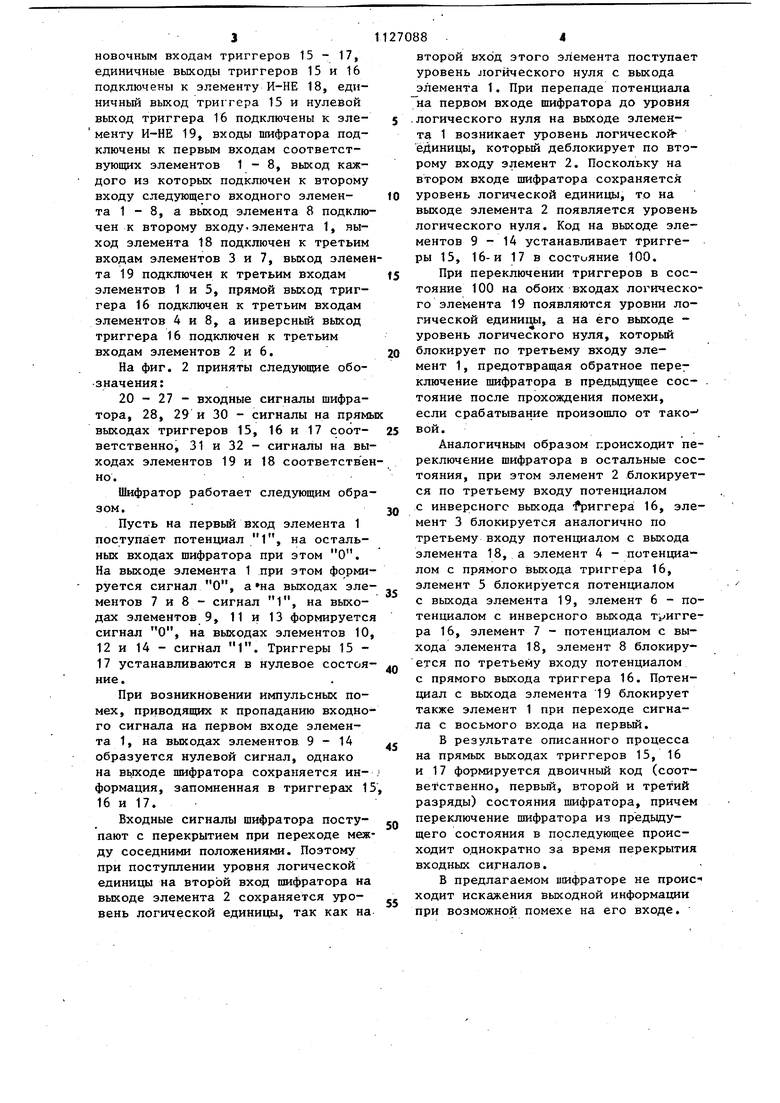

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в преобра зователях перемещений в код. Известен шифратор, предназначенный для преобразования восьмиричного кода в бинарный двоичный, содержащий семь транзисторов, базы которых подключены к входным шинам, коллекторы подключены к трем выходным шинам, а через резисторы - к шине питания tj . Недостатком известного шифратора является низкая помехоустойчивость, поскольку пропадание информации на входе приводит к искажению выходной информации. Известен шифратор, содержащий элементы И-НЕ, инверторы, элементы И-ИЛИ-НЕ 2 . Недостатком известного шифратора является его низкая помехоустойчивость, .приводящая к искажению выходной информации. . Наиболее близким по техническому решению к предлагаемому является шиф ратор, содержащий в каждом разряде два элемента И-НЕ, входы первого эле мента И-НЕ первого разряда подключены к первой, третьей, пятой и седьмой шинам, входы второго элемента И-НЕ первого разряда подключены к второй, четвертой, шестой и восьмой шинам, входы первого элемента И-НЕ второго разряда подключены к первой, второй, пятой и шестой шинам, входы второго элемента И-НЕ второго, разряда подключены к третьей четвертой, седьмой и восьмой шинам, входы первого элемента И-НЕ третьего разряда подключены к первой, второй третьей и четвертой шинам, а входы второго илемента И-НЕ третьего разря да подключены к пятой, шестой, седьмой и восьмой шинам з . Недостатком известного шифратора является его низкая помехоустойчивость. Цель изобретения - повьш1ение помехоустойчивости шифратора. Поставленная цель достигается тем что в шифратор, содержащий в каждом разряде два элемента И-НЕ, входы первого элемента И-НЕ первого разряда подключены к первой, третьей, пятой и седьмой шинам, входы второго элемента И-НЕ первого разряда подключены к второй, четвертой, шестой и восьмой шинам, входы первого злемента И-НЕ второго разряда подключены к первой, второй, пятой и шестой шинам, входы второго элемента И-НЕ второго разряда подключены к третьей, четвертой, седьмой и восьмой шинам, входы первого элемента И-НЕ третьего разряда подключены к первой, второй, третьей и четвертой шинам, а входы второго элемента И-НЕ третьего разряда подключены к пятой, шестой, седьмой и восьмой шинам, введены первый и второй дополнительные элементы И-НЕ, в каждом из входных каналов установлен входной элемент И-НЕ, а в каждый разряд шифратора введен триггер, входы которого соединены с выходами первого и второго элементов И-НЕ соответствующего разряда, а выходы подключены к выходам шифратора, входы шифратора подключены к первым входам соответствующих входных элементов И-НЕ, выход каждого из которых, подключен к соответствующей шине и к второму входу соседнего входного элемента И-НЕ, при этом выход последнего входного элемента И-НЕ подключен к второму входу первого входного элемента И-НЕ, единичные выходы триггеров первого и второго разрядов подключены к входам первого дополнительного элемента И-НЕ, выход которого подключен к третьим входам третьего и седьмого входных элементов И-НЕ, единичный выход триггера первого разряда и нулевой выход триггера второго разряда подключены к входам второго дополнительного элемента И-НЕ, выход которого подключен к третьим входам первого и пятого входных элементов И-НЕ, единичный выход триггера второго разряда подключен к третьим входам четвертого и восьмого входных элементов И-НЕ, а нулевой выход триггера второго разряда подключен к третьим входам ВТОРОГО и шестого входных элементов И-НЕ. На фиг. 1 представлена структурная схема шифратора восьми каналов в три; на фиг. 2 - временная диаграм а его работы. Шифратор содержит входные элемены И-НЕ 1-8, выходы которых подлючены к входам элементов И-НЕ 9 14, вькоды элементов 9-14 попарно каждом разряде подключены к уста3новочным входам триггеров 15 - 17, единичные выходы триггеров 15 и 16 подключены к элементу И-НЕ 18, единичный выход триггера 15 и нулевой выход триггера 16 подключены к элементу И-НЕ 19, входы шифратора подключены к первым входам соответствующих элементов 1-8, выход каждого из которых подключен к второму входу следующего входного элемента 1 - 8, а выход элемента 8 подклю чен к второму входу.элемента 1, выход элемента 18 подключен к третьим входам элементов 3 и 7, выход элеме та 19 подключен к третьим входам элементов 1 и 5, прямой выход триггера 16 подключен к третьим входам элементов 4 и 8, а инверсньй выход триггера 16 подключен к третьим входам элементов 2 и 6. На фиг. 2 приняты следующие обозначения:20 - 27 - входные сигналы шифратора, 28, 29 и 30 - сигналы на прям выходах триггеров 15, 16 и 17 соответственно, 31 и 32 - сигналы на вы ходах элементов 19 и 18 соответстве но. Шифратор работает следующим обра зом. Пусть на первый вход элемента 1 поступа ет потенциал 1, на остальных входах шифратора при этом О. На выходе элемента 1 при этом форми руется сигнал О, выходах эле ментов 7 и 8 - сигнал 1, на выходах элементов 9, 11 и 13 формируетс сигнал О, на выходах элементов 10 12 и 14 - сигнал 1. Триггеры 15 17 устанавливаются в нулевое состоя ние. При возникновении импульсных помех, приводящих к пропаданию входно го сигнала на первом входе элемента 1, на выходах элементов 9-14 образуется нулевой сигнал, однако на вьпсоде шифратора сохраняется информация, запомненная в триггерах 1 16 и 17. Входные сигналы шифратора поступают с перекрытием при переходе меж ду соседними положениями. Поэтому при поступлении уровня логической единицы на второй вход шифратора на выходе элемента 2 сохраняется уровень логической единицы, так как на 88 второй вход этого элемента поступает уровень логического нуля с выхода элемента 1. При перепаде потенциала на первом входе шифратора до уровня логического нуля на выходе элемента 1 возникает зфовень логическойёДиницы, который деблокирует по второму входу элемент 2. Поскольку на втором входе шифратора сохраняется уровень логической единицы, то на выходе элемента 2 появляется уровень логического нуля. Код на выходе элементов 9-14 устанавливает триггеры 15, 16-и 17 в состояние 100. При переключении триггеров в состояние 100 на обоих входах логического элемента 19 появляются уровни логической единицы, а на его выходе уровень логического нуля, который блокирует по третьему входу элемент 1, предотвращая обратное переключение шифратора в предьщущее сое- . тояние после прохождения помехи, если срабатывание произошло от тако- вой. Аналогичным образом происходит переключение шифратора в остальные состояния, при этом элемент 2 блокируется по третьему входу потенциалом с инверсного выхода триггера 16, элемент 3 блокируется аналогично по третьему входу потенциалом с выхода элемента 18, а элемент 4 - потенциалом с прямого выхода триггера 16, элемент 5 блокируется потенциалом с выхода элемента 19, элемент 6 - потенциалом с инверсного выхода триггера 16, элемент 7 - потенциалом с выхода элемента 18, элемент 8 блокируется по третьему входу потенциалом с прямого выхода триггера 16. Потенциал с выхода элемента 19 блокирует также элемент 1 при переходе сигнала с восьмого входа на первый. В результате описанного процесса на прямых выходах триггеров 15, 16 и 17 формируется двоичный код (соответственно, первый, второй и третий разряды) состояния шифратора, причем переключение шифратора из предыдущего состояния в последующее происходит однократно за время перекрытия входных сигналов. В предлагаемом шифраторе не проис- ходит искажения выходной информации при возможной помехе на его входе.

LJ

fm.2

LJ

LJ

| название | год | авторы | номер документа |

|---|---|---|---|

| Шифратор | 1986 |

|

SU1372626A1 |

| Устройство для контроля импульсных последовательностей | 1986 |

|

SU1338034A1 |

| Устройство для определения кратчайшего пути на графе | 1983 |

|

SU1134944A1 |

| Устройство для селекции изображений объектов | 1986 |

|

SU1464183A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Счетчик с накоплением | 1985 |

|

SU1269254A1 |

| Однотактный кольцевой счетчик единичного кода | 1981 |

|

SU1003359A1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2262735C1 |

| Устройство для синхронизации импульсов | 1980 |

|

SU940285A1 |

| Устройство для передачи и приема дискретной информации | 1990 |

|

SU1807579A1 |

ШИФРАТОР, содержащий в каждом разряде два элемента И-НЕ, входы первого элемента И-НЕ первого разряда подключены к первой, третьей, пятой и седьмой шинам, входы второго элемента И-НЕ первого разряда подключены к второй, четвертой, шестой и восьмой шинам, входы первого элемента И-НЕ второго разряда подключены к первой, второй, пятой и шестой шинам, входы второго элемента И-НЕ второго подключены к третьей, четвертой, седьмой и восьмой шинам, входы первого эле- мента И-НЕ третьего разряда подключены к первой, второй, третьей и четвертой шинам, а входы второго элемента И-НЕ третьего разряда подключены к пятой, шестой, седьмой и восьмой шинам, отличающийс я тем, что, с целью Повышения помехоустойчивости шифратора, в него введены первый и второй дополнильные элементы И-НЕ, в каждом из входных каналов установлен входной элемент И-НЕ, а в каждый разряд шифратора введен триггер, входы которого соединены с выходами первого и второго элементов И-НЕ соответствующего разряда, а выходь подключены к выходам шифратора, входы шифратора подключены к первым входам соответствующих входных элементов И-НЕ, выход каждого из которых подключен к соответствующей шине и к второму входу соседнего входного элемента И-НЕ, при этом выход последнего входного элемента И- НЕ подключен к второму ду первого входного элемента И-НЕ, единичные выходы триггеров первого и второго разрядов подключены к вхо§ дам первого дополнительного элемента И-НЕ, выход которого подключен к третьим входам третьего и седьмого .входных элементов И-НЕ, единичный ю выход триггера первого разряда и нулевой выход триггера второго разряда :р подключены к входам второго дополниэо эо тельного элемента И-НЕ, выход которого подключен к третьим входам первого и пятого входных элементов И-НЕ, единичный выход триггера второго разряда подключен к третьим входам четвертого и восьмого входных элементов И-НЕ, а нулевой выход триггера второго разряда подключен к третьим входам второго и шестого входных элементов И-НЕ.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-11-30—Публикация

1983-07-13—Подача