}Г

1

(21)4728592/09 (22)09.08,89 (46)30.08.92. Бюл. № 32

(71)Таганрогский научно-исследовательский институт связи

(72)Л.Н.Мельников, Л.Н.Мельникова и А.В.Маргелов

(56)Авторское свидетельство СССР № 425386, кл. Н 04 L 7/00, 1975.

Авторское свидетельство СССР № 629643, кл. Н 04 L 1/00. 1978.

Авторское свидетельство СССР № 1-095427, кл. Н 04 L 7/00, 1985. (54) УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ОТ ИМПУЛЬСНЫХ ПОМЕХ

(57)Изобретение относится к радиотехнике и может использоваться в устройствах передачи дискретной информации. Цель изобретения - расширение функциональных возможностей устройства путем возможности перестройки параметров входного сигнала. Устройство для защиты от импульсных помех содержит счетный триггер 6, элемент И-НЕ 7, инвертор 3 и счетчик 4. Цель достигается введением двух регистров 9 и 10, мультиплексора 8, триггера управления 13 элементов И 14 и 15, блока сравнения 5 и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2, обеспечивающих запись кодов параметров от внешнего устройства управления, хранение и выдачу этих кодов на входы блока сравнения, ведущего поочередное сравнение их с текущими кодами длительности импульсов и длительности пауз. 2 ил

| название | год | авторы | номер документа |

|---|---|---|---|

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2002 |

|

RU2229157C2 |

| СПОСОБ ИЗМЕРЕНИЯ ВРЕМЕННОГО ИНТЕРВАЛА И ВАРИАНТЫ УСТРОЙСТВА ЕГО РЕАЛИЗУЮЩЕГО | 2016 |

|

RU2615159C2 |

| СПОСОБ ФОРМИРОВАНИЯ ИНФОРМАЦИОННОГО ПОЛЯ ЛАЗЕРНОЙ СИСТЕМЫ ТЕЛЕОРИЕНТАЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1996 |

|

RU2099730C1 |

| Цифровой измеритель параметров комплексного сопротивления | 1989 |

|

SU1732292A1 |

| УСТРОЙСТВО УПРЕЖДАЮЩЕГО ВРЕМЕННОГО СДВИГА ИМПУЛЬСОВ (ВАРИАНТЫ) | 2019 |

|

RU2718827C1 |

| Линейный интерполятор | 1987 |

|

SU1418751A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 2000 |

|

RU2170444C1 |

| Способ локальной радиотелефонной связи и система для его осуществления | 1991 |

|

SU1831767A3 |

| Устройство для реализации логических алгоритмов | 1990 |

|

SU1778763A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

;;

х| СЛ 00

OD

Ј

Изобретение относится к радиотехнике и может использоваться в различных устройствах передачи дискретной информации.

Известно устройство для защиты от импульсных помех, содержащее элемент задержки на счетных триггерах, два элемента И и счетный триггер. Устройство исключает импульсные помехи ложный импульс за счет селекции импульсов по длительности, Длительность импульсов помехи меньше, чем длительность информации импульсов. Однако это устройство не исключает помехи, возникающие при дроблении импульсов (пропадание импульса).

Известно устройство для защиты от импульсных помех, содержащее парный элемент задержки и элемент ИЛИ. Устройство исключает импульсные помехи Ложный импульс, Пропадание импульса, однако не обеспечивает подавление многократных импульсных помех обеих видов, потому то в нем отсутствуют элементы управления, возвращающие его в исходное состояние.

Известно устройство для защиты от импульсных помех, содержащее счетчик, выходы которого подключены к входам первого и второго элементов И-НЕ, выход первого элемента И-НЕ подключен к выходу устройства, к входу элемента ИЛ И-НЕ и к нулевому входу счетного триггера, тактовый вход которого подключен к входу третьего элемента И-НЕ и к выходу второго элемента И-НЕ, а нулевой и единичный выходы которого подключены соответственно к входам второго, третьего элементов И-НЕ и к входу четвертого элемента И-НЕ, другой вход которого подключен к входу устройства и к входу инвертора, выход которого подключен к входу третьего элемента И-НЕ, другой вход которого подключен к выходу четвертого элемента И-НЕ, а выход - к входу первого элемента И-НЕ и к входу сброса счетчика, тактовый вход которого подключен к тактовому входу устройства и к входам первого и второго олементоз И-НЕ.

В устройстве прототипа многовходовые элементы И-НЕ 3, 7 фиксируют значения минимальной длительности импульса tmin и минимальной длительности паузы tmin. Поэтому при изменении в процессе работы параметров входных информационных импульсов в устройстве невозможно оперативно изменить значения imini, tnmin, что является нeдocfaтl(oм.

Целью изобретения является расширение функциональных возможностей устройства путем возможности перестройки

параметров входных информационных импульсов.

Это достигается тем, что в устройство для защиты от импульсных помех, содержащее счетный триггер, элемент И-НЕ, инвертор и счетчик, тактовый вход которого является тактовым входом устройства, введены первый и второй регистры, первый и второй элементы И, триггер управления,

0 мультиплексор, блок сравнения и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, при этом выход элемента ИКЛГОЧАЮЩЕЕ ИЛИ через инвертор соединен с первым входом сброса счетчика, выходы которого соединены с пер5 вой группой входов блока сравнения, ко второй группе входов подключены выходы первого и второго регистров через мультиплексор, а выход блрка сравнения соединен с первым входом элемента И-НЕ и с

0 входом счетного триггера, единичый выход которого соединен со вторым входом элемента И-НЕ, с одним из входов элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с входом управления мультиплексора, прямой и инверсный

5 выходы триггера управления соединены через соответствующие элементы И со входами записи первого и второго регистров, информационные входы которых соединены между собой и являются входами кода

0 параметров устройства, управляющим входом которого является управляющий вход триггера управления, который соединен со вторыми входами элементов И, вход сигнала установки в исходное состояние триггера

5 управления соединен с соответствующим входом счетчика и с единичным входом счетного триггера и является входом сигнала установки в исходное состояние устройства, информационным входом которого являет0 ся другой вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, тактовый вход блока сравнения соединен с тактовым входом счетчика.

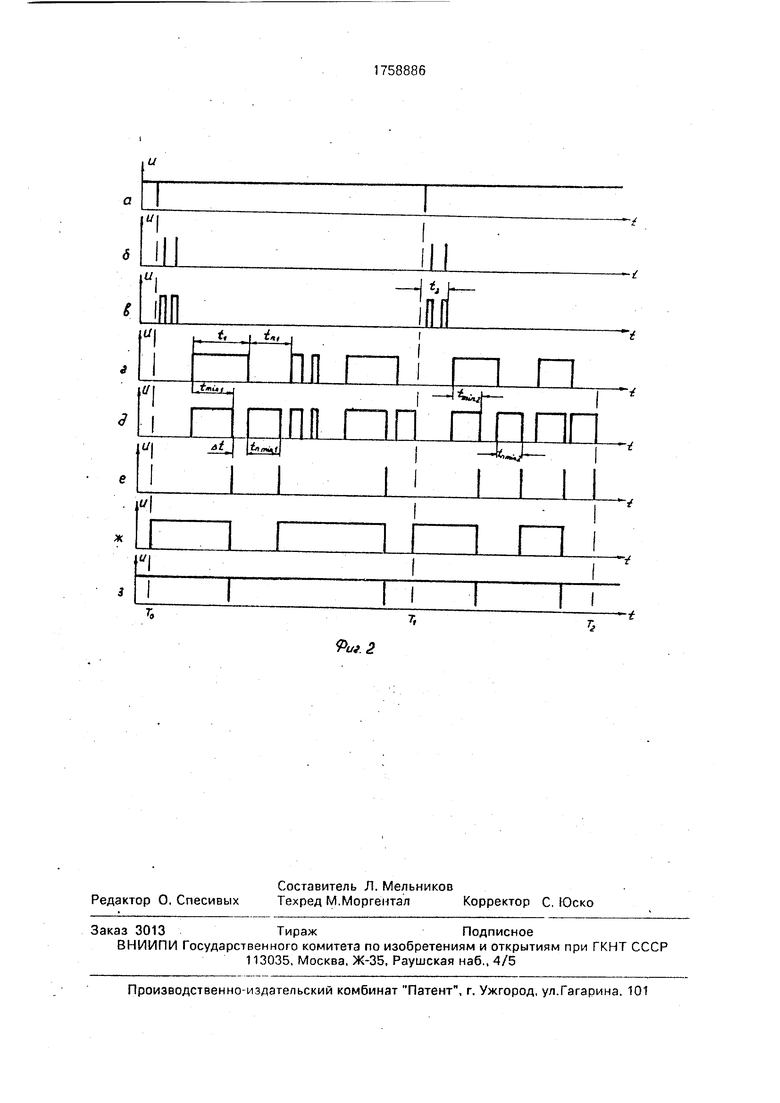

На фиг,1 приведена структурная схема устройства; на фиг,2 - временные диаграм5 мы работы устройства,

Устройство содержит информационный вход 1, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 2, инвертор 3, счетчик 4, блок сравнения 5, счетный триггер 6, элемент И-НЕ 7, мульти0 плексор 8, регистры 9, 10, входы кода параметров устройства 11, управляющий вход устройства 12, триггер управления 13, элементы И 14, 15, ВХО.Е. сигнала установки в исходное состояние устройства 16, тзкто5 вый вход устройства 17, выход устройства 18.

На временной диаграмме фиг.2 показаны эпюры следующих сигналов: а - импульсы из входе 16, б - импульсы на входе 12, в -импульсы на одном из разрядов кодового

входа 11, г - импульсы на входе 1, д - импульсы на первом сброса счетчика, е - импульсы на выходе блока сравнения 5, ж - импульсы на единичном выходе триггера 6, з - импульсы на выходе 18.

Информационный вход устройства 1 соединен с входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2, выход которого через инвертор 3 соединен с первым входом сброса счетчика 4, выходы которого соединены с первой группой входов блока сравнения 5, выход которого соединен с входом счетного триггера 6, и с первым входом элемента И-НЕ 7, единичный выход триггера 6 соединен со вторым входом элемента И-НЕ 7, с входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 и с входом управления мультиплексора 8, первая и вторая группа входов соединена соответственно с выходами регистров 9,10, информационные входы которых соединены между собой и являются входами кода параметров устройства 11, управляющий вход устройства 12 соединен с управляющим входом триггера управления 13 и со вторыми входами элементов И 14, 15, первые входы которых соединены соответственно с прямым и инверсным выходами триггера управления 13, а выходы - со входами записи регистров 10, 9, вход установки в исходное состояние триггера управления 13 соединен со вторым входом сброса счетчика 4, с единичным входом счетного триггера бис входом сигнала установки в исходное состояние устройства 16, тактовый вход устройства 17 соединен с тактовыми входами счетчика 4 и блока сравнения 5, выход элемента И-НЕ 7 соединен с выходом устройства 18.

Изобретение может быть реализовано, например, на ИМС серии 155.555. Счетчик 4 и счетный триггеры 6, 13 переключаются по задним фронтам входных импульсов. Мультиплексор 8 пропускает на выход код из регистра 9 при 1 уровне на входе управления и код из регистра 10 при О уровне на входе управления. Счетчик 4 считает тактовые импульсы при наличии на обеих входах сброса уровня 1,

В исходное состояние устройство устанавливается при подаче импульса на вход 16 установки в исходное состояние (фиг.2,а, интервал T0-Ti). При этом счетчик 4 устанавливается в О, триггер 6 в 1, триггер 13 в О. При подаче параллельного кода tmin на входы кода параметров устройства 11 (фиг.2,в, интервал T0-Ti) и первого импульса на управляющий вход устройства 12 (фиг.2,6, интервал T0-Ti) производится запись этого кода в регистр9. При подаче кода tnmini на входы 11 и второго импульса на вход 12 записывается код tnmini в регистр

5Последовательность импульсов подается на информационный вход 1 (фиг.2,г). При поступлении первого импульса длительностью ti tmin на выходе инвертора 3 устанавливается уровень 1 {фиг.2,д, интервал

10 T0-Ti) и счетчик 4 начинает считать тактовые импульсы, измеряя длительность ti. Блок сравнения 5 ведет сравнение кодов в

каждом такте и после счета nmini такto

15 товых импульсов код с выходов счетчика 4 равен коду tmin, при этом формируется импульс на выходе блока сравнения 5 (фиг.2,е, интервал T0-Ti). Триггер 6 переключается в состояние О (фиг.2,ж, интервал T0-Ti) и

0 формируется импульс на выходе 18 (фиг.2, 3, интервал T0-Ti). На выходе инвертора 3 устанавливается уровень О, удерживающий счетчик 4 в О в течение времени At ti - tmini до окончания первого импульса.

5 Затем на выходе инвертора 3 вновь устанавливается уровень 1 и счетчик 4 начинает считать тактовые импульсы, измеряя длительность паузы tni. При переключении триггера 6 в О мультиплексор начинает

0 выдавать и регистра 10 код tnmini, который сравнивается с текущим кодом счетчика 4. Если tni tnmini, выходной импульс блока сравнения 5 переключает триггер 6 в 1 и устройство готово к приему следующего им5 пульса и работе в режиме контроля деятельности импульса. Таким образом, каждый раз при поступлении входного импульса с длительностью ti tmini на входе устройства формируется выходной импульс равный по

0 длительности тактовому импульсу и совпадающий с ним по фазе, который задержан относительно переднего фронта входного импульса на время tmmi.

Если поступает импульс, длительность

5 которого меньше tmini Гфиг.2,е, второй импульс на интервале T0-Ti), он считается импульсом помехи. Счетчик 4 не успевает сосчитать nmini импульсов, блок 5 не выдает выходной импульс и триггер 6 остается в 1,

0 поэтому устройство не переключается в режим контроля паузы. Если поступит подряд несколько импульсов помехи, блок сравнения 5 не выдает ни одного выходного импульса и триггер 6 остается в 1. В этом

5 состоянии он остается пока не поступит импульс С ДЛИТеЛЬНОСТЬЮ Г, tmlnlЕсли пауза между импульсами tni меньше tnrninl, считается, что входная последовательность искажена помехой пропадание

импульса. При этом счетчик 4 не успевает сосчитать nmin2 Г тактовых импульto

сов, блок сравнения 5 не формирует выходной импульс, триггер 6 остается в О. Устройство продолжает работать в режиме контроля паузы, пока очередная пауза между импульсами не будет больше tnminl, после чего переключается в режим контроля длительности импульса.

При изменении параметров входной последовательности внешнее устройство в управления выдает на вход 16 импульс установки в исходное состояние (фиг.2,а, TI), затем подает параллельный код параметра tmin2 и первый импульс записи на вход 12 устройства (фиг.2,6, интервал Ti-T2), после чего подается параллельный код параметра tnmir 2 и второй импульс записи на вход 12. Длительность оперативной перестройки в устройстве определяется временем последовательной записи тз кодов двух параметров, поступающих с входов 11 при условии, что внешнее устройство ния к моменту подачи на вход 16 импульса установки в исходное состояние имеет текущие значения этих параметров, полученные в результате измерения, или подаваемые оператором с панели управления. После оперативной перестройки параметров устройство обрабатывает входную последовательность импульсов с измененными параметрами.

Таким образом, изобретение позволяет в сравнении с известными устройствами производить перестройку параметров входных информационных импульсов.

Формула изобретения Устройство для защиты от импульсных помех, содержащее счетный триггер, элемент И-НЕ, инвертор и счетчик, тактовый

вход которого является тактовым входом устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства путем обеспечения

возможности перестройки параметров входных информационных импульсов, введены первый и второй регистры, первый и второй элементы И, триггер управления, мультиплексор, блок сравнения и элемент

ИСКЛЮЧАЮЩЕЕ ИЛ И, при этом выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ через инвертор соединен с первым входом сброса счетчика, выход которого соединен с первой группой входов блока сравнения, к второй

группе входов которого подключены выходы первого и второго регистров через мультиплексор, тактовый вход блока сравнения соединен с тактовым входом счетчика, а выход блока сравнения соединен с первым

входом элемента И-НЕ и с входом счетного триггера, единичный выход которого соединен с вторым входом элемента И-НЕ, с одним из входов элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с входом управления мультиплексора, прямой и инверсный выходы триггера управления соединены через соответствующие элементы И с входами записи первого и второго регистров, информационные входы которых соединены между собой и

являются входами кода параметров устройства, управляющим входом которого является управляющий вход триггера управления, который соединен с вторыми входами первого и второго элементов И,

вход сигнала установки в исходное состояние триггера управления соединен со вторым входом сброса счетчика и с единичным входом счетного триггера и является входом сигнала установки в исходное состояние

устройства, информационным входом которого является другой вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.

гв

5

Авторы

Даты

1992-08-30—Публикация

1989-08-09—Подача