Изобретение относится к области вычислительной техники и может быть использовано для реализации логических алгоритмов, заданных в лингвистической форме.

Известен логический процессор, содержащий мультиплексор, регистр адреса, счетчик адреса, три-блока памяти, три регистра числа, три группы элементов И, две группы sfleMeh ов ИЛИ, узел сравнения, регистр кода сравнения, операционный блок, буферный регистр, блок селекции, шифратор, регистр вывода и блок синхронизации, первый и второй выходы которого подключены соответственно к установочному и счетному входам счетчика адэеса, выход которого подключен к первым адресным входам первого, второго и третьего блоков

памяти, управляющим входам блока синхронизации и мультиплексора, информационный вход и выход которого подключены соответственно к информационному входу процессора и ко входу регистра адреса, выход которого подключен ко вторым адресным входам первого и второго блоков памяти, третий выход блока синхронизации соединен со входами чтения первого и второго блоков памяти и информационными входами первого и второго регистров числа, четвертый выход блока синхронизации подключен ко входу чтения третьего блока памяти, входу приема третьего регистра числа и второму входу элементов И первой ipyn- пы, выход которых подключен к первому входу первой группы элементов ИЛИ, выход которой подключен к первому входу узла

XJ XI

00

XI о со

сравнения, выход которой подключен ко входу регистра кода сравнения, выход последнего подключен к информационным входам шифратора и регистра вывода, выход которого подключен к выходу процессора; выходы первого, второго и третьего блоков памяти подключены соответственно к информационным входам первого, второго и третьего регистра числа, выходы первого и второго регистров числа подключены соответственно к информационному и урав- ляющему входам блока селекции, выход которого подключен к первому входу элементов И первой группы, выход третьего регистра числа подключен к первому входу операционного блока и информационному входу буферного регистра, выход которого подключен ко второму информационному входу операционного блока и к первому входу элементов И второй группы, выход которых подключен ко второму входу элементов ИЛИ первой группы, выход операционного блока подключен ко входу второй группы элементов ИЛИ, выход которой подключен к управляющему входу буферного регистра, выход шифратора подключен ко второму адресному входу третьего блока памяти, пятый, шестой, седьмой, восьмой и девятый выходы блока синхронизации подключены соответственно к управляющему входу операционного блока, второму входу второй группы элементов И, второму входу третьей группы элементов И, информационному входу регистра вывода и второму входу второй группы элементов ИЛИ,

Недостатком данного устройства являются значительные аппаратурные затраты вызванные большим объемом требуемой памяти.

Известен лингвистический процессор, содержащий два мультиплексора адреса, регистр адреса, блок памяти входных переменных, блок памяти термов, блок памяти инструкций, блок памяти выходных переменных, три регистра числа, первый и второй регистры управления, первый и второй узлы сравнения, мультиплексор данных, регистр кода сравнения, регистр вывода, группу элементов И и блок синхронизации, причем информационным входом устройства является информационный вход первого мультиплексора адреса, выход которого подключен к информационному входу регистра адреса, выход регистра адреса соединен со вторым адресным входом блока памяти входных переменных, установочный и счетный вход счетчика адреса подключен соответственно к первому и второму выходам блока синхронизации, тактовый вход которого соединен с тактовым входом процессора, третий выход блока синхронизации подключен к синхровходам первого и второго регистров числа и входу чтения блока памяти входных переменных, выход которого соединен с информационным входом первого регистра числа, выход блока памяти термов подключен к информационному входу второго регистра числа, информационный вход и выход второго мультиплексора

0 адреса соединены соответственно со вторым адресным входом блока памяти инструкций и со входом второго регистра числа, выход блока памяти инструкций подключен к информационному входу третьего регист5 ра числа; выход первого регистра числа соединен с первым и вторым входами первого блока сравнения и информационным входом мультиплексора данных, выход первого узла сравнения подключен к информацион0 ному входу регистра кода сравнения, выход которого соединен с управляющими входами второго мультиплексора адреса и мультиплексора данных, первые и вторые входы и выходы элементов группы И подключены

5 соответственно к выходу третьего регистра числа, выходу и информационному входу первого регистра управления; четвертый выход блока синхронизации соединен с син- хровходами второго регистра управления и

0 третьего регистра числа и входу чтения блока памяти инструкций, установочный вход и синхровход первого регистра управления подключены соответственно к первому и второму выходам блока синхронизации,

5 вход чтения, первый и второй адресные входы и выход блока памяти выходных переменных соединены соответственно с шестым выходом блока синхронизации, выходами первого и второго регистров управ0 ления и информационному входу регистра вывода, синхровход и выход которого подключены соответственно к шестому выходу блока синхронизации и выходу результата процессора.

5 Недостатком данного устройства являются значительные аппаратурные затраты и недостаточные функциональные возможности.

Наиболее близким по технической сущ0 ности к достигаемому эффекту к предлагаемому устройству является лингвистический процессор.

Лингвистический процессор содержит первый и второй регистры управления, ре5 гистр числа, шифратор, блок синхронизации, блок памяти входных переменных, блок памяти выходных переменных, узел сравнения, регистр вывода, регистр адреса, мультиплексор адреса, счетчик адреса и группу элементов И. причем первый выход

блока синхронизации подключен к счетному входу счетчика адреса, информационный выход которого подключен к первому адресному входу блока памяти входных переменных, к управляющему входу мультиплексора адреса и ко входу сброса блока синхронизации; второй выход блока синхронизации подключен ко входу чтения блока памяти входных переменных и ко входу записи/чтения регистра числа; информационные входы устройства подключены соответственно к информационным входам мультиплексора адреса, выход которого подключен к информационному входу регистра адреса, выход которого подключен ко второму адресному входу блока памяти входных переменных; третий выход блока синхронизации подключен к входу записи/чтения регистра вывода и ко входу чтения блока памяти выходных переменных, выход которого подключен к информационному входу регистра вывода, выход которого подключен к выходу результата устройства; четвертый выход блока синхронизации подключен ко входам установки счетчика адреса, первого и второго регистров управления; пятый выход блока синхронизации подключен ко входам записи/чтения соответственно первого и второго регистров управления, выход блока памяти входных переменных подключен к информационному входу регистра числа; выходы первой группы регистра числа подключены к первому входу узла сравнения, а выходы второй группы регистра числа соединены с вторыми входами группы элементов И: выход узла сравнения подключен к информационным входам первого регистра управления, выход которого подключен к второму входу узла сравнения и к первому адресному входу блока памяти выходных переменных; выходы элементов И группы подключены к информационным входам второго регистра управления, выход которого подключен к первым входам элементов И группы и к входу шифратора; выход шифратора подключен ко второму адресному входу блока памяти выходных переменных; тактовый вход и вход начальной установки устройства подключены соответственно к тактовому входу и к входу начальной установки блока синхронизации.

Недостатком прототипа является низкое быстродействие при реализации алгоритмов, включающий выбор группы лингвистических правил в зависимости от множества четких условий.

Известен класс логико-лингвистических алгоритмов, в которых выбор группы лингвистических правил определяется логическими условиями. Такие алгоритмы

используются, например, в задачах управления роботом. Реализация этих алгоритмов в известном устройстве предполагает последовательное вычисление логических

условий и обработку лингвистических правил, что обуславливает его недостаточное быстродействие,

Целью изобретения является повышение быстродействия устройства.

0 Указанная цель достигается тем, что в устройство для реализации логических алгоритмов, заданных в лингвистической форме, содержащее первый и второй регистры управления, регистр числа, шифратор, блок

5 синхронизации, блок памяти входных переменных, блок памяти выходных переменных, первый узел сравнения, регистр вывода, регистр адреса, мультиплексор адреса, счетчик адреса и группу элементов И,

0 причем первый выход блока синхронизации подключен к счетному входу счетчика адреса, информационный выход которого подключен к первому адресному входу блока памяти входных переменных, к управляю5 щему входу мультиплексора адреса и к входу сброса блока синхронизации, второй выход которого подключен к входу чтения блока памяти входных переменных, информационные входы первой группы уст0 ройства подключены соответственно к информационным входам мультиплексора адреса, выход которого подключен к информационному входу регистра адреса, выход которого подключен к второму адресному

5 входу блока памяти входных переменных, третий выход блока синхронизации подключен ко входу записи/чтения регистра вывода и ко входу чтения блока памяти выходных переменных, выход которого подключен к

0 информационному входу регистра вывода, выход которого подключен к выходу результата устройства, четвертый выход блока синхронизации подключен ко входам установки счетчика адреса, первого и второго

5 регистров управления, выход первого регистра управления подключен к первому информационному входу первого узла сравнения и к первому адресному входу блока памяти выходных переменных, вто0 рой адресный вход которого подключен к выходу шифратора, выход первого узла сравнения подключен к информационному входу первого регистра управления, выходы второго регистра управления подключены к

5 первым входам элементов И группы, выходы которых подключены соответственно к информационным входам второго регистра управления, дополнительно введены второй узел сравнения, мультиплексор констант, триггер и мультиплексор маски, причем вход

числа входных переменных устройства подключен к информационному входу счетчика адреса, второй выход блока синхронизации подключен к входам записи/чтения регистра адреса, первого и второго регистров управления, четвертый выход блока синхронизации подключён ко входу установки в ноль триггера, выход которого подключен ко входу записи/чтения регистра числа, выход которого подключен к управляющему входу мультиплексора маски, выход которого подключен ко входу шифратора, информационные входы которого подключены соответственно к выходам второго регистра управления, выход регистра адреса подключен к первому информационному входу второго узла сравнения, выход которого подключен к счетному входу триггера, информационный выход счетчика адреса подключен к информационному входу регистра числа и управляющему входу мультиплексора констант, выход которого подключен к второму информационному входу второго узла сравнения, информационные входы второй группы устройства подключены соответственно к информационным входам мультиплексора констант, выходы первой и второй групп блока памяти входных переменных подключены соответ- ст венно к второму информационному входу первого узла сравнения и к вторым входам элементов И группы, тактовый вход и вход начальной установки устройства подключены соответственно к тактовому входу и к входу начальной установки блока синхронизации.

В системах, важным звеном в которых является человек, оценивающий информацию и принимающий решения, логический алгоритм управления задается в лингвистической форме Например, если на вход системы поступают параметры объекта ТЕМПЕРАТУРА И ВЛАЖНОСТЬ, а также соответствующие им константы, из базовых множеств этих лингвистических переменных, на основе которых формируются четкие условия и на выходе должно получиться значение параметра ДАВЛЕНИЕ, зависящее от этих условий, то логический алгоритм в лингвистической форме задается следующим образом:

ЕСЛИ Ттекущ. Tconst, TO

Если ТЕМПЕРАТУРА высокая, то если ВЛАЖНОСТЬ низкая, то ДАВЛЕНИЕ нормальное,

Иначе

Если ТЕМПЕРАТУРА средняя, то если ВЛАЖНОСТЬ средняя, то ДАВЛЕНИЕ низкое,

Иначе

Если ТЕМПЕРАТУРА высокая, то если

ВЛАЖНОСТЬ высокая, то ДАВЛЕНИЕ высокое, Иначе

ЕСЛИ Втекущ. Bconst, TO

Если ТЕМПЕРАТУРА высокая, то если ВЛАЖНОСТЬ низкая, то ДАВЛЕНИЕ низкое,

Иначе

Если ТЕМПЕРАТУРА средняя, то если ВЛАЖНОСТЬ средняя, то ДАВЛЕНИЕ нормальное, Иначе

Если ТЕМПЕРАТУРА высокая, то если ВЛАЖНОСТЬ высокая, то ДАВЛЕНИЕ невысокое,

Иначе

Если ТЕМПЕРАТУРА высокая, то если

ВЛАЖНОСТЬ низкая, то ДАВЛЕНИЕ невысокое, Иначе

Если ТЕМПЕРАТУРА средняя, то если ВЛАЖНОСТЬ средняя, то ДАВЛЕНИЕ высокое, Иначе

Если ТЕМПЕРАТУРА высокая, то если ВЛАЖНОСТЬ высокая, то ДАВЛЕНИЕ среднее.

Реализация подобного лргико-лингвистического алгоритма в устройстве-прототипе предполагает последовательную обработку логических условий и лингвистических правил.

В предлагаемом устройстве процессы

формирования значения выходного параметра по лингвистическим правилам и анализа логических условий реализуются параллельно, что сокращает временные затраты при выполнении алгоритмов данного

класса.

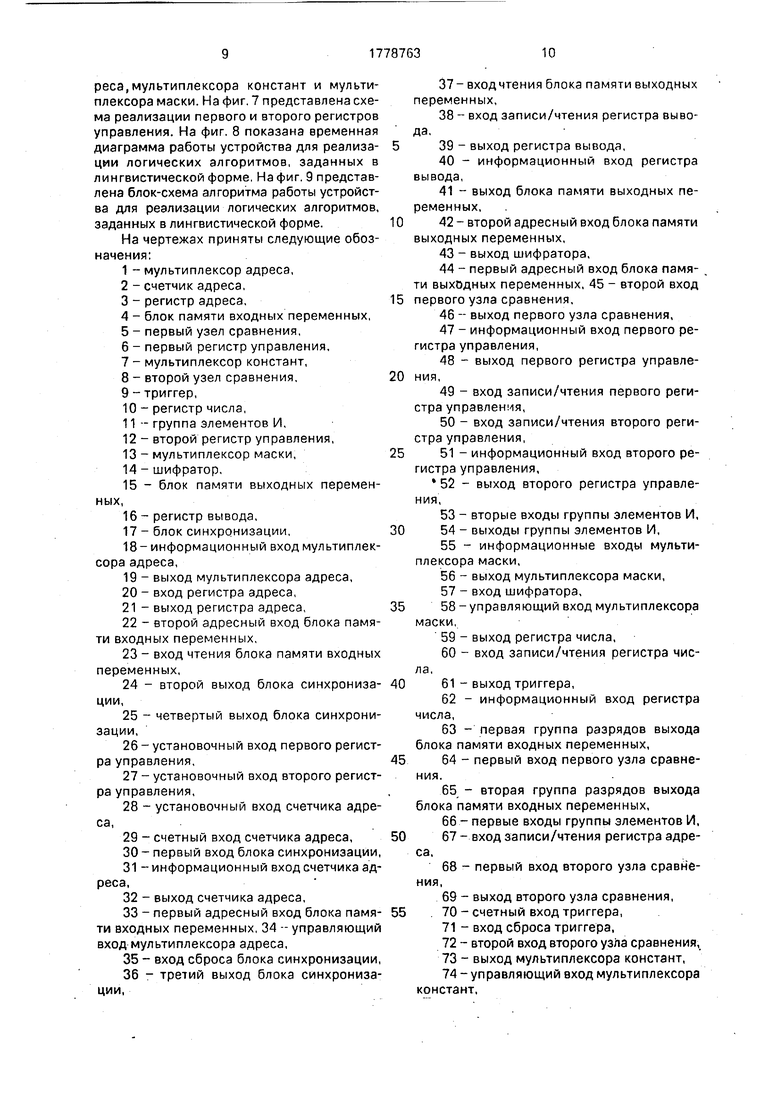

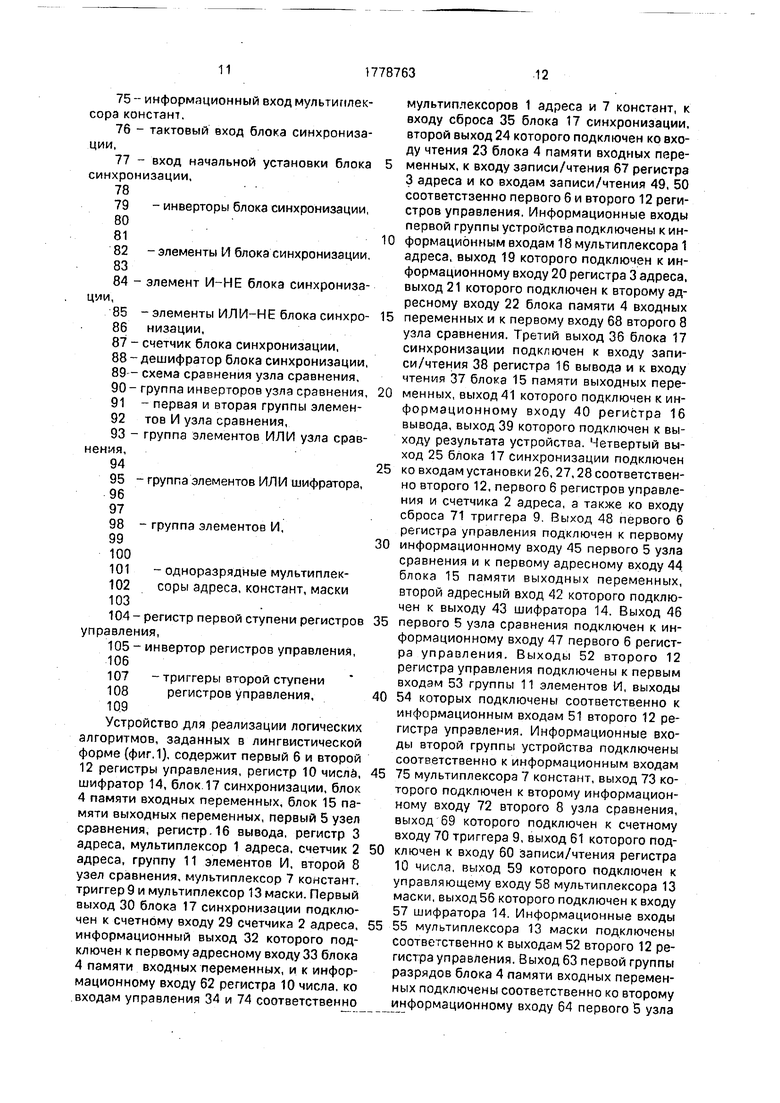

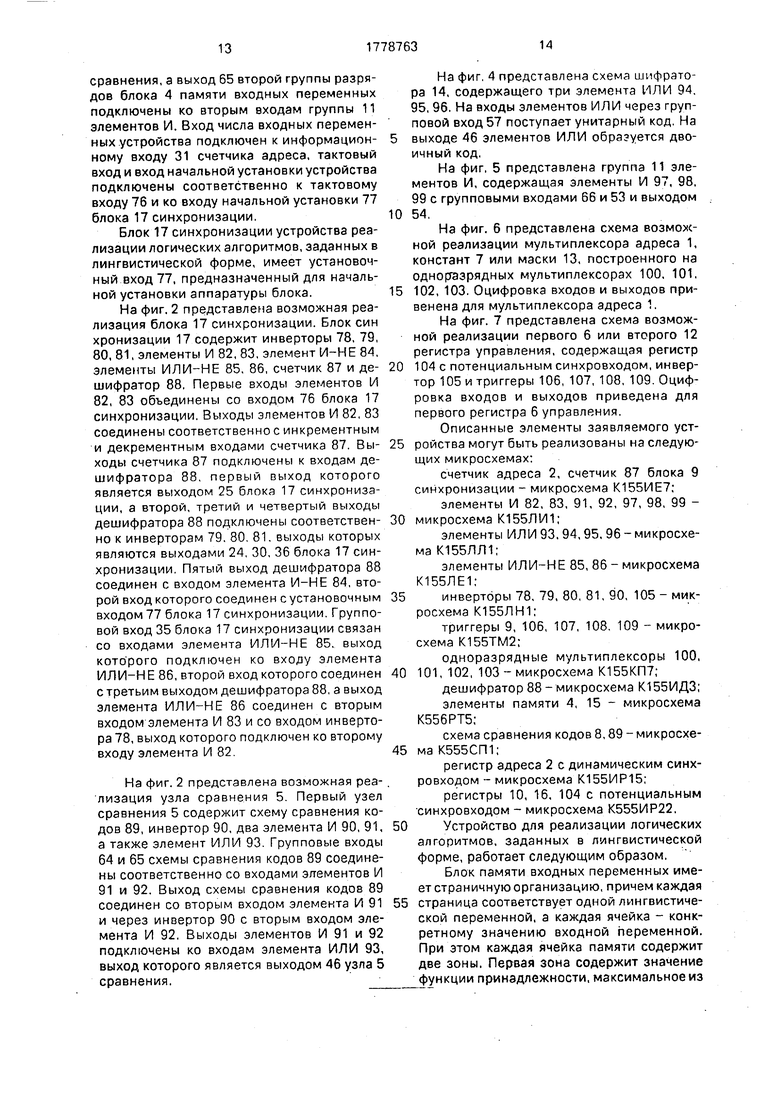

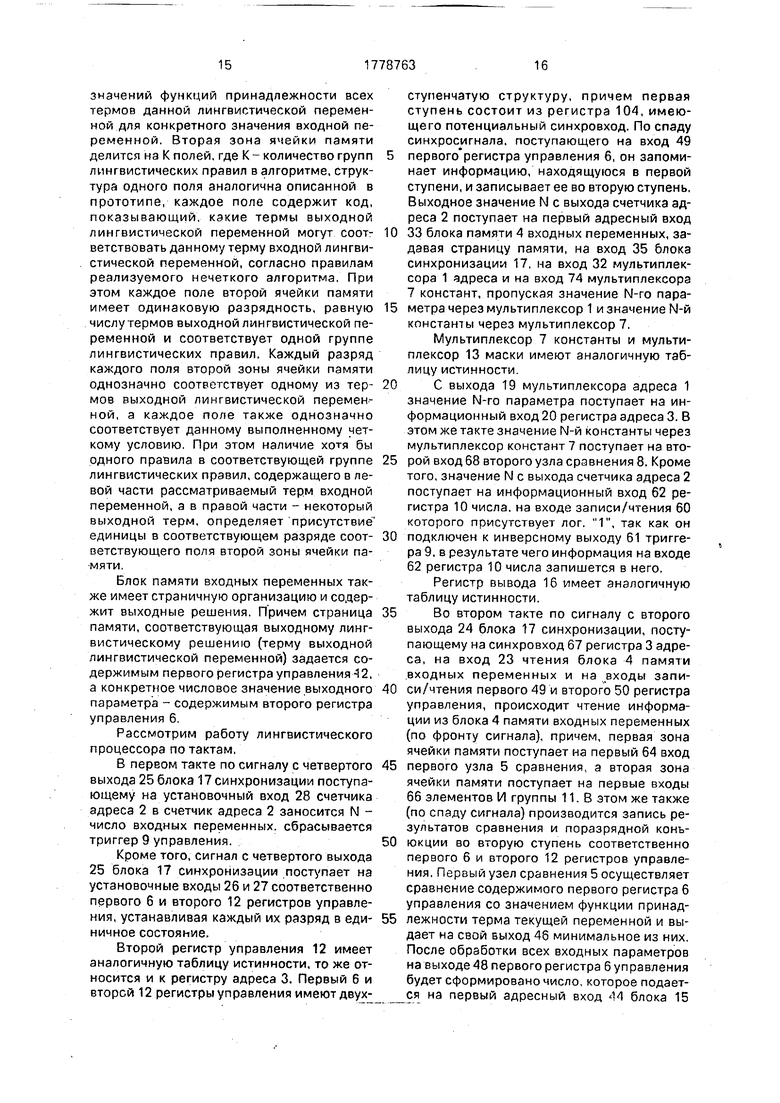

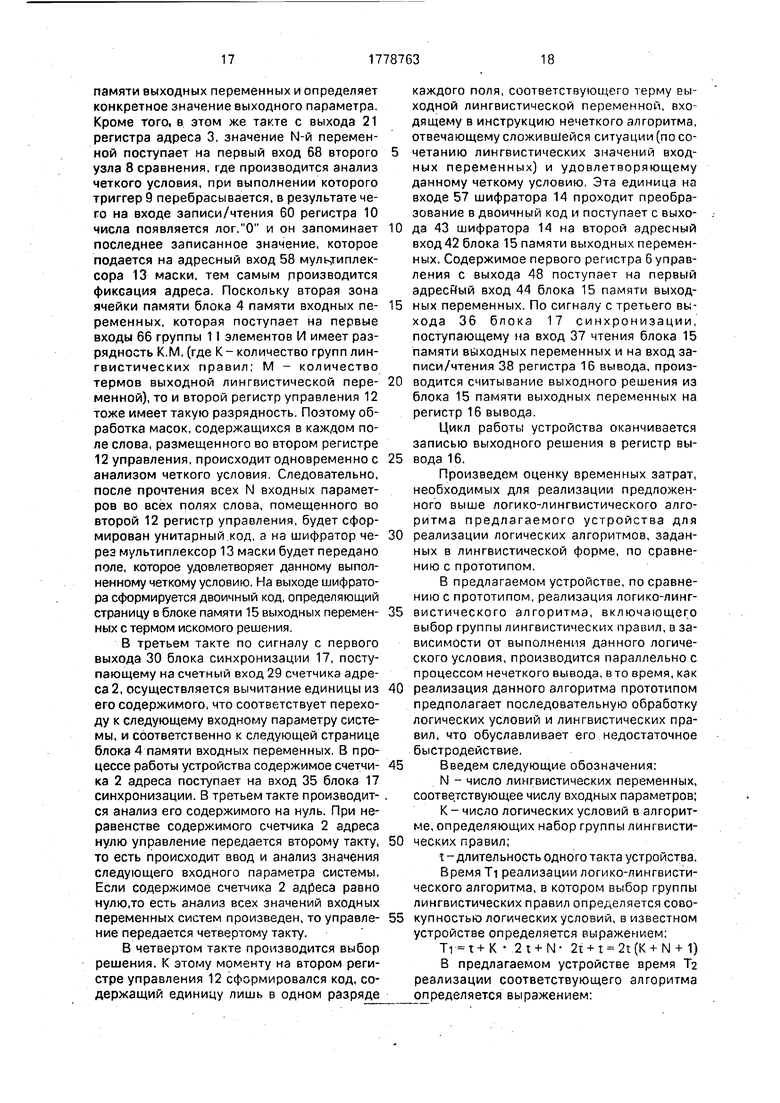

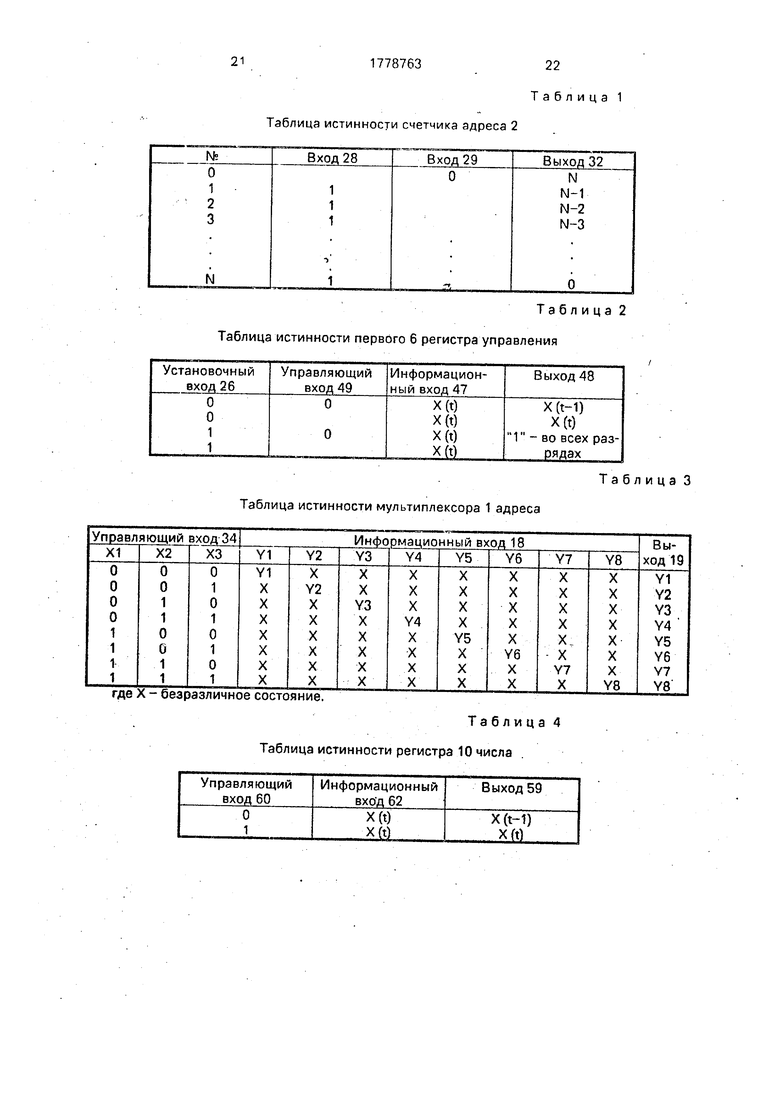

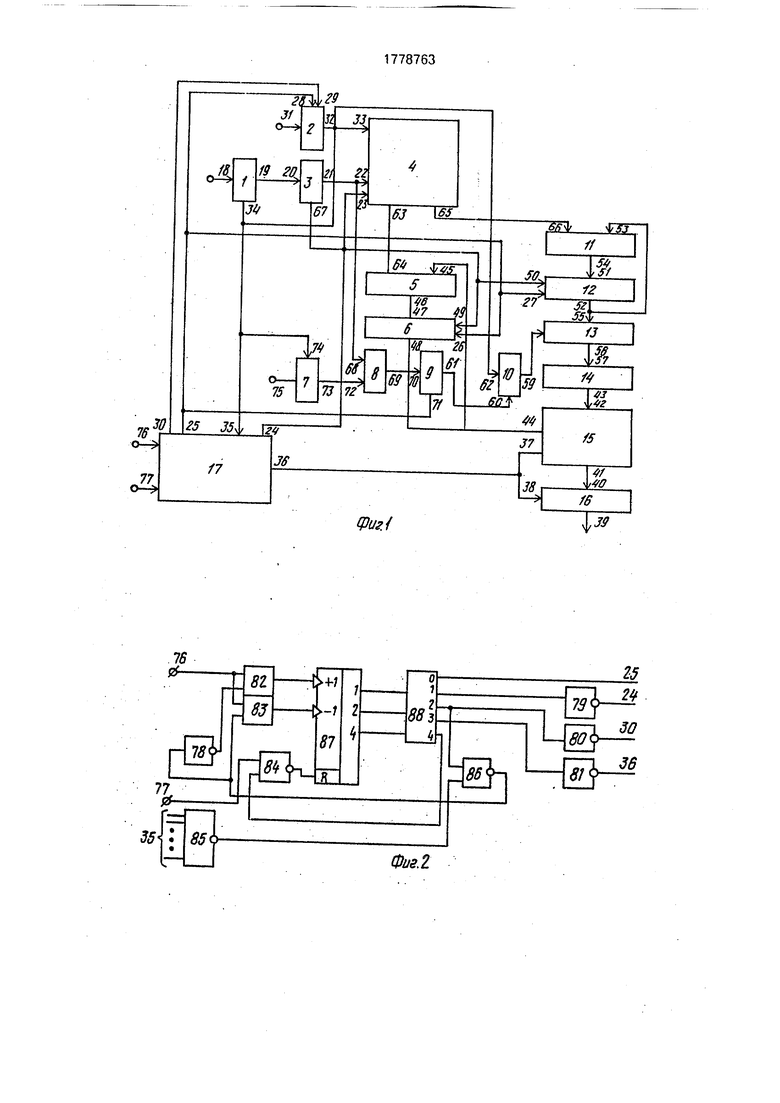

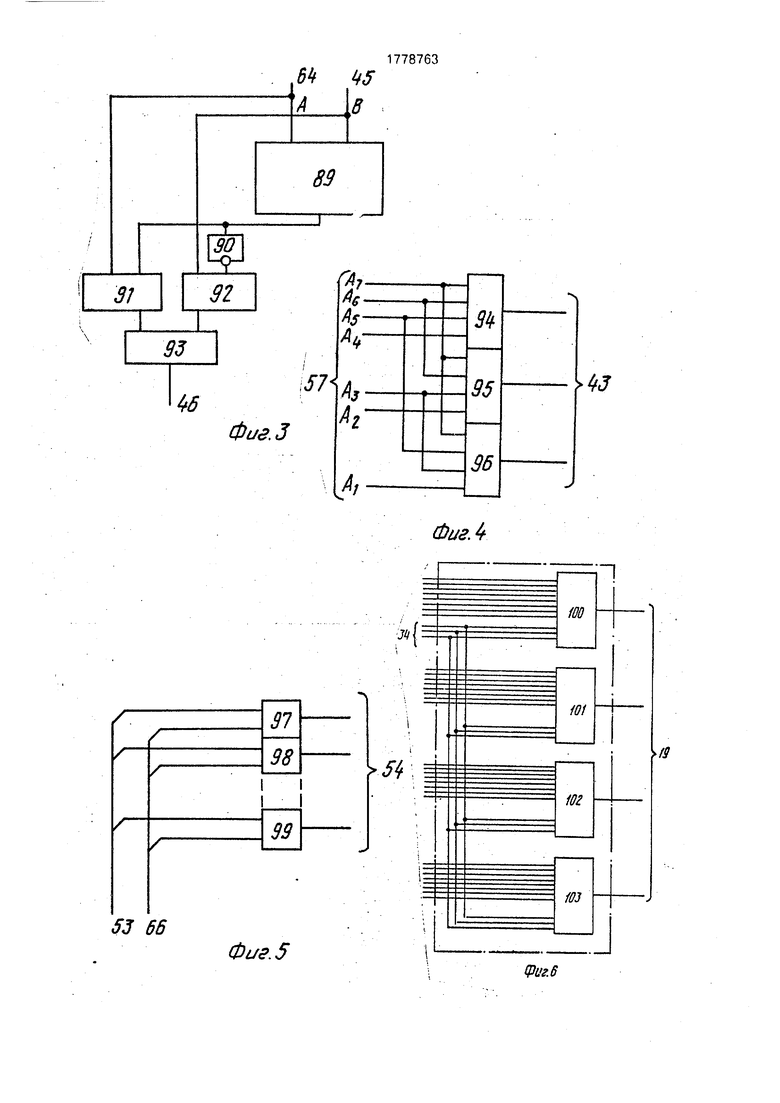

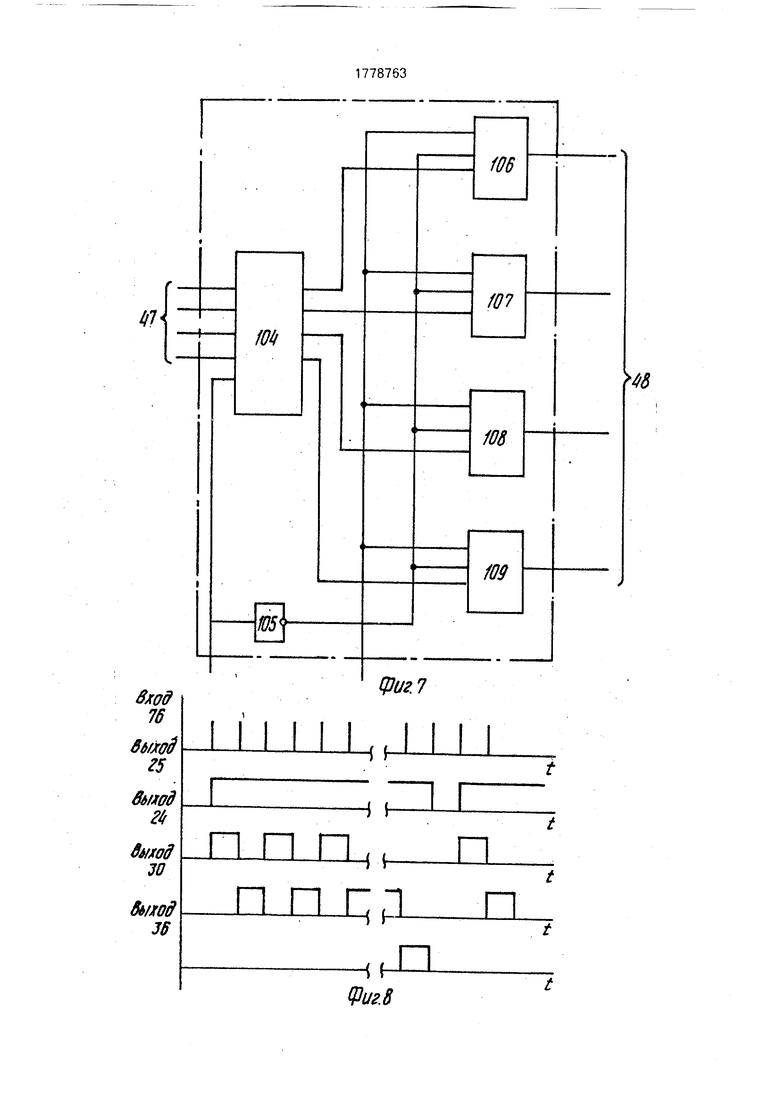

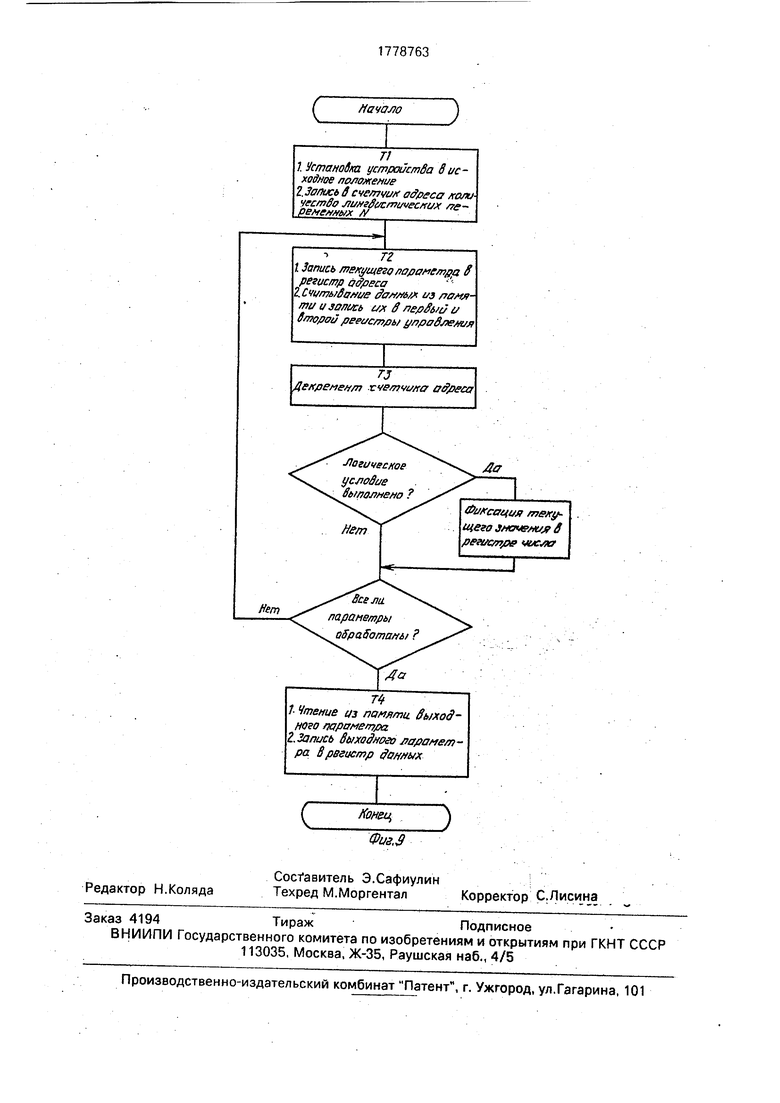

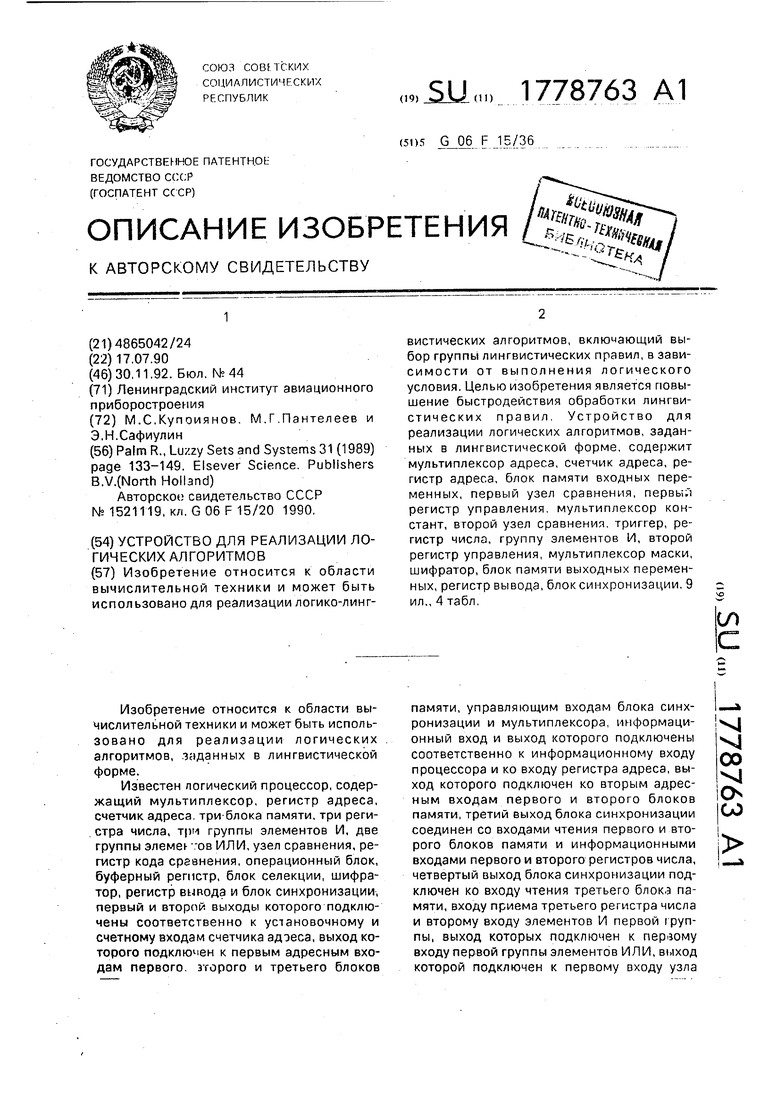

На фиг. 1 представлена функциональная схема устройства для реализации логических алгоритмов, заданных в лингвистической форме. На фиг. 2 - пример

реализации блока синхронизации. На фиг. 3 показана возможная реализация узла сравнения. На фиг. 4 приведена схема шифратора. Схема реализации группы элементов И представлена на фиг, 5. На фиг. 6 представ- лена схема реализации мультиплексора адреса,мультиплексора констант и мультиплексора маски. На фиг. 7 представлена схема реализации первого и второго регистров управления. На фиг. 8 показана временная диаграмма работы устройства для реализации логических алгоритмов, заданных в лингвистической форме, На фиг. 9 представлена блок-схема алгоритма работы устройства для реализации логических алгоритмов, заданных в лингвистической форме.

На чертежах приняты следующие обозначения:

1- мультиплексор адреса,

2- счетчик адреса,

3- регистр адреса,

4- блок памяти входных переменных,

5- первый узел сравнения,

6- первый регистр управления,

7- мультиплексор констант,

8- второй узел сравнения,

9-триггер,

10- регистр числа,

11- группа элементов И.

12- второй регистр управления,

13- мультиплексор маски,

14- шифратор,

15- блок памяти выходных переменных,

16- регистр вывода,

17- блок синхронизации,

18-информационный вход мультиплексора адреса,

19- выход мультиплексора адреса,

20- вход регистра адреса,

21- выход регистра адреса,

22- второй адресный вход блока памяти входных переменных,

23- вход чтения блока памяти входных переменных,

24- второй выход блока синхронизации,

25- четвертый выход блока синхронизации,

26- установочный вход первого регистра управления,

27- установочный вход второго регистра управления,

28- установочный вход счетчика адреса,

29- счетный вход счетчика адреса,

30- первый вход блока синхронизации,

31- информационный вход счетчика адреса,

32- выход счетчика адреса,

33- первый адресный вход блока памяти входных переменных, 34 - управляющий вход мультиплексора адреса,

35- вход сброса блока синхронизации,

36- третий выход блока синхронизации,

37- вход чтения блока памяти выходных переменных,

38 - вход записи/чтения регистра вывода, 39 - выход регистра вывода,

40- информационный вход регистра вывода,

41- выход блока памяти выходных переменных,

0 42 - второй адресный вход блока памяти выходных переменных,

43- выход шифратора,

44- первый адресный вход блока памяти выходных переменных, 45 - второй вход

5 первого узла сравнения,

46- выход первого узла сравнения,

47- информационный вход первого регистра управления,

48- выход первого регистра управле- 0 ния,

49- вход записи/чтения первого регистра управления,

50- вход записи/чтения второго регистра управления,

5 51 - информационный вход второго регистра управления,

52 - выход второго регистра управления,

53 - вторые входы группы элементов И, 054 - выходы группы элементов И,

55- информационные входы мультиплексора маски,

56- выход мультиплексора маски,

57- вход шифратора,

5 58 - управляющий вход мультиплексора маски,

59- выход регистра числа,

60- вход записи/чтения регистра числа,

0 61 - выход триггера,

62- информационный вход регистра числа,

63- первая группа разрядов выхода блока памяти входных переменных,

5 64 - первый вход первого узла сравнения.

65- вторая группа разрядов выхода блока памяти входных переменных,

66- первые входы группы элементов И, 0 67 - вход записи/чтения регистра адреса,

68- первый вход второго узла сравнения,

69- выход второго узла сравнения, 5 70 - счетный вход триггера,

71- вход сброса триггера,

72- второй вход второго узла сравнения,

73- выход мультиплексора констант,

74- управляющий вход мультиплексора констант,

75- информационный вход мультиплексора констант.

76- тактовый вход блока синхронизации,

77- вход начальной установки блока синхронизации,

78

79 - инверторы блока синхронизации,

80

81

82 - элементы И блока синхронизации,

83

84- элемент И-НЕ блока синхронизации,

85-элементы ИЛИ-НЕ блока синхро86низации,

87- счетчик блока синхронизации,

88- дешифратор блока синхронизации,

89- схема сравнения узла сравнения,

90- группа инверторов узла сравнения,

91- первая и вторая группы элемен92тов И узла сравнения,

93- группа элементов ИЛИ узла сравнения,

94

95 -группаэлементов ИЛИ шифратора,

96

97

98 - группа элементов И,

99

100

101- одноразрядные мультиплек102соры адреса, констант, маски 103

104- регистр первой ступени регистров управления,

105- инвертор регистров управления, 106

107- триггеры второй ступени

108регистров управления, 109

Устройство для реализации логических алгоритмов, заданных в лингвистической форме (фиг.1), содержит первый 6 и второй 12 регистры управления, регистр 10 числа, шифратор 14, блок 17 синхронизации, блок 4 памяти входных переменных, блок 15 памяти выходных переменных, первый 5 узел сравнения, регистр 16 вывода, регистр 3 адреса, мультиплексор 1 адреса, счетчик 2 адреса, группу 11 элементов И, второй 8 узел сравнения, мультиплексор 7 констант, триггер 9 и мультиплексор 13 маски. Первый выход 30 блока 17 синхронизации подключен к счетному входу 29 счетчика 2 адреса, информационный выход 32 которого подключен к первому адресному входу 33 блока 4 памяти входных переменных, и к информационному входу 62 регистра 10 числа, ко входам управления 34 и 74 соответственно

мультиплексоров 1 адреса и 7 констант, к входу сброса 35 блока 17 синхронизации, второй выход 24 которого подключен ко входу чтения 23 блока 4 памяти входных переменных, к входу записи/чтения 67 регистра 3 адреса и ко входам записи/чтения 49, 50 соответстзенно первого б и второго 12 регистров управления. Информационные входы первой группы устройства подключены к ин0 формационным входам 18 мультиплексора 1 адреса, выход 19 которого подключен к информационному входу 20 регистра 3 адреса, выход 21 которого подключен к второму адресному входу 22 блока памяти 4 входных

5 переменных и к первому входу 68 второго 8 узла сравнения. Третий выход 36 блока 17 синхронизации подключен к входу записи/чтения 38 регистра 16 вывода и к входу чтения 37 блока 15 памяти выходных пере0 менных, выход 41 которого подключен к информационному входу 40 регистра 16 вывода, выход 39 которого подключен к выходу результата устройства. Четвертый выход 25 блока 17 синхронизации подключен

5 ко входам установки 26, 27,28 соответственно второго 12, первого 6 регистров управления и счетчика 2 адреса, а также ко входу сброса 71 триггера 9 Выход 48 первого 6 регистра управления подключен к первому

0 информационному входу 45 первого 5 узла сравнения и к первому адресному входу 44 блока 15 памяти выходных переменных, второй адресный вход 42 которого подключен к выходу 43 шифратора 14. Выход 46

5 первого 5 узла сравнения подключен к информационному входу 47 первого 6 регистра управления. Выходы 52 второго 12 регистра управления подключены к первым входам 53 группы 11 элементов И, выходы

0 54 которых подключены соответственно к информационным входам 51 второго 12 регистра управления. Информационные входы второй группы устройства подключены соответственно к информационным входам

5 75 мультиплексора 7 констант, выход 73 которого подключен к второму информационному входу 72 второго 8 узла сравнения, выход 69 которого подключен к счетному входу 70 триггера 9, выход 61 которого под0 ключей к входу 60 записи/чтения регистра 10 числя, выход 59 которого подключен к управляющему входу 58 мультиплексора 13 маски, выход 56 которого подключен к входу 57 шифратора 14. Информационные входы

5 55 мультиплексора 13 маски подключены соответственно к выходам 52 второго 12 регистра управления. Выход 63 первой группы разрядов блока 4 памяти входных переменных подключены соответственно ко второму информационному входу 64 первого 5 узла

сравнения, а выход 65 второй группы разрядов блока 4 памяти входных переменных подключены ко вторым входам группы 11 элементов И. Вход числа входных переменных устройства подключен к информационному входу 31 счетчика адреса, тактовый вход и вход начальной установки устройства подключены соответственно к тактовому входу 76 и ко входу начальной установки 77 блока 17 синхронизации.

Блок 17 синхронизации устройства реализации логических алгоритмов, заданных в лингвистической форме, имеет установочный вход 77, предназначенный для начальной установки аппаратуры блока.

На фиг. 2 представлена возможная реализация блока 17 синхронизации. Блок син хронизации 17 содержит инверторы 78, 79, 80, 81, элементы И 82, 83, элемент И-НЕ 84. элементы ИЛИ-НЕ 85, 86, счетчик 87 и дешифратор 88, Первые входы элементов И 82, 83 объединены со входом 76 блока 17 синхронизации. Выходы элементов И 82, 83 соединены соответственно с инкрементным и декрементным входами счетчика 87. Выходы счетчика 87 подключены к входам дешифратора 88. первый выход которого является выходом 25 блока 17 синхронизации, а второй, третий и четвертый выходы дешифратора 88 подключены соответственно к инверторам 79. 80. 81, выходы которых являются выходами 24, 30, 36 блока 17 синхронизации. Пятый выход дешифратора 88 соединен с входом элемента И-НЕ 84, второй вход которого соединен с установочным входом 77 блока 17 синхронизации. Групповой вход 35 блока 17 синхронизации связан со входами элемента ИЛИ-НЕ 85. выход которого подключен ко входу элемента ИЛИ-НЕ 86, второй вход которого соединен с третьим выходом дешифратора 88, а выход элемента ИЛИ-НЕ 86 соединен с вторым входом элемента И 83 и со входом инвертора 78, выход которого подключен ко второму входу элемента И 82

На фиг. 2 представлена возможная реализация узла сравнения 5. Первый узел сравнения 5 содержит схему сравнения кодов 89, инвертор 90, два элемента И 90, 91, а также элемент ИЛИ 93. Групповые входы 64 и 65 схемы сравнения кодов 89 соединены соответственно со входами элементов И 91 и 92. Выход схемы сравнения кодов 89 соединен со вторым входом элемента И 91 и через инвертор 90 с вторым входом элемента И 92, Выходы элементов И 91 и 92 подключены ко входам элемента ИЛИ 93, выход которого является выходом 46 узла 5 сравнения.

На фиг. 4 представлена схема шифратора 14, содержащего три элемента ИЛИ 94, 95, 96. На входы элементов ИЛИ через групповой вход 57 поступает унитарный код. На выходе 46 элементов ИЛИ образуется двоичный код,

На фиг. 5 представлена группа 11 элементов И, содержащая элементы И 97, 98, 99 с групповыми входами 66 и 53 и выходом 0 54,

На фиг. 6 представлена схема возможной реализации мультиплексора адреса 1, констант 7 или маски 13, построенного на одноразрядных мультиплексорах 100. 101, 5 102, 103. Оцифровка входов и выходов при- венена для мультиплексора адреса 1.

На фиг. 7 представлена схема возможной реализации первого 6 или второго 12 регистра управления, содержащая регистр 0 104 с потенциальным синхровходом, инвертор 105 и триггеры 106, 107, 108, 109. Оцифровка входов и выходов приведена для первого регистра 6 управления.

Описанные элементы заявляемого уст- 5 ройства могут быть реализованы на следующих микросхемах:

счетчик адреса 2, счетчик 87 блока 9 синхронизации - микросхема К155ИЕ7;

элементы И 82, 83, 91, 92, 97, 98, 99 - 0 микросхема К155ЛИ1;

элементы ИЛИ 93. 94,95. 96 - микросхема К155ЛЛ1;

элементы ИЛИ-НЕ 85, 86 - микросхема К155ЛЕ1:

5инверторы 78, 79, 80, 81, 90, 105 - микросхема К155ЛН1:

триггеры 9, 106, 107, 108. 109 - микросхема К155ТМ2;

одноразрядные мультиплексоры 100, 0 101, 102, 103-микросхема К155КП7;

дешифратор 88 - микросхема К155ИДЗ;

элементы памяти 4, 15 - микросхема К556РТ5;

схема сравнения кодов 8,89 - микросхе- 5 ма К555СП1;

регистр адреса 2 с динамическим синхровходом - микросхема К155ИР15;

регистры 10, 16, 104 с потенциальным синхровходом - микросхема К555ИР22. 0 Устройство для реализации логических алгоритмов, заданных в лингвистической форме, работает следующим образом.

Блок памяти входных переменных имеет страничную организацию, причем каждая 5 страница соответствует одной лингвистической переменной, а каждая ячейка - конкретному значению входной переменной. При этом каждая ячейка памяти содержит две зоны. Первая зона содержит значение функции принадлежности, максимальное из

значений функций принадлежности всех термов данной лингвистической переменной для конкретного значения входной переменной. Вторая зона ячейки памяти делится на К полей, где К - количество групп лингвистических правил в алгоритме, структура одного поля аналогична описанной в прототипе, каждое поле содержит код, показывающий, какие термы выходной лингвистической переменной могут соответствовать данному терму входной лингвистической переменной, согласно правилам реализуемого нечеткого алгоритма. При этом каждое поле второй ячейки памяти имеет одинаковую разрядность, равную числу термов выходной лингвистической переменной и соответствует одной группе лингвистических правил. Каждый разряд каждого поля второй зоны ячейки памяти однозначно соответствует одному из термов выходной лингвистической переменной, а каждое поле также однозначно соответствует данному выполненному четкому условию. При этом наличие хотя бы одного правила в соответствующей группе лингвистических правил, содержащего в левой части рассматриваемый терм входной переменной, а в правой части - некоторый выходной терм, определяет присутствие единицы в соответствующем разряде соответствующего поля второй зоны ячейки памяти.

Блок памяти входных переменных также имеет страничную организацию и содержит выходные решения. Причем страница памяти, соответствующая выходному лингвистическому решению (терму выходной лингвистической переменной) задается содержимым первого регистра управления 42, а конкретное числовое значение выходного параметра - содержимым второго регистра управления 6.

Рассмотрим работу лингвистического процессора по тактам,

В первом такте по сигналу с четвертого выхода 25 блока 17 синхронизации поступающему на установочный вход 28 счетчика адреса 2 в счетчик адреса 2 заносится N - число входных переменных, сбрасывается триггер 9 управления.

Кроме того, сигнал с четвертого выхода 25 блока 17 синхронизации поступает на установочные входы 26 и 27 соответственно первого 6 и второго 12 регистров управления, устанавливая каждый их разряд в единичное состояние.

Второй регистр управления 12 имеет аналогичную таблицу истинности, то же относится и к регистру адреса 3. Первый 6 и второй 12 регистры управления имеют двухступенчатую структуру, причем первая ступень состоит из регистра 104, имеющего потенциальный синхровход. По спаду синхросигнала, поступающего на вход 49

первого регистра управления 6, он запоминает информацию, находящуюся в первой ступени, и записывает ее во вторую ступень, Выходное значение N с выхода счетчика адреса 2 поступает на первый адресный вход

0 33 блока памяти 4 входных переменных, задавая страницу памяти, на вход 35 блока синхронизации 17, на вход 32 мультиплексора 1 адреса и на вход 74 мультиплексора 7 констант, пропуская значение N-ro пара5 метра через мультиплексор 1 и значение N-й константы через мультиплексор 7.

Мультиплексор 7 константы и мультиплексор 13 маски имеют аналогичную таблицу истинности.

0 С выхода 19 мультиплексора адреса 1 значение N-ro параметра поступает на информационный вход 20 регистра адреса 3. В этом же такте значение N-й константы через мультиплексор констант 7 поступает на вто5 рой вход 68 второго узла сравнения 8. Кроме того, значение N с выхода счетчика адреса 2 поступает на информационный вход 62 регистра 10 числа, на входе записи/чтения 60 которого присутствует лог. 1, так как он

0 подключен к инверсному выходу 61 триггера 9, в результате чего информация на входе 62 регистра 10 числа запишется в него.

Регистр вывода 16 имеет аналогичную таблицу истинности.

5 Во втором такте по сигналу с второго выхода 24 блока 17 синхронизации, поступающему на синхровход 67 регистра 3 адреса, на вход 23 чтения блока 4 памяти входных переменных и на входы запи0 си/чтения первого 49 и второго 50 регистра управления, происходит чтение информации из блока 4 памяти входных переменных (по фронту сигнала), причем, первая зона ячейки памяти поступает на первый 64 вход

5 первого узла 5 сравнения, а вторая зона ячейки памяти поступает на первые входы 66 элементов И группы 11. В этом же также (по спаду сигнала) производится запись результатов сравнения и поразрядной конъ0 юкции во вторую ступень соответственно первого 6 и второго 12 регистров управления. Первый узел сравнения 5 осуществляет сравнение содержимого первого регистра 6 управления со значением функции принад5 лежности терма текущей переменной и выдает на свой выход 46 минимальное из них. После обработки всех входных параметров на выходе 48 первого регистра 6 управления будет сформировано число, которое подается на первый адресный вход Л4 блока 15

памяти выходных переменных и определяет конкретное значение выходного параметра. Кроме того, в этом же такте с выхода 21 регистра адреса 3, значение N-й переменной поступает на первый вход 68 второго узла 8 сравнения, где производится анализ четкого условия, при выполнении которого триггер 9 перебрасывается, в результате чего на входе записи/чтения 60 регистра 10 числа появляется лог.0 и он запоминает последнее записанное значение, которое подается на адресный вход 58 мультиплексора 13 маски, тем самым производится фиксация адреса. Поскольку вторая зона ячейки памяти блока 4 памяти входных переменных, которая поступает на первые входы 66 группы 11 элементов И имеет разрядность К.М. (где К - количество групп лингвистических правил; М - количество термов выходной лингвистической переменной), то и второй регистр управления 12 тоже имеет такую разрядность. Поэтому обработка масок, содержащихся в каждом поле слова, размещенного во втором регистре 12 управления, происходит одновременно с анализом четкого условия. Следовательно, после прочтения всех N входных параметров во всех полях слова, помещенного во второй 12 регистр управления, будет сформирован унитарный код, а на шифратор через мультиплексор 13 маски будет передано поле, которое удовлетворяет данному выполненному четкому условию. На выходе шифратора сформируется двоичный код, определяющий страницу в блоке памяти 15 выходных переменных с термом искомого решения.

В третьем такте по сигналу с первого выхода 30 блока синхронизации 17, поступающему на счетный вход 29 счетчика адреса 2, осуществляется вычитание единицы из его содержимого, что соответствует переходу к следующему входному параметру системы, и соответственно к следующей странице блока 4 памяти входных переменных. В процессе работы устройства содержимое счетчика 2 адреса поступает на вход 35 блока 17 синхронизации. В третьем такте производится анализ его содержимого на нуль. При неравенстве содержимого счетчика 2 адреса нулю управление передается второму такту, то есть происходит ввод и анализ значения следующего входного параметра системы, Если содержимое счетчика 2 адреса равно нулю.то есть анализ всех значений входных переменных систем произведен, то управление передается четвертому такту.

В четвертом такте производится выбор решения. К этому моменту на втором регистре управления 12 сформировался код, содержащий единицу лишь в одном разряде

каждого поля, соответствующего терму выходной лингвистической переменной, входящему в инструкцию нечеткого алгоритма, отвечающему сложившейся ситуации (по сочетанию лингвистических значений входных переменных) и удовлетворяющему данному четкому условию. Эта единица на входе 57 шифратора 14 проходит преобразование в двоичный код и поступает с выхо0 да 43 шифратора 14 на второй адресный вход 42 блока 15 памяти выходных переменных. Содержимое первого регистра 6 управления с выхода 48 поступает на первый адресйый вход 44 блока 15 памяти выход5 ных переменных. По сигналу с третьего выхода 36 блока 17 синхронизации, поступающему на вход 37 чтения блока 15 памяти выходных переменных и на вход записи/чтения 38 регистра 16 вывода, произ0 водится считывание выходного решения из блока 15 памяти выходных переменных на регистр 16 вывода.

Цикл работы устройства оканчивается записью выходного решения в регистр вы5 вода 16.

Произведем оценку временных затрат, необходимых для реализации предложенного выше логико-лингвистического алгоритма предлагаемого устройства для

0 реализации логических алгоритмов, заданных в лингвистической форме, по сравнению с прототипом.

В предлагаемом устройстве, по сравнению с прототипом, реализация логико-линг5 вистического алгоритма, включающего выбор группы лингвистических правил, в зависимости от выполнения данного логического условия, производится параллельно с процессом нечеткого вывода, в то время, как

0 реализация данного алгоритма прототипом предполагает последовательную обработку логических условий и лингвистических правил, что обуславливает его недостаточное быстродействие.

5 Введем следующие обозначения:

N - число лингвистических переменных, соответствующее числу входных параметров; К - число логических условий в алгоритме, определяющих набор группы лингвисти0 ческих правил;

t- длительность одного такта устройства. Время Ti реализации логико-лингвистического алгоритма, в котором выбор группы лингвистических правил определяется сово5 купностью логических условий, в известном устройстве определяется выражением:

Ti t + К 2 t + N 2t +1 2t (К + N + 1) В предлагаемом устройстве время Т2 реализации соответствующего алгоритма определяется выражением:

T2 t + N -2t + t 2t(N + 1)

Тогда повышение быстродействия д при использовании предлагаемого устройства определяется выражением:

Л-Ti 2t(K+N +1) . К

Т2 2t(N + 1)N + Г

Например, для конкретных значений , имеет

+ 5ТТ 1 5

То есть для приведенного примера быстродействие предлагаемого устройства по сравнению с прототипом, увеличилось на 50%.

Формула изобретения

Устройство для реализации логических алгоритмов, заданных в лингвистической форме, содержащее первый и второй регистры управления, регистр числа, шифратор, блок синхронизации, блок памяти входных переменных, блок памяти выходных переменных, первый узел сравнения, регистр вывода, регистр адреса, мультиплексор адреса, счетчик адреса и группу элементов И, причем, первый выход блока синхрониза- ции подключен к счетному входу счетчика адреса, информационный выход которого подключен к первому адресному входу блока памяти входных переменных, к управляющему входу мультиплексора адреса и к входу сброса блока синхронизации, второй выход которого подключен к входу чтения блока памяти входных переменных, информационные входы первой группы устройства подключены соответственно к информационным входам мультиплексора адреса, выход которого подключен к информационному входу регистра адреса, выход которого подключен к второму адресному входу блока памяти входных переменных, третий выход блока синхронизации подключен к входу записи-чтения регистра вывода и к входу чтения блока памяти выходных переменных, выход которого подключен к информационному входу регистра вывода, выход которого подключен к выходу результата устройства, четвертый выход блока синхроинзации подключен к входам установки счетчика адреса, первого и второго регистров управления, выход первого реги- стра управления подключен к первому информационному входу первого узла сравнения и к первому адресному входу блока памяти выходных переменных, второй адресный вход которого подключен к выходу шифратора, выход первого узла сравнения подключен к информационному входу первого регистра управления, выходы второго регистра управления подключены к первым входам элементов И группы, выходы которых подключены соответственно к информационным входам второго регистра управления, отличающееся тем, что, с целью повышения быстродействия, устройство содержит второй узел сравнения, мультиплексор констант, триггер и мультиплексор маски, причем, вход числа входных переменных устройства подключен к информационному входу счетчика адреса, второй выход блока синхронизации подключен к входам записи-считывания регистра адреса, первого и второго регистров управления, четвертый выход блока синхронизации подключен к входу установки в О триггера, выход которого подключен к входу записи- считывания регистра числа, выход которого подключен к управляющему входу мультиплексора маски, выход которого подключен к входу шифратора, информационные входы которого подключены соответственно к выходам второго регистра управления, выход регистр адреса подключен к первому информационному входу второго узла сравнения, выход которого подключен к счетному входу триггера, информационный выход счетчика адреса подключен к информационному входу регистра числа и к управляющему входу мультиплексора констант, выход которого подключен к второму информационному входу второго узла сравнения, информационные входы второй группы устройства подключены соответственно к информационным входам мультиплексора констант, выходы первой и второй групп блока памяти входных переменных подключены соответственно к второму информационному входу первого узла сравнения и к вторым входам элементов И группы, тактовый вход и вход начальной установки устройства подключены соответственно к тактовому входу и к входу начальной установки блока синхронизации.

211778763

22 Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический процессор | 1985 |

|

SU1305704A1 |

| Лингвистический процессор | 1985 |

|

SU1280381A1 |

| Логический процессор | 1982 |

|

SU1108454A1 |

| Управляющий процессор | 1984 |

|

SU1290341A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Устройство для сопряжения электронной вычислительной машины с дискретными датчиками | 1982 |

|

SU1084774A1 |

| Лингвистический процессор для обработки диагностической информации | 1989 |

|

SU1672417A1 |

| Многовходовой сигнатурный анализатор | 1987 |

|

SU1478220A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| Логический процессор | 1986 |

|

SU1315995A1 |

Изобретение относится к области вычислительной техники и может быть использовано для реализации логико-лингвистических алгоритмов, включающий выбор группы лингвистических правил, в зависимости от выполнения логического условия. Целью изобретения является повышение быстродействия обработки лингвистических правил. Устройство для реализации логических алгоритмов, заданных в лингвистической форме, содержит мультиплексор адреса, счетчик адреса, регистр адреса, блок памяти входных переменных, первый узел сравнения, первый регистр управления, мультиплексор констант, второй узел сравнения, триггер, регистр числа, группу элементов И, второй регистр управления, мультиплексор маски, шифратор, блок памяти выходных переменных, регистр вывода, блок синхронизации. 9 ил., 4 табл. (Л С

Таблица истинности счетчика адреса 2

Таблица 2 Таблица истинности первого 6 регистра управления

Таблица истинности мультиплексора 1 адреса

где X - безразличное состояние.

Таблица истинности регистра 10 числа

Таблица 3

Таблица 4

76

4- -1

35

iputf

25

88з

Фиг.2

54 itS

1778763

Ы

95

4J

96

Фиг.Ь

#

ш п

фиг. 7

1 f4 Ь

-i frj;a

п

-н (

П

77

ремсннш А

72

t Запись /пекущего papanfmffci S регистр а феса

ТЗ Дехремен/л -счетчика адреса

ТЬ

1- Чтение с/з памяти Зыход- ного парсгме пра

Z.3anuct Выходного параметра В регистр Зонных

Начало

)

Фиксация mejfsf- щего змте/лгя 6 регистре чыслег

Да

| Palm R., Lux.zy Sets and Systems 31 (1989) page 133-149 | |||

| Elsever Science | |||

| Publishers B.V.(North Holland) Авторское свидетельство СССР № 1521119,кл.G 06 F15/20 1990. |

Авторы

Даты

1992-11-30—Публикация

1990-07-17—Подача