(Л С

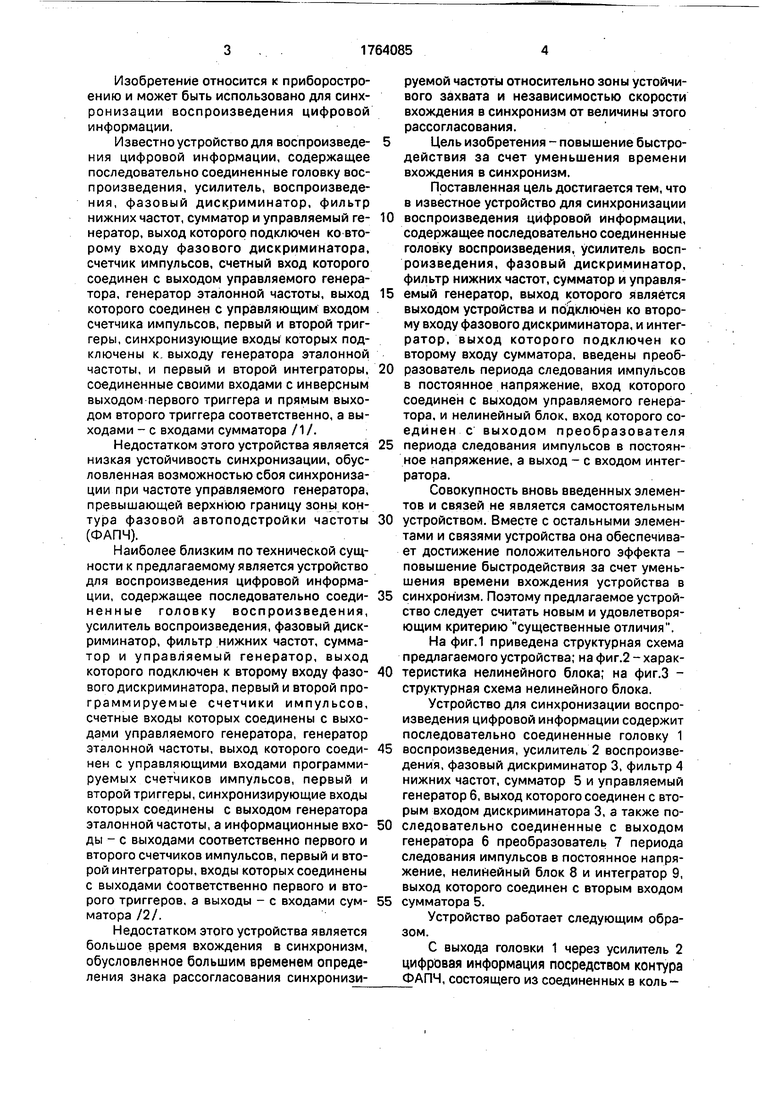

Изобретение относится к приборостроению и может быть использовано для синхронизации воспроизведения цифровой информации. Цель изобретения - повышение быстродействия за счет уменьшения времени вхождения в синхронизм. Сущность изобретения: устройство содержит 1 головку (1) воспроизведения, 1 усилитель (2) воспроизведения, 1 фазовый дискриминатор (3), 1 фильтр (4) нижних частот, 1 сумматор (5), 1 управляемый генератор (6), 1 преобразователь (7) периода следования импульсов в постоянное напряжение, 1 нелинейный блок (8) и 1 интегратор (9). 1 - 2 -3-4-5-6-7-8-9-5, 6-3. Зил.

Фиг.1

N 0

|ь iO 00

;сл

Изобретение относится к приборостроению и может быть использовано для синхронизации воспроизведения цифровой информации.

Известно устройство для воспроизведе- ния цифровой информации, содержащее последовательно соединенные головку воспроизведения, усилитель, воспроизведения, фазовый дискриминатор, фильтр нижних частот, сумматор и управляемый ге- нератор, выход которого подключен ко второму входу фазового дискриминатора, счетчик импульсов, счетный вход которого соединен с выходом управляемого генератора, генератор эталонной частоты, выход которого соединен с управляющим входом счетчика импульсов, первый и второй триггеры, синхронизующие входы которых подключены к выходу генератора эталонной частоты, и первый и второй интеграторы, соединенные своими входами с инверсным выходом первого триггера и прямым выходом второго триггера соответственно, а выходами - с входами сумматора /1/.

Недостатком этого устройства является низкая устойчивость синхронизации, обусловленная возможностью сбоя синхронизации при частоте управляемого генератора, превышающей верхнюю границу зоны контура фазовой автоподстройки частоты (ФАПЧ).

Наиболее близким по технической сущности к предлагаемому является устройство для воспроизведения цифровой информации, содержащее последовательно соеди- ненные головку воспроизведения, усилитель воспроизведения, фазовый дискриминатор, фильтр нижних частот, сумматор и управляемый генератор, выход которого подключен к второму входу фазо- вого дискриминатора, первый и второй про- граммируемые счетчики импульсов, счетные входы которых соединены с выходами управляемого генератора, генератор эталонной частоты, выход которого соеди- нен с управляющими входами программируемых счетчиков импульсов, первый и второй триггеры, синхронизирующие входы которых соединены с выходом генератора эталонной частоты, а информационные вхо- ды - с выходами соответственно первого и второго счетчиков импульсов, первый и второй интеграторы, входы которых соединены с выходами соответственно первого и второго триггеров, а выходы - с входами сум- матора 111.

Недостатком этого устройства является большое время вхождения в синхронизм, обусловленное большим временем определения знака рассогласования синхронизируемой частоты относительно зоны устойчивого захвата и независимостью скорости вхождения в синхронизм от величины этого рассогласования.

Цель изобретения - повышение быстродействия за счет уменьшения времени вхождения в синхронизм.

Поставленная цель достигается тем, что в известное устройство для синхронизации воспроизведения цифровой информации, содержащее последовательно соединенные головку воспроизведения, усилитель воспроизведения, фазовый дискриминатор, фильтр нижних частот, сумматор и управляемый генератор, выход которого является выходом устройства и подключен ко второму входу фазового дискриминатора, и интегратор, выход которого подключен ко второму входу сумматора, введены преобразователь периода следования импульсов в постоянное напряжение, вход которого соединен с выходом управляемого генератора, и нелинейный блок, вход которого соединен с выходом преобразователя периода следования импульсов в постоянное напряжение, а выход - с входом интегратора.

Совокупность вновь введенных элементов и связей не является самостоятельным устройством. Вместе с остальными элементами и связями устройства она обеспечивает достижение положительного эффекта - повышение быстродействия за счет уменьшения времени вхождения устройства в синхронизм. Поэтому предлагаемое устройство следует считать новым и удовлетворяющим критерию существенные отличия.

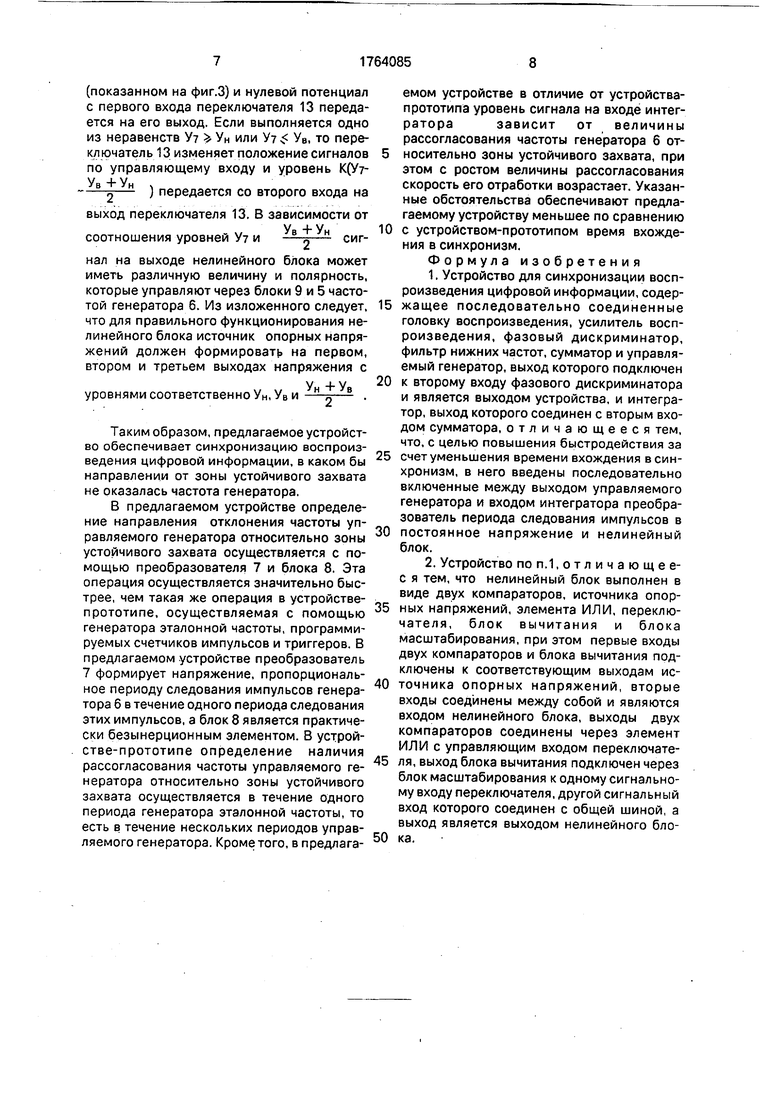

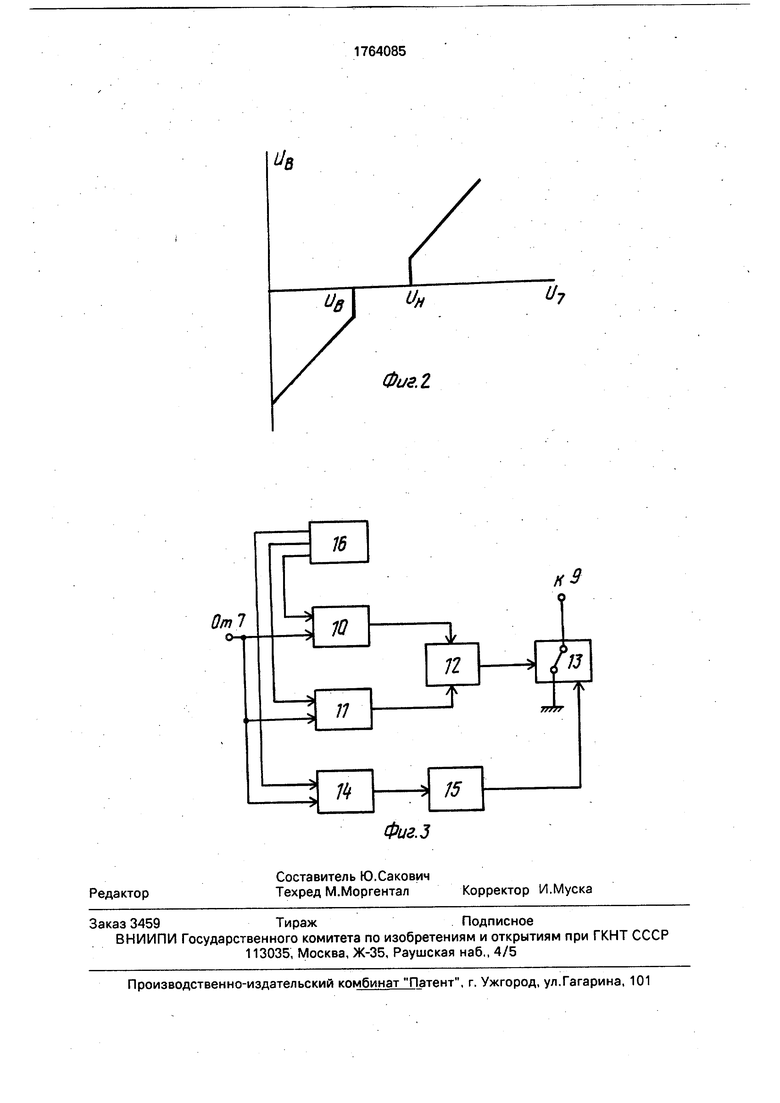

На фиг.1 приведена структурная схема предлагаемого устройства; на фиг.2 - характеристика нелинейного блока; на фиг.З - структурная схема нелинейного блока.

Устройство для синхронизации воспроизведения цифровой информации содержит последовательно соединенные головку 1 воспроизведения, усилитель 2 воспроизведения, фазовый дискриминатор 3, фильтр 4 нижних частот, сумматор 5 и управляемый генератор 6, выход которого соединен с вторым входом дискриминатора 3, а также последовательно соединенные с выходом генератора 6 преобразователь 7 периода следования импульсов в постоянное напряжение, нелинейный блок 8 и интегратор 9, выход которого соединен с вторым входом сумматора 5.

Устройство работает следующим образом.

С выхода головки 1 через усилитель 2 цифровая информация посредством контура АПЧ, состоящего из соединенных в кольцо генератора 6, дискриминатора 3, фильтра 4 и сумматора 5, управляет частотой и фазовым сдвигом вырабатываемых генератором 6 импульсов.

Схема, состоящая из преобразователя 7 и блока 8, осуществляет проверку соответствия частоты импульсов генератора 6 в зоне устойчивого захвата контура ФАПЧ. Преобразователь 7 формирует постоянное напряжение, уровень Ут которого пропорционален периоду следования импульсов генератора 6. Сигнал уровня Ут с выхода преобразователя 7 поступает на вход блока 8. Характеристика блока 8 (зависимость уровня УЗ выходного напряжения от уровня Ут входного) имеет вид (фиг.2): О, .

У8 .

К(У7-Ун g Ув). приУ7 УниУ7 У

где Ун и Ув - уровни напряжения на выходе преобразователя 7, соответствующие нижней и верхней границам частотной зоны устойчивой работы контура ФАПЧ,

К - постоянный коэффициент (крутизна характеристики).

Если частота генератора 6 меньше нижней границы зоны устойчивого захвата контура ФАПЧ, то формируемое преобразователем 7 напряжение превышает уровень У„ , на выходе блока 8 появляется сигнал положительной полярности, причем уровень этого сигнала тем больше, чем больше отклонение частоты генератора 6 от нижней границы зоны устойчивого захвата контура ФАПЧ. Сигнал с выхода блока 8 интегрируется интегратором 9, и результат интегрирования поступает на второй вход сумматора 5. В этих условиях сигнал на выходе интегратора 9 и на втором входе сумматоре 5 увеличивается, а следовательно, увеличиваются уровень сигнала на выходе сумматора 5 и частота генератора 6. Этот процесс продолжается до тех пор, пока частота генератора 6 не увеличится настолько, что контур ФАПЧ войдет в зону устойчивого захвата, уровень У напряжения на выходе преобразователя 7 окажется в пределах Ув - Ун, уровень сигнала на выходе блока 8 станет равным нулю, а напряжение на выходе интегратора 9 и втором входе сумматора 5 перестанет изменяться.

Если частота генератора 6 больше верхней границы зоны устойчивого захвата контура ФАПЧ, то формируемое преобразователей 7 напряжение становится меньше уровня У6, на выходе блока 8 появляется сигнал отрицательной полярности, причем уровень этого сигнала тем больше, чем

больше отклонение частоты генератора 6 от верхней границы зоны устойчивого захвата контура ФАПЧ. В этих условиях сигнал на выходе интегратора 9 и на втором входе

сумматора 5 уменьшается, а следовательно, уменьшаются уровень сигнала на выходе сумматора 5 и частота генератора 6. Этот процесс продолжается до тех пор, пока частота генератора 6 не уменьшится настоль0 ко, что контур ФАПЧ войдет в зону устойчивого захвата, уровень У напряжения на выходе преобразователя 7 окажется в пределах Ув - УН , уровень сигнала на выходе блока 8 станет равным нулю, а напря5 жение на выходе интегратора 9 и втором входе сумматора 5 перестанет изменяться. На фиг.З приведена структурная схема нелинейного блока 8. Нелинейный блок со0 держит компараторы 10 и 11, элемент 12 ИЛИ, переключатель 13, блок 14 вычитания, масштабный блок 15 и источник опорных напряжений 16. Первые входы первого и второго компараторов 10 и 11 соединены с

5 суммирующим входом блока 14 вычитания и являются входом нелинейного блока, вторые входы компараторов соединены с первым и вторым выходами источника опорных напряжений соответственно. Выходы ком0 параторов соединены с соответствующими входами элемента 12 ИЛИ, выход которого подключен к управляющему входу переключателя 13. Вычитающий вход блока 14 соединен с третьим выходом источника

5 опорных напряжений 16, его выход через масштабный блок 15 подключен к одному из сигнальных входов переключателя 13, другой сигнальный вход которого подключен к нулевой шине, а выход является выходом

0 нелинейного блока.

Нелинейный блок работает следующим образом.

Если формируемое преобразователем 7 напряжение У превышает уровень Ун или

5 является более низким, чем Ув, то на выходах компараторов 10 и 11 соответственно появляется потенциал, соответствующий логической 1, а на выходе элемента 12 ИЛИ и управляющем входе.переключателя

0 13 появляется разрешающий потенциал, изменяющий положение переключателя 13. Из величины уровня У в блоке 14 вычита- . ется уровень (Ун + Ув)/2, а их разность масштабируется в блоке 15, на выходе которого

чп.1 УН Ь УВч 1появляется уровень К( ). Если

уровень Уу лежит между уровнями Ун и Ув, то есть Ув У Ун, то сигнал на управляющем входе блока 13 отсутствует, переключатель 13 находится в исходном состоянии

(показанном на фиг.З) и нулевой потенциал с первого входа переключателя 13 передается на его выход. Если выполняется одно из неравенств Уу Ун или Уу Ув, то переключатель 13 изменяет положение сигналов по управляющему входу и уровень К(УуУ + У ) передается со второго входа на

выход переключателя 13. В зависимости от

У + У

соотношения уровней Уу и -2-х-- сигнал на выходе нелинейного блока может иметь различную величину и полярность, которые управляют через блоки 9 и 5 частотой генератора 6. Из изложенного следует, что для правильного функционирования нелинейного блока источник опорных напряжений должен формировать на первом, втором и третьем выходах напряжения с

Ун +Ув уровнями соответственно Ун, Ув

Таким образом, предлагаемое устройство обеспечивает синхронизацию воспроизведения цифровой информации, в каком бы направлении от зоны устойчивого захвата не оказалась частота генератора.

В предлагаемом устройстве определение направления отклонения частоты управляемого генератора относительно зоны устойчивого захвата осуществляется с помощью преобразователя 7 и блока 8. Эта операция осуществляется значительно быстрее, чем такая же операция в устройстве- прототипе, осуществляемая с помощью генератора эталонной частоты, программируемых счетчиков импульсов и триггеров. В предлагаемом устройстве преобразователь 7 формирует напряжение, пропорциональное периоду следования импульсов генератора 6 в течение одного периода следования этих импульсов, а блок 8 является практически безынерционным элементом. В устройстве-прототипе определение наличия рассогласования частоты управляемого генератора относительно зоны устойчивого захвата осуществляется в течение одного периода генератора эталонной частоты, то есть в течение нескольких периодов управляемого генератора. Кроме того, в предлагаемом устройстве в отличие от устройства- прототипа уровень сигнала на входе интеграторазависит от величины рассогласования частоты генератора 6 относительно зоны устойчивого захвата, при этом с ростом величины рассогласования скорость его отработки возрастает. Указанные обстоятельства обеспечивают предлагаемому устройству меньшее по сравнению

с устройством-прототипом время вхождения в синхронизм.

Формула изобретения

к второму входу фазового дискриминатора и является выходом устройства, и интегратор, выход которого соединен с вторым входом сумматора, отличающееся тем, что, с целью повышения быстродействия за

счет уменьшения времени вхождения в синхронизм, в него введены последовательно включенные между выходом управляемого генератора и входрм интегратора преобразователь периода следования импульсов в

постоянное напряжение и нелинейный блок.

UH

U7

Фиг. 2.

| Устройство для синхронизации воспроизведения цифровой информации | 1980 |

|

SU907580A1 |

| Устройство для синхронизации воспроизведения цифровой информации | 1986 |

|

SU1377905A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

Авторы

Даты

1992-09-23—Публикация

1990-11-16—Подача