(5А) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ВОСПРОИЗВЕДЕНИЯ ЦИФРОВОЙ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации сигналов воспроизведения цифровой информации | 1986 |

|

SU1462413A1 |

| Устройство для синхронизации воспроизведения цифровой информации | 1986 |

|

SU1377905A1 |

| Устройство для синхронизации воспроизведения цифровой информации | 1990 |

|

SU1764085A1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| Способ формирования периодических двуполярных колебаний с заданным фазовым сдвигом и устройство для его реализации | 2016 |

|

RU2625047C1 |

| Устройство для формирования синхросигнала при воспроизведении с носителя магнитной записи | 1986 |

|

SU1462414A1 |

| УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 2014 |

|

RU2565526C1 |

| Устройство автоматической подстройки частоты | 1983 |

|

SU1231607A1 |

| Способ записи цифровой информации | 1983 |

|

SU1112393A2 |

| Приемник сигналов офсетной фазовой манипуляции | 1987 |

|

SU1434559A1 |

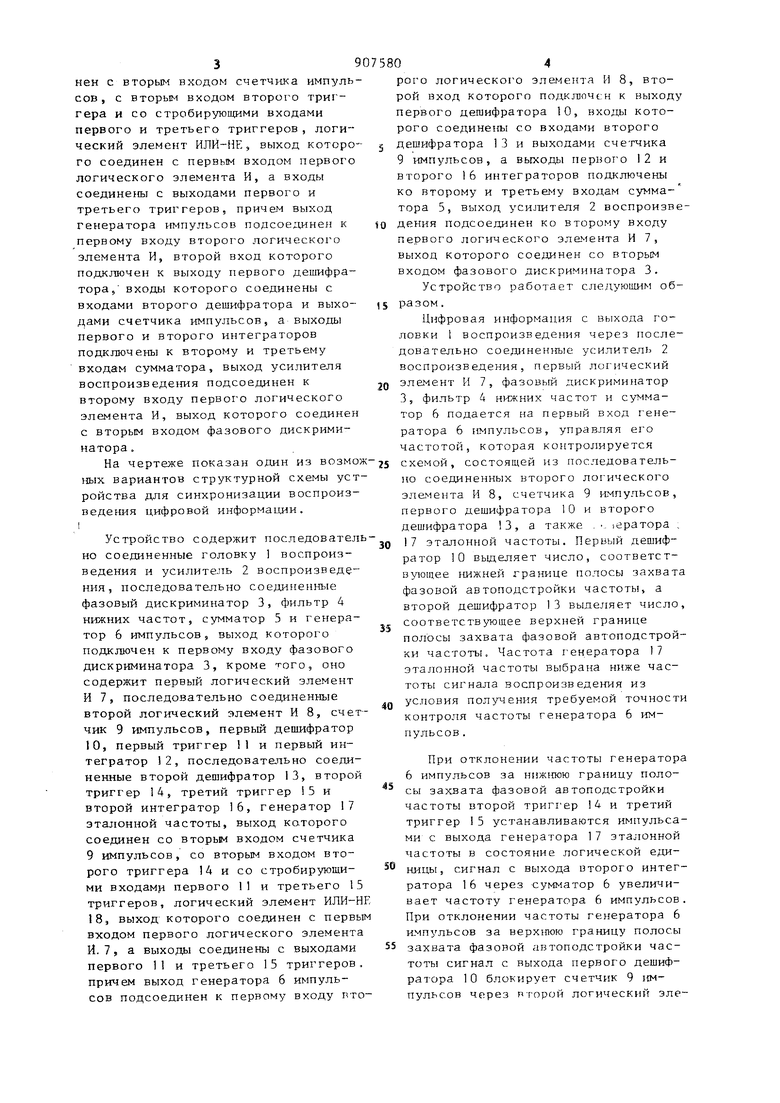

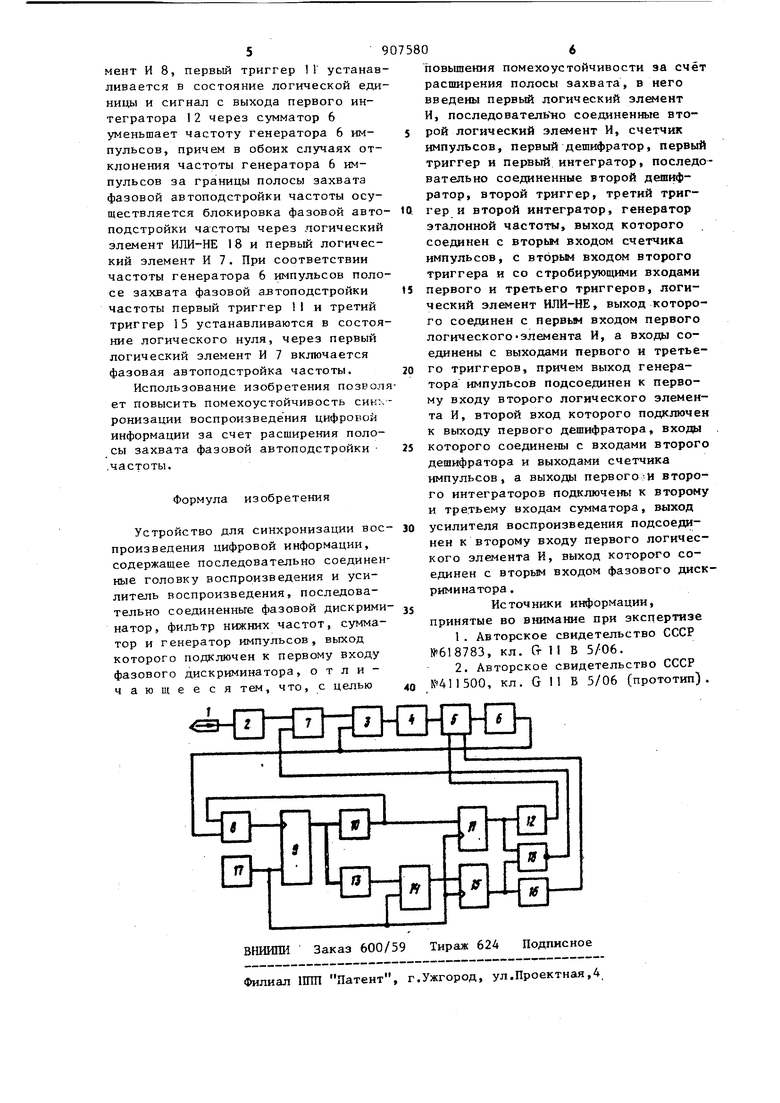

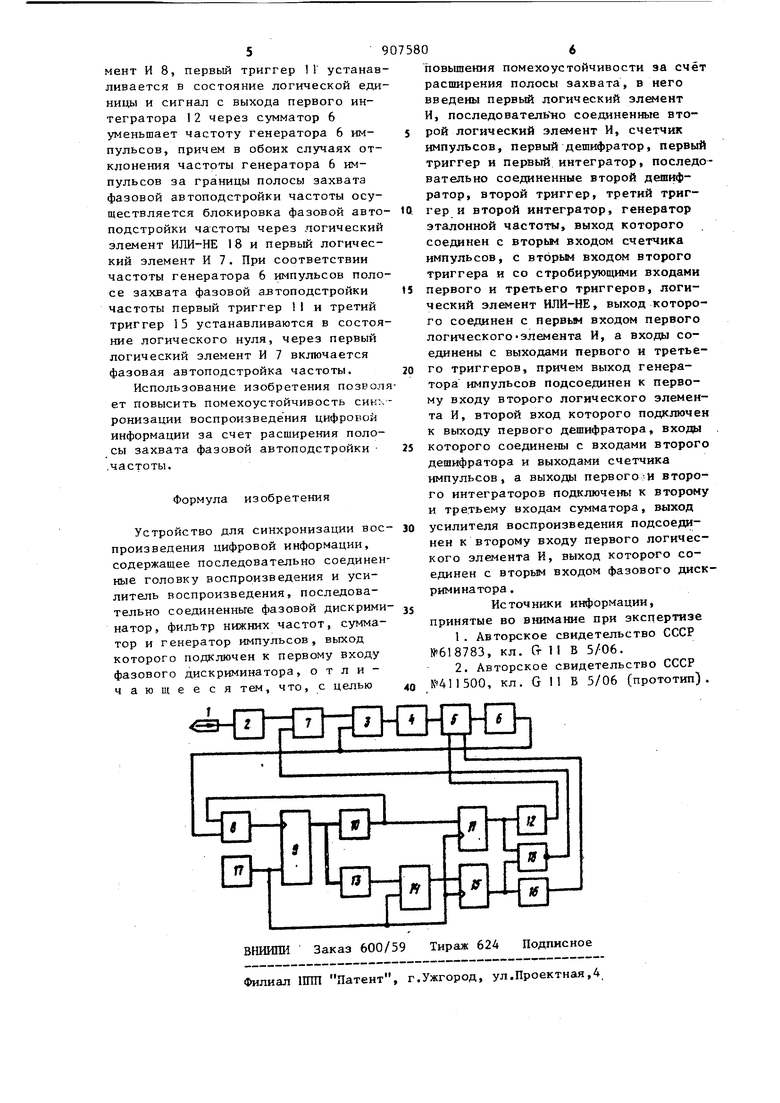

Изобретение относится к магнитной записи, а именно к устройствам для синхронизации воспроизведения цифровой информации. Известно устройство для синхрон зации воспроизведения цифровой информации, содержащее генератор импульсов, ко входу которого подклоч последовательно соедасиенные суммат фильтр нижних частот и фазовый дискриминатор, а также триггеры и логические элементы И 1 J. Недостаток этого устройства заключается в низкой помехозащищенно ти. Известно также устройство, соде жащее последовательно соедикеняие управляемый генератор, фазовый дис риминатор, фильтр нижних частот, сумматор и генератор импульсов, вы :од которого соединен со вторым входом фазового дискриминатора, частотный дискриминатор, первый вход которого связан с выходом управляющего генератора, второй вход - с входом управ ля жого генератора, а выход его подсоединен к второму входу су1в4атора и управляемому входу управляемого генератора Г2. . Недостаток известного устройства состоит в малой П(1ехоза1ф1щенности вследствие малой полосы захвата. Цель изобретения - повьшение помехоустой чивости за счет раснгирения полосы захвата. Эта цель достигается тем, что в устройство для синхронизации воспроизведения цифровой информации введешь первый логический элемент И, последсжательно соединенные второй логический элет«ент И, счетчик импульсов, первый дещифратор, первый триггер и первый интегратор, последовательно соединенмле второй дешифратор, второй триггер, третий триггер и второй интегратор, генератор эталонной частоты, выход которого соединен с вторым входом счетчика импульсов, с вторь м входом второго триггера и со стробирующими входами первого и третьего триггеров, логи ческий элемент ИЛИ-НЕ, выход которого соединен с первым входом первого логического элемента И, а входы соединены с выходами первого и третьего триггеров, причем выход генератора импульсов подсоед 1нен к первому входу второго логического элемента И, второй вход которого подключен к выходу первого дешифратора/ входы которого соединены с входами второго дешифратора и выходами счетчика импульсов, а выходы первого и второго интеграторов подключены к второму и третьему входам сумматора, выход усилителя воспроизведения подсоединен к второму входу первого логического элемента И, выход которого соединен с вторым входом фазового дискриминатора . На чертеже показан один из возмож-25 ных вариантов структурной схемы уст ройства для синхронизации воспроизведения цифровой информации. I Устройство содержит последовател но соединенные головку 1 воспроизведения и усилитель 2 воспроизведения, последовательно соединенные фазовый дискриминатор 3, фильтр 4 нижних частот, сумматор 5 и генератор 6 импульсов 5 выход которого подключен к первому входу фазового дискриминатора 3, кроме того, оно содержит первый логический элемент И 7, последовательно соединенные второй логический элемент И 8, счет чик 9 импульсов, первый депшфратор 10, первый триггер 11 и первый интегратор 12, последовательно соединенные второй дешифратор 13, второй триггер 14, третий триггер 15 и второй интегратор 16, генератор 17 эталонной частоты, выход которого соединен со вторьм входом счетчика 9 импульсов, со вторым входом второго триггера 14 и со стробирующими входам первого 11 и третьего 15 триггеров, логический элемент ИЛИ-Н 18, выход которого соединен с первь входом первого логического элемента И. 7, а выходы соединены с выходами первого 1 и третьего 15 триггеров причем выход генератора 6 импульсов подсоединен к первому входу пто

рого логического элемента И 8, второй вход которого подключен к выходу первого дешифратора 10, входы которого соединены со входа ш второго дешифратора 13 и выходами счетчика 9 импульсов, а вьгходы первого 12 и второго 16 интеграторов подключены ко второму и третьему входам сумматора 5, выход усилителя 2 воспроизведения подсоединен ко второму входу первого логического эламента И 7, выход которого сое;« нен со вторым входом фазового дискриминатора 3.

Устройство работает следующим образом .

Цифровая информация с выхода головки 1 воспроизведения через последовательно соединенные усилитель 2 воспроизведения, первый логический элемент И 7, фазовый дискриминатор 3, фильтр 4 нижних частот и сумматор 6 подается на первый вход генератора 6 1мпульсов, управляя его частотой, которая контролируется схемой, состоящей из последовательно соединенных второго логического элемента И 8, счетчика 9 импульсов, первого дешифратора 10 и второго дешифратора 3, а также . - lepaTopa : 17 эталонной частоты. Первый дешифратор 10 вьщеляет число, соответствующее нижней границе полосы захвата фазовой автоподстройки частоты, а второй дешифратор 13 выделяет число, соответствующее верхней границе полосы захвата фазовой автоподстройки частоты. Частота генератора 17 эталонной частоты выбрана ниже частоты сигнала воспроизведения из условия получения требуемой точности контроля частоты генератора 6 импульсов . При отклонении частоты генератора 6 импульсов за нижютю границу полосы захвата фазовой автоподстройки частоты второй триггер 14 и третий триггер I5 устанавливаются импульсами с выхода генератора 17 эталонной частоты в состояние логической единицы, сигнал с выхода второго интегратора 16 через сумматор 6 увеличивает частоту генератора 6 импульсов. При отклонении частоты генератора 6 импульсов за верхнюю границу полосы захвата фазовой автоподстройки частоты сигнал с вь1хода первого дешифратора 10 блокирует счетчик 9 импульсов через РТорой логический элемент И 8, первый триггер 11 устанавливается в состояние логической единицы и сигнал с выхода первого интегратора I2 через сумматор 6 уменьшает частоту генератора 6 импульсов, причем в обоих случаях отклонения частоты генератора 6 импульсов за границы полосы захвата фазовой автоподстройки частоты осуществляется блокировка фазовой авто подстройки частоты через логический элемент ИЛИ-НЕ 18 и первый логический элемент И 7. При соответствии частоты генератора 6 импульсов полосе захвата фазовой а-втоподстройки частоты первый триггер 1I и третий триггер 15 устанавливаются в состояние логического нуля, через первый логический элемент И 7 включается фазовая автоподстройка частоты.

Использование изобретения позволет повысить помехоустойчивость сик:чронизации воспроизведения цифровой информации за счет расширения полосы захвата фазовой автоподстройки .частоты.

Формула изобретения

Устройство для синхронизации воепроизведения цифровой информации, содержащее последовательно соединенные головку воспроизведения и усилитель воспроизведения, последовательно соединенные фазовой дискриминатор, фильтр нижних частот, сумматор и генератор импульсов, выход которого подключен к первому входу фазового дискриминатора, отличающееся тем, что, с целью

повышения помехоустойчивости за счёт расширения полосы захвата, в него введены первый логический элемент И, последовательно соединенные второй логический элемент И, счетчик импульсов, первый дешифратор, первый триггер и первый интегратор, последовательно соединенные второй дешифратор, второй триггер, третий триггер и второй интегратор, генератор эталонной частоты, выход которого соединен с вторым входом счетчика импульсов, с втбрьм входом второго триггера и со стробирующими входами первого и третьего триггеров, логический элемент ИЛИ-НЕ, выход которого соединен с первьм входом первого логического-элемента И, а входы соединены с выходами первого и третьего триггеров, причем выход генератора импульсов подсоединен к первому входу второго логического элемента И, второй вход которого подключен к выходу первого дешифратора, входы которого соединены с входами второго дешифратора и выходами счетчика импульсов, а выходы первого и второго интеграторов подключены к второму и третьему входам сумматора, выход усилителя воспроизведения подсоединен к второму входу первого логического элемента И, выход которого соединен с вторым входом фазового дискриминатора .

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-02-23—Публикация

1980-07-01—Подача