частота

Фиг 1

Изобретение относится к резервируемой аппаратуре цифровой вычислительной техники и может быть использовано для построения высоконадежных цифровых устройств.

Цель изобретения - повышение надежности устройства.

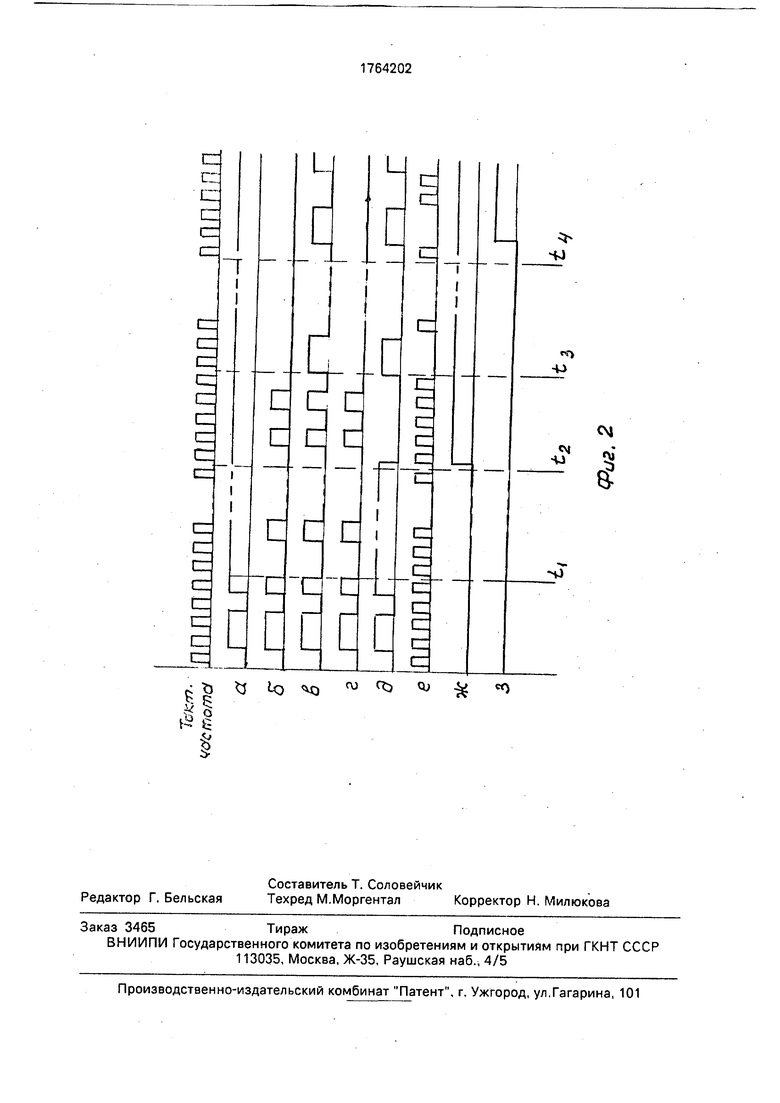

На фиг.1 представлена схема предлагаемого устройства; на фиг.2 - временные диаграммы, поясняющие принцип его работы.

Трехканальное мажоритарно-резервированное устройство содержит в каждом из каналов резервируемые блоки 1-3, первые 4-6, вторые 7-9, третьи 10-12 элементы И, первые 13-15, вторые 16-18 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, элементы И-НЕ 19-21, счетчики сбоев 22-24, триггеры отключения канала 25-27, триггеры строба 28-30. Устройство содержит также мажоритарный элемент 31, элемент нечетности 32, первый 33, второй 34, третий 35, четвертый 36 элементы И, первый 37, второй 38, третий 39 элементы ИЛИ, элемент НЕ 40, элемент задержки 41.

Выходы резервируемых блоков 1-3 соединены с первыми входами первых элементов И 4-6, выходы которых подключены к первым входам первых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 13-15, вторых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 16-18 и вторых элементов И 7-9, к соответствующим входам мажоритарных элементов 31 и элемента нечетности 32, к объединенным S-и D- входам триггеров строба 28-30.

Выходы первых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 13-15 соединены с первыми входами элементов И-НЕ 19-21, выходами соединенных со счетными входами счетчиков сбоев 22-24, установочные входы которых объединены и подключены к шине устройства Сброс.

Выходы соответствующих разрядов счетчиков сбоев 22-24 соединены с соответствующими входами третьих элементов И 10-12, выходами соединенных с счетными входами триггеров отключения канала 25- 27, S-и D-входы которых объединены и подключены к шине Лог.1 устройства, а их R-входы соединены между собой и с объединенными одноименными входами триггеров строба 28-30 и подключены к входу установки в нуль устройства.

Инверсные выходы триггеров отключения канала 25-27 соединены с вторыми входами первых элементов И 4-6, а прямые выходы - с соответствующими входами первого элемента ИЛИ 37, выход которого соединен с первым входом первого элемента И 33. Второй вход элемента И 33 соединен с выходом элемента нечетности 32, а выход

подключен к первому входу второго элемента И 34 и входу элемента НЕ 40, выход которого соединен с первыми входами третьего элемента И 35 и четвертого элемента И 36.

Выход третьего элемента И 35 подключен к счетным входам триггеров строба 28-30 каждого из каналов, выходы которых соединены с вторыми входами вторых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 16-18. Выходы по0 следних подключены к вторым входам вторых канальных элементов И 7-9, выходы которых соединены с соответствующими входами второго элемента ИЛИ 38. Выход элемента ИЛИ 38 подключен к второму вхо5 ду второго элемента И 34, выход которого соединен с первым входом третьего элемента ИЛИ 39.

Выход мажоритарного элемента 31 подключен к второму входу четвертого элемен0 та И 36, выходом соединенного с вторым входом третьего элемента ИЛИ 39, выход которого является выходом устройства и соединен с вторыми входами первых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 13-15 каждого

5 из каналов.

Тактовый вход устройства подключен к второму входу третьего элемента И 35 и входу элемента задержки 41, выход которого соединен с вторыми входами элементов

0 И-НЕ 19-21 каждого из каналов.

Устройство работает следующим образом.

Синхронная работа резервируемых блоков 1-3 обеспечивается их идентично5 стью в исправном состоянии и синхронным поступлением входных сигналов Вх.1, Вх.2, Вх.З. Влияние незначительных взаимных задержек (сдвигов фронтов) сигналов на выходах блоков 1-3 (фиг.2а,б.в) на

0 работу узлов устройства, выявляющих отказавший канал, устраняется при помощи опроса соответствующих сигналов импульсами такт, частота (входной сигнал тактовой частоты). Предполагается, что отказы

5 имеют вид постоянный нуль или постоянная единица. После отказа одного из блоков, при выявлении различия сигналов в двух оставшихся, неверным считается сигнал, не изменивший своего значения.

0 На приведенной временной диаграмме для определения принято, что в момент ti происходит отказ блока 1 типа постоянная единица, а в момент времени :з - отказ блока 2 типа постоянный нуль.

5 В момент включения устройства по шине Установка в 0 происходит отрицательный импульс, который устанавливает триггеры 25-27 и 28-30 в исходное состояние. При этом на управляющие входы элементов И 4-6 поступает сигнал логической

единицы, разрешающий прохождение информации через эти элементы. По шине Сброс приходит положительный импульс, который обнуляет счетчики 22-24.

Пусть в исходном состоянии блоки 1-3 исправны и существуют сигналы Х1,Х2,ХЗ. При этом на выход устройства поступает сигнал с выхода мажоритарного элемента 31 через открытый элемент И 36 и элемент ИЛИ 39. Нулевым сигналом с выхода элемента ИЛИ 37 (триггеры 25-27 обнулены) блокируется прохождение сигналов через элементы И 33 и И 34.

Затем в момент ti в блоке 1 произойдет отказ, в результате которого сигнал Х1 перейдет в единичное состояние, а сигналы Х2 и ХЗ не изменятся. При этом так же, как и при трех исправно работающих блоках, на выход устройства продолжает поступать правильный сигнал с выхода мажоритарного элемента 31 (фиг.2г), совпадающий с сигналами Х2 и ХЗ.

Сигнал с выхода устройства поступает на входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 13-15. При этом прохождение сигналов через элементы 20,23,11,26 и 21,24,12,27 запрещено нулевыми сигналами с выходов , элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 14 и 15, так как на входах последних присутствуют одинаковые сигналы - выходной и один из сигналов Х2 и ХЗ. В моменты несовпадения выходного сигнала с сигналом Х1 на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 появляются сигналы логической единицы, которые стробируются сигналами тактовой частоты на элементе И-НЕ 19 и поступают в виде импульсов на счетчик 22 до тех пор, пока последний не заполняется, что будет обнаружено элементом И 10, сигнал с выхода которого опрокидывает триггер 25 (момент времени t2). Сигнал логического нуля с инверсного выхода триггера 25 отключает первый канал, блокируя элемент И 4, при этом сигнал Х1 во время дальнейшей работы будет все время находится в нулевом состоянии. Элементы 28,16 и 7 вследствие этого будут заблокированы, а на выходе элемента нечетности 32 появится сигнал логического нуля (фиг.2д).

Триггеры 29 и 30 осуществляют сдвиг сигналов Х2 и ХЗ исправных блоков в соответствии с сигналами тактовой частоты, поступающими через открытый элемент И 35 (фиг.2е) на С-входы указанных триггеров. Далее через элементы 17,8,38 и 18,9,38 эти сигналы поступают на элемент И 34, через который они не могут пройти на выход устройства, так как он блокирован нулевым сигналом на его втором входе.

Таким образом, на выход устройства по- прежнему поступает сигнал с выхода мажоритарного элемента 31.

При приходе очередного сигнала по ши5 не Сброс счетчик 22 будет обнулен и снова заполнен сигналами с выхода элемента И- НЕ 19, однако на работу устройства это не влияния не окажет, так как триггер 25 работает в режиме запоминания (фиг,2ж).

10 Пусть в момент тз после отключения первого неисправного блока произойдет отказ в блоке 2, при этом сигнал Х2 перейдет в нулевое состояние, а сигнал ХЗ не изменится.

15 Как только сигналы Х2 и ХЗ разойдутся (т.е. примут разную полярность), на выходе элемента нечетности 32 логический нуль сменится логической единицей, тактовые импульсы через элемент И 35 перестанут

0 поступать на триггеры 29 и 30, они зафиксируют предыдущие состояния сигналов Х2 и ХЗ. Далее сигнал ХЗ сменит полярность и снова совпадает с сигналом Х2, при этом элемент нечетности 32 даст разрешение че5 рез элемент И 33, элемент НЕ 40 на прохождение очередного тактового импульса через элемент И 35 на триггеры 29 и 30. Триггер 29 своего состояния не изменит, так как не меняется входной сигнал Х2. Элемент ИСК0 ЛЮЧАЮЩЕЕ ИЛИ 17 нулевым уровнем на своем выходе запретит прохождение сигнала Х2 через элемент И 8. Триггер 30 изменит свое состояние на противоположное, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 18 при сравне5 нии предыдущего состояния сигнала ХЗ с его текущим значением зафиксирует на своем выходе логическую единицу и тем самым разрешит прохождение текущего состояния сигнала ХЗ через элемент И 9, ИЛИ 38 и

0 далее через открытый элемент И 34 на выход устройства. При следующей смене полярности сигнала ХЗ элемент нечетности 32 перейдет в состояние нуль и т.д. Таким образом, на выход устройства будет поступать

5 сигнал ХЗ с третьего исправного блока. При этом по-прежнему элементы 21,24,12,27 будут заблокированы нулевым сигналом с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15. На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ

0 14 в моменты несовпадения сигналов Х2 и ХЗ появляются сигналы логической единицы, которые стробируются сигналами тактовой частоты на элементе И-НЕ 20 и поступают в виде импульсов на счетчик 23

5 до тех пор, пока последний не заполнится, что будет обнаружено элементом И 11, сигнал с выхода которого опрокинеттриггер 26. Сигнал логического нуля с инверсного выхода триггера 26 (фиг,2з) отключает второй канал, блокируя элемент И 5, в результате

чего сигнал Х2 в дальнейшем будет находиться в состоянии логического нуля (начиная с момента времени t4). Таким образом, оба сигнала Х1 и Х2 будут находиться в состоянии логического нуля, однако на работу устройства это не влияет, так как на шину Выход будет по-прежнему поступать сигнал с выхода исправного третьего блока.

При приходе очередного сигнала по шине Сброс счетчик 23 будет обнулен, а затем снова заполнен сигналами с выхода элемента И-НЕ 20, однако на работу устройства это не влияние не окажет, так как триггер 26 работает в режиме запоминания.

Элемент задержки 41 учитывает временные рассогласования сигналов обратной связи с выхода устройства и сигналов Х1,Х2,ХЗ. Тем самым устраняется срабатывание элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 13-15 из-за временных сдвигов указанных сигналов.

Так как нумерация блоков 1 -3 и соответствующих им каналов прохождения информации может быть выбрана произвольно, вышеизложенное справедливо для различных сочетаний отказов в различных блоках и каналах.

Формула изобретения Трехканал ьное мажоритарно-резервированное устройство, содержащее лервый- четвертый элементы И, первый-третий элементы ИЛИ, мажоритарный элемент, элемент НЕ, и причем в каждом из каналов резервируемый блок, первый-третий элементы И, первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И-НЕ, счетчик сбоев, триггер отключения канала и триггер строба, в каждом канале выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом элемента И-НЕ, выход которого подключен к счетному входу счетчика сбоев, установочный вход которого объединен с установочными входами счетчиков сбоев других каналов и подключен к шине Сброс устройства, S- и D-входы триггеров отключения каналов подключены к шине Лог,1 устройства, R-входы триггеров отключения каналов и триггеров строба подключены к входу установки в О устройства, отличающееся тем, что, с целью повышения надежности устройства, в него введены элемент нечетности, элемент задержки и в каждый канал второй элемент ИСКЛЮЧАЮЩЕЕ

ИЛИ, причем в каждом канале выход резервируемого блока соединен с первым входом первого элемента И, выход которого подключен к первому входу первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, объединенным S-и

D-входам триггера строба, первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и второго элемента И и соответствующим входам мажоритарного элемента и элемента нечетности, выходы соответствующих разрядов счетчика сбоев соединены с соответствующими входами третьего элемента И, выход которого подключен к счетному входу триггера отключения канала, инверсный выход которого соединен с вторым входом

первого элемента И канала, а прямой выход - с соответствующим входом первого элемента ИЛИ, выход которого подключен к первому входу первого элемента И, второй вход которого соединен с выходом элемента

нечетности, а выход подключен к первому входу второго элемента И и входу элемента НЕ, выход которого соединен с первыми входами третьего и четвертого элементов И, выход третьего элемента И подключен к

счетному входу триггера строба каждого из каналов, выход которого соединен со вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к второму входу второго элемента И каналов,

выход которого соединен с соответствующим входом второго элемента ИЛИ, выход которого подключен к второму входу второго элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, выход мажоритарного элемента подключен к второму входу четвертого элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ, выход которого является выходом устройства и соединен с

вторыми входами первых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ каждого из каналов, тактовый вход устройства подключен к второму входу третьего элемента И и входу элемента задержки, выход которого соединен с вторыми входами элементов И-НЕ каждого из каналов.

CM

I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для мажоритарного выбора асинхронных сигналов | 1986 |

|

SU1420661A1 |

| Адаптивное резервированное устройство | 1983 |

|

SU1174929A1 |

| Мажоритарное устройство | 1981 |

|

SU1096767A1 |

| Резервированная система | 1982 |

|

SU1101827A1 |

| Устройство для компенсации реактивной мощности | 1990 |

|

SU1746463A1 |

| Многоканальное устройство для выборки информации | 1975 |

|

SU591855A1 |

| УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ | 2008 |

|

RU2396591C1 |

| Трехканальное мажоритарно-резервированное устройство | 1983 |

|

SU1160616A1 |

| ТРЕХЭЛЕМЕНТНОЕ МАЖОРИТАРНОЕ УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2007 |

|

RU2347264C2 |

| Устройство для учета перемещающихсяиздЕлий | 1979 |

|

SU830439A1 |

Использование: резервирование аппаратуры цифровой вычислительной техники для построения высоконадежных цифровых устройств. Сущность изобретения: устройство содержит: 3 резервируемых блока

$ о мэ

ГО (5 Qj

«)

| Патент США № 3538498, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Кинематографический аппарат | 1923 |

|

SU1970A1 |

| Трехканальное мажоритарно-резервированное устройство | 1983 |

|

SU1160616A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1992-09-23—Публикация

1990-05-28—Подача