ГС элемента ИЛИ соединен с выходом блока контроля своего канала, выход - с одним из входов дешифратора кода управления каждого блока адаптации, выход четвертого элемента ИЛИ подключен к одному из входов 11749 29 шестого элемента ИЛИ в кажчом канале, выход шестого элемента ИЛИ соединен с входом разрешения дешифратора кода управления, выходы которого подключены к управляющим входам мажоритарного элемента своего канала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивное резервированное устройство | 1981 |

|

SU962959A1 |

| Устройство для резервирования и восстановления микропроцессорной системы | 1986 |

|

SU1374235A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

| АДАПТИВНОЕ МАЖОРИТАРНО-РЕЗЕРВИРОВАННОЕ УСТРОЙСТВО | 1988 |

|

SU1566986A1 |

| Резервированное устройство | 1989 |

|

SU1605236A1 |

| Устройство для обработки информации | 1990 |

|

SU1758649A1 |

| Устройство для обмена информацией синхронных каналов | 1978 |

|

SU752320A1 |

| Трехканальная резервированная микропроцессорная система | 1985 |

|

SU1378287A1 |

| Резервированная система | 1988 |

|

SU1584137A1 |

Л.ЦАПТИВНОЕ РЕЗЕРВИРОВАННОЕ УСТРОЙСТВО, содержащее в каждом ка1нале блок контроля, вход которого подключен к контрольному выходу резервируемого блока данного канала, элемент сравнения, элемент ИЛИ и блок адаптации, содержащий дешифратор кода управления, три элемента И, пять элементов РШИ, мажоритарный элемент, элемент НЕ и первый триггер, отличающееся тем, что, с целью повышения надежности за счет тосстановления мажоритарной конфигурации при восстановлений работоспособности ранее отказавших каналов, в него введены четвертый элемент И, счетчик, таймер и второй триггер, а информационный выход резервируемого блока в каждом канале подключен к первому входу элемента сравнения и к одному из входов мажоритарных элементов каждого канала, второй вход элемента сравнения в каждом канале соединен с выходом мажоритарного, элемента, выход элемента сравнения соединен с входом U элемента НЕ, первыми входами первого и второго элементов И блока адап1-;П1У{И данного канала и одним из входов первого элемента ИЛИ и второго элемента И блоков адаптации остальных каналов, выход второго элемента И соединен с первым 5-входом первого триггера, второй S-вход которого соединен с вторым входом первого элемента И, выходом синхроимпульса своего резервируемого блока и с первым входом третьего элемента И, второй и третий входы которого соединены с выходами первого элемента ИЛИ и элемента НЕ соответственно, выход третьего элемента И подключен к первому входу второго элемента ИЛИ, второй вход которого Ф подключен к выходу сброса резервируе(Л мого блока своего канала, К -входу первого триггера, первомуR-входу второго триггера и первому входу третьего элемента ИЛИ, второй вход второго элемента ИЛИ соединен с выходом таймера и вторым R-входом второго триггера, выход второго элемента ИЛИ подключен к входу установ sl ки в О счетчика, счетный вход кото451 рого соединен с выходом первого элемента И и входом запуска таймера, вход сброса которого подключен D к выходу третьего элемента ИЛИ, первый выход счетчика соединен с первым входом четвертого элемента И, второй выход - с вторым входом третьего элемента ИЛИ и 5-входом второго триггера, третий вход третьего элемента ИЛИ подключен к выходу четвертого элемента И, второй вход которого подключен к выходу второго триггера и первым входам четвертого и пятого элементов ИЛИ, второй вход шестого элемента ИЛИ соединен с выходом первого триггера, второй пнго

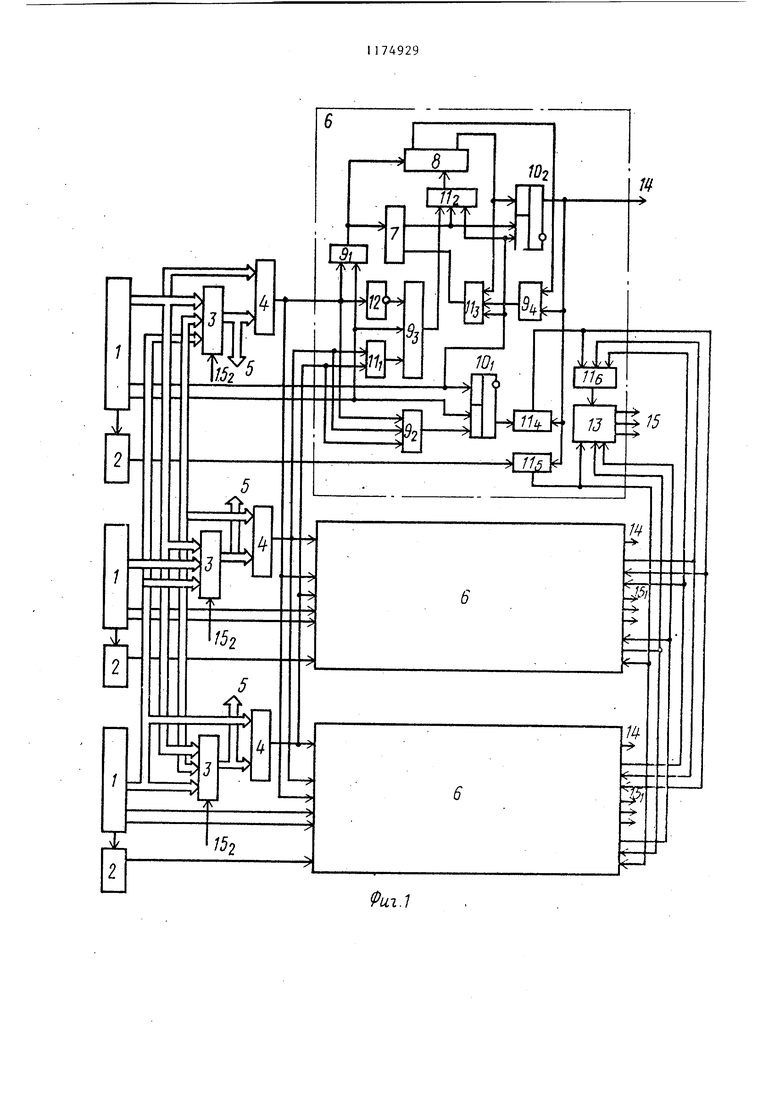

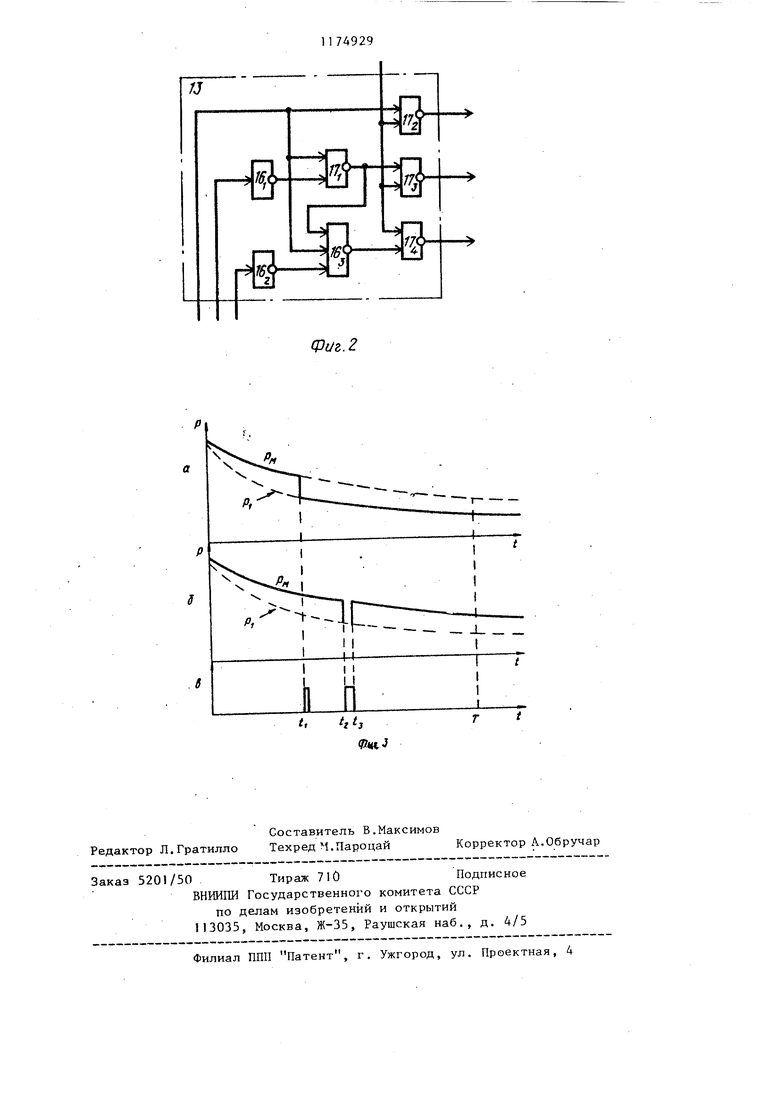

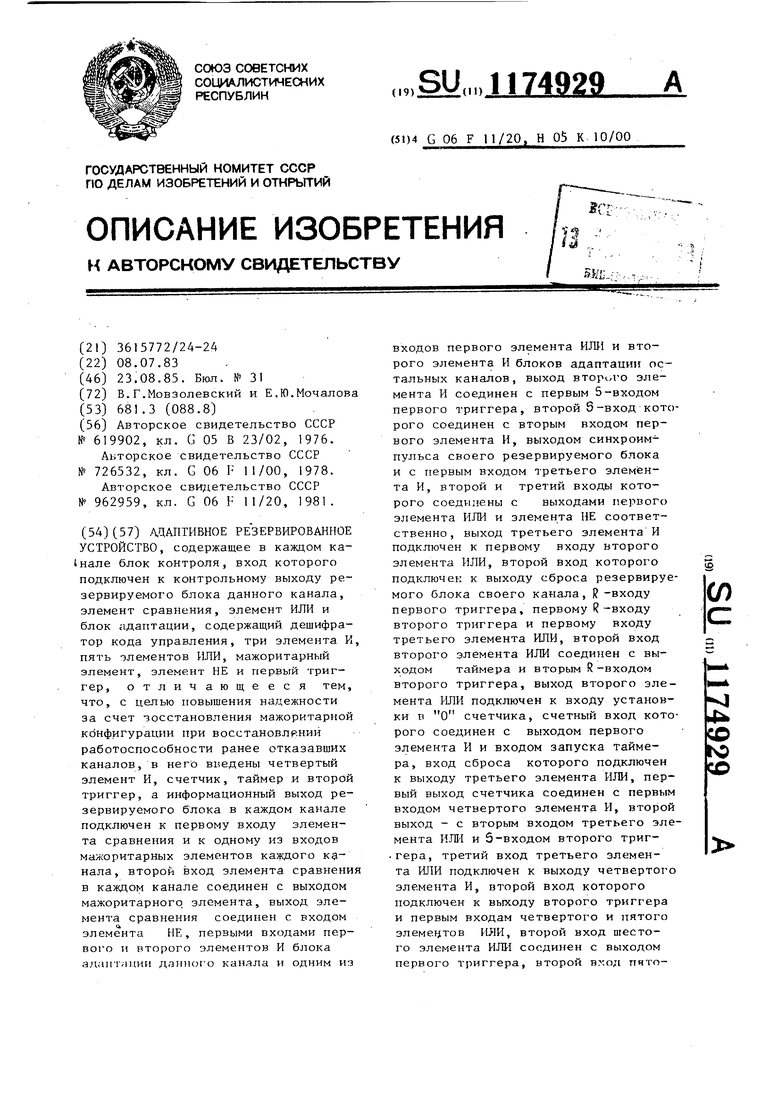

Изобретение относится к автомати ке и вычислительной технике и может быть использовано в устройствах, использующих схемные методы повышения надежности функционирования. Цель изобретения - повьшхение надежности устройства за счет восстановления мажоритарной конфигурации при восстановлении работоспособности ранее отказавших каналов. На фиг.1 представлена структурная схема предлагаемого устройства; на фиг.2 - схема дешифратора кодов управления,- на фиг.За, S и & - графики вероятности безотказной работы известного и предлагаемого устройст прн наличии сбоев в момент времени i| или временных отказов в момент Х2 . , Устройство (фиг.1) содержит в кaж дом канапе резервируемый блок 1, блок 2 контроля, управляемый мажоритарный элемент 3, элемент 4 сравнения, выходную информационную магистраль 5 и блок 6 адаптации, таймер 7 СЧ1 тчик 8, элементы И 9 ,.. . , 9, триггеры 10( и lOj, элементы ИЛИ 11 ..., 11 и НЕ 12, дешифратор 13 кодов управления, выход 14 отказа, управляющие выходы 1 5 блока адаптации II управляющие входы 152 мажоритарных элементов, инверторы 16 и 16 и элементы И-НЕ 17| ,... 17 5-. Управляемые мажоритарные элементы 3.(фиг.1) в зависимости от сигналов на входах 152 Управления с выходов дешифраторов 13 осуществляют функцию мажоритирования выходной информации блоков 1 или передачу на выходные магистрали 5 сигналов с выхода одного из блоков 1. При коде сигнала 1I1 на управляющих входах 152 э-;емент 3 выполняет функцию 2 из 3, при коде 100 на выходную магистраль 5 пропускается выходная информация блока 1 первого канала, при коде 010 пропускается информация второго канала, при коде 001 - информация третьего канала. Дешифратор 13 управляет работой мажоритарного элемента 3 своего канала по сигналу разрешения с выхода элемента ИЛИ 11, и сигналами контроля, поступающими с выходов элементов 11,, всех каналов. При отказе канала сигнал контроля с выхода элемента 11с поступает на входы всех дешифраторов 13 низким уровнем - логическим О. Если отказ отсутствует, то сигнал на выходе элемента ИЛИ 11 имеет высокий уровень логическую 1. С выхода элемента ИЛИ 11 в каждом канале на разрешающий вход дешифратора 13 кодов управления. Гна первые входы элементов И+НЕ 172,..., 174 фиг.2) поступает логический О, в результате чего на выходе дешифратора 13 (на выходах элементов И-НЕ 17 ,.. . , 17., фиг.2) присутствует код 111, по которому элемент 3 (фиг.1) реализует функцию 2 из 3. Если с выхода элемента ИЛИ 11 поступает сигнал отказа (логическая 1), то на выходе дешифратора появляется код, который зависит от сигналов на входах дешифратора 13, поступающих с вывсех канаходов элементов лов, в соответствии с которыми элемент 3 пропускает информацию с входных магистралей на выходную 5: i 10 010 2-й ка1 1 . О О 01 3-й каЭлемент 4 производит сравнение информации, поступающей на его вход с информационной магистрали контролируемого канала, с информацией на выходе мажоритарного элемента 3 сво .го канала и выдает результат сравне ния на входы элемента НЕ 12 и элеме тов И 9, и 92 блока 6 своего канала и на. входы элементов ИЛИ 11 , и И 9 блоков 6 двух других каналов. Сигнал ошибки на выходе элемента 4 им , етвысокий уровень - логическую 1 при отсутствии ошибки на выходе эл мента 4 - низкий уровень (логический О). Таймер 7 отрабатывает время, в течение которого осуществляется на копление ошибок в счетчике 8. Сигнал ошибки формируется элементом 4 в результате несравнения информации своего канала с мажоритированной-ин формацией и-поступает на первый вход элемента И 9 блока 6 своего канала, на второй вход которого с выхода синхроимпульса блока 1 посту пает стробирующий сигнал. Стробирую щий .сигнал вырабатывается в каждом канале схемой управления (не цоказана) при .каждом подключении информации на внутренних магистралях.Стробирование осуществляется для исключения, ложных отказов в результате внутренних задержек элементов При появлении сигнала отказа с выхода элемента 4 элемент 9 по стробирующему сигналу с выхода блока 1 вырабатывает импульс, поступающий на счетный в-ход .счетчика 8 и на вход запуска таймера 7. После отработки установленного времени таймер 7 вырабатывает импульс сброса, .поступающий .на входы установки в О триггера 102 и через элемент ИЛИ 112 счетчика 8. Сброс таймера в нулевое состояние осуществляется через элемент ИЛИ Пз сигналами, поступающими с выхода блока приведения в исходное состояние, с выхода элемента И 9 и с второго выхода счетчика 8. Счетчик 8 накапливает сигналы ошибки, поступающие с выхода эле9мента И 9. Сигналы на ныходах счетчиха 8 появляются при отсчет. определенного количества импульсон. Количество импульсов, необходимых для появления сигнала на втором выходе, больше, чем количество импульсов, необходимых для появления сигнала на первом выходе. Если счетчик 8 отсчитывает количество импульсов (колнчество ошибок, выработанных элементом 4}, необходимых для появления сигнала на своем втором. выходе за время, меньше установотенного в таймере 7, то импульс с этого в.ыхода установит триггер IOj в единичное состояние и через элемент 1 1- приведет таймер 7 в исходное состояние. Единичный сигнал на выходе 14 триггера 10 свидетельствует об отказе данного канала и вьщается на индикацию отказа через элемент ИЛИ 1.14 своего канала и через.элементы ИЛИ 1Ц блоков 6 адаптации остальных кана.пон на разрешающий вход дешифраторов 13 кодов управления. Если сигнал ошибки продолжает поступать на счетный вход счетчика 8 и на вход запуска таймера 7, то сброс последнего в исходное состояние будет происходить в момент появления импульса на первом выходе -счетчика 8 через элементы И 94 и ИЛИ 11. Счетчик 8 и триггер 10 установятся в нулевое состояние таймером 7, если за время, отрабатываемое таймером 7, счетчик 8 накопит меньшее число имиульсов, чем необходимо для появления сигнала на первом выходе счетчика 8. Таким образом, сброс сигнала отказа с выхода.14 триггера 10, свидетельствующего о восстановлении работоспособности канала, происходи в том случае, если число отк-азов, поступающих с .выхода элемента 4 за время, отрабатываемое таймером 7, будет гораздо меньше числа отказов, при котором происходит переполнение счетчика 8 ошибок и фиксация триггером lOj отказа канала. . Сброс счетчика 8 ошибок происходит и в том случае, если в момент появления импульса строба с выхода элемента 4 одного из соседних канплов на элемент ИЛИ 11 поступает сигнал отказа, а на выходе элемента 4 своего канала отказ отсутствует.- Такая комбинация свидетельствует о том, что ошибки в каналах не возникают одновременно и допускается работа в режиме 2 из 3. Триггер 10, устанавливается в единичное состояние (выдает сигнал отказа на дешифраторы 13 кодов управления) в момент прихода стробирут-чцего импульса при одновременно появлении отказов в трех каналах на входе элемента И92. Такая ситуация возникает, при совпадающих во времен от .азах в двух любых каналах. . В основу работы предлагаемого устройства (фит. 1) положен следующий при цип. Адаптивное резервируемое устройс Во (фиг.1) работает в мажоритарном ре жиме при единичных сбоях в информации, возникающих в разные моменты времени в блоках 1. Определение сбой в информации блока 1 или его отказ, .осуществляется по интенсив.ности отказов с выхода элемента меж канального сравнения информации (по количеству отказов за определенное время). При превышении определенного.лисла отказов с выхода элемента сравнения канал считается отказавшим и устройство (фиг,1 переходит на работу от одного из исправных каналов, работоспособность кото рого определяется блоком 2 внутрика нального контроля (например, контр.о лем информацией на четность). При восстановлении работоспособности ранее.отказавшего канала, что опред ляется по исчезновению браков с выхода элемента сравнения данного ка нала либо по уменьшению их интенсив ности ниже установленного уровня, происходит восстановление мажоритар ной конфигурации, -что повышает надежность устройства. Устройство работает следующим об разом. , После в.ключения питания в блоках вырабатывается импульс установки в нулевое состояние элементов с памятью, по которому с вькодов блоков 1 подается сигнал, по которому счетчик 8, таймер 7 и триггеры 10у и 10 устанавливаются в исходное (нулевое) состояние. С выходов элементов ИЛИ 1Ц каждого блока 6 на дешифраторы 13 кодов управления через элементы ИЛИ 11 поступает логи ческий О, по которому дешифраторы 13 вьщают на управляющие входы мя5коритарных элементов 3 код 111, устанавливающий режим 2 из 3. 0тказы в каналах отсутствуют, поэтому выполняется сравнение информации на элементах 4. на выходах блоков 2 контроля и элементов 4 устанавливаются нулевые сигналы. В процессе длительного функционирования в контролируемых каналах возникают неисправности, которые приводят к появлению ошибок в информационной магистрали резервируемого блока 1. Первая неисправность, которая возникает, например, в первом канале, обнаруживается элементом 4-сравнения, вырабатывающим логическую 1 и блоком 2 контроля, выраб атыв ающим . Принцип обнаружения и фиксации ошибок следующий. При возникновении отказа в одном из каналов, например в первом, элемент 4 сравнения вырабатывает сигнал отказа, который поступает на элементы И 9 и 92 и НЕ 12 своего блока 6 адаптации и элементы ИЛИ П и И 9 других блоков 6. Стробирующий импульс разрешает прохождение сигнала отказа через элемент И 9 на счетный вход счетЧика 8 ошибок и вход запуска таймера 7. В блоках 6 адаптации соседних каналов счетчик 8 и таймер 7 не запускаются, так как отсутствуют отказы на выходах элементов 4 этих каналов. Таймер 7 блока 6 первого канала запускается и начинает отрабатывать установленное время. Счетчик 8 увеличивает .свое состояние на единицу с приходом каждого импульса отказа. . Если количество отказов за вре- . мя 1 , отрабатываемое таймером 7, меньше допустимого, например, при одиночных сбоях в контролируем.ом -канале, то за время Г. сигнал на втором выходе счетчика 8 не появляется и таймер вырабатывает импульс, устан а влив акиций счетчик 8 в О и подтверждающий исходное состояние lOj. Так как состояния триггера 162 во всех блоках 6 адаптриггеровтации не изменились, то дешифраторы 13 кодов управления вырабатывают код 111, при котором блока 1 выполняет функцию 2 из 3. На сигналы внутриканального контроля с выходов блоков 2 дешифраторы 13 не реагируют, так как на их разрешающем входе присутствует О с выходов элементов ИЛИ 11. Если счетчик 8 накапливает количество ошибок, превышающее допустимое за время работы таймера 7, то на втором выходе счетчика 8 появляется сигнал, устанавливающий триггер 10д в единичное состояние, и через элемент ИЛИ 11 сбрасывает таймер 7 в нулевое состояние. Единичный сигнал с выхода триггера 10 поступает на выход 14 индикации отказа канала, через элементы ИЛИ 11 и 11 своего канала и через элементы 1 Ц блоков 6 остальных каналов на разрешающие входы дешифраторов 1 и разрешает прохождение сигналов с выходов элементов ИЛИ 11 на дешифраторы 13 всех блоков 6 для управле ния элементами 3. Так как в данном случае с выхода элемента ИЛИ 11 бл ка 6 первого канала и с выхода,блока 2 поступает сигнал отказа триггера 10, а на выходах элементов Ilj блоков 6 второго и третьего каналов отказы отсутствуют /как по внутриканальному контролю блоков 2, так и по междуканальному с выходов триггеров lOj) то на входы дешифрато- ров 13 подается код 100, по которому на их выходах формируется код 010 и элементы 3 всех каналов пропускают на информационные магистрали 5 информацию с магистрали, блока 1 второго канала. Элементы 4 сравнения в этом случае сравнивают информацию на магистралях своего канала с информацией на выходе блока 1 второго канала, что позволяет продолжать контролировать отказавший канал по исправному. Таким образом, при полном отказе одного канала устройство фиг.1 переходит на работу от одного исправного канала, что повьш1ает надежность до величины Pfвepoятнoc ти безотказной работы одного канала а второй исправный канал переводится в резерв. При возникновении одиночного сбоя или временного отказа в канале, на который произошла перестройка (в данном случае - на второй канал), блок 2 внутриканального контроля вырабатывает сигнал отказа, который че рез эл.емент ИЛ1-1 11 блока 6 адаптации поступает на входы дешифраторов 1 всех каналов. Код на входах дешифраторов 13 - 110, по нему на управляющие входы элементов 3 поступает код 001 и на выходные магистрали 5 всех каналов пропускается информация блока 1 третьего канала. При исчезновении временного отказа во втором канале на вход дешифраторов 13 подается код 100 и элементы 3 снова пропускают на выход 5 информацию второго канала. Если отказ второго каната постоянный, то по сигналу внутриканального контроля блока 2 второго канала элементы 3 пропускают информацию третьего канала (первый канал продолжает оставаться в состоянии отказа и на входе дешифраторов 13 присутствует код 100), элемент. 4 второго канала вырабатывает отказ по результату сравнения информации блока 1 второго канала с информацией на магистрали 5 исправного третьего канала, счетчик. 8 блока 6 второго канала накапливает отказы и устанавливает триггер 10 2 в единичное состояние, на выходе элемента П устанавливается постоянно сигнал отказа второго канала и на выходе дешифраторов 13 присутствует код 00 , подключающий через элементы 3 на выходные магистрали 5 информацию блока 1 третьего канала. Аналогично могут быть осуществлены фиксация отказов и перестройки конфигурации при любом другом порядке возникновения отказов в каналах. Рассмотрим работу устройства (фиг.1) при возникновении типичных отказовых ситуациях. Возникновение отказов в двух каналах, не совпадающих во времени. Элемент 4 первого канала вырабатывает сигналы отказов, которые накапливаются счетчиком 8 блока 6. При возникновении отказа, например, в третьем канале его элемент 4 сравнения вырабатывает сигнал, который сосчитывается счетчиком 8 блока 6 третьего канала и одновременно поступит через элемент ИЛИ 111 блока 6 первого канала на элемент И 9. Так как ошибки в первом и третьем каналах не перекрьшаются во времени, то на выходе 14 первого канала в этот момент времени сигнал ошибки отсутствует (выдается логический О). По стробирующему сигналу на выходе элемента 9 блока 6 первого канала (так как на его входах . присутствуют единицы появляется vtMпульс который через элемент ИЛИ IIj сбрасывает счетчик 8 в О. Триггеры ICj не изменяют своего исходного состояния и элемент 3 продолжает выполнять функцию 2 из 3 .Таким образом,, отказы, вырабатываемые элементами сравнения 4 Двух каналов в разные моменты времени, сбрасывают накапливаемые счетчиками 8 противоположных каналов откавы, удерживая тем самым работу элементов 3 в режиме мажоритара. Аналогичным образом поддерживает ся мажоритарная конфигурация элемен тов при возникновении отказов в трех к налахв разные моменты времени. При возникновении отказов в двух каналах одновременно, например в первом и втором, элементы 4 сравнения всех каналов вырабатывают сигналы отказов, поступающие на эле-, менты И 92 всех блоков 6 адаптации Сигналы на выходе элементов 9 по стробирующим сигналам устанавливают триггеры 10, блоков 6 в единичное состояние, логические 1 с выходов которых через свои элементы ИЛИ 114 -6 поступают на разре шающие входы дешифраторов 13 кодов управления, по которым выходной сиг нал дешифраторов 13 вырабатывается в зависимости от кода на выходах элементов 11. Так как элементы вну риканального контроля первого и вто рого каналов вырабатывают сигналы отказов,- то на входах, дешифраторов присутствует код ПО, по котррому . на управляющих входах элементов 3 устанавливается код 001 и на выходные магистрали 5 пропускается -ин формация блока 1 третьего канала. Отказ канала с последующим восста новлением работоспособности. При работе с одним отказавшим каналом, например первым, элемент 4 сравнивает информацию своего канала с информацией исправного (в Данном случае с информацией второго канала, которая пропускается элементами 3с выхода блока 1 второго канала на магист-. раль 5. В том случае, если отказ в первом канале устранится, например процессор работает с отказавшей страницей ПЗУ или ОЗУ, а затем переходит на работу с исправной страницей, то элемент 4 сравнения первого кана ла не вырабатывает сигнал .ошибки. Так как таймер 7 блока 6 первого канала запущен предьщущим сигналом отказа с выхода элемента 4 и отрабатывает время, а счетчик 8 не увеличивает своего состояния, то на первом его выходе не появляется сигнал сброса таймера 7 и через установлен.ное время последний вырабатывает сигнал, по которому триггер Ю устанавливается в нулевое состояние и на разрешающих входах дешифраторов 13 кодов управления.появляется логический О...На выходах дешифраторов 13 устанавливается Код 111, по кото.рому элементы 3 переходят на работу в мажоритарном режиме. Таким образом, предла1аемое устройство имеет повышенную надежность . за счет восстановления мажор.итарной конфигурации при восстановлении работоспособности ранее отказавших каналов особенно .в условиях помех и сбоев информации.

| Адаптивное резервированное устройство | 1977 |

|

SU619902A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Трехканальное мажоритарно-резервированное устройство | 1978 |

|

SU726532A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Адаптивное резервированное устройство | 1981 |

|

SU962959A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-08-23—Публикация

1983-07-08—Подача