Изобретение откосится к построе-; нию резервируемой аппаратуры цифровой вычислительной техники на потенциальных интегральных схемах, блоки которых обрабатывают информацию j сигналов в виде набора слов, полуслов или двойных слов, и пожет быть использовано для построения высоконадежных цифровых устройств. Цель изобретения - повьшение надеж- 0 ности устройства, в частности сохранение работоспособности при отказе двух каналов из трех.

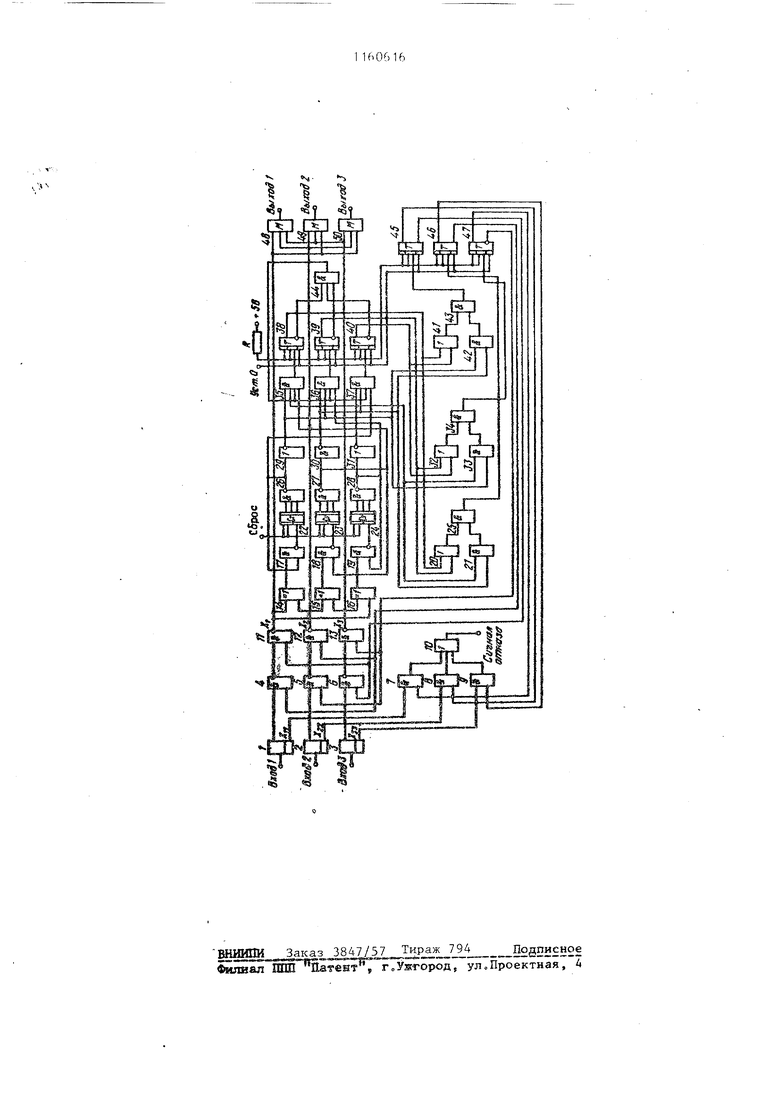

На чертеже представлена схема устройства,15

Устройство содержит резервируемые блоки 1-3 (с узлами алгоритмического контроля и исправления кратковременных отказов типа сбоев),элементы И-НЕ 4-6, элементы И 7-10, эле- 20 менты И-НЕ 11-13, элементы ИСКПЮЧАЮЩЕЕ ИЛИ 14-16, элементы И-НЕ 17-19, элемент ИЛИ 20, элемент И 21, счетчики 22-24, элемент И 25, элементы И-НЕ 26-28, инверторы 29-31, эле- 25 мент ИЛИ 32, элементы И 33-37, триггеры 38-40, элемент КП1Л 41, элементы И 42-44, триггеры 45-47 и мажоритарные элементы 48-50. .

Устройство работает следующим об- JQ разом,

В момент включения устройства по шине Установка в О приходит отрицательньп импульс, которьй устанавливает триггеры 38-40, 45-47 в исходное

35 состояние. При этом на управляющие входы элементов И-НЕ 4-6 и 11-13 поступает сигнал логической единицы5 разрешающий прохождение информации через эти элементы. По шине Сброс приходит пололсительный импульс, который обнуляет счетчики 22-24, при этом на вькодах элементов И-НЕ 26-28 появляется сигнал логической единицы, который разрешает прохождение сигналов с элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 14-16 на счетчики 22-24.

Пусть в исходном состоянии блоки 1-3 исправны и существуют сигналы X., х, Xj. Затем в какой-то момент 50 в блоке 1 произойдет катастрофический отказ, в результате чего сигнал х превратится в тождественньй нуль, а сигналы Хл и Xj изменятся. Тогда на выходах элементов ИСКЛЙЙАЩЕЕ ИЛИ 55 14 и 16 начнут появляться сигналы логической единицы в моменты несовпа.дения сигналов х и х с сигналом .

через элементы И-НЕ 17 и 19 до тех пор, гюка не заполнятся с-четчики 22 и 24, что будет обнаружено элементами И-НЕ 26 и 28, на выходах которых появится сигнал логического нуля, который поступит на управляющие входы .элементов И-НЕ 17 и 19 и запретит дальнейшее прохождение сигналов на счетчики 22 и 24. Сигналы логического нуля с выходов элементов И-НЕ 26 и I28, проинвертированные инверторами 29 и 31, пройдут через логический элемент И 35 и опрокинут триггер 38, в результате чего на выходе элемента 44 образуется сигнал логического ну-) ля, который запретит прохождение сигналов через элементы И 35-37. Триггеры 45-47 состояние не изменяют, в результате чего элементы И-НЕ 4-6 и 11будут пропускать сигналы, которые мажоритарными элементами 48-50 будут восстановлены на выходе устройства. При приходе очередного сигнала по шине Сброс счетчики 26 и 28 будут очищены, а затем заполнены сигналами с элементов И-НЕ 17 и 19, однако на работу устройства это никакого влияния не окажет в результате запрета прохождения сигналов через элементы И 35-37.

Пусть в некоторый момент времени после отказа первого блока произойдет катастрофический отказ в блоке 2, в результате чего сигнал х, превратится в тождественный нуль, а сигнал Xj не изменится. При этом произойдет кратковременная блокировка мажоритарных элементов 48-50, в результате чего на вькодах кратковременно зафиксируется сигнал тождественного нуля , При этом на выходе элемента ИС1ШЮЧАЮЩЕЕ ИЛИ 14 зафиксируется сигнал тождественного нуля, а на выходах элементов ИСКПЮЧ УОЩЕЕ ИЛИ 15 и 16 будет формироваться сигнал логической единицы в момент несовпадения сигнала X.J с сигналом тождественного нуля. Если отказ произойдет в такой момент времени, что счетчики 23 и 24 не будут заполнены до момента прихода импульса по шине Сброс, то эти счетчики будут очищены и подготовлены к заполнению после этого импульса. Как только эти счетчики будут заполнены, прохождение сигналов через элементы И-НЕ 18 и 19 будет запрещено. При этом логические функции элементов 20,21,25,32-34, 41-43 3 выбраны таким образом, что произойдет опрокидывание триггера 46 так, что сигнал логического нуля поступит на управляющие входы элементов И-НЕ 4 и 12, в результате чего в сигнале х подтвердится тождествеиньм нуль, а сиг-нал х изменится на тожд ственную единицу. При этом мажоритар ные элементы 48-50 деблокируются и начнут проп скать на выход третьего исправного блока. При приходе очередного импульса по шине Сброс счетчики 23 и 24 будут очищены, а затем заполнены, однако это не окаже влияния на работу предлагаемого устройства, поскольку триггеры 45-47 работают в режиме запоминания, а не счета. Если в блоке 2 произойдет от каз, приводящий к появлению в канал 2 сигнала разноименного с сигналом в канале 1, то кратковременной бло 16 , 4 кировки мажоритарных элементов не произойдет, а в остальном предлагаемое устройство будет работать аналогично. Если в какой-то момент времени в блоке 3 произойдет алгоритмический отказ, выявляемый устройством алгоритмического контроля и исправления кратковременных отказов так, что на выходе блока 3 появится сигнал Xjj отказа, то этот сигнал совместно с сигналом с прямого выхода триггера 46 пройдет через элементы И9иИЛИ10и на выходе устройства Сигнал отказа появится сигнал общего отказа. Поскольку нумерация блоков 1-3 и соответствующих им каналов прохождения информации может быть выбрана произвольно, проведенные рассуждения справедливы для различных сочетаний отказов в различных блоках и каналах.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для мажоритарного включения резервируемых логических блоков | 1985 |

|

SU1325727A1 |

| Трехканальное мажоритарно-резервированное устройство | 1990 |

|

SU1764202A1 |

| Резервированная система | 1982 |

|

SU1101827A1 |

| Резервированный делитель частоты | 1983 |

|

SU1163473A1 |

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

| Устройство для мажоритарного выбора сигналов | 1981 |

|

SU1018120A1 |

| Устройство для мажоритарного выбора сигналов | 1984 |

|

SU1238278A1 |

| Адаптивное резервированное устройство | 1983 |

|

SU1174929A1 |

| Резервированный генератор | 1978 |

|

SU746975A1 |

| Резервированное устройство | 1979 |

|

SU819995A1 |

ТРЕХКАНАПЬНОЕ МАЖОРИТАРНОРЕЗЕРВИРОВАННОЕ УСТРОЙСТВО, содержащее по числу каналов резервируемые блоки, информационные выходы которых подключены к первьяу входам соответствующих первых элементов И-НЬ, выходы которых подключены к первым входам вторьЕх элементов И-НЕ, выходы которых соединены с соответствующими входами мажоритарньсх элементов, выходы которых являются информаш онными выходами устройства , и первые триггеры, отличающееся тем, что, с целью повышения надежности, в него введены по числу каналов вторые триггеры, третьи и чет- . вертые элементы И-НЕ, элементы ИСКЛЮЧАЮЩЕЕ ШИ, элементы НЕ, первые четвертые элементы И, первые и вторые элементы ИЛИ и пятЫй элемент И, в каждом канале входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены соответственно к выходам вторых элементов И-НЕ данного и последующего каналов, а выход - к первому входу третьего элемента И-НЕ данного канала, выход ко- ., торого соединен со счетным входом счетчика данного канала установочные входы которого соединены с шиной Сброс, а выходы - через четвертый элемент И-НЕ с вторым входом третьего элемента И-НЕ и входом элемента НЕ данного канала и первым входом первого элемента И предыдущего канала, выход каждого из которых соединен с синхровходом первого триггера одноименного канала, R-вход триггера соединен с шиной Установка в О, S и Dвходы через резистор - с шиной питания, а инверсньш выход - с входом пятого элемента И, выход которого .подключен к вторым входам первьгх элементов И, контрольные выходы резервируемых блоков соединены с первыми входами вторых элементов И, выходы которых соединены через первый элемент ИЛИ с контрольным выходом устройства, а I вторые входы с прямыми выходами втосл рых триггеров предыдущего канала, инверсный выход каждого из которых соединен с вторым входом второго элемента данного канала и вторым входом первого элемента предьщутцего канала, синхровход - с выходом .третье го элемента И данного канала, R-вход с шиной Установка в О, а S и D-BXCbt) ды - с одноименными входами первых триггеров, прямой выход каждого из о сз: которых соединен с первым входом второго элемента ИЛИ данного канала и вторьтм входом второго элемента ИЛИ О5 последующего канала, а выход - с первым входом третьего элемента И данного канала, второй вход которого подключен к выходу четвертого элемента И, первьй вход которого соединен с третьим входом первого элемента И последующего канала и выходом элемента НЕ и четвертым входом первого элемента И данного канала, второй вход - с первым входом четвертого элемента И последукяцего канала.

| РЕЗЕРВИРОВАННОЕ УСТРОЙСТВОE:?^'iJV. -, | 0 |

|

SU314206A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 426532, кл | |||

| G 0 F 11/00, 1975. | |||

Авторы

Даты

1985-06-07—Публикация

1983-04-08—Подача