Изобретение относится к импульсной технике и может найти применение в сверхскоростных вычислительных устройствах.

Построение компьютеров нового поколения с производительностью более 200 млн. операций в секунду и других средств гигабитовой техники возможно на новой элементной базе. Современные интегральные микросхемы (ИМС) на кремниевой эмиттерно-связанной логике (ЭСЛ) и ее модификациях могут быть усовершенствованы в части повышения быстродействия, однако не на столько, чтобы служить основой перспективных вычислительных устройств.

Известные логические элементы (ЛЭ) И-ИЛИ-НЕ, выполненные на кремниевой ЭСЛ, имеют среднее время задержки сигнала τзс≈ 0,5-1,0 нс при потребляемой мощности Ро ≈ 10 мВт и дальнейшее улучшение этих показателей связано с ухудшением помехоустойчивости за счет снижения величины логического перепада.

Значительно большее быстродействие ( τзс≅ 0,1 нс) при меньших энергетических затратах (Ро ≅ 7 мВт) достигается в арсенидогаллиевых ЛЭ И-ИЛИ-НЕ типа логический буферизированный каскад (ЛБК) с двухзатворным полевым транзистором или ЛБК на основе двух последовательно включенных транзисторов.

Однако в первом арсенидогаллиевом аналоге неудовлетворительна развязка между двумя затворами, а во втором аналоге снижена помехоустойчивость из-за различия логических уровней срабатывания по входам И (затвором двух, последовательно включенных входных транзисторов).

Из известных ЛЭ типа ЛБК наиболее близким по технической сущности, взятым в качестве прототипа, является вентиль ИЛИ-НЕ, содержащий три переключателя тока, затворы которых образуют входы логического элемента, истоки подключены к общей шине, а стоки объединены и подключены к транзисторному ограничителю тока, истоковый повторитель, который состоит из последовательно соединенных входного транзистора, стоком объединенным со стоком ограничителя тока, подключенным к источнику питания, затвором - к стокам переключателей, двух диодов, генератора тока, подключенного истоком, объединенным с затвором, к источнику питания, а стоком - к выходу.

Прототип обладает высокой развязкой по входам, но не способен выполнять логические функции в универсальном базисе И-ИЛИ-НЕ.

Целью изобретения является расширение функциональных возможностей за счет реализации дополнительной операции И-НЕ.

Поставленная цель достигается тем, что в логический элемент на полевых транзисторах, содержащий три транзисторных переключателя тока, затворы которых образуют входы элемента, истоки подключены к общей шине, стоки объединены, транзисторный ограничитель тока, подключенный истоком и затвором к стокам транзисторов переключателей, истоковый повторитель, который содержит входной транзистор, подключенный стоком к стоку ограничителя и источнику питания, затвором - к стокам переключателей, истоком через диод - к выходу элемента и стоку генератора тока, подключенного истоком и затвором к клемме источника питания, введен четвертый транзисторный переключатель тока, подключенный параллельно имеющимся переключателям, причем суммарная ширина каналов двух транзисторов переключателей, затворы которых образуют входы И, равна ширине канала любого из оставшихся транзисторов, затворы которых образуют входы ИЛИ.

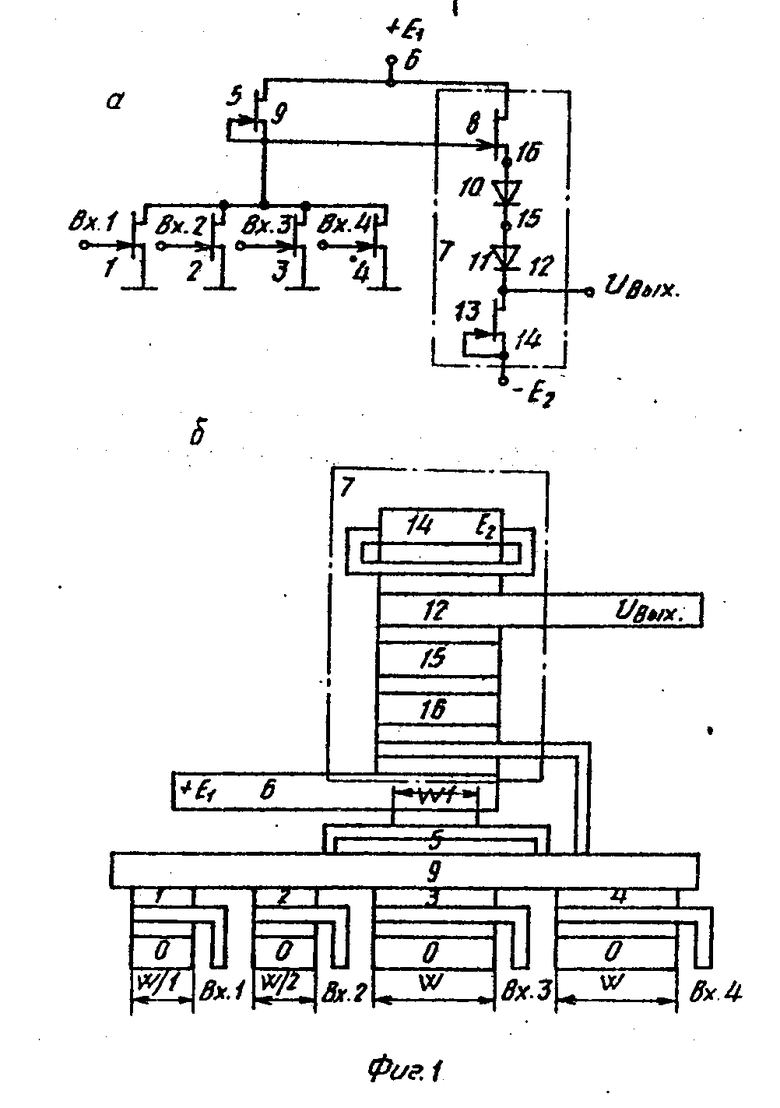

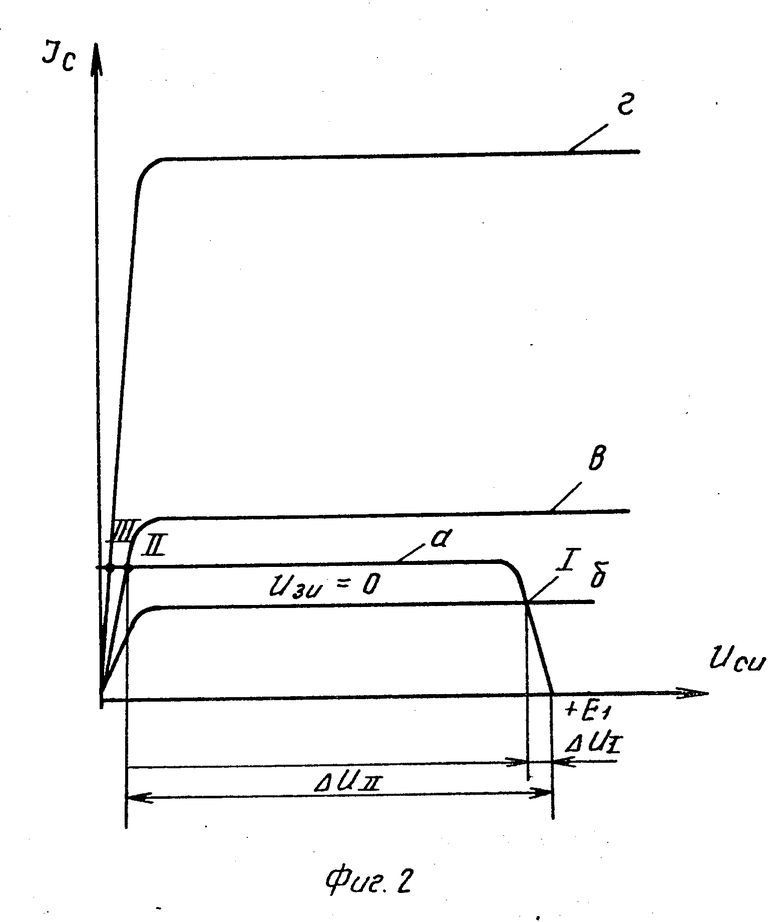

На фиг. 1а представлена принципиальная схема логического элемента; на фиг. 1б - внешний вид топологии логического элемента; на фиг. 2 - условно выходные вольтамперные характеристики ограничителя тока (кривая а) и переключателей тока (кривые б, в, г).

Логический элемент, представленный на фиг. 1а, содержит четыре транзисторных переключателя тока 1-4, выполненных на нормально открытых полевых транзисторах, затворы которых образуют входы элемента, причем Вх1 и Вх2 - входы схемы И, а Вх3 и Вх4 - входы схемы "ИЛИ" истоки подключены к общей шине "0", а стоки - к истоку транзисторного ограничителя тока 5, у которого исток объединен с затвором, а сток подключен к клемме 6 положительного источника питания +Е1 и к истоковому повторителю 7, который содержит входной транзистор 8, затвором подключенный к точке 9, образованной стоками переключателей тока 1-4, стоком - к клемме 6, истоком через диоды 10, 11 - к выходу 12 элемента и к стоку генератора тока 13, подключенного истоком и затвором к клемме 14 отрицательного источника питания -Е2.

Логический элемент, вариант внешнего вида топологии которого представлен на фиг. 1б, выполнен на полевых транзисторах с затвором Шоттки с каналом n-типа и диодах Шоттки. Обозначения, используемые на фиг. 1б, соответствуют обозначениям на фиг. 1а. При этом элементы 15, 16 соответствуют точкам 15, 16 на фиг. 1а. Транзисторы 3,4 выполнены с шириной канала W, транзисторы 1, 2 с шириной канала W/2, транзистор 5 с шириной канала W1, которая выбирается из интервала, задаваемого неравенством

W > W1 > W/2.

В общем случае, когда

Wmin + Wmax = W, где Wmin, Wmax - минимальная и максимальная ширина каналов транзисторов переключателей тока 1, 2, реализующих операцию И, то

W > W1 > Wmin.

Устройство работает следующим образом. В исходном состоянии когда на клемму 6 воздействует источник напряжения +E1, на клемму 14 воздействует источник напряжений -E2, а на входы транзисторов 1-4 воздействуют одинаковые сигналы с напряжением, равным или более отрицательным, чем напряжение отсечки тока стока транзисторов, то транзисторы 1-4 переключателей тока окажутся закрытыми. Вследствие чего потенциал в точке 9 приблизится к потенциалу точки 6. Напряжение в точке 16 будет максимальным и положительным.

Такая ситуация обуславливает высокий логический уровень выходного напряжения в точке 12, то есть Uвых = U12 = U1л. Если на вход транзистора 1 (или 2) воздействует высокий потенциал (равный приблизительно потенциалу общей шины) Uo ≈ 0, транзистор 1 откроется (см. фиг. 2, б), рабочая точка займет положение 1 (см. фиг. 2). Падение напряжения на транзисторе 5 ограничителя тока будет соответствовать Δ U1, (то есть Uз ≈ U6) транзистор 5 закрыт. Напряжение в точке 9 будет высоким и положительным, что соответствует высокому напряжению в точках 16 и 12, то есть на выходе Uвых = Uл1.

Если одновременно на входы транзисторов 1, 2 (или на вход одного из транзисторов 3,4) воздействует высокий потенциал (равный приблизительно потенциалу общей шины), транзисторы откроются (см. фиг. 2, в), рабочая точка займет положение 11 (см. фиг. 2) и падение напряжения на транзисторе 5 будет Δ UII.

Ток источника напряжений +Е1, ограниченный ограничителем тока 5, разветвляясь через открытые транзисторы переключателей тока, достигнет общей шины "0", причем разветвление тока будет пропорциональным ширине канала каждого открытого транзистора переключателей тока.

Эта ситуация обеспечивает пониженное напряжение в точках 9, 16, а в точке 12 произойдет увеличение отрицательного напряжения, соответствующего нижнему логическому уровню напряжения, то есть

Uвых = U12 = Uл0.

Если на входы транзисторов 1-4 воздействует высокий потенциал (равный приблизительно потенциалу общей шины), все транзисторы переключателей тока 1-4 будут открыты. Рабочая точка займет положение III (см. фиг. 2). Суммарный ток, представленный кривой "Г" на фиг. 2, источника напряжения +Е1, ограниченный транзисторным ограничителем тока 5, разветвляясь через транзисторы переключателей тока 1-4, достигнет общей шины. Причем разветвление тока будет пропорциональным ширине канала каждого транзистора переключателя тока. Эта ситуация обеспечивает пониженное напряжение в точках 9, 16, а в точке 12 произойдет увеличение отрицательного напряжения, соответствующего нижнему логическому уровню напряжения, то есть

Uвых = U12 = Uл0 Рассмотренные режимы работы свидетельствуют о том, что логический элемент реализует функцию И/ИЛИ-НЕ. Если объединить входы транзисторов 1-2, то есть образовать единый транзистор с шириной канала W = = W/2 + W/2, равного ширине канала любого из транзисторов 3,4, то устройство будет выполнять логическую функцию 3 ИЛИ-НЕ, так как ток ограничителя тока 5 на транзисторе с шириной канала W1 будет всегда меньше любого из транзисторов 3, 4 и объединенных транзисторов 1,2.

Если на входах транзисторов 3, 4 подать сигналы, соответствующие логическому уровню "0", тем самым закрыть эти транзисторы, то устройство будет реализовать логическую функцию И-НЕ, потому что закрытые транзисторы 1, 2, имеющие малую ширину канала, не способны порознь обеспечить прохождение тока ограничителя 5.

Таким образом, логический элемент при воздействиях логических уровней на входы Вх1, Вх2, Вх3, Вх4 транзисторов переключателей тока 1-4 способен реализовать на выходе "U вых" логическую функцию И/ИЛИ-НЕ (Y = X1. x2 + x3 + x4) и содержит наименьшее число схемных элементов по сравнению со схемами, выполненные на элементах в элементарных базисах И, ИЛИ, НЕ, а также в более сложных базисах И-НЕ, ИЛИ-НЕ.

В отличие от прототипа, прелагаемый логический элемент обладает более широкими функциональными возможностями. А именно: он способен реализовать функцию И/ИЛИ-НЕ, тогда как прототип только ИЛИ-НЕ.

Базис И/ИЛИ-НЕ универсален, так как может быть использован в менее сложных базисах И-НЕ, ИЛИ-НЕ, НЕ, и гибок при синтезе более сложных устройств, так функция "Исключающее ИЛИ" может быть реализована на основе двух элементов.

Устройство, представляя собой функционально полную систему, обладает большим быстродействием. При выполнении логического элемента в виде интегральной схемы на арсениде галлия, он обладает временем задержки 50-200 пс.

Логический элемент технологичен в изготовлении за счет регулярности структуры. (56) Арсенид галлия в микроэлектронике: Под ред. Мордковича. - М. , Мир, 1988, с. 283, рис. 6.7.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 1991 |

|

RU2060578C1 |

| ПРЕОБРАЗОВАТЕЛЬ ЛОГИЧЕСКИХ УРОВНЕЙ | 1988 |

|

SU1593538A1 |

| ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1990 |

|

RU2089943C1 |

| Устройство выборки и хранения | 1980 |

|

SU921087A1 |

| Устройство реверсирования тока | 1985 |

|

SU1246359A1 |

| Устройство для последовательного включения источников питания в МДП интегральных схемах | 1986 |

|

SU1406771A1 |

| ИСТОЧНИК ПИТАНИЯ НЕЛИНЕЙНОЙ ИЛИ ЛИНЕЙНОЙ НАГРУЗКИ | 2021 |

|

RU2768272C1 |

| Способ формирования амплитудно-частотной характеристики усилителя для воспроизведения сигнала, записанного на грампластинку (RIAA корректор) | 2021 |

|

RU2783838C1 |

| СХЕМА СЧИТЫВАНИЯ СИГНАЛОВ ИЗ ЯЧЕЕК МАТРИЦЫ ФОТОДЕТЕКТОРОВ | 2007 |

|

RU2343588C1 |

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

Изобретение относится к импульсной технике и может найти применение в сверхскоростных вычислительных устройствах. Устройство содержит четыре транзисторных переключателя тока, транзисторный ограничитель тока, истоковый повторитель, клемму положительного источника питания, клемму отрицательного источника питания. 2 ил.

ЛОГИЧЕСКИЙ ЭЛЕМЕНТ на полевых транзисторах, содержащий не менее двух транзисторных переключателей тока, затворы которых образуют входы элемента, истоки подключены к общей шине, а стоки объединены, транзисторный ограничитель тока, подключенный истоком и затвором к стокам транзисторов переключателей, а также истоковый повторитель, который содержит входной транзистор, подключенный стоком к стоку ограничителя и к клемме источника питания, затвором - к стокам переключателей, истоком через диод - к выходу элемента и стоку генератора тока, подключенного истоком и затвором к клемме дополнительного источника питания, отличающийся тем, что, с целью расширения функциональных возможностей за счет реализации дополнительной операции И - НЕ, в него введен дополнительный транзисторный переключатель тока, подключенный параллельно имеющимся переключателям, при этом суммарная ширина каналов двух транзисторов переключателей тока, затворы которых образуют входы И, больше ширины канала транзистора ограничителя тока, а ширина канала каждого из двух транзисторов переключателей тока меньше ширины канала транзистора ограничителя тока.

Авторы

Даты

1994-04-15—Публикация

1990-08-14—Подача