Фис. /

Изобретение относится к импульсной и вычислительной технике и может быть использовано в составе МДП интегральных схем с несколькими источниками питания, в частности в электрически стираемых ППЗУ в качестве переключающего устройства, обеспечивающего заданную последовательность подключения источников к внутренним узлам схемы.

Целью изобретения является стабилизация заданного порога включения при увеличении уровня коммутируемого напряжения за счет увеличения диапазона рабочих напряжений, повышения чувствительности порога переключения и устранения влияния разброса конструктивных и технологических факторов элементов интегральной схемы устройства.

Цель достигается путем введения делителя напряжения, нагрузочного элемента и двух инверторов, которые совместно с пороговым элементом формируют управляющие сигналы с высокой стабильностью точки срабатывания для переключения введенного дополнительного переключателя высоковольтного источника напряжения, осуществляющего включение по превьшению минимально Допустимого значения напряжения и отключение по понижению ниже минимального допустимого значения.

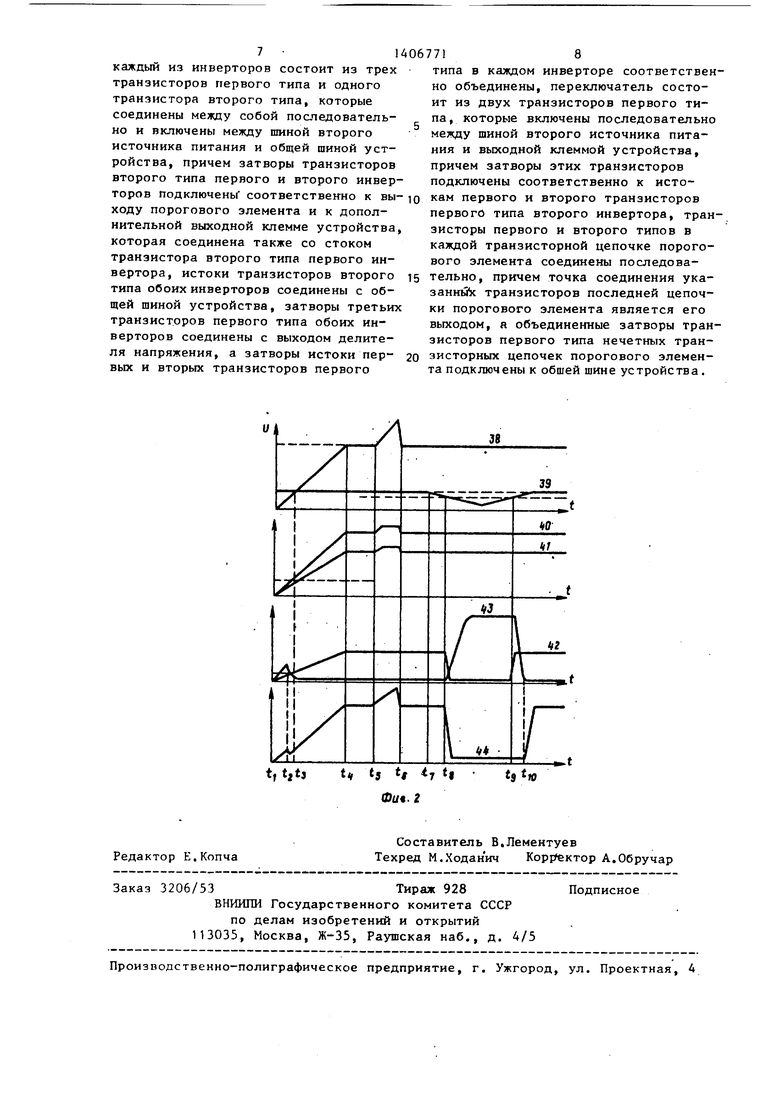

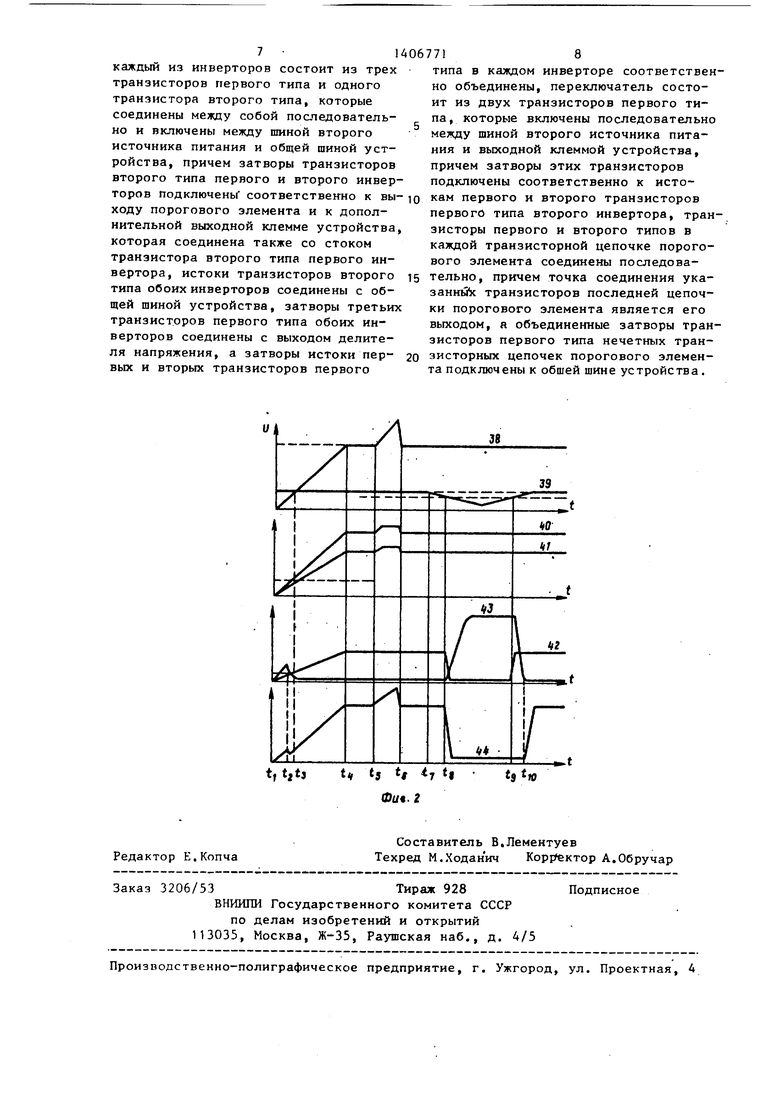

На фиг,1 изображена принципиальная схема устройства; на фиг,2 - временные диаграммы напряжений в основных узлах схемы.

Устройство содержит пороговый эле- ент 1 , делитель 2 напряжения, нагрузочный элемент 3, первый 4 и второй 5 инверторы, переключатель 6. Пороговый эле мент 1 состоит из четного числа транзисторных цепочек 7, каждая из которых содержит последовательно соеднне11ные транзисторы 8 и

9соответственно первого типа - со встроенным каналом и второго типа с индуцированным каналом. Транзисторные цепочки 7 включены между шиной

10питания порогового элемента и общей шиной I1 устройства. Транзисторные цепочки 7 включены по каскадной схеме, причем точка соединения транзисторов последней транзисторной цепочки является выходом 12 порогового элемента 1,

Клемма 13 первого - низковольтного источника напряжения, соединена

0

5

0

5

0

5

0

5

0

5

с затворами транзисторов 8 первого типа четных транзисторных цепочек, а затворы тех же транзисторов нечетных транзисторных цепочек подключены к общей шине 11 устройства.

Делитель 2 напряжения вьтолнен в виде цепочки пяти транзисторов 14 - 18 первого типа, транзистора 19 второго типа и конденсатор 20. Делитель 2 напряжения включен между шиной 21 второго высоковольтного источника питания и общей шиной 11 устройства. Выходом 22 делителя 2 напряжения является точка соединения затвора и источника третьего транзистора 16 цепочки, затвора и стока четвертого транзистора 17 цепочки, стока транзистора 19 второго типа и первой обкладки конденсатора 20, который выполнен в виде МДП транзисторной структуры. Затворы и истоки остальных транзисторов первого типа цепочки объединены.

Нагрузочный элемент 3 состоит из трех транзисторов 23-25 первого типа, включенных последовательно между шиной 21 второго источника питания и шиной 10 питания порогового элемента. Затвор третьего транзистора 25 первого типа соединен с выходом 22 делителя 2 напряжения, а затворы других транзисторов 23 и 24 соединены с истоками.

Первый 4 и второй 5 инверторы состоят из трех транзисторов 26-28 и 29-31 первого типа и одного транзистора 32 и 33 второго типа соответственно. Транзисторы инверторов соединены последовательно и включены между шиной второго источника 21 питания и общей шиной 11 устройства.

Затворы транзисторов 32 и 33 второго типа первого 4 и второго 5 инверторов подключены соответственно к выходу 12 порогового элемента 1 и точке соединения стока транзистора 32 второго типа и истока третьего транзистора 28 первого типа первого инвертора. С этой точкой соединена также дополнительная выходная клемма 34 устройства Блокировка работы. Затворы третьих транзисторов 28 и 31 первого типа обоих инверторов соединены с выходом 22 делителя 2 напряжения, а затворы первых 26 и 29 и вторых 27 и 30 транзисторов первого типа инвер7б)ров 4 и 5 соединены с истоками.

21

Переключатель 6 состоит из двух транзисторов 35 и 36 первого типа, которые включены между собой последовательно между шиной 21 второго источника питания и выходной клеммой 37 устройства. При этом затворы этих транзисторов подключены соответственно к истокам первого 29 и второго ЗгО транзисторов первого типа второго инвертора 5.

На фиг.2 указанные позиции соответствуют напряжениям в следующих узлах схемы устройства: 38 - на гаине 21 второго источника питания, 39 - на клемме 13 первого источника напряжения, 40 - на шине 10 питания порогового элемента I, 41 - на выходе 22 делителя 2 напряжения, 42 - на выходе 12 порогового элемента 1, 43 - на дополнительной выходной клемме 34 устройства, 44 - на выходной клемме 37 устройства.

Устройство работает следующим об- разом.

Когда в исходном состоянии (t, О, фиг.2) первый - низковольтный источник питания, находится во включенном состоянии (на клемме 13 поло- жительное напряжение, например 5 в), а источник высоковольтного напряжения выключен (на шине 21 второго источника питания нулевое напряжение)| напряжение на выходной клемме 37 устройства также отсутствует.

При возрастании потенциала второго высоковольтного источника питания до номинального значения на затворе транзистора 1 9 за счет деления напряже- ния на пяти последовательно включенных транзисторах 14-18 образуется потенциал, близкий к назначению порогового напряжения транзистора второго типа. При этом транзистор 19 находит ся в предгюроговой области, т.е. в проводимости не участвует. Наличие двух транзисторов 14 и 15, ограничУ - вающих ток, протекающий через делитель 2 напряжения, позволяет полу- чить на выходе 22 этого делителя напряжение, близкое к напряжению низковольтного источника питания, а также получить напряжение между электродами каждг,го из транзисторов 14 и 15 близкое к половине общего падения напряжения на этих транзисторах, что является фактором, гарантирующим надежную работу МЛП-транзисторов в

0

5

5

О

0 g п g

5

71

диапазоне напряжения питания высоковольтного источника равного, например ,21В.

При превышении напряжением второ- го - высоковольтного источника питания, значения порогового напряжения МДП-транзисторов во внутренних точках устройства начинает происходить процесс отработки логических уровней и в момент tj устанавливаются уровни потенциалов, обеспечивающие выполнение устройством своих функций. В момент времени t напряжение на высоковольтном источнике питания уже превь Лиает напряжение низковольтного источника питания, и дальнейшее увеличение напряжения на высоковольтном источнике питания - шине 21, приво, дит к увеличению потенциала на выходной клемме 37 устройства, поскольку на выходе 12 порогового элемента 1 потенциал находится на единичном уровне и возрастает, отслеживая возрастание высоковольтного питания.

Рассмотрим работу устройства при выбросах на источнике высоковольтного напряжения. Пусть, начиная с времени t J. , напряжение превышает допустимое значение. Это приводит к пре- вьпцению потенциала затвора транзистора 19 над пороговым напряжением и к стабилизации напряженля на выходе делителя 2 напряжения. Включение затвора транзистора 17 на свой сток приводит к повышению коэффициента стабилизации за счет нелинейной характеристики транзистора 17, более резкому возрастанию проводимости при повыпечии напряжения и, следовательно, к большему падению напряжения на токостабилизируюием транзисторе 18. Включение конденсатора 20 позволяет понизить дифференциальное сопротивление и отфильтровать потенциал на выходе 22 делителя 2 напряжения от всплесков напряжения с крутыми фронтами.

Рассмотрим работу устройства при понижении источника низковольтного напряжения (момент времени t, ). Геометрические размеры транзисторов 8 первого типа порогового элемента выбираются такими, чтобы равенство токов транзисторных цепочек 7 достигалось при равенстве напряжения на низковольтном источнике значению минимально допустимому. Тогда уменьшение напряжения ниже минимально

допустимого на величину чувствительности последовательно включенных цепочек приводит к появлению на выходе 12 порогового элемента уровня О.

Таким образом, при незначительном отклонении источника низковольтного напряжения ниже значения минимально допустимого навеличину 80 - 120 мВ за счет последовательного усиления потенциалов на затворах транзисторов 9 на выходе 12 формируется полньш перепад напряжения, достаточный для срабатывания первого инвертора А.

Второй инвертор 5 обеспечивает формирование управляющих сигналов с необходимыми уровнями, обеспечиваю- Р1ИМИ полное открытие транзисторов 35 и 36 переключателя 6 при наличии напряжения на низковольтном источнике питания, а также отключение нагрузки от высоковольтного источника напряжейия.

Таким образом, предлагаемое устройство производит переключение высоковольтного источника напряжения (включение по превышению напряжения минимально допустимого значения и отключение по понижению ниже минимально допустимого) с высокой стабильностью точки переключения и обладает высокой надежностью к броскам высоковольтного напряжения и большой величиной переключаемого напряжения.

Порог включения можно устанавливать на любую величину путем изменения крутизны транзисторов в транзисторных цепочках 7. Величина зоны срабатывания зависит от общего коэффициента усиления цепочек 7 в зоне срабатывания. Чувствительность устройства, т.е. величина зоны срабатывания, разница между напряжением включения и отключения может быть существенно уменьшена путем увеличения числа каскадно включенных транзисторных цепочек 7.

Формула и зоб,ре тения

Устройство для последовательного включения источников питания в МДП интегральных схемах, содержащее пороговый элемент, состоящий из четного числа транзисторных цепочек, каждая из которых содержит транзистор первого типа со встроенным каналом и транзистор второго типа с индуци067716

рованным каналом, стоки транзисторов первого типа транзисторных цепочек объединены и подключены к шине питания порогового элемента, а истоки транзисторов второго типа подключены к общей шине, затворы транзисторов первого типа нечетных транзисторных цепочек объединены, а затворы тран10 зисторов первого типа четных транзисторных цепочек подключеяы к клемме первого источника питания, затворы транзисторов второго типа всех транзисторных цепочек, за исключением

15 первой, подключены к стоку транзистора второго типа предыдущей транзисторной цепочки, затвор и сток транзистора второго типа первой транзисторной цепочки объединены, сток тран20 зистора второго типа последней транзисторной цепочки является выходом порогового элемента, отличаю- щ е е с я тем, что, с целью стабилизации заданного порога включения при

25 увеличении уровня коммутируемого напряжения, в устройство дополнительно .введен нагрузочный элемент, делитель напряжения, два инвертора и переключатель, причем нагрузочный элемент

30 состоит из трех транзисторов первого типа, которые включены между собой последовательно между шиной второго источника питания и шиной питания порогового элемента, затворы пер2g вого и второго транзисторов первого типа нагрузочного элемента соединены с истоками тех же транзисторов, а затвор третьего, исток которого подключен к шине питания порогового

40 элемента, - с выходом делителя напряжения, которой выполнен в виде цепочки из пяти транзисторов первого типа, соединенных последовательно и включенных между шиной второго источника

45 питания и общей шиной устройства, конденсатора и транзистора второго типа, которые включены параллельно между точкой соединения третьего и четве)того транзисторов цепочки,

50 являющейся выходом делителя напряжения, и общей шиной устройства, причем затвор транзистора второго типа делителя напряжения соединен с об- щей точкой четвертого транзистора

55 цепочки, затвор и сток которого объединены, и пятого транзистора той же цепочки, причем затворы и истоки у первого, второго, третьего и пятого транзисторов цепочки объединены, а

каждый из инверторов состоит из трех транзисторов первого типа и одного транзистора второго типа, которые соединены между собой последовательно и включены между шиной второго источника питания и общей шиной устройства, причем затворы транзисторов второго типа первого и второго инвертипа в каждом инверторе соответствен но объединены, переключатель состоит из двух транзисторов первого типа, которые включены последовательно

между шиной второго источника питания и выходной клеммой устройства, причем затворы этих транзисторов подключены соответственно к исто- торов Подключены соответственно к вы- ю кам первого и второго транзисторов ходу порогового элемента и к допол- первого типа второго инвертора, тран нительной выходной клемме устройства, зисторы первого и второго типов в которая соединена также со стоком каждой транзисторной цепочке порого- транзистора второго типа первого ин- вого элемента соединены последова- вертора, истоки транзисторов второго 15 тельно, причем точка соединения ука- типа обоих инверторов соединены с об- занньЬс транзисторов последней цепоч- щей шиной устройства, затворы третьих транзисторов первого типа обоих инверторов соединены с выходом делителя напряжения, а затворы истоки пер- 20 зисторных цепочек порогового элемен- вых и вторых транзисторов первого та подключены к обшей шине устройства .

ки порогового элемента является его выходом, а объединенные затворы транзисторов первого типа нечетных трантипа в каждом инверторе соответственно объединены, переключатель состоит из двух транзисторов первого типа, которые включены последовательно

между шиной второго источника питания и выходной клеммой устройства, причем затворы этих транзисторов подключены соответственно к исто- кам первого и второго транзисторов первого типа второго инвертора, тран зисторы первого и второго типов в каждой транзисторной цепочке порого- вого элемента соединены последова- тельно, причем точка соединения ука- занньЬс транзисторов последней цепоч- зисторных цепочек порогового элемен- та подключены к обшей шине устройства .

ки порогового элемента является его выходом, а объединенные затворы транзисторов первого типа нечетных тран

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство формирования импульсов на МДП-транзисторах | 1986 |

|

SU1345339A1 |

| Устройство обнаружения смены адресного сигнала в интегральном исполнении на МОП-транзисторах | 1984 |

|

SU1249695A1 |

| Формирователь напряжения записи для запоминающего устройства | 1988 |

|

SU1550580A1 |

| Импульсный генератор (его варианты) | 1980 |

|

SU911693A1 |

| Формирователь импульсного сигнала по переднему и заднему фронтам адресных сигналов на МОП -транзисторах | 1985 |

|

SU1381694A1 |

| Переключающее устройство с переменной структурой | 1985 |

|

SU1287278A1 |

| ИСТОЧНИК ПИТАНИЯ НЕЛИНЕЙНОЙ ИЛИ ЛИНЕЙНОЙ НАГРУЗКИ | 2021 |

|

RU2768272C1 |

| ПОЛУПРОВОДНИКОВОЕ УСТРОЙСТВО НЕРАЗРУШАЕМОЙ ПАМЯТИ | 1992 |

|

RU2097842C1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Формирователь импульсов регенерации для запоминающих устройств на мдп-транзисторах | 1974 |

|

SU500581A1 |

Изобретение относится к импульсной и вычислительной технике. Цель изобретения - стабилизация заданного порога включения при увеличении урорня коммутируемого напряжения. Устройство содержит пороговый элемент I, состоящий из четного числа транзисторных цепочек 7. Введение делителя 2 напряжения, нагрузочного элемента 3, инверторов Д и 5 и образование новых функциональных связей увеличивает диапазон рабочих напряжений, повышает чувствительность порога переключения и устраняет влияние разброса конструктивных и технологических факторов элементов интегральной схемы устройства. 2 ил. с

| Патент QUA № 3602738, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ холодной проковки точечных сварных соединений | 1949 |

|

SU85727A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-06-30—Публикация

1986-12-16—Подача