Изобретение относится к интегральной микроэлектронике и может быть использовано в производстве схем оперативных запоминающих устройств и логических элементов.

Целью изобретения является расширение области применения за счет стабилизации выходного напряжения низкого логического уровня.

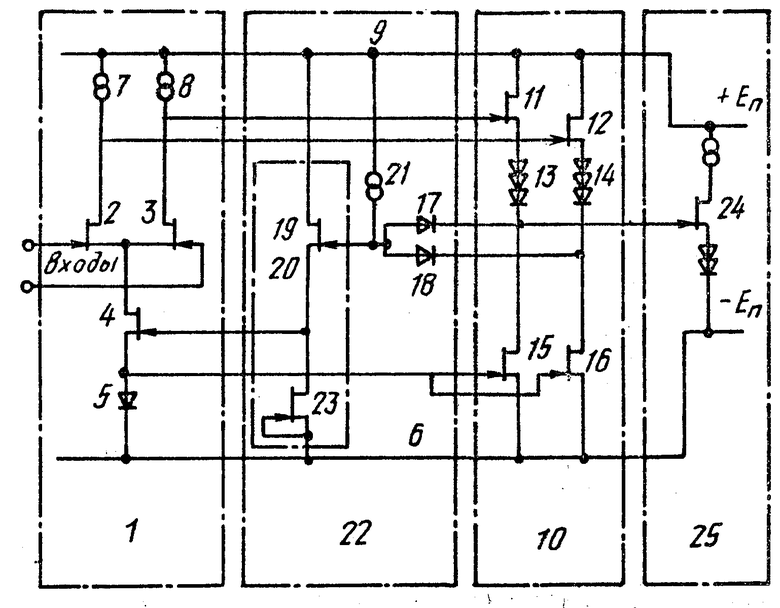

На чертеже представлена электрическая принципиальная схема преобразователя логических уровней со стабилизацией напряжения низкого логического уровня, содержащего входной дифференциальный каскад 1, который состоит из переключательных транзисторов 2, 3, истоки которых соединены со стоком транзистора 4, выполняющего функцию генератора тока, исток которого соединен с анодом диода 5, катод которого подключен к отрицательной шине питания 6. Затворы транзисторов входного дифференциального каскада 1 являются входами преобразователя, а стоки через генераторы тока 7, 8 подключены к положительной шине питания, а также в выходные истоковые повторители 10. Истоковые повторители 10 состоят из транзисторов 11, 12, затворы которых подключены к стокам транзисторов 2, 3, стоки подключены к положительной шине питания 9, а истоки подключены к анодам диодных сборок сдвига уровня 13, 14, состоящих из последовательно включенных диодов, катоды которых подключены к стокам транзисторов 16, 15, выполняющих функцию управляемых генераторов тока, истоки которых подключены к отрицательной шине питания 6, а затворы соединены с истоком транзистора 4. В стоки генераторов тока 15, 16 катодами подключены диоды 17, 18, которые соединены с затвором транзистора 19 дополнительного истокового повторителя 20 и первым выводом генератора тока 21, второй вывод которого подключен к положительной шине питания 9. Дополнительный истоковый повторитель 20 входит в состав цепи нелинейной отрицательной обратной связи по напряжению 22 и содержит транзистор 19, сток которого подключен к положительной шине питания 90 а источник подключен к затвору транзистора 4, а также к стоку транзистора 23, выполняющего функцию генератора тока дополнительного истокового повторителя. Затвор и исток транзистора 23 подключены к отрицательной шине питания 6.

Преобразователь логических уровней работает следующим образом.

Пусть в начальный момент времени на затворе транзистора 2 действует напряжение высокого логического уровня, а на затворе транзистора 3 действует напряжение низкого логического уровня. Данные воздействия приводят к тому, что на стоке транзистора 2 устанавливается напряжение низкого логического уровня, а на стоке транзистора 3 напряжение высокого логического уровня. Сформированные логические уровни через истоковые повторители 11, 12 и диоды сдвига уровня сигнала 13, 14 передаются на выход преобразователя. На выходе устанавливается напряжение равное U0-En, при этом транзистор 24 логического элемента 25 надежно заперт вследствие того, что на его истоке действует опорный потенциал равный 2U0-En. Опорный потенциал истока транзистора 24 в разных схемах может быть разным. В зависимости от этого может изменяться количество диодов в истоковой цепи дополнительного истокового повторителя. Напряжение низкого логического уровня в схеме преобразователя вычисляется по формуле

Uвых U05 + U3u4 + U3u19 Uoooc

U3u4 + U3u19, где U05 напряжение пятки диода 5;

U3u4 напряжение затвор-исток транзистора 4, равно 0 В;

U3u119 напряжение затвор-исток транзистора 19;

U00oc напряжение пятки диода, подключенного катодом к выходу. Разность потенциалов затвор-исток транзистора 19 стабилизирована генератором тока 23 и равна U0, тогда как напряжение затвор-исток транзистора 4 может изменяться вследствие эффектов паразитного управления, что приводит к изменению напряжений выходных логических уровней и, как следствие, ненадежной работы логического элемента, который нагружается на выход преобразователя. Пусть в последующий момент времени изменилась разность потенциалов затвор-исток транзистора 4, это влечет изменение потенциалов на стоках транзисторов 2, 3, что через истоковые повторители 11, 12 и диоды сдвига уровня 13, 14 передается на выход. Но цепь нелинейной отрицательной обратной связи отрабатывает отклонение потенциала затвор-исток транзистора 4, благодаря чему система удерживается в стабильном состоянии. Причем вследствие того, что в отрицательную обратную связь введены диоды, стало возможным жестко застабилизировать напряжение низкого логического уровня, а значит обеспечить надежное запирание логического элемента 25.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство выборки и хранения | 1979 |

|

SU826564A1 |

| Устройство выборки и хранения | 1980 |

|

SU921087A1 |

| Логический элемент на полевых транзисторах с затвором Шотки ИСПЛ-типа | 1989 |

|

SU1742993A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1990 |

|

SU1769682A1 |

| ИСТОЧНИК ПИТАНИЯ НЕЛИНЕЙНОЙ ИЛИ ЛИНЕЙНОЙ НАГРУЗКИ | 2021 |

|

RU2768272C1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1994 |

|

RU2114500C1 |

| Устройство выборки и хранения | 1980 |

|

SU963131A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА НОРМАЛЬНО ОТКРЫТЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 1987 |

|

SU1530059A1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ ЭСЛ-КМОП | 1994 |

|

RU2097914C1 |

| Операционный усилитель | 1990 |

|

SU1753583A1 |

Изобретение относится к интегральной микроэлектронике и может быть использовано при производстве схем оперативных запоминающих устройств и логических элементов. Цель изобретения - расширение области применения за счет стабилизации напряжения низкого логического уровня. Преобразователь содержит входной дифференциальный каскад 1, выходные истоковые повторители 10, дополнительный истоковый повторитель 20. Для достижения поставленной цели в устройство дополнительно введены генератор тока 21 и диоды 17, 18, а также новые связи. 1 ил.

ПРЕОБРАЗОВАТЕЛЬ ЛОГИЧЕСКИХ УРОВНЕЙ на полевых транзисторах с барьером Шотки, содержащий входной дифференциальный каскад, который состоит из первого и второго переключательных транзисторов, истоки которых подключены к стоку транзистора управляемого генератора тока, исток которого соединен с анодом диода, катод которого подключен к отрицательной шине питания, затворы переключательных транзисторов входного дифференциального каскада соединены с входами устройства, стоки подключены через соответствующие генераторы тока к положительной шине питания, а также к затворам транзисторов первого и второго выходных истоковых повторителей соответственно, стоки которых подключены к положительной шине питания, а истоки подключены к анодам соответствующих диодных сборок, катоды которых подключены к стокам соответствующих транзисторов управляемых генераторов тока, дополнительный истоковый повторитель, состоящий из транзистора, сток которого подключен к положительной шине питания, и транзистора неуправляемого генератора тока, затвор и исток которого подключены к отрицательной шине питания, а его сток соединен с затвором транзистора управляемого генератора тока входного дифференциального каскада, отличающийся тем, что, с целью расширения области применения за счет стабилизации напряжения низкого логического уровня, в него дополнительно введены генератор тока и первый и второй диоды, катоды которых подключены к стокам соответствующих транзисторов управляемых генераторов тока выходных истоковых повторителей, а аноды подключены к затвору транзистора дополнительного истокового повторителя и к первому выводу дополнительного генератора тока, второй вывод которого подключен к положительной шине питания, истоки транзисторов управляемых генераторов тока выходных истоковых повторителей подключены к отрицательной шине питания, а затраты соединены с истоком транзистора управляемого генератора тока входного дифференциального каскада, затвор которого подключен к истоку транзистора дополнительного истокового повторителя.

| Патент США N 4616189, кл | |||

| Катодная трубка Брауна | 1922 |

|

SU330A1 |

Авторы

Даты

1996-04-20—Публикация

1988-10-06—Подача