Изобретение относится к области электротехники и может быть использовано для регулирования скорости вращения асинхронных электродвигателей в различных отраслях промышленности.

Известен частотно-фазовый детектор, содержащий дифференциальный усилитель, выход которого является выходом устройства, два D-триггера, элемент И-НЕ, входы которого соединены с прямыми выходами D-триггеров, а выход - с R-входами D-триггеров, 0-входы D-триггеров соединены с источником логической 1, а входы синхронизации D-триггеров являются входами частотно-фазового детектора, два элемента И, два блока задержки, причем прямые выходы каждого D-триггера через соответствующий элемент И соединены с входами дифференциального усилителя, а второй вход каждого элемента И через соответствующий блок задержки соединен с ин- версным выходом соответствующего D-триггера,

Недостатком указанного частотно-фазового детектора является низкая точность.

Известен также частотно-фазовый детектор, содержащий первый и второй D- триггеры, входы синхронизации которых являются входами частотно-фазового детектора, а информационные D-входы D-триггеров являются входами логической единицы частотно-фазового детектора, элемент И- НЕ, входы которого соединены с прямыми выходами первого и второго D-триггеров, а выход - с входами сброса D-триггеров, четыре резистора, два конденсатора и операционный усилитель, выход которого является выходом частотно-фазового детектора, причем инверсный выход первого D- триггера соединен через последовательно подключенные первый и второй резисторы с прямым выходом второго D-триггера, а точка соединения первого и второго резисторов подключена к инвертирующему входу операционного усилителя и первому выводу первого конденсатора, другой вывод которого соединен с выходом операционного усилителя, прямой выход первого D-триггера соединен через последовательно подключенные третий и четвертый резисторы с инверсным выходом второго D-триггера, а точка соединения третьего и четвертого резисторов подключена к неинвертирующему входу операционного усили- теля и первому выводу второго конденсатора, другой вывод которого подключен к общей шине. /

Недостатком известного частотно-фазового детектора является наличие нелинейных искажений.

Целью изобретения является уменьшение нелинейных искажений.

Поставленная цель достигается тем, что в частотно-фазовом детекторе, содержащем

5 первый и второй D-триггеры, входы синхронизации которых являются входами частотно-фазового детектора, а информационные D-входы D-триггеров являются входами логической единицы частотно-фазового детек0 тора, операционный усилитель, выход которого является выходом частотно-фазового детектора, при этом инверсный выход первого D-триггера подключен к прямому выходу, второго D-триггера через последо5 вательно соединенные первый и второй резисторы, точка соединения которых подключена к инвертирующему входу операционного усилителя, к которому через первый конденсатор подключен выход опе0 рационного усилителя, прямой выход первого D-триггера подключен к инверсному выходу второго D-триггера через последовательно соединенные третий и четвертый резисторы, точка соединения которых под- {

5 ключена к неинвертируемому входу опера--- ционного усилителя, который соединен с общей шиной через второй конденсатор, согласно изобретению, вход синхронизации первого D-триггера подключен к входу сбро0 са второго D-триггера через введенный первый одновибратор, вход синхронизации второго D-триггера подключен к входу сброса первого D-триггерз через введенный второй одновибратор.

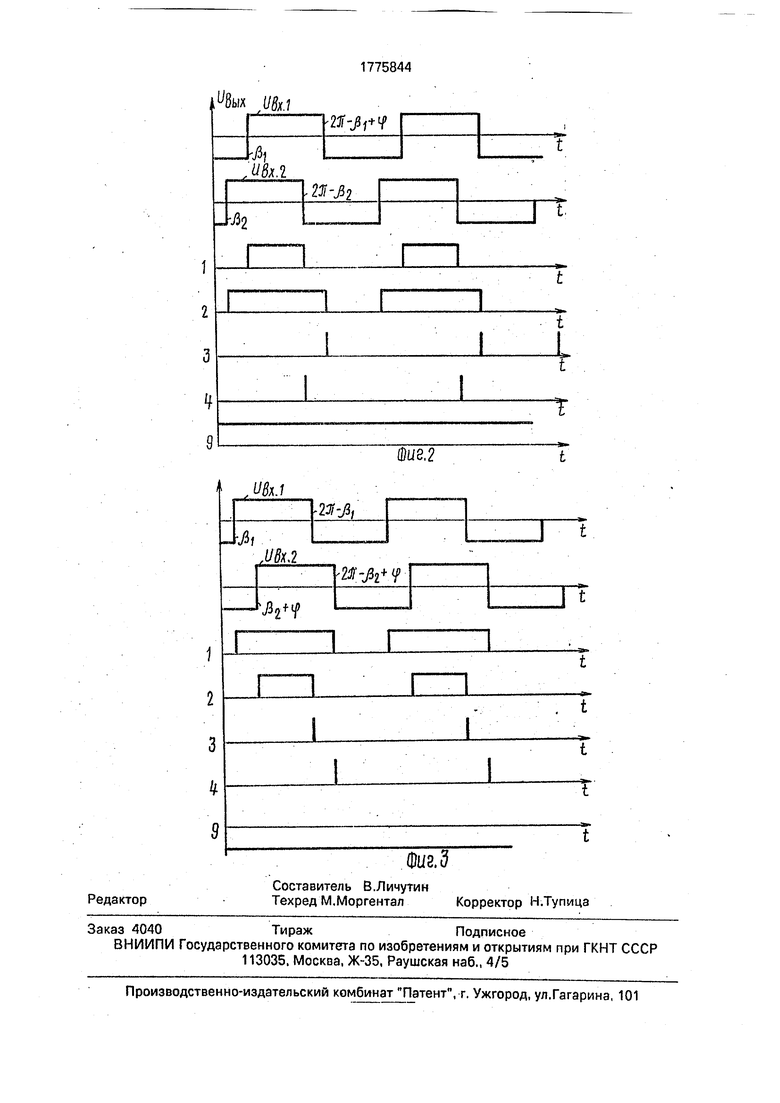

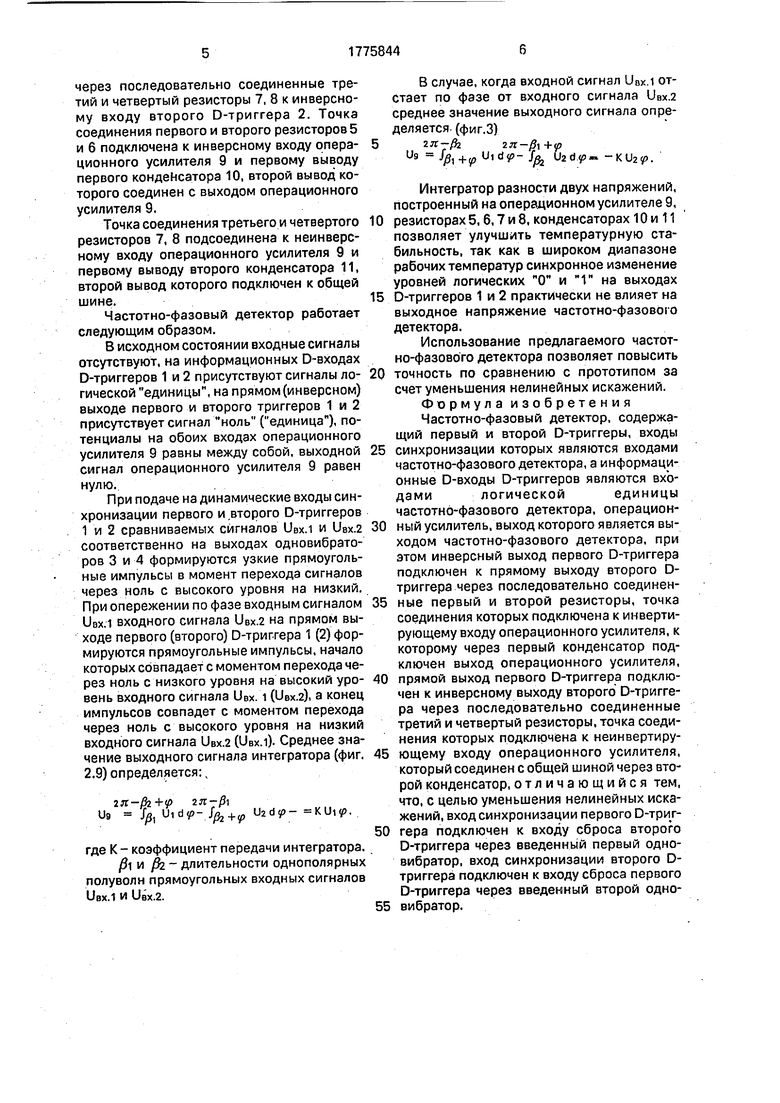

5 На фиг. 1 приведена структурная электрическая схема частотно-фазового детектора; на фиг. 2 и 3 - временные диаграммы работы его.

Частотно-фазовый детектор содержит

0 первый и второй D-триггеры 1 и 2, первый и второй одновибраторы 3 и 4, первый, второй, третий и четвертый резисторы 5, 6, 7 и 8, операционный усилитель 9, первый и второй конденсаторы 10 и 11.

5 Информационные D-входы первого и вто- / рого D-триггеров 1 и 2 являются входами логической единицы частотно-фазового детектора. Входы синхронизации первого и второго D- триггеров 1 и 2 являются первым и вторым

0 входами частотно-фазового детектора и соединены соответственно с входами первого и второго одновибраторов 3 и 4. Входы сброса первого и второго D-триггеров 1 и 2 подключены соответственно к выходам вто5 рого 4 и первого 3 одновибраторов. Инверсный выход первого D-триггера 1 через последовательно соединенные первый и второй резисторы 5 и 6 подключены к прямому выходу второго D-триггера 2, Прямой

выход первого D-триггера 1 подсоединен

через последовательно соединенные третий и четвертый резисторы 7, 8 к инверсному входу второго D-триггера 2. Точка соединения первого и второго резисторов 5 и 6 подключена к инверсному входу операционного усилителя 9 и первому выводу первого конденсатора 10, второй вывод которого соединен с выходом операционного усилителя 9.

Точка соединения третьего и четвертого резисторов 7, 8 подсоединена к неинверсному входу операционного усилителя 9 и первому выводу второго конденсатора 11, второй вывод которого подключен к общей шине.

Частотно-фазовый детектор работает следующим образом.

В исходном состоянии входные сигналы отсутствуют, на информационных D-входах D-триггеров 1 и 2 присутствуют сигналы логической единицы, на прямом (инверсном) выходе первого и второго триггеров 1 и 2 присутствует сигнал ноль (единица), потенциалы на обоих входах операционного усилителя 9 равны между собой, выходной сигнал операционного усилителя 9 равен нулю.

При подаче на динамические входы синхронизации первого и второго D-триггеров 1 и 2 сравниваемых сигналов UBX.I и Uex.2 соответственно на выходах одновибрато- ров 3 и 4 формируются узкие прямоугольные импульсы в момент перехода сигналов через ноль с высокого уровня на низкий. При опережении по фазе входным сигналом UBX.I входного сигнала UBx.2 на прямом выходе первого (второго) D-триггера 1 (2) формируются прямоугольные импульсы, начало которых совпадает с моментом перехода через ноль с низкого уровня на высокий уровень входного сигнала UBx. 1 (Uex.2), а конец импульсов совпадет с моментом перехода через ноль с высокого уровня на низкий входного сигнала Uex.2 (UBX.I). Среднее значение выходного сигнала интегратора (фиг. 2.9) определяется: k

2n-( гл-fr Ue Sfr Uidp- Sfc+p KUip.

где К - коэффициент передачи интегратора.

fi и fk - длительности однополярных

полуволн прямоугольных входных сигналов

Uax.1 И Uex.2.

В случае, когда входной сигнал UBX 1 отстает по фазе от входного сигнала Uex.2 среднее значение выходного сигнала определяется (фиг.З) гп-рг2Я-51+Р

Us J/3, +(o Uid«o- /д, U2dp--KU2.

Интегратор разности двух напряжений, построенный на операционном усилителе 9,

резисторах 5,6,7 и 8, конденсаторах 10 и 11 позволяет улучшить температурную стабильность, так как в широком диапазоне рабочих температур синхронное изменение уровней логических О и 1 на выходах

D-триггеров 1 и 2 практически не влияет на выходное напряжение частотно-фазовою детектора.

Использование предлагаемого частотно-фазового детектора позволяет повысить

точность по сравнению с прототипом за счет уменьшения нелинейных искажений. Формула изобретения Частотно-фазовый детектор, содержащий первый и второй D-триггеры, входы

синхронизации которых являются входами частотно-фазового детектора, а информационные D-входы D-триггеров являются входамилогическойединицычастотно-фазового детектора, операционный усилитель, выход которого является выходом частотно-фазового детектора, при этом инверсный выход первого D-триггера подключен к прямому выходу второго D- триггера через последовательно соединенные первый и второй резисторы, точка соединения которых подключена к инвертирующему входу операционного усилителя, к которому через первый конденсатор подключен выход операционного усилителя,

прямой выход первого D-триггера подключен к инверсному выходу второго D-триггера через последовательно соединенные третий и четвертый резисторы, точка соединения которых подключена к неинвертирующему входу операционного усилителя, который соединен с общей шиной через второй конденсатор,отличающийся тем, что, с целью уменьшения нелинейных искажений, вход синхронизации первого D-триггера подключен к входу сброса второго D-триггера через введенный первый одно- вибратор, вход синхронизации второго D- триггера подключен к входу сброса первого D-триггера через введенный второй одновибратор.

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный частотно-фазовый детектор | 1989 |

|

SU1702539A1 |

| Частотно-фазовый детектор | 1986 |

|

SU1406717A1 |

| ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 2006 |

|

RU2300170C1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Устройство для передачи и приема двух сигналов по одному проводу | 1989 |

|

SU1741281A1 |

| Устройство для синхронизации цифровой магнитной записи | 1989 |

|

SU1691888A1 |

| Цифровой измеритель перемещений | 1987 |

|

SU1620947A1 |

| Интегрирующий аналого-цифровой преобразователь | 1987 |

|

SU1628204A1 |

| Устройство для контроля электромагнита | 1986 |

|

SU1348776A1 |

| Устройство для определения абсолютного значения | 1983 |

|

SU1137484A1 |

Изобретение относится к электротехнике и может использоваться для регулирования скорости вращения асинхронных электродвигателей в различных отраслях промышленности. Цель - уменьшение нелинейных искажений. Частотно-фазовый детектор содержит первый и второй D-тригге- ры (Т) 1 и 2, первый, второй одновибраторы

| Авторское свидетельство СССР №111406717, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-11-15—Публикация

1990-02-26—Подача