.

8

S

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 2006 |

|

RU2300170C1 |

| Частотно-фазовый детектор | 1990 |

|

SU1775844A1 |

| УСТРОЙСТВО АНАЛОГОВОГО ДАТЧИКА УГЛА ФАЗОВОГО СДВИГА МЕЖДУ НАПРЯЖЕНИЕМ И ТОКОМ | 2011 |

|

RU2492572C2 |

| Электропривод постоянного тока | 1986 |

|

SU1661951A1 |

| Фазовый дискриминатор | 1986 |

|

SU1334355A1 |

| Преобразователь напряжения в интервал времени | 1988 |

|

SU1649662A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И ПРЕОБРАЗОВАНИЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2001 |

|

RU2203520C2 |

| Устройство управления зарядом никель- ВОдОРОдНОй АККуМуляТОРНОй бАТАРЕи | 1979 |

|

SU807446A1 |

| Фазовращатель | 1984 |

|

SU1224739A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

Изобретение относится к радиотехнике и .может использоваться в устр-вах АПЧ. Цель изобретения - улучшение темсвязи, сер. РИТ, пературной стабильности. Устройство содержит D-триггеры 1 и 2, элемент И - НЕ 3, четыре резистора 4, 5, 6, 7, конденсатор 8, операционный усилитель 9. В устройство введен второй конденсатор 10, соединенный с неи1шертирую1цим входом операционного усилителя. В результате одновременного понижения напряжения на неинвертирующем и новышения напряжения на инвертирующем входах операционного усилителя 9 напряжение на выходе частотно-фазового детектора понижается до момента прихода переднего фронта сигнала на вход синхро цизации D-триггера 1, пропорционального разности фаз входных сигналов. 1 ил.

.В)(одг

;

Выход

а:

10

Изобретение относится к радиотехнике и может использоваться в устройствах автоподстройки частоты.

Цель изобретения - улучшение температурной стабильности.

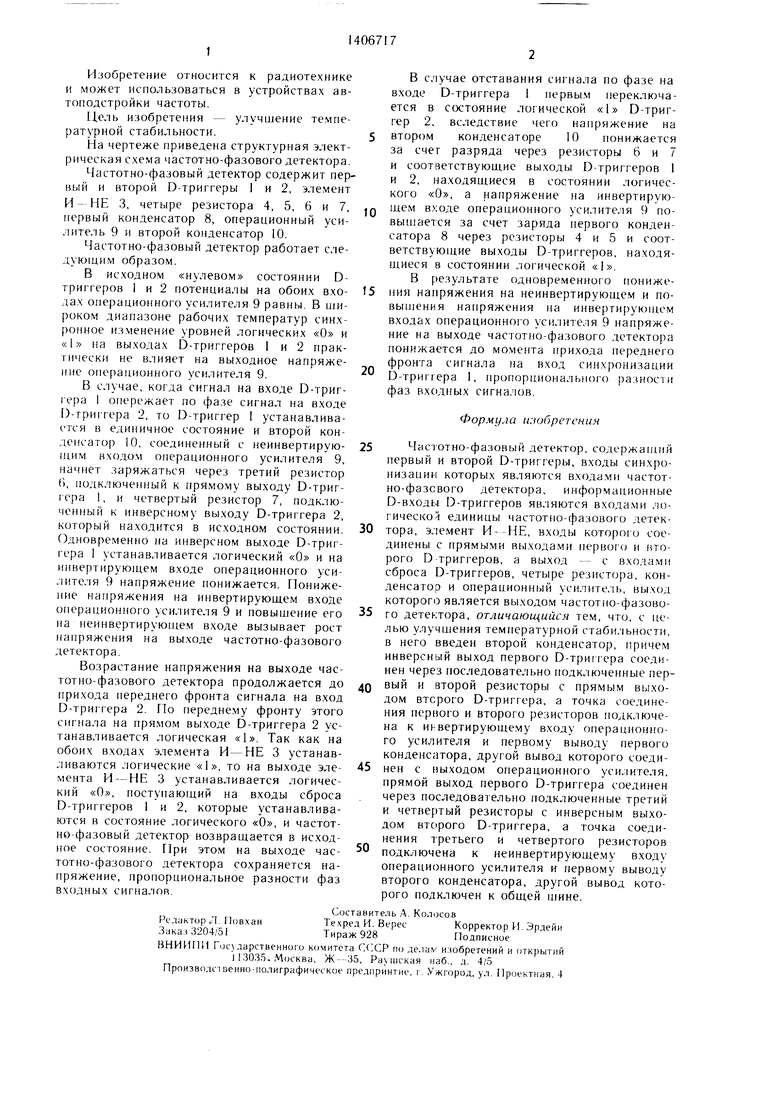

На чертеже приведена структурная электрическая схема частотно-фазового детектора.

Частотно-фазовый детектор содержит первый и второй D-триггеры 1 и 2, элемент

И- НЕ 3, четыре резистора 4, 5, 6 и 7, иервый конденсатор 8, операционный усилитель 9 и второй конденсатор 10.

Частотно-фазовый детектор работает следующим образом.

В исходном «нулевом состоянии D- триггеров 1 и 2 потенциалы на обоих входах операционного усилителя 9 равны. В широком диапазоне рабочих температур синхронное изменение уровней логических «О и «I на выходах D-триггеров 1 и 2 практически не влияет на выходное напряжение операционного усилителя 9.

В случае, когда сигнал на входе D-триг- гера 1 опережает по фазе сигнал на входе D-триггера 2, то D-триггер 1 устанавливается в единичное состояние и второй конденсатор 10, соединенный с неинвертирующим входо.м операционного усилителя 9, начнет заряжаться через третий резистор (, подключенный к прямому выходу D-триг- (ера 1, и четвертый резистор 7, подключенный к инверсно.му выходу D-триггера 2, который находится в исходном состоянии. Одновременно на инверсном выходе D-триггера 1 устанавливается логический «О и на инвертирующем входе операционного усилителя 9 напряжение понижается. Понижение напряжения на инвертирующем входе операционного усилителя 9 и повышение его на неинвертирующем входе вызывает рост напряжения на выходе частотно-фазового детектора.

Возрастание напряжения на выходе частотно-фазового детектора продолжается до прихода иереднего фронта сигнала на вход D-триггера 2. По переднему фронту этого сигнала на прямом выходе D-триггера 2 устанавливается логическая «1. Так как на обоих входах элемента И-НЕ 3 устанавливаются логические «1, то на выходе элемента И - НЕ 3 устанавливается логический «О, поступающий на входы сброса D-триггеров 1 и 2, которые устанавливаются в состояние логического «О, и частотно-фазовый детектор возвращается в исходное состояние. При этом на выходе частотно-фазового детектора сохраняется напряжение, пропорциональное разности фаз входных сигналов.

0

5

0

5

0

5

0

5

0

В случае отставания сигнала по фазе на входе D-триггера 1 иервы.м переключается в состояние логической «I D-триггер 2, вследствие чего напряжение на втором конденсаторе 10 понижается за счег разряда через резисторы 6 и 7 и соответствующие выходы D-триггеров 1 и 2, находящиеся в состоянии логического «О, а напряжение на инвертирующем входе операционного усилителя 9 повышается за счет заряда первого конденсатора 8 через резисторы 4 и 5 и соответствующие выходы D-триггеров, находящиеся в состоянии логической «1.

В р)езультате одновременного понижения напряжения на неинвертирующем и повышения насфяжения на инвертирующем входах операционного усилителя 9 напряжение на выходе частотно-фазового детектора понижается до момента прихода переднего фронта сигнала на вход синхронизации D-триггера 1, пропорционального разности фаз входных сигналов.

Формула изобретения

Частотно-фазовый детектор, содержащий первый и второй D-триггеры, входы синхронизации которых являются входами частот- но-фазсвого детектора. информационные D-входы D-триггеров являются входами логической единицы частотно-фазового детектора, элемент И--НЕ, входы которого соединены с прямыми выходами первог о и (второго D-триггеров, а выход - с входами сброса D-триггеров, четыре резистора, конденсатор и операционный усилитель, выход которого является выходом частотно-фазового детектора, отличающийся тем, что, с целью улучшения температурной стабильности, в него введен второй конденсатор, причем инверсный выход первого D-триггера соединен через последовательно подключенные первый и второй резисторы с прямым выходом второго D-триггера, а точка соединения первого и второго резисторов подключена к инвертирующему входу операционного усилителя и первому выводу первого конденсатора, другой вывод которого соединен с 1 ыходом операционного усилителя, прямой выход первого D-триггера соединен через последовательно подключеннь е третий и четвертый резисторы с инверсным выходом второго D-триггера, а точка соединения третьего и четвертого резисторов подключена к неинвертирующему входу операционного усилителя и первому выводу второго конденсатора, другой вывод которого подключен к общей шине.

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Автоматический огнетушитель | 0 |

|

SU92A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-06-30—Публикация

1986-05-05—Подача