Изобретение относится к радиотехнике, а именно к технике радиосвязи, и может быть использовано в составе связных радиоприемных устройств, обеспечивающих прием и демодуляцию сигналов с программной перестройкой рабочей частоты (ППРЧ).

Известны устройства обнаружения сигналов: А.С. СССР N 566218; А.С. СССР N 717674; А.С. СССР N 800925; А.С. СССР N 800927; А.С. СССР N 809017; А.С. СССР N 907487; А.С. СССР N 987543. В известных устройствах задача обнаружения решается путем вычисления отношения правдоподобия и сравнения его с некоторым пороговым уровнем. Для обеспечения высокой помехоустойчивости в них применяется непараметрическая обработка сигнала, а именно используются ранговые статистики, однако эти устройства невозможно непосредственно использовать в связных коротковолновых радиоприемниках, работающих в режиме приема сигналов с ППРЧ, что обусловлено недостаточными функциональными возможностями обнаружителей: во-первых, они не рассчитаны на обнаружение сигналов, имеющих структуру частотно-временной матрицы, во-вторых, в них не решается задача синхронизации.

Наиболее близким техническим решением к заявляемому является квазиоптимальный некогерентный обнаружитель сигналов с ППРЧ, который выбран в качестве прототипа [1].

Известный квазиоптимальный некогерентный обнаружитель сигналов с ППРЧ содержит сумматор, пороговый блок, коммутатор, блок накопителей, блок выбора максимума сигнала, N параллельных каналов (N параллельных трактов обработки), каждый из которых включает последовательно соединенные перемножитель (преобразователей частоты), полосовой фильтр, детектор огибающей и квадратор, сигнальные входы всех каналов объединены и являются сигнальным входом устройства, другие входы всех перемножителей подключены к напряжениям опорных частот, выходы квадраторов всех N каналов подключены через коммутатор к последовательно соединенным блоку накопителей и блоку выбора максимального сигнала, первый и второй выходы которого подключены к соответствующим входам сумматора, выход сумматора соединен с входом порогового блока, выход которого является выходом обнаружителя.

Недостатком известного устройства является недостаточная помехоустойчивость в условиях воздействия широкого спектра помех, поскольку для принятия решения об обнаружении сигнала применяется статистика, основанная на использовании истинных значений принимаемого напряжения, а не робастная. Кроме того, прототип, как и все перечисленные выше аналоги, не решает задачу синхронизации. Известное устройство обнаружения предполагает, что число каналов (трактов) обработки сигналов с ППРЧ равняется общему количеству используемых для работы частот (см. А.С. СССР N 1569998). В результате, увеличение числа применяемых рабочих частот, необходимое для повышения помехоустойчивости, будет вызывать усложнение устройства.

Целью изобретения является разработка устройства обнаружения, обеспечивающего более высокую помехоустойчивость и имеющего большие функциональные возможности.

Поставленная цель достигается тем, что в известное устройство обнаружения сигналов с ППРЧ, содержащее блок опорных частот, имеющий N частотных выходов, блок накопителей, блок выбора максимума сигнала и N параллельных трактов обработки (где N ≥ 2), каждый из которых содержит последовательно соединенные преобразователь частоты, полосовой фильтр и детектор огибающей, причем сигнальные входы всех преобразователей частоты объединены и являются сигнальным входом устройства, входы гетеродинирующих напряжений преобразователей частоты подключены к соответствующим частотным выходам блока опорных частот, выходы каждого из N трактов обработки подключены к соответствующим информационным входам блока накопителей, информационные выходы которого соединены с входами блока выбора максимума сигнала, дополнительно введены распределитель импульсов и управляемый делитель с входами "Синхронизация" и "Установка", последний из которых соединен с входами "Пуск" блока опорных частот и распределителя импульсов. Выходы "Тактовая частота" и "Опорная тактовая частота" управляемого делителя подключены к одноименным входам распределителя импульсов. Вход Ти и вход прерываний τэ блока опорных частот попарно объединены с входами Ти и τэ блока выбора максимума сигнала и подключены соответственно к выходам импульсов с длительностью Ти и τэ распределителя импульсов. Вход "Запуск" каждого из трактов обработки объединен с соответствующим входом "Запись" блока накопителей и подключен к соответствующему выходу "Запуск" распределители импульсов. N выходов "Разрешение" распределителя импульсов подключены к соответствующим N входам "Разрешение" блока накопителей. Выход распределителя импульсов "Начало шага" соединен с соответствующим входом прерывания "Начало шага" блока выбора максимума сигнала, выходы "Синхронизация есть", "Конец шага" и M выходов "Номер гипотезы" которого соединены с соответствующими входами управляемого делителя (где M - 2, 3, ... ,). N входов "Готовность данных" блока выбора максимума сигнала соединены с соответствующими выходами блока накопителей. Вход "Импульс сопровождения адреса" блока накопителей подключен к одноименному выходу блока выбора максимума сигнала.

Распределитель импульсов содержит счетчик-делитель на R, N двухвходовых элементов И, N инверторов, N дифференцирующих цепочек, двухвходовой элемент ИЛИ, N-входовой элемент ИЛИ и элемент задержки. Входы N инверторов и N дифференцирующих цепочек попарно объединены и соединены соответственно с 1, ... , N выходами счетчика-делителя на R. Выход первой дифференцирующий цепочки соединен с входом элемента задержки, выход которого подключен к первому входу N-входового элемента ИЛИ, выходы остальных дифференцирующих цепочек подключены к соответствующим (N-1) входам N-входового элемента ИЛИ. (N+1)-й выход счетчика-делителя на R подключен к первому входу двухвходового элемента ИЛИ, выход которого соединен с входом "Обнуление" счетчика-делителя на R. Выходы N инверторов соединены соответственно с первыми входами N элементов И, вторые входы которых объединены между собой и являются входом "Тактовая частота" распределителя импульсов. Выходы всех элементов И являются первой группой из N выходов "Запуск" распределителя импульсов. "Счетный" вход счетчика-делителя на R является входом "Опорная тактовая частота" распределителя импульсов. Выходы N инверторов образуют вторую группу из N выходов "Разрешение" распределителя импульсов. Второй вход двухвходового элемента ИЛИ является входом "Пуск" распределителя импульсов. Выход первой дифференцирующей цепочки и выход N-входового элемента ИЛИ являются соответственно выходами импульсов длительностью Ти и τэ распределителя импульсов.

Управляемый делитель содержит опорный генератор, первый, второй и третий делители частоты, счетчик делитель, первый дешифратор, второй дешифратор, реверсивный счетчик, счетчик шагов, таймер, пять двухвходовых элементов И, два двухвходовых элемента ИЛИ, два инвертора, две дифференцирующие цепочки, элемент задержки, TB-триггер и RS-триггер. Выход опорного регенератора подключен к входу первого делителя частоты, счетный вход счетчика-делителя объединен с первым входом первого элемента И и соединен с выходом первого делителя частоты. Выход счетчика-делителя подключен к счетному входу реверсивного счетчика, выходы которого 1,...,G подключены соответственно к входам первого дешифратора. Второй вход первого элемента И объединен с входом первого инвертора и подключен к выходу первого дешифратора. Разрешающий вход счетчика-делителя соединен с выходом первого инвертора. Входы второго и третьего делителей частоты объединены и соединены с выходом первого элемента И. Выход верхней частоты третьего делителя соединен с первым входом второго элемента И, второй вход которого соединен с выходом третьего элемента И, на первый вход которого поступает напряжение с выхода TB-триггера. Счетный вход TB-триггера соединен с выходом счетчика шагов, управляющий вход которого объединен с первым входом первого элемента ИЛИ и подключен к выходу первой дифференцирующей цепочки. Вход первой дифференцирующей цепочки объединен с первым входом пятого элемента И и соединен с выходом RS-триггера. Счетный вход счетчика с выходом объединен с вторым входом первого элемента ИЛИ и соединен с выходом пятого элемента И. Выход первого элемента ИЛИ подключен к установочному входу таймера, счетный вход которого объединен с первым входом четвертого элемента И и соединен с выходом нижней частоты третьего делителя частоты. Выходы таймера соединены с входами второго дешифратора. Второй вход четвертого элемента И объединен с входом второго инвертора, разрешающим входом таймера, входом второй дифференцирующей цепочки и подключен к выходу второго дешифратора, выходы второго и четвертого элементов И соединены соответственно с входами второго элемента ИЛИ. Выход второй дифференцирующей цепочки соединен с входом элемента задержки. Вход "Разрешение" реверсивного счетчика объединен с R-входом RS-триггера и является входом "Синхронизация есть" управляемого делителя. Второй вход пятого элемента И является входом "Конец шага" управляемого делителя. S-вход RS-триггера является входом "Синхронизация" управляемого делителя. Обнуляющий вход реверсивного счетчика объединен с установочным входом TB-триггера, обнуляющим входом счетчика шагов и является входом "Установка" управляемого делителя. Входы 1,...,М реверсивного счетчика являются входами соответственных разрядов "Номер гипотезы" управляемого делителя. Выход элемента задержки является выходом сигнала "Начало шага" управляемого делителя. Выход второго делителя частоты является выходом "Тактовая частота" управляемого делителя. Выход второго элемента ИЛИ является выходом "Опорная тактовая частота".

Предлагаемое техническое решение основано на совместном выполнении функций поиска, обнаружения и оценивания временного параметра сигнала с ППРЧ.

Сущность предложения по сокращению количества трактов обработки сигнала с ППРЧ по сравнению с прототипом основывается на осуществлении временной привязки работы блока опорных частот к сигналам службы единого времени. Это позволяет существенно ограничить область временной неопределенности возможного положения подлежащего обнаружению сигнала (например, при ручной привязке эта область может достигать одной - двух секунд). Введенные в заявляемое устройство блоки позволяют осуществлять последовательно-параллельный поиск сигнала в зоне неопределенности, в результате задача обнаружения решается с использованием того же количества трактов обработки, которое применяется для демодуляции.

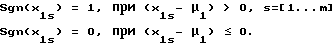

Сущность предложения по повышению помехоустойчивости заявляемого устройства по сравнению с прототипом основано на использовании в нем непараметрической обработки сигнала. Так, для принятия решения о наличии или отсутствии сигнала в том или ином элементе зоны временной неопределенности применяется знакоранговая статистика. При анализе одного элемента зоны временной неопределенности время оценивания выбрано таким, чтобы случайный процесс, наблюдаемый в каждом частотном тракте обработки, можно было считать стационарным. Разнос между частотами взят таким, чтобы помехи в разных трактах можно было считать независимыми. Тогда, после взятия достаточно частых отсчетов продетектированного напряжения в каждом тракте обработки, суммирования их и деления на количество взятых отсчетов можно для каждого из трактов определить свое среднее значение обработанного напряжения. Например, пусть для первого частотного тракта из продетектированного в течение времени T напряжения формируется выборка X1, состоящая из m отсчетов и имеющая вид x11, x12,..., x1m, где первый индекс это номер выборки, а второй - номер отсчета в ней. Тогда, среднее значение напряжения взятых отсчетов в первой выборке равно μ1= (1/m) • (x11+...+x1m) . Далее, для каждого тракта обработки вводится модифицированная выборка, в которой истинные значения взятых отсчетов заменяются усеченными. Усеченные значения отсчетов получаются с использованием знаковой функции .

.

В условиях действия только помех вероятность превышения любым отсчетом среднего значения в своем тракте обработки для помехи с произвольной симметричной функцией плотности вероятности будет равна 1/2. После суммирования значений отсчетов модифицированных выборок по всем трактам обработки за время анализа одного участка неопределенности получим сумму первых отсчетов S1, сумму вторых отсчетов S2 и так далее.

.

.

где

K - количество выборок, формируемых при анализе одного участка неопределенности.

При отсутствии сигнала значения каждой из сумм будут примерно одинаковыми, поскольку помехи, действующие в разных трактах, статистически независимы. При появлении на входе устройства полезного сигнала отсчеты в определенные моменты на разных частотах уже будут зависимы. Те суммы, которые соответствуют по времени одновременному присутствию сигнала и помех, будут намного больше, чем те, где сигнал отсутствует. Выбрав определенным образом пороговый уровень, можно обеспечить стабильное значение вероятности ложной тревоги для более широкого класса помех, чем гауссовские.

Сущность предложения по оцениванию истинного временного положения обнаруженного сигнала с ППРЧ сводится к следующему. После того, как сигнал обнаружен, решение о его наиболее вероятном положении в анализируемом участке временной неопределенности принимается с использованием хранящихся в памяти истинных значений взятых отсчетов по всем трактам обработки. Для этого в тех модифицированных суммах, в которых произошло превышение порогового уровня, усеченные значения отсчетов заменяются величиной превышения истинного значения над средним, суммируются и значения сумм сравниваются между собой. То временное положение, для которого значение суммы отсчетов получается наибольшим, и является наиболее точным временным положением сигнала с ППРЧ.

При такой совокупности существенных признаков предлагаемое устройство, наряду с решением задачи обнаружения сигналов с ППРЧ, дополнительно решает и задачу синхронизации, определяя с требуемой точностью положение сигнала с ППРЧ на оси времени и имея в своем составе при этом меньшее, чем в прототипе, количество трактов обработки.

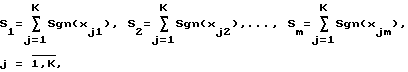

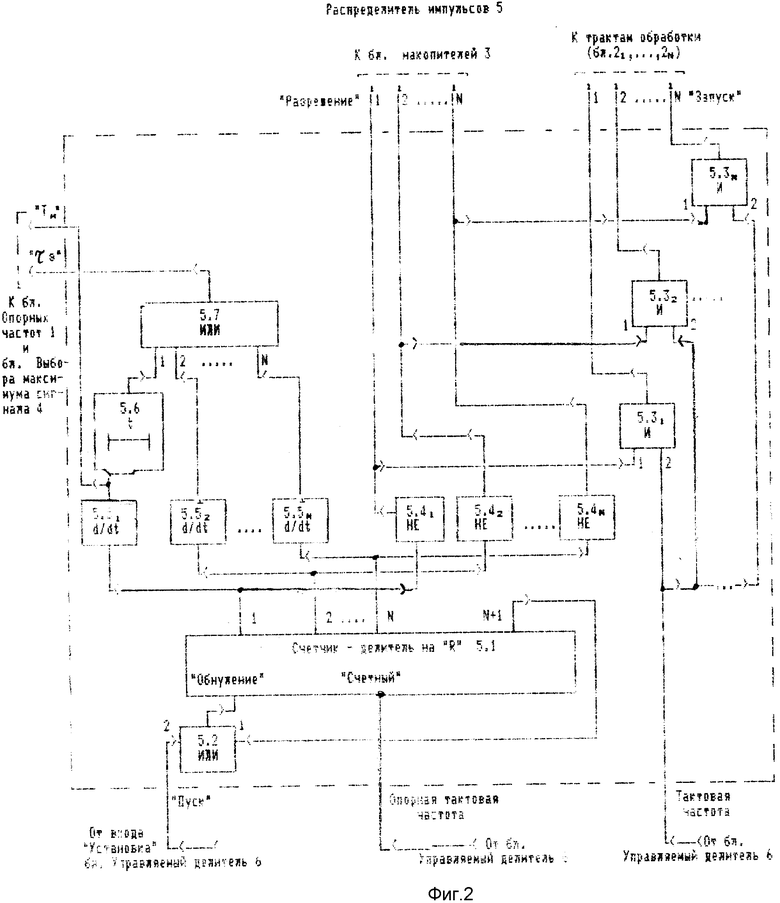

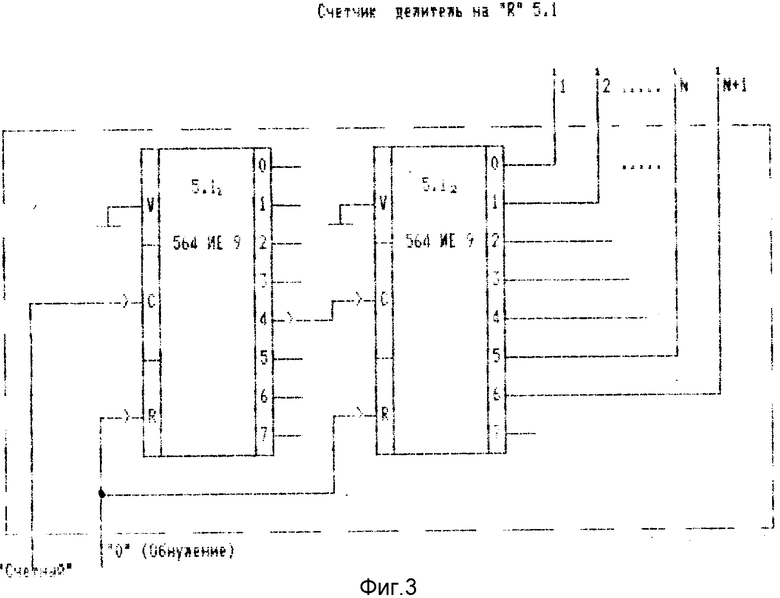

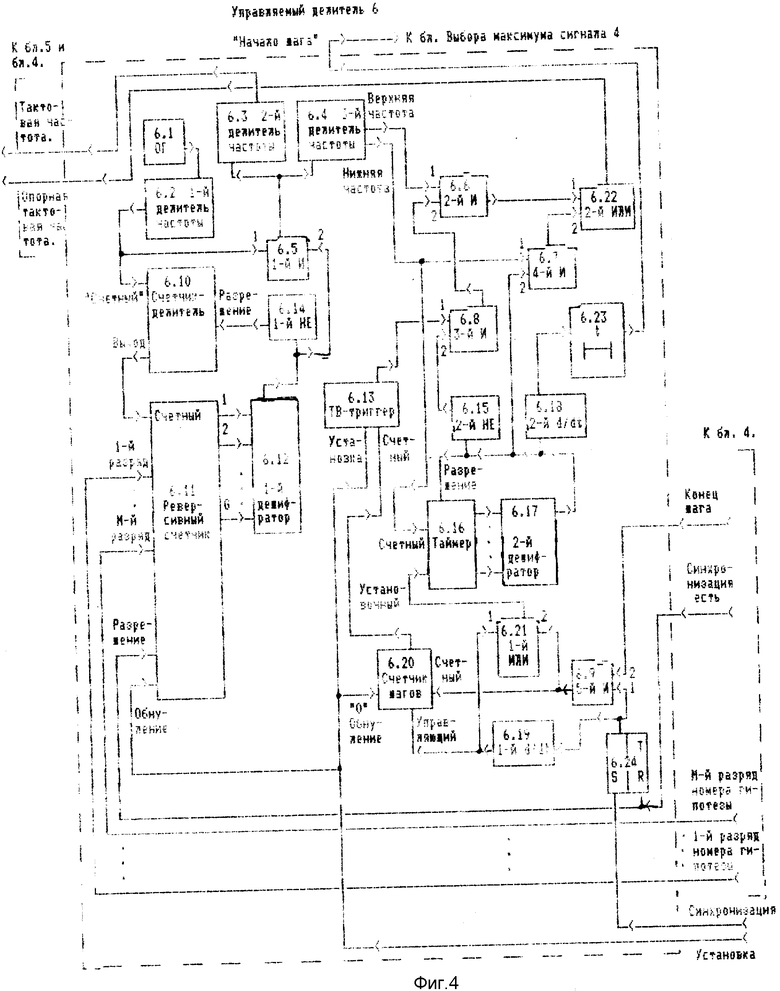

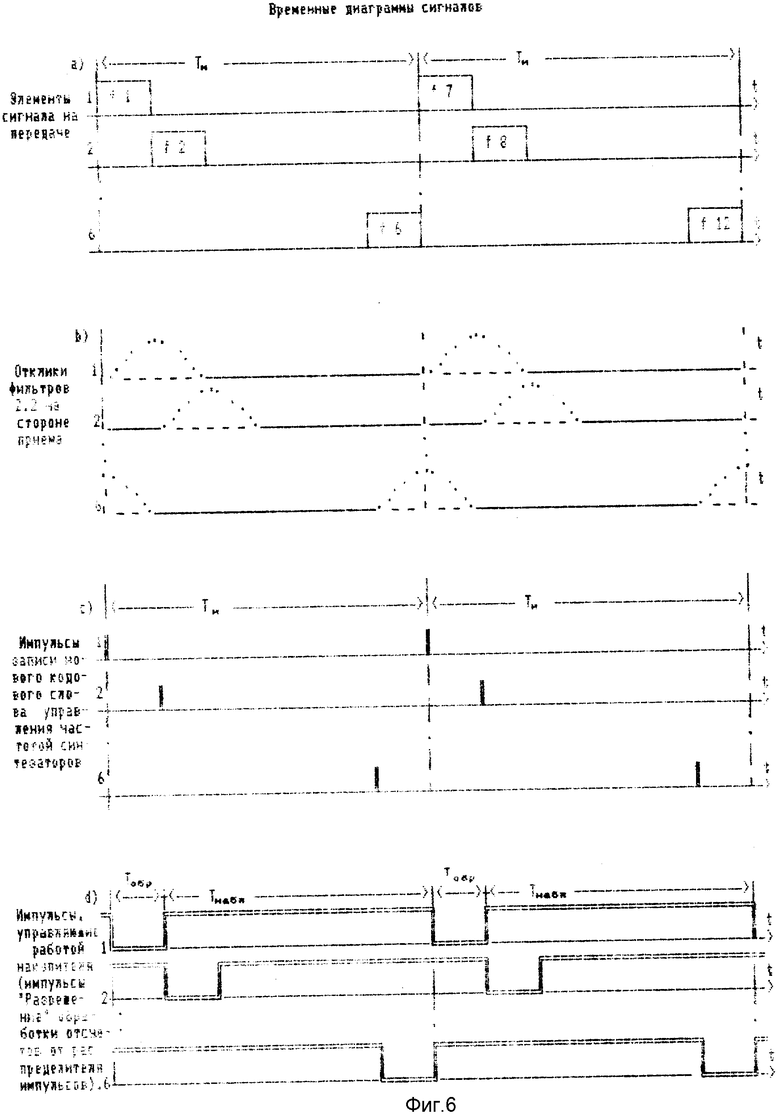

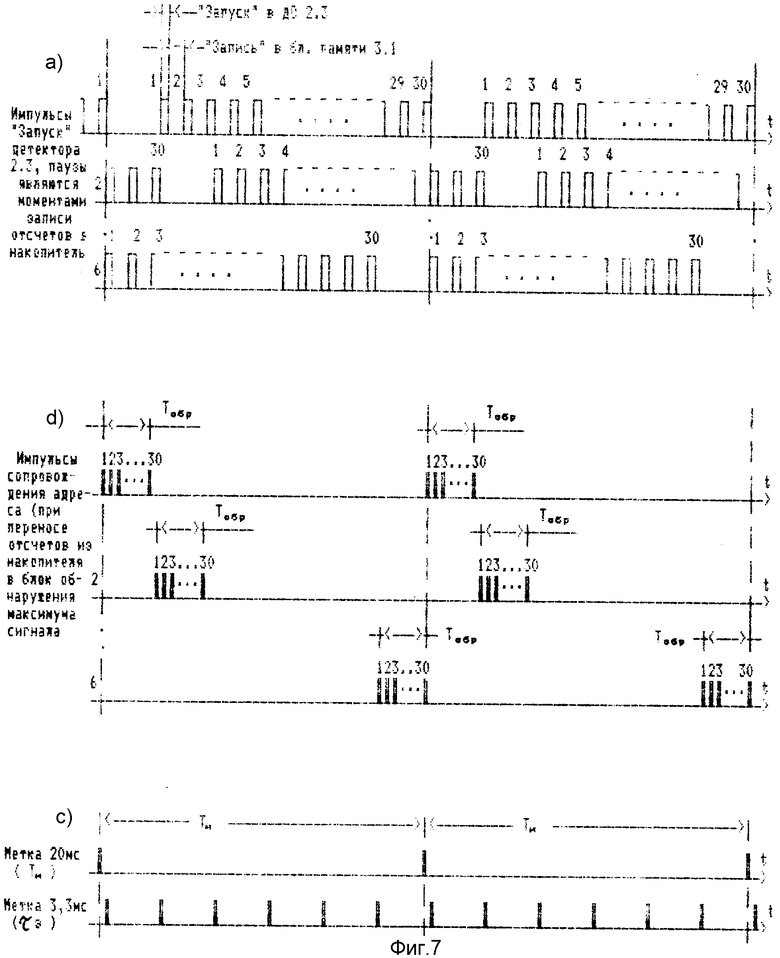

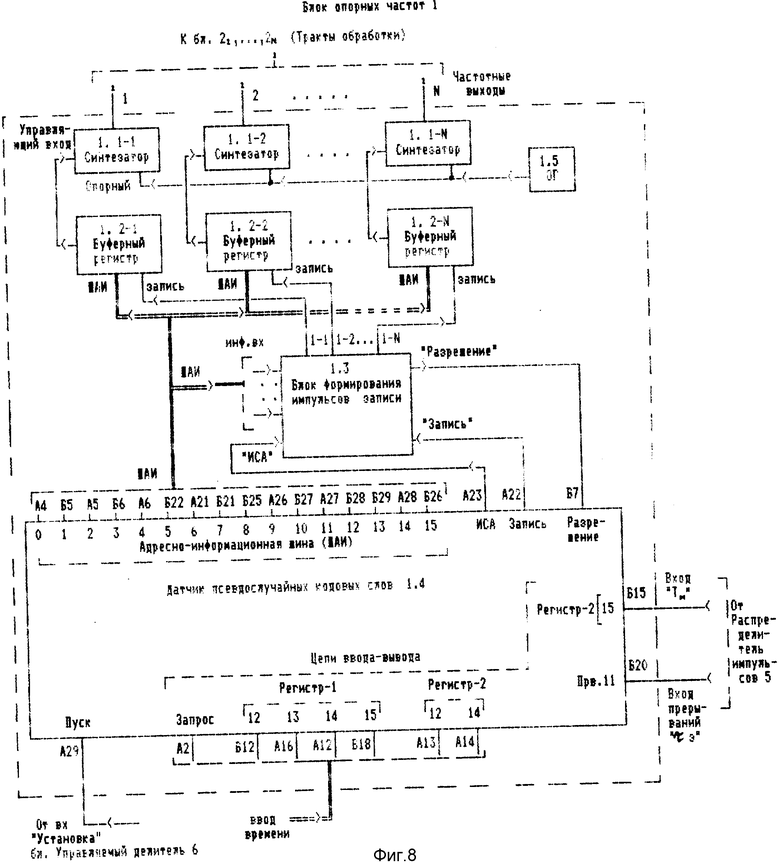

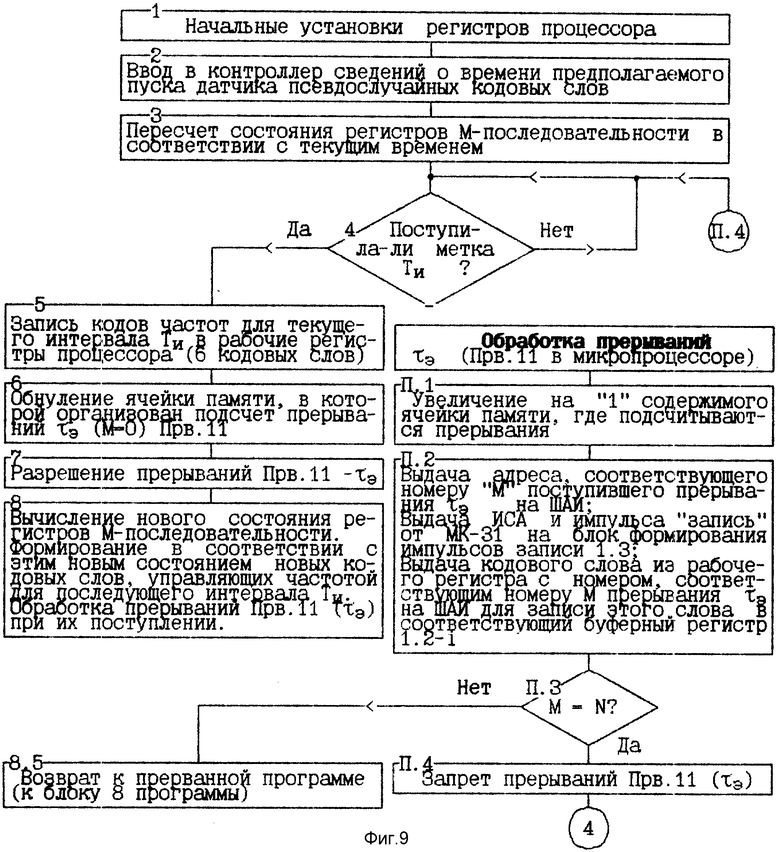

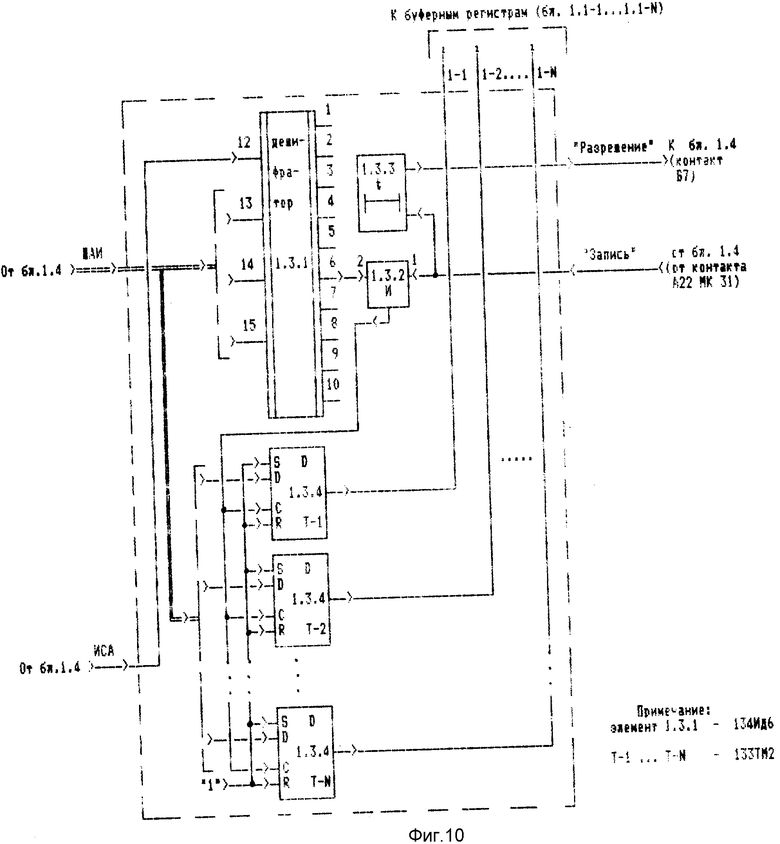

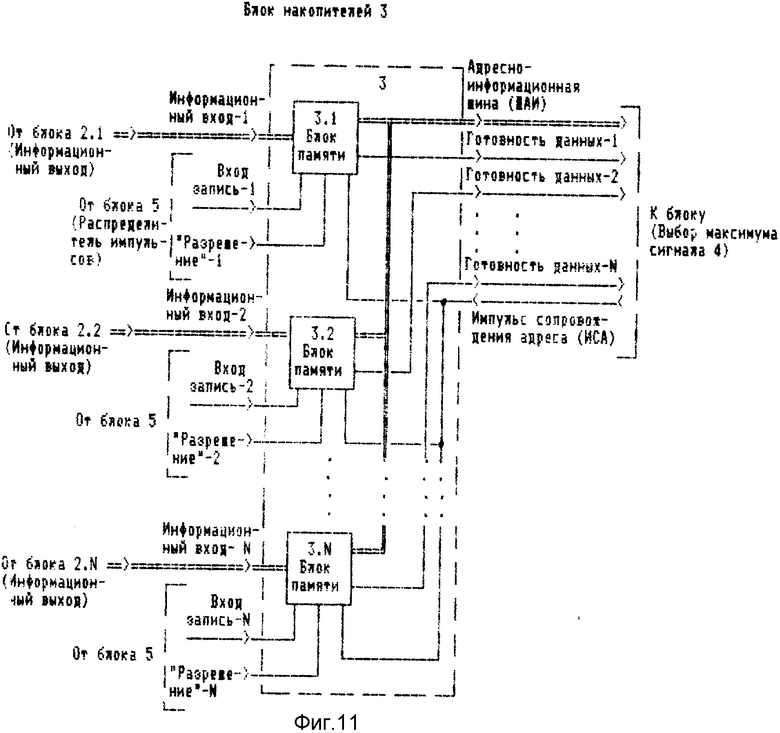

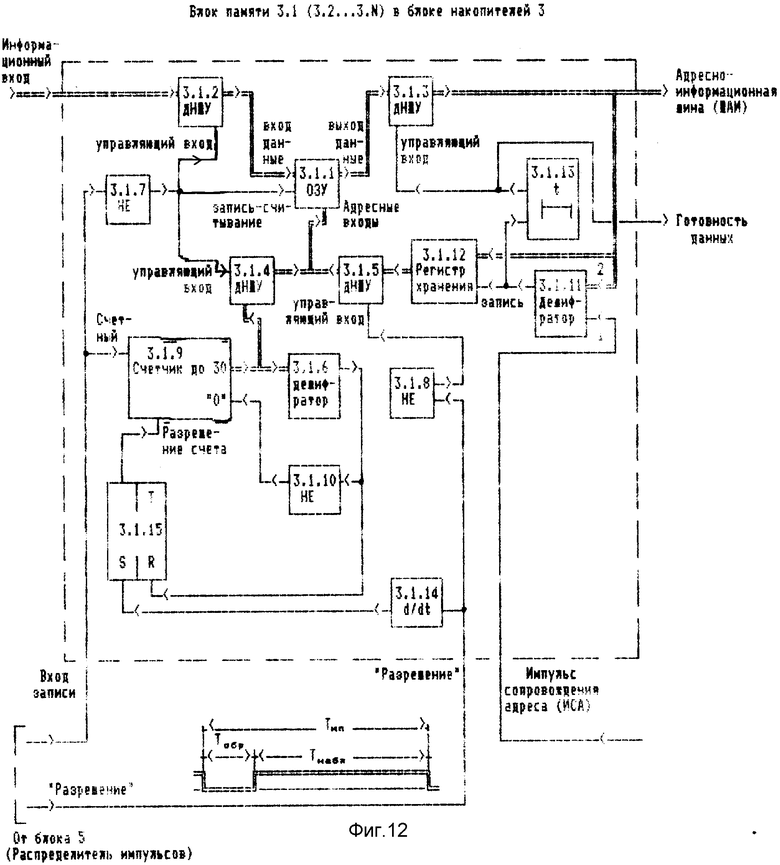

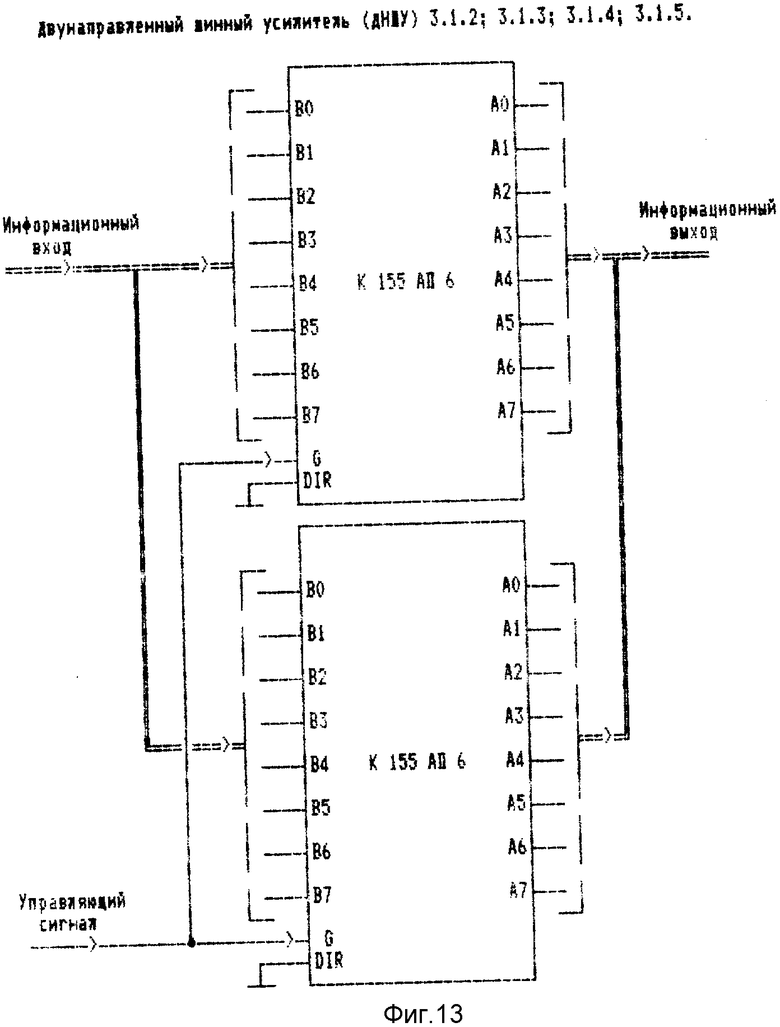

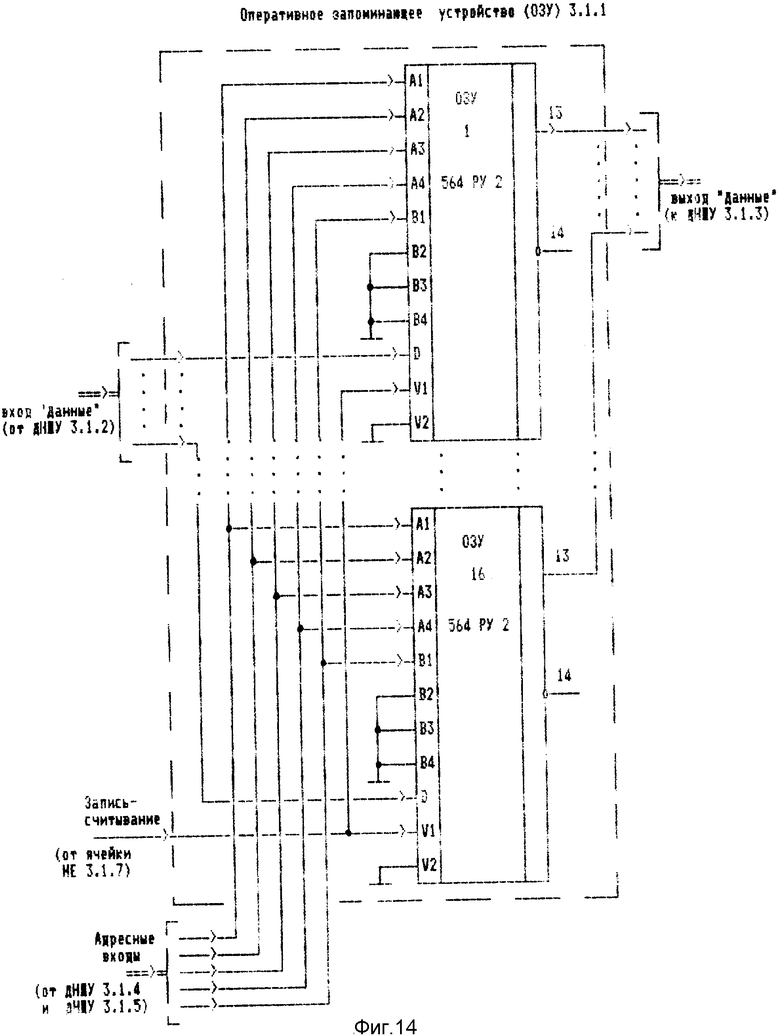

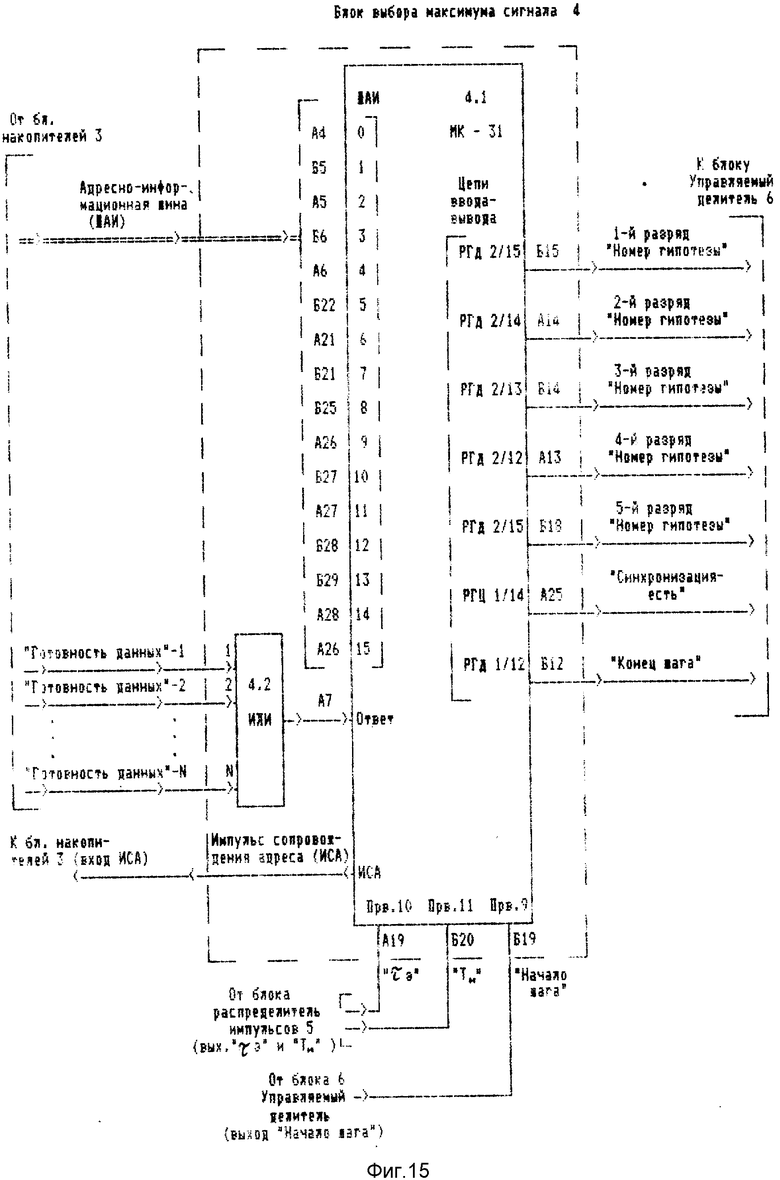

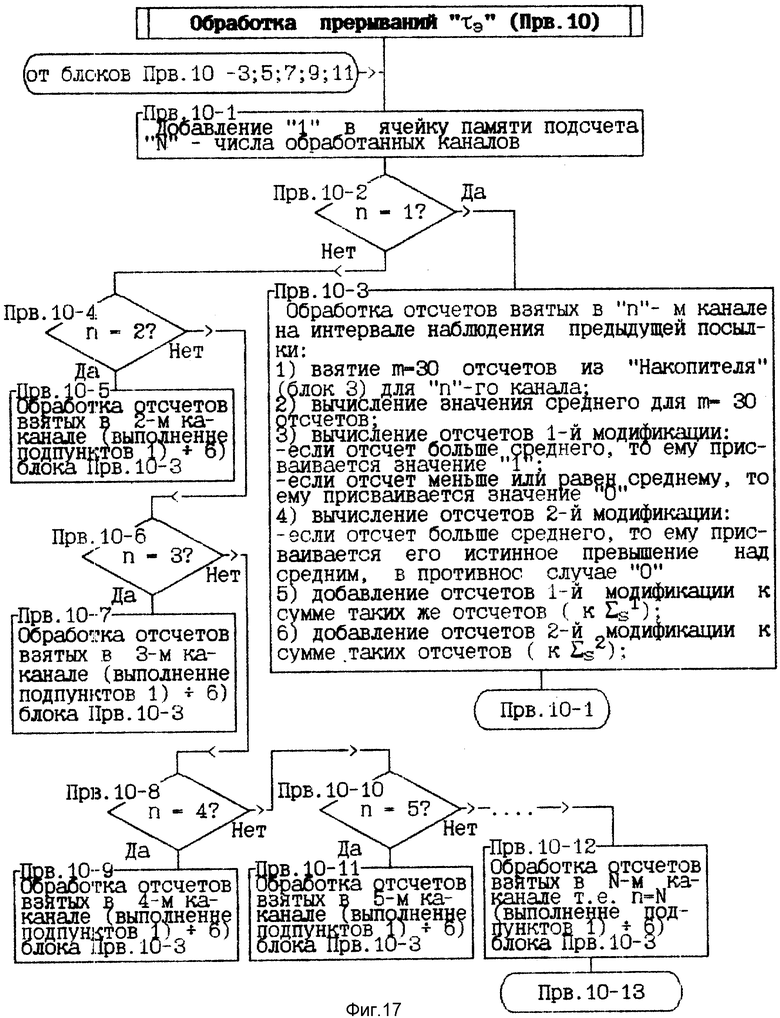

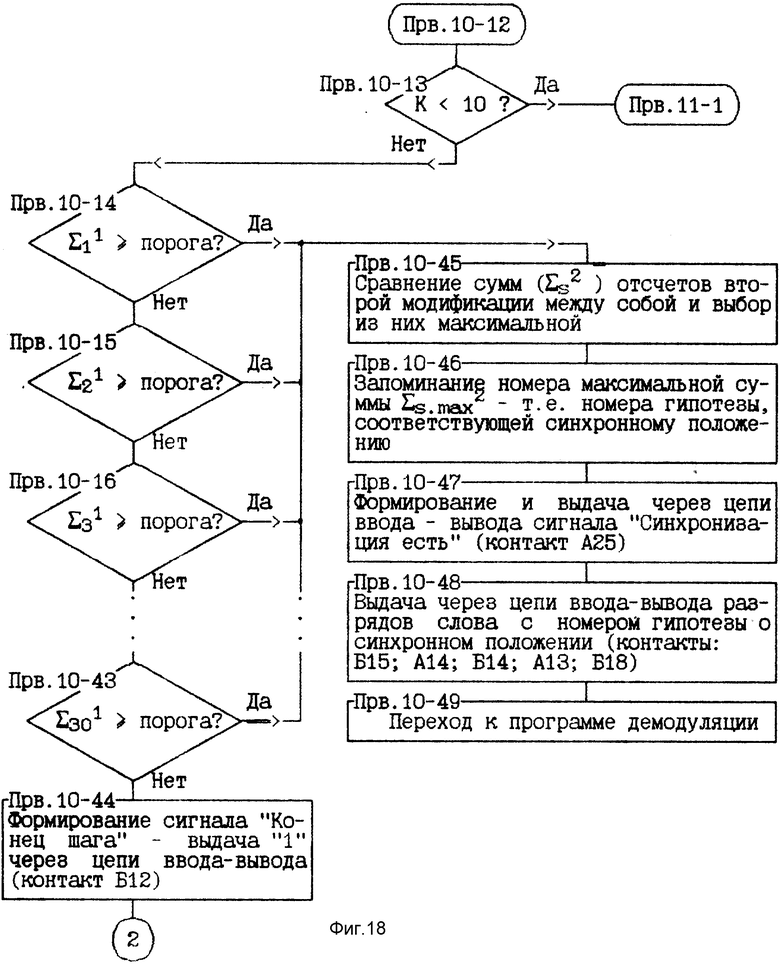

На фиг.1 изображено устройство обнаружения сигналов с ППРЧ; на фиг. 2 - распределитель импульсов (РИ) 5; на фиг. 3 - счетчик делителя на "R" 5.1; на фиг. 4 - управляемый делитель 6; на фиг. 5 - счетчик шагов 6.20; на фиг. 6 и 7 -временные диаграммы сигналов, поясняющие принцип работы заявляемого устройства; на фиг. 8 - блок опорных частот 1; на фиг. 9 - блок-схема программы микроконтроллера, реализующего функцию датчика псевдослучайных кодовых слов 1.4; на фиг. 10 - блок формирования импульсов записи 1.3; на фиг. 11 - блок накопителей 3; на фиг. 12 - схема блоков памяти 3.1 (3.2, ..., 3.N); на фиг. 13 - двунаправленный шинный усилитель 3.1.2 - 3.1.5; на фиг. 14 - оперативное запоминающее устройство (ОЗУ) 3.1.1 ; на фиг. 15 - блок выбора максимума сигнала 4; на фиг. 16-18 - блок-схема программы микроконтроллера в блоке выбора максимума сигнала 4.

Устройство обнаружения сигналов с ППРЧ, показанное на фиг.1, содержит блок опорных частот (БОЧ)1, блок накопителей 3, блок выбора максимума сигнала (БВМС)4, распределитель импульсов (РИ)5, управляемый делитель (УД)6 и N трактов обработки с 21 по 2N, в каждом из трактов обработки 21, ..., 2N имеется преобразователь частоты (ПЧ) 2.1, полосовой фильтр (ПФ) 2.2, детектор огибающей (ДО) 2.3. БОЧ 1 имеет входы "Пуск", "Ввод времени", "Ти", "Прерывание τэ " и N частотных выходов. Вход "Ввод времени" служит для ввода информации о текущем времени, вход "Пуск" является входом запуска времени, входы Ти и прерывания τэ соединены соответственно с выходами Ти и τэ РИ 5. Частотные выходы ВОЧ 1 с 1-го по N-й соединены с гетеродинными входами ПЧ 2.1 соответственно с 1-го по N-й всех трактов обработки. Первые входы ПЧ 2.1 всех трактов обработки объединены между собой и являются сигнальным входом устройства. В каждом тракте обработки выход ПЧ 2.1 соединен с входом ПФ 2.2, выход ПФ 2.2 соединен с первым входом ДО 2.3. Выходы ДО 2.3 всех N трактов обработки с помощью информационных шин соединены с соответствующими информационными входами блока накопителей 3. Каждый из N входов "Запись" блока накопителей 3 объединен с входом "Запуск" ДО 2.3 соответствующего тракта обработки и подключен к соответствующему выходу "Запуск" РИ 5. Входы "Разрешение" блока накопителей 3 соединены с соответствующими выходами "Разрешение" РИ 5. Вход "Импульс сопровождения адреса" (ИСА) блока накопителей 3 соединен с соответствующим выходом ВВМС 4. Выходная адресно-информационная шина (ШАИ) блока накопителей 3 соединена с ШАИ ВВМС 4. N выходов "Готовность данных" блока накопителей 3 соединены соответственно с N входами "Готовность данных" ВВМС 4. Входы прерывания Ти и τэ БВМС 4 подключены к соответствующим выходам РИ 5, вход прерывания "Начало шага" соединен с соответствующим выходом УД 6. Выходы БВМС 4 "Конец шага", "Синхронизация есть", а также выходы с 1-го по М-й разрядов "Номер гипотезы" соединены с одноименными входами УД 6, который кроме того имеет вход "Синхронизация" и вход "Установка". Вход "Установка" УД 6 соединен с входами "Пуск" БОЧ 1 и РИ 5. Выходы УД 6 "Тактовая частота" и "Опорная тактовая частота" соединены с соответствующими входами РИ 5.

На фиг.2 приведена схема РИ 5, предназначенного для формирования сигналов управления во времени работы блоков, входящих в устройство обнаружения сигналов с ППРЧ.

РИ 5 содержит счетчик-делитель на R 5.1, двухвходовой логический элемент ИЛИ 5.2, N двухвходовых элементов И 5.31 - 5.3N, N инверторов 5.41 - 5.4N дифференцирующих цепей 5.51 - 5.5N, элемент задержки 5.6 и N-входовой элемент ИЛИ 5.7. Вход "Пуск" РИ 5 является вторым входом элемента ИЛИ 5.2, вход "Опорная тактовая частота" является счетным входом счетчика-делителя 5.1 на R, вход "Тактовая частота" соединен с объединенными вторыми входами N элементов И 5.3. Выходы РИ Ти и τэ являются выходами первой диф. цепочки 5.51 и элемента ИЛИ 5.7 соответственно. N выходов РИ 5 "Разрешение" являются выходами N инверторов 5.41 - 5.4N. N выходов "Запуск" являются выходами N элементов И 5.31 - 5.3N. Входы диф. цепочек 5.51 - 5.5N попарно объединены и подключены к N выходам счетчика-делителя на R 5.1, (N + 1)-й выход которого соединен с первым входом логического элемента ИЛИ 5.2. Вход обнуления счетчика-делителя на R 5.1 подключен к выходу элемента ИЛИ 5.2. Выход диф. цепочки 5.51 подключен к первому входу элемента ИЛИ 5.7 через элемент задержки 5.6, выходы остальных диф. цепей 5.52 - 5.5N подключены непосредственно к соответствующим входам элемента ИЛИ 5.7. Выходы инверторов 5.41 - 5.4N соединены с первыми входами N элементов И 5.31 - 5.3N.

Схемы дифференцирующих цепей 5.51 - 5.5N известны (Титце У. и Шенк К. Полупроводниковая схемотехника.-М.: Мир. 1982, с. 146, рис. 11.16.)

Схемы задержки известны (Фролкина В.Т. Импульсные устройства. М.: Машиностроение, 1966, с. 42). Элемент задержки 5.6 может быть выполнен на RC-цепи.

Счетчик-делитель на R 5.1 предназначен для выработки опорных сигналов в РИ 5.

Схемы счетчиков-делителей известны и описаны (Шило В.Л. Популярные цифровые микросхемы. Справочник. М. : Радио и связь, 1987, с. 239-241, рис. 2.40). В частности, как показано на фиг. 3 для R-30 такая схема может быть реализована на микросхеме 564 ИЕ 9.

Схема счетчика делителя на R 5.1 содержит два счетчика (5.11 и 5.12), счетный вход счетчика 5.11 является счетным входом счетчика-делителя на R 5.1. Входы обнуления обоих счетчиков (входы R) объединены и являются входом "Обнуление" счетчика-делителя на R 5.1. Выход 5-го разряда счетчика 5.11 соединен с счетным входом счетчика 5.12, (N + 1), выходы которого являются выходами счетчика-делителя на R 5.1.

На фиг. 4 показана схема УД 6, предназначенного для осуществления сдвигов во времени (в пределах области неопределенности) всех управляющих сигналов в устройстве обнаружения сигналов с ППРЧ.

УД 6 содержит опорный генератор (ОГ) 6.1, три делителя частоты 6.2-6.4, пять двухвходовых логических элементов И (6.5-6.9), счетчик-делитель 6.10, реверсивный счетчик 6.11, дешифратор 6.12, ТВ-триггер 6.13, два инвертора 6.14 и 6.15, таймер 6.16 с дешифратором 6.17, две дифференцирующие цепочки (диф. цепочки) 6.18 и 6.19, счетчик шагов 6.20, два логических элемента ИЛИ 6.21 и 6.22, элемент задержки 6.23 и RS-триггер 6.24.

Вход УД 6 "Установка" соединен с входами обнуления реверсивного счетчика 6.11, счетчика шагов 6.20 и установочным входом ТВ-триггера 6.13. Входы УД 6 1-й, 2-й, ..., M-й разряды "Номер гипотезы" подключены соответственно к входам "1-й разряд", "2-й разряд", ..., "M-й разряд" реверсивного счетчика 6.11. Вход "Конец шага" УД 6 соединен с вторым входом пятого элемента И 6.9. Вход УД 6 "Синхронизация есть" соединен с R-входом RS-триггера 6.24 и входом "Разрешение" реверсивного счетчика 6.11. Вход УД 6 "Синхронизация" соединен с S-входом RS-триггера 6.24. Выход УД 6 "Тактовая частота" является выходом второго делителя частоты 6.3. Выход УД 6 "Опорная тактовая частота" является выходом второго тактового элемента ИЛИ 6.22, а выход "Начало шага" - выходом элемента задержки 6.23.

Выход опорного генератора 6.1 через первый делитель частоты 6.2 подключен к первому входу первого элемента И 6.5 и счетному входу счетчика-делителя 6.10, выход которого соединен со счетным входом реверсивного счетчика 6.11. G выходов реверсивного счетчика 6.11 подключены к входам первого дешифратора 6.11, выход которого соединен с вторым входом первого элемента И 6.5 непосредственно и с входом "Разрешение" счетчика-делителя 6.10 через первый инвертор 6.14. Выход первого элемента И 6.5 подключен к входам второго и третьего делителя частоты 6.3 и 6.4. Выход "Верхняя частота" третьего делителя частоты 6.4 соединен с первым входом второго элемента И 6.6, а выход "Нижняя часть" - с первым входом четвертого элемента И 6.7 и счетным входом таймера 6.16. Выходы второго и третьего элементов И 6.6 и 6.7 через второй элемент ИЛИ 6.22 подключены к выходу УД 6 "Опорная тактовая частота". Выход RS-триггера 6,24 подключен к первому входу пятого элемента И 6.9 непосредственно, а к управляющему входу счетчика шагов 6.20 и первому входу первого элемента ИЛИ 6.21 - через первую дифференциальную цепь 6.19. Выход пятого элемента И 6.9 соединен со счетным входом счетчика шагов 6.20 и вторым входом первого элемента ИЛИ 6.21, выход которого соединен с установочным входом таймера 6.16. Выход счетчика шагов 6.20 соединен со счетным входом триггера 6.13, выход которого подключен к первому входу третьего элемента И 6.8. Выходы таймера 6.16 соединены с вторым дешифратором 6.17, выход которого через второй инвертор 6.15 соединен с вторым входом третьего элемента И 6.8 и непосредственно соединен с входом "Разрешение" таймера 6.16, вторым входом четвертого элемента И 6.7 и входом второй диф. цепи 6.18, выход которого соединен с входом элемента задержки 6.23.

На фиг.5 приведена схема счетчика шагов 6.20, предназначенного для подсчета шагов по области неопределенности в процессе поиска сигнала с ППРЧ.

Счетчик шагов 6.20 содержит счетчик до 2-х 6.20.1, RS-триггер 6.20.2, элемент задержки 6.20.3, счетчик до L/2 6.20.4, двухвходовой элемент И 6.20.5, четыре логических элемента ИЛИ 6.20.6 - 6.20.9. Вход обнуления счетчика шагов 6.20 является первым входом элемента ИЛИ 6.20.7. Вход, по которому могут поступать сигналы от элемента И 6.9 в УД 6, является счетным выходом счетчика до L/2 6.20.4. Вход S RS-триггера 6.20.2 является управляющим входом триггера шагов 6.20 и подключен (в УД 6) к диф. цепи 6.19. Выходом счетчика шагов 6.20 является выход элемента ИЛИ 6.20.6, соединенный также с 2-м входом элемента ИЛИ 6.20.7. Первый вход элемента ИЛИ 6.20.6 подключен к L-му выходу счетчика до 2-х 6.20.1, а второй вход соединен с выходом элемента И 6.20.5. Входы обнуления счетчиков 6.20.1 и 6.20.4 объединены и соединены с 1-м входом элемента ИЛИ 6.20.8 и выходом элемента ИЛИ 6.20.7. Вход "Разрешение" счетчика до L/2 6.20.4 соединен с выходом элемента ИЛИ 6.20.9, первый вход которого объединен с вторым входом И 6.20.5 и подключен к первому выходу RS-триггера 6.20.2. Второй вход элемента ИЛИ 6.20.9 объединен с входом "Разрешение" счетчика до 2-х 6.2-0.1 и подключен к 2-му выходу RS-триггера 6.20.2. Выход L/2 счетчика до L/2 6.20.4 подключен к счетному входу счетчика до 2-х 6.20.1, первому входу элемента И 6.20.5 и входу элемента задержки 6.20.3, выход которого соединен с вторым входом элемента ИЛИ 6.20.8. Выход элемента ИЛИ 6.20.8 соединен с R-входом RS-триггера 6.20.2.

Опорные генераторы известны (Павлов К.М. Радиоприемные устройства КВ cвязи: Учеб. пособие для техникумов связи. М.: Связь, 1980, с. 83, рис. 2.30).

Делители частоты 6.2, 6.3, 6.4 и 6.10 могут быть выполнены на счетных делителях, описанных в книге Шило В. Л. Популярные цифровые микросхемы. Справочник. -М. : Радио и связь, 1987, с. 240-242. В частности, их можно реализовать, например, на микросхемах 564 ИЕ 10. На таких же схемах может реализован таймер 6.16.

Реверсивный счетчик 6.11 описан в той же книге на с. 242-245 и может быть реализован на микросхеме 564 ИЕ 11.

Дешифраторы 6.12 и 6.17 описаны в книге Шило В.Л. Популярные цифровые микросхемы. Справочник. -М. : Радио и связь, 1987, с. 261-264 и могут быть реализованы на микросхеме 564 ИД 1. Триггеры ТВ и RS рассматриваются там же на с. 62-66.

На фиг. 8 приведена схема БОЧ 1, который предназначен для формирования гетеродинирующих напряжений для ПЧ 2.1 трактов обработки 21.

БОЧ 1 содержит N синтезаторов частот (с 1.1-1 по 1.1-N), N буферных резисторов (с 1.2-1 по 1.2-N), блок формирования импульсов записи (БФИЗ) 1.3 и датчик псевдослучайных кодовых слов (ДПКС) 1.4, и опорный генератор (ОГ) 1.5. Вход "Пуск" ДПКС 1.4 соединен с входом "Установка" устройства в целом. Входы цепей ввода-вывода ДПКС 1.4, а именно "Запрос", входы 12-15 "Регистр-1" и входы 12 и 14 "Регистр-2" образуют цепь "Ввод времени" в БОЧ 1. Адресно-информационные выходы ДПКС 1.4 образуют адресно-информационную шину (ШАИ). Входы ДПКС 1.4 - Прв. 11 и вход 15 "Регистр-2" являются соответственно входом "Прерывание τэ " и входом "Ти" БОЧ 1 и соединены с соответствующими выходами РИ 5. N частотных выходов БОЧ 1 являются выходами соответствующих N синтезаторов частот 1.1-1, 1.1-2, ..., 1.1-N. Управляющий вход каждого из N синтезаторов 1.1 соединен с входом соответствующего буферного регистра 1.2, входы которых объединены между собой и подключены к адресно-информационной шине ДПКС 1.4. Опорные входы всех синтезаторов подключены к выходу ОГ 1.5. Входы "Запись" каждого из буферных регистров 1.2-1, ..., 1.2-N подключены соответственно к выходам 1-1,...,1-N блока формирования импульсов записи 1.3, информационные входы которого подключены к адресно-информационной шине ДПКС 1.4. Вход ИСА и вход "Запись" блока формирования импульсов записи (БФИЗ) 1.3 соединены с одноименными выходами ДПКС 1.4, а вход ДПКС 1.4 "Разрешение" соединен с одноименным выходом блока формирования импульсов записи 1.3.

Схемы и принципы работы синтезаторов частот известны и описаны, например, в книге "Цифровые радиоприемные системы: Справочник /М.И.Жодзишский и др. / Под ред. М.И.Жодзишского.-М.: Радио и связь, 1990, с. 72, рис. 37. В частном случае синтезаторы частот 1.1-1,...,1.1-N могут быть реализованы, например, на синтезаторах, изготовленных в Российском институте мощного радиостроения, децимальный номер схемы ЕР.2.329.008.ЭЗ.

Буферные регистры 1.2-1,...,1.2-N являются регистрами хранения информации, которые рассматриваются во многих источниках. Например, в справочнике "Применение интегральных микросхем в электронной вычислительной технике". М. : Радио и связь, 1987. Подобные регистры описаны на с. 109, рис. 5.44. В частности, буферные регистры 1.2,...,1.2-N можно реализовать на D-триггерах. Описание D-триггеров приводится в книге Шило В.Л. Популярные цифровые микросхемы. Справочник. М.: Радио и связь, 1987, с. 72-73. В частности можно использовать D-триггеры, выполненные на микросхемах 133ТМ2.

Блок формирования импульсов записи (БФИЗ) 1.3 предназначен для управления процессом записи кодовых слов в буферные регистры 1.2-1,...,1.2-N.

На фиг. 10 изображена схема БФИЗ 1.3, которая содержит дешифратор 1.3.1 для дешифрирования адреса, двухвходовой элемент И 1.3.2, элемент задержки 1.3.3 и N D-триггеров 1.3.4 с 1-го по N-й. Три информационных входа дешифратора 12.3.1 подключены к трем соответствующим разрядам ШАИ ДПКС 1.4, четвертый информационный вход является входом ИСА. Шесть разрядов ШАИ (при N-6) подключены к D-входам каждого из D-триггеров 1.3.4. Вход "Запись" блока формирования импульсов записи 1.3 соединен с первым входом элемента И 1.3.2 и входом элемента задержки 1.3.3, выход которого является выходом "Разрешение". Выходы всех D-триггеров 1.3.4 образуют выходы 1-1,1-2,...,1-N блока формирования импульсов записи 1.3. Выход дешифратора 1.3.1 соединен с вторым входом элемента И 1.3.2, выход которого подключен к объединенным вместе счетным входам всех D-триггеров 1.3.4. Входы S и R всех D-триггеров объединены и на них подан уровень логической "1".

Дешифратор 1.3.1 может быть реализован на микросхеме 134ИД6, которая описана в книге Шилов В.Л. Популярные цифровые микросхемы. Справочник. М.: Радио и связь, 1987, с. 261-263. D-триггерные схемы рассматриваются там же на с. 72-73. В частности, можно использовать D-триггеры, выполненные на микросхемах 1333ТМ2.

ДПКС 1.4 предназначен для выработки кодовых слов управления частотами синтезаторов 1-1,1-2,...,1-N, а также сигналов управления работой БФИЗ 1.3.

ДПКС 1.4 может быть реализован на ЭВМ, например на микроконтроллере МК-31, который построен на базе однокристальной микроЭВМ К586ВЕ1 в Российском институте мощного радиостроения.

Блок-схема программы ДПКС приведена на фиг. 9.

Преобразователи частоты 2.1 в каждом тракте обработки выполнены по двойной балансовой схеме и описаны в книге Гоноровского Н.С. Радиотехнические цепи и сигналы, ч. II. М.: Сов. Радио, 1967, с. 149, рис. 4.19.

Полосовые фильтры 2.2. - электромеханические фильтры типа ФЭМ 5 - 041 - 301.63 - 0,26C - 3B.

Детекторы огибающей (ДО) 2.3 - синхронные детекторы огибающей с цифровым выходом, выполненные по авторскому свидетельству СССР N 1.706.005.

Блок накопителей 3 предназначен для хранения отсчетов, взятых на интервале наблюдения.

На фиг. 11 показана схема блока накопителей 3, которая содержит N одинаковых блоков памяти 3.1,...,3.N. N информационных входов блока накопителей 3 являются информационными входами N блоков памяти 3.1,...,3,N. N входов "Запись" и N входов "Разрешение" являются соответствующими входами каждого из N блоков памяти. Вход "Импульс сопровождения адреса" (ИСА) блока накопителей 3 является общим для всех блоков памяти 3.1,...,3.N. Информационные выходы всех блоков памяти 3.1,...,3.N подключены к общей адресно-информационной шине (ШАИ), являющейся выходом блока накопителей 3. Кроме того, каждый из N блоков памяти 3.1,...,3.N имеет выход "Готовность данных". Эти выходы образуют соответствующую группу из N выходов блока накопителей 3.

Блок памяти 3.1 предназначен для хранения отсчетов одного тракта обработки 2i.

На фиг. 12 представлена схема блока памяти 3.1, которая содержит ОЗУ 3.1.1, четыре двунаправленных шинных усилителя (ДНШУ) 3.1.2-3.1.5, три инвертора 3.1.7, 3.1.8 и 3.1.10, счетчик до "30" 3.1.9, два дешифратора 3.1.6 и 3.1.11, регистр хранения 3.1.12, элемент задержки 3.1.13, дифференцирующую цепь 3.1.14 и RS-триггер 3.1.15. Информационный вход блока памяти 3.1 является информационным входом ДНШУ 3.1.2. Вход записи блока памяти 3.1 соединен с входом инвертора 3.1.7 и счетным входом счетчика до "30" 3.1.9, вход "Разрешение" соединен с входом инвертора 3.1.8 и входом дифференцирующей цепи 3.1.14, вход ИСА является первым входом дешифратора 3.1.11. Адресно-информационная шина для обмена информацией между блоком 3 накопителей и блоком 4 выбора максимума сигнала соединена с выходом ДНШУ 3.1.3, входом регистра хранения 3.1.12 и вторым входом дешифратора 3.1.11. Выход "Готовность данных" является выходом элемента задержки 3.1.13 и соединен, кроме того, с управляющим входом ДНШУ 3.1.3. Выход ДНШУ 3.1.2 соединен с входом данных ОЗУ 3.1.1, выход данных которого соединен с входом ДНШУ 3.1.3. Выход инвертора 3.1.7 подключен к входу запись/считывание ОЗУ 3.1.1 и управляющим входам ДНШУ 3.1.2 и 3.1.4. Адресные входы ОЗУ 3.1.1 соединены с выходами ДНШУ 3.1.4 и 3.1.5. Выходы счетчика до "30" 3.1.9 соединены с входами ДНШУ 3.1.4 и дешифратора 3.1.6, выход которого подключен через инвертор 3.1.10 к выходу обнуления счетчика до "30" 3.1.9 и к R-входу RS-триггера 3.1.15 непосредственно. Выход RS-триггера 3.1.15 соединен с входом "Разрешение счета" счетчика до "30" 3.1.9, S-вход RS-триггера 3.1.15 соединен с выходом дифференцирующей цепи 3.1.14. Управляющий вход ДНШУ 3.1.5 соединен с выходом инвертора 3.1.8, а информационные входы ДНШУ 3.1.5 соединены с выходами регистра хранения 3.1.12, вход записи которого соединен с выходом дешифратора 3.1.11 и входом элемента задержки 3.21.13.

На фиг. 13 показана схема ДНШУ, который служит для подключения (отключения) шины данных или адресов ОЗУ 3.1.1.

Двунаправленные шинные усилители описаны в книге Шило В.Л. Популярные цифровые микросхемы. Справочник. М. : Радио и связь, 1987, с. 34. В частности, ДНШУ 3.1.2-3.1.5 могут быть выполнены на микросхемах К 155 АП 6.

ОЗУ 3.1.1 предназначено для запоминания и хранения отсчетов огибающей напряжения, взятых в тракте обработки на интервале наблюдения.

Схемы построения ОЗУ известны и описаны, см., например, в книге Большие интегральные схемы запоминающих устройств. Справочник /А.Ю.Гордонов и др., под ред. А.Ю. Гордонова и Ю.Н.Дьяконова. М.: Радио и связь, 1990, с. 80-85. В частности, как показано на фиг. 6.3, ОЗУ 3.1.1 может быть реализовано на микросхемах 564РУ2.

Регистр хранения адреса отсчета 3.1.12 выполнен по схеме, изображенной на рис. 5.44 с. 109 в книге Применение интегральных микросхем в электронной вычислительной технике, под ред. Б. Н. Файзулаева и Б.В. Тарабарина. М.: Радио и связь, 1987.

Дешифратор 3.1.6 выполнен по схеме, описанной в книге Шило В.Л. Популярные цифровые микросхемы. М.: Радио и Связь, 1987, с 137, рис. 1.98. В этой же книге на с. 74 рис. 1.53 описан RS-триггер.

Схема дифференцирования 3.1.14 описана на с. 146, рис. 11.16 в книге Титце У. и Шенк К. Полупроводниковая схемотехника. М.: Мир, 1982.

Схема задержки построена на RS-цепи.

На фиг. 15 показан БВМС 4, предназначенный для непараметрической обработки отсчетов, накопленных на интервале наблюдения, и формирования сигналов управления процессом поиска, а также для принятия решения об обнаружении сигнала с ППРЧ и выдачи управления для устранения рассогласования.

Блок выбора максимума сигнала 4 включает микроконтроллер МК-31 4.1. и N-входовой элемент ИЛИ 4.2, выход которого подключен к входу "Ответ" МК-31 4.1. Входы элемента ИЛИ 4.2 являются входами "Готовность данных" с 1 по N блока выбора максимума сигнала 4. Адресно-информационная шина БВМС 4 является адресно-информационной шиной МК-31. 4.1.

В БВМС 4 микроконтроллер МК-31 4.1 предназначен для обработки информации и управления периферийным оборудованием в реальном масштабе времени. Как было указано выше, он выполнен на базе однокристальной микроЭВМ К586ВЕ1 в Российском институте мощного радиостроения.

Блок-схема программы работы МК-31 4.1 представлена на фиг. 16-18.

Заявляемое устройство работает следующим образом.

Для осуществления синхронизации и последующей передачи информации использован сигнал в виде частотно-временной матрицы с программно-перестраиваемой рабочей частотой. При таком сигнале на отрезке времени, равном длительности каждой информационной посылки Tи, излучается N элементарных импульсов, следующих друг за другом (см. фиг. 6а). Длительность каждого элементарного импульса τэ в N раз меньше длительности информационной посылки Tи, τэ= Tω/N. Каждый элементарный импульс излучается на новой несущей частоте. Номиналы несущих частот при формировании сигнала назначаются с помощью датчика, вырабатывающего перед началом временного интервала Tи N кодовых слов, каждому из которых ставится в соответствие значение несущей частоты. Информационные признаки закладываются в порядок излучения назначенных для данной информационной посылки n частот. Например, последовательное излучение частот f1, f2,..., fi,..., fN соответствует передаче информационной единицы, при излучении информационного нуля последовательность меняется: fi,fi+1,..., fN, f1, f2,..., fi-1.

На приеме формируют N гетеродинирующих напряжений, подводимых к N смесителям. Для правильной демодуляции сигнала необходимо строгое соответствие частот гетеродинирующих сигналов с частотами импульсов принимаемого сигнала.

Частоты гетеродинирующих напряжений устанавливаются в соответствии с кодовыми словами, вырабатываемыми датчиком псевдослучайных кодовых слов, аналогичным датчику на стороне передачи.

Синхронизация датчиков осуществляется с использованием единого времени, устанавливаемого до начала обмена информацией. Для более точной синхронизации со стороны передающей станции в течение некоторого времени передается последовательность сигналов, например последовательность, соответствующая информационным нулям или информационным единицам, или иная, известная заранее на стороне приема. По этому сигналу осуществляется поиск синхронного положения в приемном устройстве.

На передаче смена несущих частот сигнала синхронизации, осуществляемая в соответствии с кодовыми словами от датчика, производится в моменты времени, которые согласованы с временными метками единого времени и с информационными посылками, образующими синхросигнал. Частоты для передачи любой информационной посылки выбираются датчиком с равной вероятностью для каждой частоты, и их появление не зависит от вида информационной последовательности. Поэтому сигнал, используемый в устройстве, имеет спектральные характеристики, не зависящие от вида информации. Это позволяет, не ухудшая скрытности системы, создать предпочтительные условия для режима синхронизации, а именно перед обменом информацией всегда передавать известную на приеме последовательность, например последовательность информационных единиц.

Точность синхронизации задается допустимым асинхронизмом, при котором еще возможна демодуляция сигнала с требуемой достоверностью, и зависит от длительности элемента сигнала. В заявляемом устройстве при длительности информационной посылки Tи=20 мс число частотных составляющих N матрицы сигнала выбрано равным 6, длительность элемента сигнала τэ равна при этом 3,3 мс. Допустимый асинхронизм в этом случае принят примерно 0,5 мс, что составляет около 15% от длительности элемента сигнала (см., например, Свириденко С.С. Основы синхронизации при приеме дискретных сигналов.-М.: Связь, 1974, с. 70, рис. 4.8). Наличие такого асинхронизма не снижало помехоустойчивость системы передачи сигналами описанной выше структуры в радиоканале КВ-диапазона во всех случаях, когда вероятность ошибки задавалась не ниже 10-2.

В заявляемом устройстве в процессе синхронизации осуществляется последовательно-параллельный поиск сигнала. На каждом этапе исследуется не одна, а несколько гипотез о синхронном положении. Обработку сразу нескольких гипотез уменьшает время синхронизации, но ужесточает требования к быстродействию и сложности устройства. Число обрабатываемых на одном этапе гипотез выбирается путем компромисса и в нашем случае составляет 30 гипотез.

Когда передаваемый сигнал состоит из последовательности известных на приеме информационных посылок (например, в нашем случае из последовательности "единиц"), принятие гипотезы о положении начала информационной посылки однозначно определяется временным положением импульсного отклика на выходе фильтра в каждом канале.

На любом этапе поиска для каждой гипотезы (из группы в 30 гипотез, исследуемых на этом этапе) вычисляется функционал как сумма модифицированных отсчетов, взятых на интервале нескольких информационных посылок, например К. Отсчеты берут в моменты ожидаемого отклика фильтра в каждом из каналов. Полученную в результате сумму сравнивают с некоторым порогом. Гипотеза, при которой происходит превышение порога, принимается в качестве правильной, а сигнал считывается обнаруженным. После этого сравнивают суммы превышения "истинных" отсчетов над средним, накопление сумм превышения отсчетов над средним производится параллельно с накоплением сумм модифицированных отсчетов. Синхронным положением принимается то, которое связано с гипотезой, соответствующей наибольшей сумме превышений отсчетов.

Число посылок, в течение которых суммируются отсчеты и которое определяет длительность этапа поиска tэтапа, а также значение порога выбраны с учетом задаваемых вероятностей ложной тревоги и пропуска цели и минимальным средним временем, отводимым для обнаружения сигнала. На практике в диапазоне коротких волн это число соответствует 10-15 информационным посылкам.

Если на этапе поиска ни одна из исследуемых 340 гипотез не была принята, сдвигают положение временных последовательностей на один шаг и приступают к рассмотрению группы новых гипотез. При выборе шага учитывают величину интервала, который может быть исследован на одном этапе, и требования к точности определения синхронного состояния.

В заявляемом устройстве, как было сказано выше, сдвиг между соседними положениями синхронизации Δτac выбран 0,5 мс - это величина неустранимого асинхронизма.

При определении интервала, который может быть исследован на длительности каждой информационной посылки, необходимо учитывать временные затраты на нарастание напряжения сигнала в канальном фильтре.

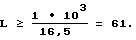

В заявляемом устройстве на интервале посылки Tи=20 мс время наблюдения Tнабл. (время для взятия отсчетов) составляет 16,5 мс, остальное время Tи-Tнабл.= Tнараст.(20 мс - 16,5 мс) отведено для нарастания напряжения на фильтре. Время, отведенное для нарастания напряжения на фильтре, используется для обработки результатов наблюдения на предыдущей посылке. Количество гипотез, которое исследуется на интервале посылки, составляет

Tнабл./Δτac= 16,5/0,5 ≈ 30.

Очевидно, что величина шага после окончания этапа безрезультатного поиска составляет 16,5 мс. При обнаружении сигнала величина требуемого сдвига распределителя зависит от номера гипотезы (от 1 до 30), для которой получена максимальная сумма "истинных" отсчетов и лежит в пределах 0,5 - 16,5 мс.

После включения питания устанавливают единое время вручную или автоматически, если это предусмотрено той системой, куда входит заявляемое устройство. Показания времени вводятся в блок 1 опорных частот через цепи ввода-времени датчика псевдослучайных кодовых слов 1.4 (см. фиг. 7), по сигналу "Установка" датчик псевдослучайных кодовых слов 1.4 устанавливается в положение, соответствующее показаниям введенного времени. Одновременно все узлы устройства, требующие обнуления, ставятся в исходное положение (распределитель импульсов 5, управляемый делитель 6).

Режим поиска сигнала устанавливается по сигналу "Синхронизация", который может быть сформирован либо автоматически в некотором внешнем устройстве, либо по воле оператора.

Работа устройства поясняется временными диаграммами различных сигналов, которые представлены на фиг. 6 и 7.

На диаграммах показаны сигналы при синхронном положении устройства.

На фиг. 6 представлен порядок следования элементов сигнала на стороне передачи при числе элементов N, равном шести на длительности информационной посылки Tи. На фиг. 6b изображены отклики фильтров 2.2 в трактах обработки 2ш. На фиг. 6c показаны моменты смены частот гетеродинирующих напряжений для трактов обработки: в эти моменты производится запись в буферные регистры 1.2-i нового кодового слова, управляющего частотой перестраиваемого синтезатора частоты 1.1-i. На фиг. 6d показаны сигналы, управляющие работой блока накопителей 3, при этом поясняется расположение интервалов наблюдения Tнабл.и обработки Tобраб. для каждого из каналов обработки. На фиг. 7a представлены импульсы, управляющие работой детекторов 2.3i, по этим импульсам запускается работа ДО 2.3i. В промежутках между импульсами "Запуск" осуществляется запись сигналов с выхода детектора 2.3i в блок памяти 3.i блока накопителей 3. Фиг 7b поясняет, как расположены на временной оси сигналы для управления процессом считывания отсчетов из блока накопителей 3 в блок выбора максимума сигнала 4.

На фиг. 7c показаны метки времени: Tи=20 мс и τэ= 3,3 мc.

Первая метка τэ на интервале Tи задержана относительно метки Tи на tз≈10-20 мкс (см. фиг. 2 элемент задержки 5.6) во избежание совпадения их при обработке программами микроконтроллеров ДПКС 1.4, а также БВМС 4.

Режим поиска включается по команде "Синхронизация", при этом в управляемом делителе 6 происходят следующие процессы (см. фиг. 4 и 5). RS-триггер 6.24 устанавливается в положение, при котором к работе подготовлена ячейка И 6.9 для прохождения сигнала "Конец шага" от блока выбора максимума сигнала 4. Кроме того, по переднему фронту напряжения на выходе RS-триггера 6.24 (через схему дифференцирования 6.19) устанавливаются в исходное положение счетчик шагов 6.20 и таймер 6.16 (через элемент ИЛИ 6.21).

При заполнении счетчика шагов 6.20 из исходного положения первый раз подсчет шагов производится до половинного объема счетчика L/2 (см. фиг.5).Всякое последующее (кроме первого после прихода команды "Синхронизация") заполнение счетчика шагов 6.20 происходит до полного его объема L, где L -число шагов, которое может быть сделано при просмотре всей зоны неопределенности. При точности установки времени ± 0,5 с необходимо просматривать зону неопределенности величиной в 1 с.

Интервал наблюдения на одном шаге составляет 16,5 мс, этот интервал исследуется в течение 10 информационных посылок, после чего делается "шаг" и изучается следующий интервал 16,5 мс. При просмотре всей зоны неопределенности шагов составляет L .

.

Выбираем ближайшее четное число 62, тогда L2/2=31. Процесс поиска начинается всегда в сторону ускорения и устранения возможного отставания работы распределителя импульсов 5. Для этого в управляемом делителе 6 ТВ-триггер 6.13, от положения которого зависит ускорение или замедление распределителя импульсов 5 после каждого шага, перед началом поиска сигналом "Установка" ставится в соответствующее положение.

Итак, при начале поиска осуществляется 31 шаг (L/2) со сдвигом распределителя импульсов 5 в сторону ускорения его работы, после чего счетчик шагов 6.20 обнуляется (см. фиг.5) по цепи: выход L/2 счетчика до L/2 6.20.4, элементы И 6.20.5, ИЛИ 6.20.6, ИЛИ 6.20.7. Одновременно сигналом с выхода счетчика шагов 6.20 (см. фиг.4) ТВ-триггер 6.13 перебрасывается в иное положение, снимая управление с цепей, обеспечивающих ускорение распределителя импульсов 5. Последующие сдвиги будут осуществляться путем замедления распределителя импульсов 5. Кроме того, в счетчике шагов 6.20 с задержкой, необходимой для завершения обнуления счетчиков 6.20.1, 6.20.4 (см. элемент задержки 6.20.3 < 1 мкс), срабатывает RS-триггер 6.20.2, подготавливает схему счетчика шагов к режиму счета до L. Причем, начиная со второго заполнения счетчика шагов 6.20, подсчет выполняется до L=62, после чего вновь меняется направление сдвигов распределителя импульсов 5. Так что часть устройства работает до момента обнаружения сигнала синхронизации.

Итак, устройство приступила к поиску сигнала. На выходах БОЧ 1 происходит поочередная смена частот гетеродинирующих напряжений. На каждом из выходов частота остается неизменной в течение длительности информационной посылки Ти, момента же смены частоты сдвинуты относительно друг друга на время τэ, равное длительности элемента сигнала, см. диаграмму на фиг. 6с.

Номиналы частот гетеродинирующих напряжений назначаются в соответствии с программой ДПКС 1,4 (см. фиг.9).

Программа ДПКС 1.4 начинается с восприятия информации о текущем времени, которая поступает через цепи ввода-вывода микроконтроллера (МК-31) по сигналу "Установка". После получения сведений о текущем времени осуществляется пересчет состояния регистров М-последовательности (организованных программно) в соответствии с текущим временем. После чего программа готова к восприятию меток Ти. При поступлении метки Ти осуществляется запись N кодов опорных частот для текущего интервала Ти в рабочие регистры процессора (в нашем случае N=6, т.е. записывается шесть кодов опорных частот (шесть кодов слов). Затем ячейки памяти, в которых организован подсчет прерываний τэ (счет до N= 6), обнуляются и разрешаются прерывания по меткам τэ (Прв.11 в МК-31). Ожидая прихода прерывания τэ , машина выполняет действия по вычислению нового состояния регистров M-последовательности (для последующего интервала Ти и формированию в соответствии с этим новым состоянием новых кодовых слов, соответствующих значениям опорных частот на следующем интервале Ти. При поступлении прерывания по метке τэ увеличивается на "1" содержимое ячейки памяти, где подсчитываются прерывания τэ . Затем выдается на адресно-информационную шину адрес, соответствующий номеру (в программе назван М) поступившего прерывания τэ . Выдается также импульс сопровождения адреса (ИСА) и сигнал "Запись" от ДПКС 1.4, которые поступают на блок формирования импульсов записи 1.3. В ответ на эти сигналы в блоке формирования импульсов записи 1.3, к которому в данный момент были адресованы перечисленные выше сигналы, вырабатывается ответный сигнал, поступающий на вход "Разрешение" ДПКС 1.4. Сигнал "Разрешение" формируется на основе сигнала "Запись" путем задержки его на время < 1 мкс, необходимое для срабатывания узлов в блоке формирования импульсов записи 1.3 (см. элемент задержки 1.3.3 на фиг.10). После получения этого сигнала ДПКС 1.4 выдает на ШАИ кодовое слово из рабочего регистра, номер которого соответствует номеру М прерывания τэ , с тем чтобы слово было записано затем в соответствующий буферный регистр 1.2.1 блока опорных частот 1.

Затем в программе проверяется прошло ли разрешенное количество прерываний τэ (проверяется равно ли M=N, где N=6). Если нет, программа возвращается к вычислению нового состояния регистров M-последовательности. Разумеется, время, необходимое для этих вычислений, должно быть меньше длительности Ти. Если число прерываний τэ достигло шести (т.е. выполняется равенство M=N), то программа запрещает эти прерывания и возвращается к ожиданию метки Ти. Далее все повторяется.

В каждом тракте обработки 2 i заявляемого устройства входной сигнал после преобразования частоты в преобразователе 2.1 (на основе поступающего в данный момент гетеродинирующего напряжения) проходит узкополосный фильтр 2.2 и детектируется в цифровом детекторе огибающей 2.3.

Значения огибающей сигнала в каждом тракте обработки 21,...,2N в виде цифрового кода с выхода детектора 2.3 поступают на информационный вход блока накопителей 3. Моменты формирования цифровых отсчетов задаются сигналами "Запуск" детектора огибающей 2.3. Вырабатываются сигналы "Запуск" в распределителе импульсов 5. Диаграммы этих сигналов для каждого из трактов обработки 21,...2N представлены на фиг.7a). За время информационной посылки (т. е. на длительности существования гетеродинирующего напряжения некоторой одной частоты) берется 30 отсчетов - столько, сколько рассматривается гипотез на интервале наблюдения Tнабл.

На интервале наблюдения Tнабл. в блоках памяти 3.1,...,3.N соответственно для каждого тракта обработки 21,...2N оказываются записанными 30 отсчетов - по числу импульсов запуска детектора 2.3.

Подсчет записываемых цифровых значений обрабатываемого сигнала и формирование на основе счета адреса записи осуществляется в счетчике 3.1.9 (см. фиг. 12). Разрешается счет по сигналу от RS-триггера 3.1.15, который срабатывает от импульса на выходе дифференцирующей схемы 3.1.14 по переднему фронту первого импульса запуска детектора 2.3 (см. диаграмму на фиг.7a)).

Формирование цифрового значения отсчета в ДО 2.3 начинается по переднему фронту каждого импульса "Запуск". Ширина импульсов "Запуск" от распределителя импульсов 5 установлена большей, чем время, требуемое для формирования цифрового значения в ДО 2.3.

В промежутках между импульсами "Запуск" осуществляется запись цифровых отсчетов в ОЗУ 3.1.1. В эти моменты времени цифровые выходы детекторов огибающей 2.3 через двунаправленный шинный усилитель 3.1.2 подключаются к выходной шине данных ОЗУ 3.1.1. В тот же момент времени к адресному входу ОЗУ 3.1.1 через ДНШУ 3.1.4 подключается выход счетчика 3.1.9, формирующего адрес записи. После прохождения 30 отсчетов счетчик 3.1.9 останавливается и обнуляется. Разрешение счета снимается, поскольку RS-триггер 3.1.15 переключается сигналом, поступающим с выхода дешифратора на тридцать 3.1.6.

По окончании интервала наблюдения Nнабл. на интервале обработки Tобраб. отсчеты, записанные в блоках памяти 3.1 - 3.N, считываются в блок выбора максимума сигнала 4 поочередно, начиная с тракта обработки 21 и заканчивая трактом обработки 2N.

На фиг.16 приведена блок-схема алгоритма обработки принимаемых сигналов. Программа обработки отсчетов начинается по прерыванию "Начало шага", поступающему на вход Прв. 9 микроконтроллера МК-31 4.1 в блок выбора максимума сигнала 4 от управляемого делителя 6. При поступлении прерывания "Начало шага" обнуляются ячейки ОЗУ микроконтроллера, в которых организован подсчет циклов обработки; подсчет числа каналов, обрабатываемых на одном интервале Tи (счет до N=6); подсчет K числа интервалов Tи, необходимых для принятия решения о наличии (или отсутствии) сигнала при K=10. После этого разрешается обработка прерываний по импульсам Tи и  .

.

В начале каждого интервала обработки производится считывание отсчетов из блока накопителей 3, при этом процессом считывания полностью управляет микроконтроллер МК-31 4.1. По прерыванию Прв.10  , которое означает начало интервала обработки, микроконтроллер вырабатывает адрес подлежащего считыванию отсчета: 3 разряда адресного слова содержит номер блока памяти 3.1 в блоке накопителей 3, к которому обращается машина, остальные разряды адресного слова содержат номер отсчета (один из 30-ти). В блоке памяти 3.1 три разряда ШАИ, с помощью которых указывается номер блока памяти, подключены к второму входу дешифратора 3.1.11 (см. фиг.12).

, которое означает начало интервала обработки, микроконтроллер вырабатывает адрес подлежащего считыванию отсчета: 3 разряда адресного слова содержит номер блока памяти 3.1 в блоке накопителей 3, к которому обращается машина, остальные разряды адресного слова содержат номер отсчета (один из 30-ти). В блоке памяти 3.1 три разряда ШАИ, с помощью которых указывается номер блока памяти, подключены к второму входу дешифратора 3.1.11 (см. фиг.12).

Если номер данного блока памяти 3.1 соответствует коду из этих 3-х разрядов, то на выходе дешифратора 3.1.11 формируется импульс, по которому в регистр хранения 3.1.12 записывается содержимое адресного слова, определяющее номер отсчета и являющееся адресом для считывания значения отсчета из ОЗУ 3.1.1.

В интервале обработки открыты двунаправленные усилители ДНШУ 3.1.3 и 3.1.5, поэтому адрес считываемого отсчета оказывается подключенным к адресному входу ОЗУ 3.1.1. Выход данных ОЗУ 3.1.1 подключается кратковременно к адресно-информационным шинам по импульсу "Готовность данных", формируемому из сигнала на выходе дешифратора 3.1.11 с небольшой задержкой t, необходимой для срабатывания регистра 3.1.12. Считывание всех 30 отсчетов занимает около 60 мкс, т.к. осуществляется со скоростью работы микроконтроллера.

В соответствии с программой обработки для группы из 30 отсчетов, принадлежащих данному тракту обработки, вычисляется среднее. Затем отсчеты модифицируются на две категории. Каждый из 30-ти отсчетов сравнивается со средним значением, полученным для данного канала за интервал наблюдения Tнабл.. Если отсчет больше среднего, то ему становится в соответствие две модификации отсчета: первая - равная "единица", другая - равная превышению этого отсчета над средним.

Отсчет, модифицированный в единицу, добавляется к той сумме отсчетов первой модификации, которая имеет индекс, соответствующий номеру данного отсчета. Отсчет, модифицированный в превышение над средним, добавляется к сумме, накапливающей превышения над средним и имеющей соответствующий индекс. Такая процедура выполняется для каждого из 30 отсчетов в данном канале. По следующему прерыванию Прв.10 (τэ) микроконтроллер МК-31 4.1 приступает к аналогичной обработке 30 отсчетов, хранящихся в следующем блоке памяти 3.(i=1).

После добавления к соответствующим суммам всех отсчетов в 30 ячейках ОЗУ ЭВМ оказываются накопленными суммы соответственно первых, вторых, ... , тридцатых отсчетов первой модификации для всех 6-ти трактов (каналов) обработки - обозначим их Σ

В других 30 ячейках накоплены суммы отсчетов второй модификации - Σ

После следующего интервала наблюдения каждая из сумм будет увеличена путем добавления соответствующих отсчетов, если они превысили значение среднего. Таким образом, максимальное значение отсчетов, добавляемых к сумме после обработки отсчетов на интервале Tи и составляет 6 (по числу каналов обработки) или меньше, если были отсчеты ниже или равные среднему.

По прошествии 10 интервалов Tи (в нашем случае K=10) в каждой сумме может быть накоплено максимум 60 слагаемых. По окончании этого накопления, т.е. по достижению K числа 10, каждая из 30 сумм отсчетов первой модификации сравнивается с установленным порогом. Если порог не достигнут ни в одной из сумм, то в блоке 4 выбора максимума сигнала формируется сигнал "Конец шага", он выдается через цепи ввода-вывода МК-31 4.1 на вход управляемого делителя 6, после чего машина возвращается к ожиданию прерывания по сигналу "Начало шага".

В управляемом делителе 6 (см. фиг.4) сигнал "Конец шага" проходит ячейку И 6.9, во-первых, увеличивает на единицу состояние счетчика шагов 6.20, во-вторых, сбрасывает в "0" (через элемент ИЛИ 6.21) таймер 6.16. При этом сбрасывается и выходной сигнал дешифратора 6.17, что приводит к закрытию ячейки И 6.7 и, напротив, через инвертор 6.15 разрешается работа ячейки И 6.8, а также подсчет импульсов, поступающих на счетный вход таймера 6.16. Если в данный момент триггер 6.13 стоит в положении, когда на его выходе, соединенном с входом ячейки И 6.8, есть единица, то напряжение с выхода И 6.8 открывает прохождение импульсов "Верхняя частота" (в нашем случае 3 кГц) через ячейку И 6.6, то есть увеличивается частота импульсов, проходящих к распределителю импульсов 5 через ячейку ИЛИ 6.22. В нормальном режиме через ячейку ИЛИ 6.22 проходят импульсы от И 6.7 с выхода "Нижняя частота" (в нашем случае 1,5 кГц) делителя частоты 6.4. Таймер 6.16 осуществляет подсчет такого числа импульсов, которое обеспечивает сдвиг фазы распределителя импульсов 5 на 16,5 мс, именно на такое число настроен дешифратор 6.17. Как только дешифратор 6.17 срабатывает, снимается разрешающее напряжение для прохождения счетных импульсов на таймер 6.16, открывается ячейка И 6.7 для прохождения через нее импульсов "Нижняя частота" (1,5 кГц) нормальной работы распределителя 5 и закрываются ячейки И 6.8 и И 6.6, что прекращает поступление импульсов "Верхняя частота" (3 кГц) к ячейке ИЛИ 6.22. Кроме того, на выходе элемента задержка 6,23 (задержка необходима для срабатывания перечисленных выше логических элементов и составляет < 1 мкс) формируется сигнал "Начало шага". В результате распределитель импульсов 5 продолжает работу с обычной скоростью, будучи сдвинутым на 16,5 мс вперед.

Если в момент прихода сигнала "Конец шага" триггер 6.13 стоял в положении, когда на его плече, управляющем ячейкой И 6.8, нулевое напряжение, то в этом случае в течение времени работы таймера 6.16 к распределителю импульсов 5 не проходят никакие счетные импульсы. В результате распределитель импульсов будет задержан (сдвинут "назад") на 16,5 мс. Как говорилось выше, сдвиги вперед (или назад) повторяются после каждого прихода сигнала "Конец шага", пока не будет пройдена вся зона неопределенности, а счетчик шагов 6.20 досчитает до L. После этого сигналом с выхода счетчика шагов 6.20 триггер 6.13 перебрасывается в иное положение, а следовательно, будет изменено направление сдвига при последующих L шагах и т.д.

Если на каком-то из шагов одной из сумм, накапливающих отсчеты первой модификации, будет достигнут порог (см. блок-схему алгоритма на фиг.16), то программа переходит к просмотру сумм отсчетов второй модификации. Из этих сумм выбирается максимальная, а положение отсчетов, образовавших эту сумму, принимается за синхронное. Номер этой суммы запоминается.

Через цепи ввода-вывода микроконтроллера МК-31 4.1 выдаются сигналы "Cинхронизация есть", а также разряды кодового слова, содержащего сведения о номере суммы (номере гипотезы), положение которой принято синхронным.

Программа обнаружения и синхронизации на этом заканчивается, машина может приступать к исполнению других задач, например, программы демодуляции.

Сигналы "Синхронизации есть" и разряды "Номер гипотезы" поступают на соответствующие входы управляемого делителя 6 (см. фиг.4). В результате запрещается работа узлов управляемого делителя 6, обеспечивающих описанные выше сдвиги распределителя 5 при шагах по зоне неопределенности, так как сигналом "Синхронизация есть" RS-триггер 6.24 устанавливается в положение, при котором закрывается ячейка И 6,9 и запрещается прохождение к схеме импульсов "Конец шага". Кроме того, сигнал "Синхронизации есть" воздействует на вход разрешения записи внешней информации в реверсивный счетчик 6.11. К информационным же входам этого счетчика одновременно поступают все разряды кода с номером гипотезы синхронного положения. В результате номер гипотезы заносится в реверсивный счетчик 6.11. Подключенный к выходу реверсивного счетчика 6.11 дешифратор 6.12 настроен на нулевое положение счетчика. Как только в счетчике 6.11 устанавливается номер гипотезы синхронного положения, дешифратор 6.12 снимает свое выходное напряжение. Это приводит к тому, что, во-первых, закрывается ячейка И 6.5, а, во-вторых, через элемент НЕ 6.14 разрешается прохождение счетных импульсов к счетчику-делителю 6.10. В течение времени, пока закрыта ячейка И 6.5, не проходят импульсы, обеспечивающие работу распределителя импульсов 5, в результате на это время распределитель импульсов задерживается, а все вырабатываемые им последовательности импульсов сдвигаются в сторону отстаивания. Величина сдвига точно соответствует номеру гипотезы о синхронном положении. Это соответствие обеспечивается подбором частоты счетных импульсов и коэффициентом деления счетчика-делителя 6.10. Импульсы с выхода счетчика-делителя 6.10 поступают на счетный вход реверсивного счетчика 6.11. Как только положение реверсивного счетчика 6.11 достигнет нуля, срабатывает дешифратор 6.12, открывается ячейка И 6.5 и снова восстанавливается нормальное прохождение импульсов к распределителю 5. Одновременно снимается разрешение работы счетчика-делителя 6.10. Все временные последовательности устройства оказываются установленными в синхронное положение.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИНХРОННЫЙ ДЕТЕКТОР | 1997 |

|

RU2124804C1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ОШИБОК | 1998 |

|

RU2127943C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА СИГНАЛОВ РАДИОСТАНЦИЙ | 1998 |

|

RU2132111C1 |

| ЧАСТОТНО-АДАПТИВНАЯ РАДИОЛИНИЯ ДЛЯ ПЕРЕДАЧИ СРЕДНЕСКОРОСТНЫХ ПОТОКОВ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1998 |

|

RU2142200C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА РАДИОСТАНЦИЙ | 1994 |

|

RU2099868C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2116670C1 |

| СПОСОБ ОБСЛУЖИВАНИЯ ЗАПРОСОВ ПОЛЬЗОВАТЕЛЕЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ (ВАРИАНТЫ) | 1998 |

|

RU2140666C1 |

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ В РАДИОЛИНИИ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧИХ ЧАСТОТ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1994 |

|

RU2097923C1 |

| УСТРОЙСТВО ДИАГНОСТИКИ СОСТОЯНИЯ АППАРАТУРЫ СВЯЗИ | 1997 |

|

RU2124266C1 |

| МНОГОКАНАЛЬНОЕ АДАПТИВНОЕ РАДИОПРИЕМНОЕ УСТРОЙСТВО | 1994 |

|

RU2066925C1 |

Изобретение относится к радиотехнике, а именно к технике радиосвязи, и предназначено для использования в составе радиоприемных устройств. Целью изобретения является разработка устройства обнаружения, обеспечивающего более высокую помехоустойчивость и расширенные функциональные возможности. Для достижения поставленной цели в устройство обнаружения, которое содержит блок опорных частот и N трактов обработки сигнала (2I,...,2N), подключенных через блок накопителей к блоку выбора максимума сигнала, введены распределитель импульсов и управляемый делитель. В устройстве реализуются совместно функции обнаружения и определения временного положения сигнала с программной перестройкой рабочей частоты. В устройстве используется привязка к меткам единого времени, что сужает область временной неопределенности возможного положения сигнала. Поиск сигнала осуществляется поэтапным просмотром зоны неопределенности последовательно-параллельным методом. При обработке сигнала вычисляется функционал, как сумма отсчетов, которые модифицированы по двум категориям на основе использования знаковой функции и превышения отсчетами среднего на интервале наблюдения. Решение об обнаружении сигнала принимается по результатам сравнения с порогом. Положение максимальной суммы, превышающей значения среднего, считается синхронным положением. 2 з.п. ф-лы. 18 ил.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| SU, авторское свидетельство, 1569998, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1998-05-10—Публикация

1997-01-23—Подача