Изобретение относится к вычислительной технике и может быть использовано для сопряжения аналоговых датчиков с вычислительными устройствами, функционирующими в системе остаточных классов (СОК).

Известен преобразователь напряжения в код системы остаточных классов, содержащий число каналов преобразования по числу основания СОК, в каждом из которых содержатся последовательно соединенные устройства сравнения,управления, компенсации напряжения, блок коррекции.

Однако преобразователь имеет большие аппаратурные затраты и инструментальные ошибки.

Известно устройство для преобразования напряжения в код СОК, содержащее делители эталонного напряжения, компараторы, переключатели, группы элементов ИЛИ, дешифратор, комбинационные схемы.

Однако устройство реализует принцип прямой дешифрации (считывания) и имеет большие аппаратурные затраты.

Наиболее близким к предлагаемому по сущности технического решения является устройство, содержащее блок определения остатка по наибольшему основанию, содержащий последовательно соединенные первый аналого-цифровой преобразователь, цифроаналоговый преобразователь, блок вычитания, второй вход которого соединен с входом первого АЦП, второй АЦП, п-1 канал определения остатков по остальным сснсваниям СОК, входы которых соединены с входом блока определения остатка по наибольшему основанию и с входом устройства, содержащий последовательно соединенные АЦП, сумматоры, шифраторы, блоки коррекции, состоящие из сумматоров по модулю, входы которых подключены к первым входам регистров и схем сравнения, выходы которых подключены к вторым входам регистров, источник опорных напряжений,

Однако известное устройство обладает низкой надежностью вследствие больших аппаратурных затрат.

Цель изобретения - повышение надежности путем сокращения аппаратурных затрат.

Поставленная цель достигается тем, что в аналого-цифровой преобразователь напряжения в код СОК, содержащий блок вычитания, аналого-цифровой преобразователь, выход которого является первой выходной шиной, (п - 1) сумматоров по модулю соответствующего основания СОК, выходы которых соединены с соответствующими информационными входами (п - 1) регистров, выходы которых являются соответственно выходными шинами, введены

источники опорных напряжений, два элемента 2И, элемент задержки, дешифратор, счетчик тактовых импульсов, (п - 1) блоков хранения констант, одновибратор, элемент дифференцирования, мультиплексор, аналоговый коммутатор, компаратор, блок выборки и запоминания, RS- триггер, S - вход которого является

0 шиной запуска, а выход подключен к первому входу первого элемента 2И, второй вход которого является шиной тактовых импульсов, а выход подключен к первому входу второ5 го элемента 2И и к входу элемента задержки, выход которого соединен с входом счетчика тактовых импульсов, выход которого подключен к управляющему информационному входу аналогового комму0 татора, к входам (п - 1) блоков хранения констант и к входу дешифратора, выход последнего из которых подключен к входу од- нозибратора, выход которого подключен к управляющим входам (п - 1) мультиплексо5 ров и к входу элемента дифференцирования, выход которого подключен к R-входу RS-триггера, первый и второй выходы источника опорных напряжений подключены соответственно к первому и второму инфор0 мационным входам аналогового коммутатора, третий информационный вход которого является входной шиной, выход которого подключен к первому входу блока вычитания, выход которого подключен к инфор5 мационному входу блока выборки и запоминания и к входу компаратора, выход которого подключен к второму входу второго элемента 2И, выход которого подключен к тактовым входам (п - 1) регистров и к

0 управляющему входу блока выборки и запоминания, выход которого подключен к второму входу блока вычитания и к входу аналого-цифрового преобразователя, выход которого подключен к первым информа5 ционным входам (п - 1) мультиплексоров, вторые информационные входы которых соответственно соединены с выходами (п - 1) блоков хранения констант, выходы (п - 1) мультиплексоров подключены соответст0 венно к первым входам (п - 1) сумматоров по модулю соответствующего основания СОК торые входы которых соединены с выходами соответствующих (п - 1) регистров. Сущность изобретения заключается в

5 повышении надежности путем сокращения аппаратурных затрат за счет применения метода квазипараллельного преобразования с пересчетом результата преобразования по одному ведущему основанию в остатки по остальным основаниям. При этом все остатки приближаются к одному и тому же уровню с погрешностью по ведущему основанию. Это достигается введением (п - 1) блоков хранения констант, (п - 1) мультиплексора, аналогового коммутатора, компа- ратора, блока выборки и запоминания, триггера, двух элементов 2И, элемента задержки, счетчика тактовых импульсов, од- ковибратора.

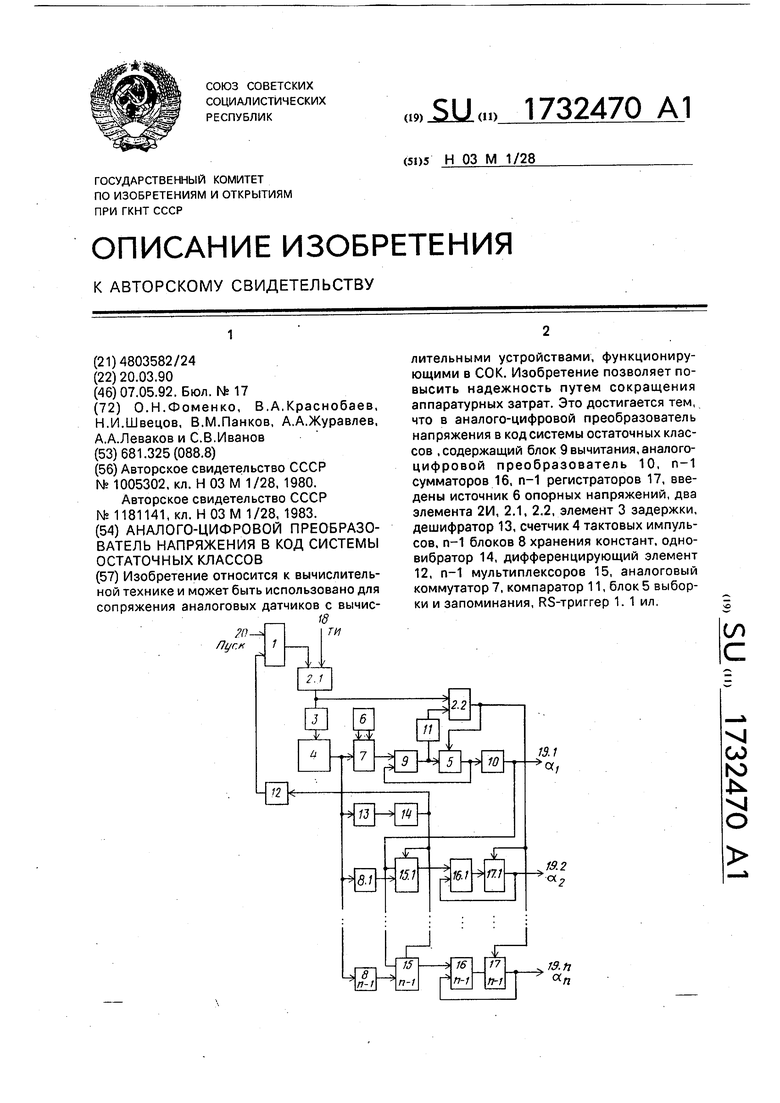

На чертеже представлена структурная схема аналого-цифрового преобразователя напряжения в код СОК.

Предлагаемый преобразователь содержит RS-триггер 1, элементы 2И, 2.1,2.2, элемент 3 задержки, счетчик 4, блок 5 выборки и запоминания, источник 6 эталонных напряжений, аналоговый коммутатор 7, блоки 8.1-8.П-1 хранения констант, блок9 вычитания, АЦП 10, компаратор 11, дифференциру- ющую цепочку 12, дешифратор 13, одновибратор 14, мультиплексоры 15.1- 15.П-1, сумматоры 16.1-16.n-1 по модулю, регистры 17.1-17.n-1, шину 18 подачи тактовых импульсов, выходные шины 19.1-19.п-1 устройства, шину 20 Пуск устройства.

В предлагаемом устройстве S-вход триггера 1 соединен с шиной 20 Пуск устройства. Выход RS-триггера 1 подключен к первому входу элемента 2.1, второй вход которого соединен с шиной 18 подачи так- товых импульсов, а выход подключен к первому входу элемента 2.2 и к входу элемента 3 задержки. Время задержки элемента 3 находится в пределах 0 t3 rn , где rn - период следования тактовых импульсов. Выход элемента 3 подключен к тактовому входу счетчика 4, модуль счета которого должен быть на единицу больше количества опорных напряжений преобразователя. Выход счетчика 4 подключен к входам группы блоков 8.1-6.П-1 хранения констант и к информационному входу аналогового коммутатора 7. Все блоки 8.1-8.п-1 каждому состоянию счетчика 4 ставят в однозначное соответствие код определенной, своей константы. Так, аналоге- вый коммутатор 7 по приходу каждого тактового импульса подключает эталонные напряжения Kjq с источника 6 опорных напряжений, удовлетворяющих сравнению 0 sKimod Pi. На выходе блоков 8.1-8.п-1 вы- деляется остаток цифрового эквивалента опорного напряжения K.q по соответствующему модулю. Так, если на выходе аналого,- вого коммутатора 7 присутствует эталонное напряжение Kiq, то на выходе блока 8. на- ходится код Kimod Pj, при этом j 2,п.

Разрядность блока 8.j равна разрядности наибольшего остатка по модулю Pj. Блоки 8.1-8.п-1 хранения констант могут быть

выполнены на базе постоянных запоминающих УСТРОЙСТВ, дешифраторов и т.д. Дешифратор 13 выделяет m-есостояние счетчика4, запуская одновибратор 14, который вырабатывает прямоугольный импульс положительной полярности, длительность импульса tn должна быть в пределах Tn tn 2ТП. Выход одновибратора 14 подключен к управляющим входам мультиплексоров 15.1-15.п-1 и к входу дифференцирующей цепочки 12. По заднему срезу прямоугольного импульса одновибратора 14 дифференцирующей цепочкой 12 формируется импульс, который обнуляет триггер 1, поступая на его R-вход. Выходы мультиплексоров 15.1-15.п-1 до срабатывания одновибратора 14 подключены к вторым своим входам.

При подаче на управляющие входы мультиплексоров 15 положительного потенциала с выхода одновибратора 14 выходы мультиплексоров 15 подключаются к своим первым входам, т.е. к выходу аналого-цифрового преобразователя 10. Выходы источника 6 опорных напряжений подключены к входам аналогового коммутатора 7, выход которого подключен к первому входу блока 9 вычитания, выход которого подключен к блоку 5 выборки и запоминания и к компаратору 11, который переходит в единичное состояние при наличии на его входе неотрицательного потенциала и обнуляется, если на его вход поступит напряжение отрицательное. Выход компаратора 11 подключен к первому входу элемента 2.2, который управляет прохождением тактовых импульсов: если на первом входе элемента 2.2 присутствует потенциал логического нуля, то тактовые импульсы не проходят на его выход, и наоборот. Выход элемента 2.2 подключен к тактовым входам группы регистров 17.1-17.п-1 и к управляющему входу блока 5 выборки и запоминания, выход которого подключен к входу АЦП 10 и к второму входу блока 9 вычитания. АЦП 10 выполнен малоразрядным, лишь для преобразования остаточного напряжения блока 5 в его цифровой эквивалент ai . Выходы мультиплексоров 15 подключены к первым входам соответствующих сумматоров 16 по модулю, выходы которых подключены к входам соответствующих регистров 17, выходы которых подключены к выходным шинам 19.2-19.п-1 устройства.

Предлагаемый преобразователь использует следующий принцип работы .

Цифровой эквивалент А преобразуемого напряжения Unp в СОК с основаниями {Pi}, i 1 ,п может быть представлен остатками {а,} в виде А («1 , Oiап), где п количество оснований PI СОК, которые должны удовлетворять условию попарной простоты и упорядоченности по величине (основание PI - наименьшее), а их произведение Ф- диапазону изменения цифровых эквивалентов преобразуемых напряжений. С другой стороны

Unp EajKjq+aiq±0, О)

где q - шаг квантования

О- ошибка преобразования

# Kjmod Pi;

(2)

aj Ј, {0, 1 - в зависимости от факта вхождения константы в выражение (1);

Pi;

(3)

m - количество констант преобразования. Так, для случая половинного разбиения

(разрядного уравновешивания)

Ki Pi;(4)

Ki 2Kj-i:(5)

j 2,m;(6)

Ф тФ

. iog2-p b, (7)

где Ь - ближайшее к b целое, не меньшее b.

Тогда представляется возможным в процессе нахождения остатка а от числа А по модулю Pi решать задачу вычисления остальных остатков оз.... ctn Покажем это на примере. Пусть Pi 2, Рг 3, Рз 5, Ф 235 30. А 21. Множество констант согласно формул (2, 3, 5, 6) , 8, 4,2;

{Kjmod Pi} 0,0, 0,0;

{Kjmod P2} 1,2,11,2;

{Kjmod Рз} 1,3, 4,2.

Используя соотношения (1)-(7), определим остатки { а-, }. Для этого проверим разность выбираемого числа А и старшего коэффициента Ki 16. Если разность числа и константы будет неотрицательной, то коэффициенту ai присваивают значение 1 и фиксируют полученный результат, от которого впоследствии будут вычитаться известные константы в порядке уменьшения их величины AI А - ai Кч 21 - 16 5 О (фиксируют). Если же такая разность даст отрицательный результат, то вычитаемая константа пропускается, так как Аа AI - 32 К2 5. Следовательно,5 необходимо пропустить.

Выбираем константу Кз 4, Аз А2 - аз х хКз 5-1-4 0-1 (фиксируем). HU 2;

0

5

0

5

0

5

0

5

0

5

А4 Аз - 34 -2 1 (пропускаем). На этом процесс преобразования завершен. Одновременно с вычитанием j-й кон- станты в сумматорах по модулю Pi, Г 2,п происходит суммирование остатков этой константы по соответствующим основаниям

02 (Ki mod P2 + Кз mod P2+ а 1) х х mod Pz(1 + 1 + 1)mod3 0;

Оз 2 (Kimod P2 + Ksmod Рз + «1) х х mod Рз (1 + 4 + 1)mod5 0.

Проверка

«1 21mod2 1; аи -: 21mod3 0; 03 21mod5 1.

Процесс преобразования завершен, при этом конечная цель преобразования достигнута, число А в СОК представлено своими остатками А 21 (1,0, 1) по основанию {Pi} 2, 3, 5.

Преобразователь работает следующим образом.

В исходном состоянии RS-триггер 1, регистры 17 и счетчик 4 обнулены. Нулевое состояние счетчика 4 обеспечивает подключение аналоговым коммутатором 7 опорного напряжения Kiq с источником 6 опорных напряжений к первому входу блока 9 вычитания, а из блоков 8 хранения констант - считывание кодов Kimod PJ, где j 2,п. Выход триггера 1 блокирует прохождение тактовых импульсов через элемент 2.1. Потенциал логического нуля с выхода дешифратора 13 и, следовательно, одновибра- тора 14, обеспечивает подключение мультиплексорами 15 выходов блоков 8 хранения констант к первым входам соответствующих сумматоров 16 по модулю. В блок 5 выборки и запоминания записана величина преобразуемого напряжения.

С приходом запускающего импульса по шине 20 RS-триггер 1 переходит в единичное состояние и, таким образом, обеспечивает поступление тактовых импульсов в преобразователь. Знак разности Опр - Kiq напряжений определяет потенциал на выходе блока 9 вычитания. Если разностное напряжение положительно, то с выхода компаратора 11 на первый вход элемента 2,2 поступает разрешающий потенциал, что обеспечивает прохождение тактового импульса на управляющий вход блока 5 выборки и запоминания и на тактовые входы регистров 17, и, следовательно, осуществляется в них запись результатов суммирования по модулю. В случае, когда разность

отрицательна, уровень логического нуля с выхода компаратора 11 блокирует прохождение тактового импульса через элемент 2.2.

Через время задержки Тз тактовый импульс поступает на тактовый вход счетчика 4, который изменит свое состояние и обеспечит выборку эталонного напряжения, кодов {femod PJ} из соответствующего блока 8 хранения констант. Далее процесс преобразования происходит аналогично, пока по m-му импульсу не будет использовано последнее опорное напряжение Kmq и его остаточные представления по остальным, кроме первого, модулям. При этом в блоке 5 выборки и запоминания находится разностное напряжение, которое, проходя через АЦП 10, поступает на выходную шину 19.1 в виде кода «1 A mod Pi .После m-ro импульса на выходе блоков 8 хранения констант будет присутствовать нулевой код, кроме того, на выходе дешифратора 13 появится потенциал логической единицы, запустится одновибратор 14, единичный потенциал с выхода которого посредством мультиплексоров 15 подключит выход АЦП 10 к первым входам сумматоров 16 по модулю, при этом на выходах их формируются истинные значения а - ап и (т + 1)-й импульс запишет их в регистры 17. До прихода (т + 2)-го импульса одновибратор 14 перейдет в нулевое состояние, а на выходе дифференцирующей цепочки 12 сформируется импульс, который переведет RS-триггер 1 в нулевое состояние по его R-входу. Это блокирует дальнейшее прохождение тактовых импульсов через элемент 2И 2.1. Процесс преобразования на этом заканчивается.

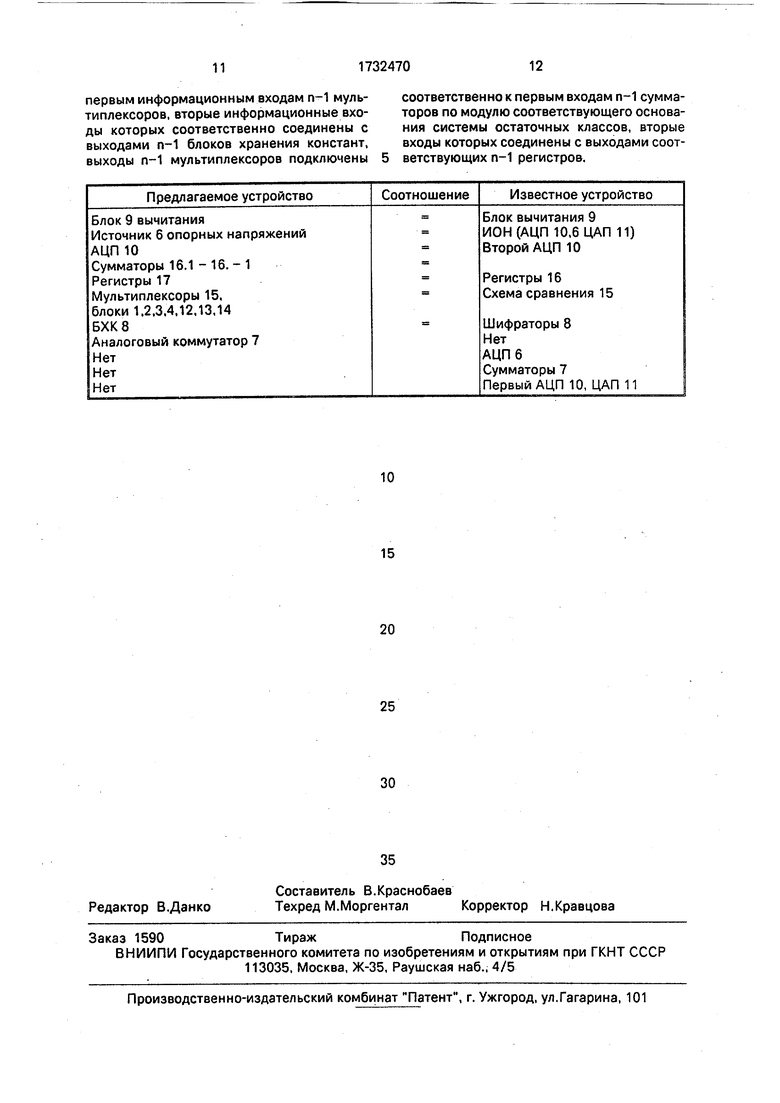

Техническое преимущество предлагаемого преобразователя по сравнению с известным заключается в повышении надежности путем сокращения аппаратурных затрат. Сравнительный анализ аппаратурных затрат предлагаемого и известного преобразователей приведены в таблице

Как видно изтаблицы, аппаратурные затраты предлагаемого устройства более чем вдвое меньше, чем у известного Кроме того, у предлагаемого устройства методические ошибки существенно меньше, чем у известного, так как приближение идет к одному уровню в одном канале, а не независимо. Аналоговая часть, в основном определяющая надежности АЦП, у предлагаемого устройства в п раз меньше.

Экономический эффект от использования изобретения заключается в существенном удешевлении устройства сопряжения СЦВМ СОК, в удешевлении аппаратуры обнаружения и исправлении ошибок за счет повышения достоверности результатов преобразования.

Ф о р м у л а и з о б 0 ет е н и я

Аналого-цифровой преобразователь напряжения в код системы остатрчных классов, содержащий блок вычитания, аналого-цифровой преобразователь, выход которого является первой выходной шиной, п-1 сумматоров по модулю соответствующего основания системы остаточных классов, выходы которых соединены с соответствуК щими информационными входами п-1 регистров, выходы которых являются соответственно п-1 выходными шинами, отличающийся тем, что, с целью повышения надежности путем сокращения аппаратурных затрат, в него введены источник опорных напряжений, два элемента 2И, элемент задержки, дешифратор, счетчик тактовых импульсов, п-1 блоков хранения констант, одновибратор, элемент дифференцирования, п-1 мультиплексоров, аналоговый коммутатор, компаратор, блок выборки и запоминания, RS-триггер, S-вход которого является шиной запуска, а выход подключен к первому входу первого элемента 2И, второй вход которого является шиной тактовых импульсов, а выход подключен к первому входу второго элемента 2И и к входу элемента задержки, выход которого соединен с входом счетчика тактовых импульсов, выход

которого подключен к управляющему входу аналогового коммутатора, к входам п-1 блоков хранения констант и к входу дешифратора, выход последнего из которых подключен к входу одновибратора, выход

которого подключен куправляющим входам п-1 мультиплексоров и к входу элемента дифференцирования, выход которого подключен к R-входу RS-триггера, первый и второй выходы источника опорных напряжений

подключены соответственно к первому и второму информационным входам аналогового коммутатора, третий информационный вход которого является входной шиной, выход аналогового коммутатора подключен к

первому входу блока вычитания, выход которого подключен к информационному входу блока выборки и запоминания и к входу компаратора, выход которого подключен к второму входу второго элемента 2И, выход

которого подключен к тактовым входам п-1 регистров и к управляющему входу блока выборки и запоминания, выход которого подключен к второму входу блока вычитания и к входу аналого-цифрового преобразователя, выход которого подключен к

первым информационным входам п-1 мультиплексоров, вторые информационные входы которых соответственно соединены с выходами п-1 блоков хранения констант,

соответственно к первым вход торов по модулю соответству ния системы остаточных кл входы которых соединены с в

выходы п-1 мультиплексоров подключены 5 ветствующих п-1 регистров.

соответственно к первым входам п-1 сумматоров по модулю соответствующего основания системы остаточных классов, вторые входы которых соединены с выходами соот

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода-вывода аналоговых сигналов | 1981 |

|

SU1015369A1 |

| Функциональный преобразователь угла поворота вала в код | 1985 |

|

SU1309314A1 |

| Система экстремального регулирования | 1985 |

|

SU1352452A1 |

| Устройство стабилизации амплитуды видеосигнала | 1989 |

|

SU1748283A1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ ТЕМНОВОГО СИГНАЛА МНОГОЭЛЕМЕНТНЫХ ФОТОДИОДНЫХ ПРИЕМНИКОВ | 1996 |

|

RU2123768C1 |

| Устройство для измерения характеристик сверхпроводящих образцов | 1989 |

|

SU1675789A1 |

| ИЗМЕРИТЕЛЬ АМПЛИТУДЫ ГАРМОНИЧЕСКИХ СИГНАЛОВ | 2002 |

|

RU2224263C1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| Многоканальный фотометр | 1987 |

|

SU1492224A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1478330A1 |

Изобретение относится к вычислительной технике и может быть использовано для сопряжения аналоговых датчиков с вычис1д лительными устройствами, функционирующими в СОК. Изобретение позволяет повысить надежность путем сокращения аппаратурных затрат. Это достигается тем, что в аналого-цифровой преобразователь напряжения в код системы остаточных классов .содержащий блок 9вычитания,аналого- цифровой преобразователь 10, п-1 сумматоров 16, п-1 регистраторов 17, введены источник 6 опорных напряжений, два элемента 2И, 2.1, 2.2, элемент 3 задержки, дешифратор 13, счетчик 4 тактовых импульсов, п-1 блоков 8 хранения констант, одно- вибратор 14, дифференцирующий элемент 12, п-1 мультиплексоров 15, аналоговый коммутатор, компаратор 11, блок5 выборки и запоминания, RS-триггер 1. 1 ил, (Л С i со ю Јь о

Предлагаемое устройство

Блок 9 вычитания

Источник 6 опорных напр

АЦП 10

Сумматоры 16.1 - 16. - 1

Регистры 17

Мультиплексоры 15,

блоки 1.2.3.4,12,13,14

БХК8

Аналоговый коммутатор 7

Нет

Нет

Нет

Соотношение

Известное устройство

Блок вычитания 9 ИОН (АЦП 10,6 ЦАП 1 Второй АЦП 10

Регистры 16 Схема сравнения 15

Шифраторы 8 Нет АЦП 6 Сумматоры 7

Первый АЦП 10, ЦАП

| Устройство для преобразования напряжения в код системы остаточных классов | 1981 |

|

SU1005302A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аналого-цифровой преобразователь в системе остаточных классов | 1983 |

|

SU1181141A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-05-07—Публикация

1990-03-20—Подача