Изобретение относится к импульсной и вычислительной технике и может быть использовано а магистральн.о последовательном интерфейсе с центральным управлением, применяемом в системе электронных модулей в качестве передающего устройства.

Известен формирователь биполярных импульсов, содержащий два канала, проводимость транзисторов одного из которых противоположна проводимости транзисторов другого канала, в состав каждого из каналог входят транзисторный ключ, источник питания одной полярности, два диода и выходной транзистор, а также выходную шину.

Недостатком этого формирователя является отсутствие защиты от перегрузки по току и низкое быстродействие. Наиболее близким по технической сущности является формирователь биполярных сигналов, содержащий двухполярный источник питания, общий вывод которого соединен с общей шиной устройства, три диода, двенадцать резисторов, три ключа одного типа проводимости и один ключ другого типа проводимости, причем вход первого ключа соединен с первым входом устройства, первый и второй выходные каналы, первые выводы первого и второго выхо,цных каналов соединены с выходом устройства, вторые выходы - с общей шиной устройства, третий вывод первого выходного кангэла соедине с положительным выводом двухполярного источника питания, отрицатель.ный вывод которой соединен с третьим выводом второго выходного канала.

Недостатки этого формирователя - отсутствие защиты от перегрузки по току, низкое быстродействие и низкая амплитуда выходного сигнала за счет падения напряжения на змиттерных переходах транзисторов 16 м 17, элемента И-ИГг 12, ключа 20, эмиттерного повторителя 21 и выходного транзистора 27.

Цель изобретения - защита от перегрузки по току, повышение быстродейстг ия и амплиту,цы выходного сигнала,

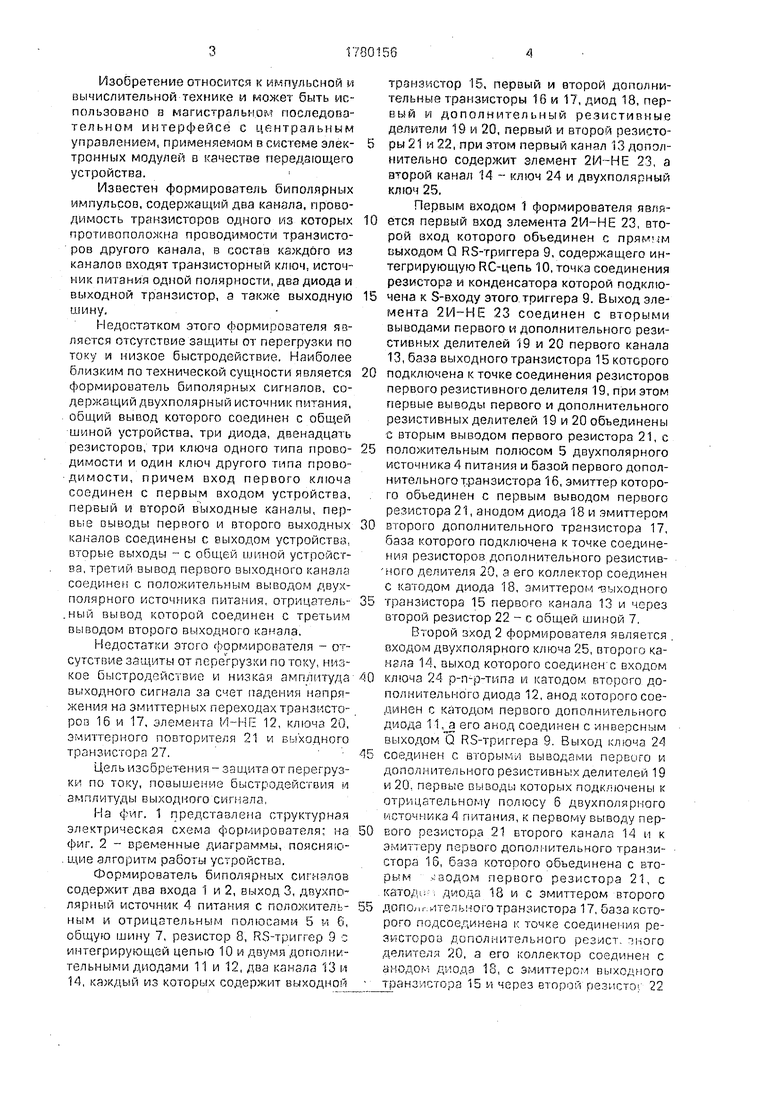

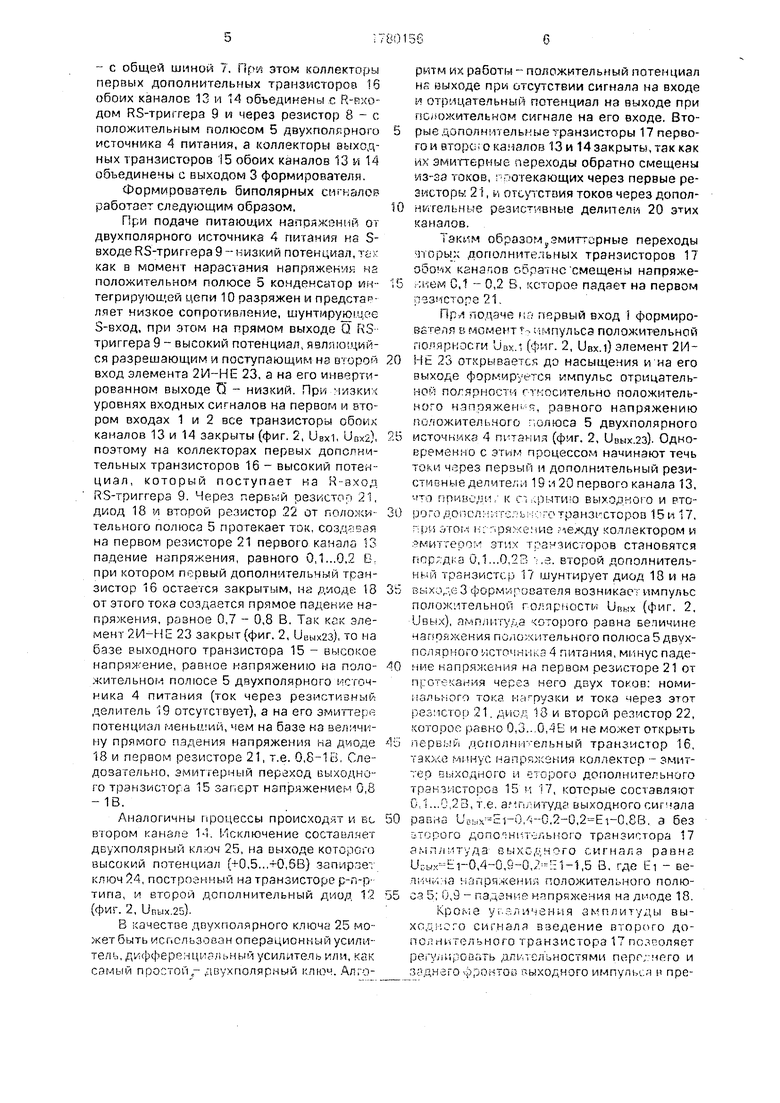

На фиг. 1 Г1редставлена структурная злектрическая схема формирователя; на фиг. 2 - временные диаграммы, поясняю. щие алгоритм работы устройства.

Формирователь биполярных сигналов содержит два входа 1 и 2, выход 3, двухполярный источник 4 питания с положительным и отрицательным полюсами 5 и 6, общую шину 7, резистор 8, RS-триггер Э с интегрирующей цепью 10 и двумя дополнительными диодами 11 и 12, два канзла 13 и 14, каждый из которых содержит выходной

транзистор 15, первый и второй дополнительные транзисторы 16 и 17, диод 18, первый и дополнительный резистивные дел 1тели 19 и 20, первый и второй резисторы21 м 22, при этом первый канал 13 дополнительно содержит элемент 21/1-НЕ 23, а агорой канал 14 - ключ 24 и двухполярный ключ 25,

Первым входом 1 формирователя явля0 етсп первый вход элемента 2И-НЕ 23, второй вход которого объединен с выходом Q RS-триггера 9, содержащего интегрирующую RC-цепь 10, точка соединения резистора и конденсатора которой подключена к S-входу этого триггера 9. Выход элемента 2И-НЕ 23 соединен с вторыми выводами первого и дополнительного резистивных делителей 19 и 20 первого канала 13, база выходного транзистора 15 которого

0 подключена к точке соединения резисторов первого резистивного делителя 19, при этом первые выводы первого и дополнительного резистивных делителей 19 и 20 объединены е вторым выводом первого резистора 21, с

5 положительным полюсом 5 двухполярного источника 4 питания и базой первого дополнительного транзистора 16, эмиттер которо, го объединен с первым выводом первого резистора 21, анодом диода 18 и эмиттером

0 второго дополнительного транзистора 17, база которого подключена к точке соединения резисторов дополнительного резистивного делителя 20, а его коллектор соединен С катодом диода 18, эмиттером чзыходного

5 транзистора 15 первого канала 13 и через второй резистор 22 - с общей шиной 7,

Второй вход 2 формирователя является . входом двухполярного ,члюча 25, второго канала 14, выход которого соединенс входом

0 ключа 24 р-п-р-типа и катодом второго дополнительного диода 12, анод которого соединен с катодом первого дополнительного диода 11,j его анод соединен с инверсным выходом Q RS-триггера 9. Выход ключа 24

5 сое,динен с вторыми выводами первого и дополнительного резистивных делителей 19 и 20, первые выводы которых подключены к отрицательному полюсу 6 двухполярного источника 4 питания, к первому выводу пер0 Еого резистора 21 второго канала 14 и к эмиттеру первого дополнительного транзистора 16, база которого объединена с вторым ;водом первого резистора 21, с катод ; 1 диода 18 и с эмиттером второго

5 ,п,опОлг..1тельноготранзистора 17, база которого подсоединена к точке соединения резисторов дополнительного резист. тного делителя 20, а его коллектор соединен с анодом диода 18, с змиттером выходного транзистора 15 и через етороД резисто. 22

-с общей шиной 7, При этом коллекторы первых дополнительных транзисторов 15 обоих каналов 13 и 14 объединены .с R-RXOдом НЗ-триггера 9 и через резистор 8 - с положительным полюсом 5 двухполярного источника 4 питания, а коллекторы выходных транзисторов 15 обоих каналов 13 и 14 объединены с выходом 3 формирователя.

Форммровзтель биполярных сигналов работает следующим образом.

При подаче питающих напряжений от двухполярного источника 4 питания на Sвходе НЗ-триггера9 -низкий потенциал, тек как в момент нарастания напряженля на положительном полюсе 5 конденсатор митегрирующей цепи 10 разряжен и предстарляет низкое сопротивление, шунтирующее З-вход, при этом на прямом выходе Q RS триггера 9 - высокий потенциал, являющийся разрешающим и поступающим нз второй вход элемента 2И-НЕ 23, а на его инвертированном выходе П - низкий. При | 1зких уровнях входных сигналов на первом и втором входах 1 и 2 все транзисторы обоих каналов 13 и 14 закрыты (фиг. 2, Usxi, ивх2;, поэтому на коллекторах первых дополнительных транзисторов 16 - высокий потенциал, который поступает на Н-вход RS-триггерз 9. Через первый резистор 21, диод 18 W второй резистор 22 от положительного полюса 5 протекает ток, соз/давая на первом резисторе 21 первого канала 13 падение напряжения, равного 0,1...0,2 О, при котором первый дополнительный транзистор 16 остается закрытым, на диоде 18 от этого тока создается прямое падение напряжения, равное 0,7 - 0,8 В. Так как элемент 2И-НЕ 23 закрыт (фиг. 2, ивь1х2з), то на базе выходного транзистора 15 - высокое напряжение, равное напряжению на положительном полюсе 5 двухполярного источника 4 питания (ток через резистивный делитель 19 отсутствует), а на его эмичтерв потенциал меньц.ий, чем на базе на величину прямого падения напряжения на диоде 18 и первом резисторе 21, т.е. 0,8-1 В, Следозательно, эмиттерный переход выходного транзистора 15 заперт напряжением 0,6

-1В.

Аналогичны процессы происходят и вс втором канале 1ч. Исключение составляет двухполярный ключ 25, на выходе которого высокий потенциал (+0,5...+0,6В} запирзет ключ 24, построенный на транзисторе р-п-ртипа, и второй дополнительный диод 12

(фиг. 2, Unbix.25).

В качестве двухполярного ключа 25 может быть использован операционный усилитель, дифференциальный усилитель или, как самый простой,- ,цвухполярный ключ. Алгоритм их. работы- положительный потенциал HS выходе при отсутствии сигнала на входе и отрицательный потенциал на выходе при пс(ожительнам сигнале на его входе. Вторые дополнительные транзисторы 17 первого и вторснока.чзлов 13 и 14 закрыты, так как их эмигтерные переходы обратно смещены мз-эа токов, Гоотекающих через первые резисторы 21, iri токов через дополнь ггельные резистивные делители 20 этих каналов.

Тэкым образоМуЭмитторные переходы чторь х дополнительных транзисторов 17 канапов ооратнссмещены напряже.;нем С,1 - 0,2 В, которое падает на первом резисторе 21.

Пру1 лодзче lis первый вход i формирователя в момент Г-, 11 чпульсэ положительной полярности ивх. (фиг. 2, UBX.I) элемент 2ИНЁ 23 открываетск до насыщения ина его выходе формируется импульс отрицательной полярности гткосительно положительного нэпряжен -я, равного напряжению гпэ.южитель.чого полюса 5 двухполярного источнике 4 п1-танил (фиг, 2, ивьлх.2з). Одновременно с этим процессом начинают течь токи через первый и дополнительный резистивные делители 19 и 20 первого канала 13, приводи, к С-.. выходного и второго допсл;;1ггсяь;;оготранз1 сторов 15 и 17, при этом HL ;-. коллектором и ; миггером этих транзисторов становятся пор;;дка 0,1,..0,2В .е. второй дополнительный транзистор 17 шунтирует диод 18 и на выходе 3 формирователя возникает импульс положительной голпрностм URWX (фиг. 2, ивых), амплитуда которого равна величине нагфяжеиия поло): ительного полюса 5 двухпслярного лсточннкз 4 питания, минус падение напряжения на первом резисторе 21 от протекания через него двух токов: номиi aль ioгo тока нагрузки и тока через этот резмслор 21. диод 18 и второй резистор 22, которое равно 0,3...0,4Е и не может открыть первый дополнительный транзистор 16, такхе минус напряжения коллектор - змиттер выходного и еторого дополнительного транзистороз 15 и 17, которые составляют 0,1...0,2В, т.е. а 1плитуда выходного сигнала равна Увых-Е ,2-0,2-Е 1-0,88. а без L-TGporo Aono:Hiriuj-. трзнзистора 17 а.мплмтудз выходного сигнала равна U;:.wx-E 1-0,4-0,9-0,2-:: 1-1,5 В, где El - вел1--;ч;.-;:1а нагфяжения положительного полюса Б; 0,9 - падание напряжения нз диоде 18.

Кроме уг.зличения амплитуды выхадисго сигналя взедение второго дополнительного транзистора 17 позсоляет peryjiUpouaTb длиггельностями nepr;: iero и заднего фронтой выходного импулься и пределах от 30 до 120 не путем изменения величии резисторов первого и дополнительного резмстийных делителей 19 vi 20 (фиг. 2, Увых), а также выбором соответствующих типов транзисторов: выходного и второго дополнительного 15 и 17, у которых величины емкостей коллекторного и эмиттерного переходов существенно влияют на длительности переднего и заднего фронтов выходного сигнала гф1 и Гф2 (фиг. 2, UBUX).

При изменении амплитуды входного сигнала в момент i:i на первом входе 1 форг 1ирователя с высокого уровня на низкий (фиг. 2, Uax.i) происходит запирание элемента 2И-НЕ 23, на выходе которого происходит формирование заднего фронта выходного импульса, связанное с зарядами емкостей змиттерного перехода выходного транзистора 15 и коллекторного перехода DToporo дополнительного транзистора 17. Затем происходит запирание эмиттерного перехода выходного транзистора 15 обратным напряжением, создаваемым за снет протекания тока.через первый резистор 21. диод 18 и второй резистор 21 и подачи полного напряжения EI положительного полюса 5 двухполярного источника 4 питания на базу зтого транзистора, что уменьшает время рассасывания неосновных носителей в его базе, а следовательно, уменьшает задержку заднего фронта выходного импульса относительно входного с 80 не до 15...20 не (80...100 НС - удлинение выходного сигнала без запирающего напряжения и 15...20 не удлинение выходного сигнала при подаче на змиттерный переход выходного транзистора 15 запирающего напряжения).

При подаче импульса положительной полярности на второй вход 2 формирователя в момент ti,(фиг, 2, Uax2) на выходе двухполярного ключа 25 происходит изменение полярности выходного сигнала с положительной на отрицательную (фиг. 2, ивых25). Выходной сигнал (импульс) отрицательной полярности с выхода даухполярного ключа 25 поступает на вход ключа 24 р-п-р-типа, открывает его и на его выходе формируется импульс положительной полярности относительно отрицательного напряжения отрицательного полюса б двухполярного источника 4 питания (фиг, 2, UsuxZ). Одновременно этот импульс поступает на катод второго дополнительного диода 12. но так как здесь включены два последовательно соединенных первый и второй дополнительные ,циоды 11 и 12. то суммарное их сопротивление значительно больше входного сопротивления ключа 25 и весь ток практически пост5,пает в базу этого ключа. Дальше начинают протекать процессы, аналогичные процессам первого канала 13, описанные выше.

На фиг. 2 UBbix f(t) изображена эпюра

выходного напряжения формирователя, на которой видно значительное уменьшение задних фронтов гфа импульсов из-за очень короткого времени окончания импульса нз первом входе 1 и началом импульса на

втором входе 2. Здесь происходит быстрое запирание коллекторного перехода выходного транзистора 15 р-п-р-типа первого канала 13, так как его коллектор поступает напряжение отрицательной полярности и

запирает его. Аналогичный процесс происходит и во втором канале 14. Задержка переднего фронта выходного импульса составляет 15...20 не (на фиг. 2 не показана). Длительность переднего фронта

гф1 120нс; ..,15 не. Длительность переднего фронта может быть уменьшена до 30 НС путем выбора выходного и второго дополнительного транзисторов 15 и 17.Период выходных импульсов больше периода

входных на 10..,15 не за счет задержки переднего фронта выходного импульса. На фиг. 2 UBbix f(t) показаны также единичные выходные импульсы, длительность переднего и заднего фронтов которых одинакова и

равна 120 не..

Быстродействие формирователя достигается путем подачи запирающих напряжений на эмиттерные переходы выходных транзисторов 15 обоих каналов 13 и 14 и

запирающего напряжения положительной полярности на вход ключа 24 второго канала 14.

Защита от перегрузки по току в формирователе осуществляется следующим образом.

Пусть во время действия входного импульса на первом входе 1 формирователя произошло несанкционированное короткое замыкание на его выходе 3, прм этом резко

возрастает его выходной ток, который увеличивает падение напряжения на первом резисторе 21 первого канала 13 до 0,8 В, чго приводит к открыванию первого дополнительного транзистора 16 и уменьшению

напряжения-на его коллекторе, а следовательно, и на f -входе RS-триггера 9, приводящее к изменению его состояния, т.е. на его пг;тмом выходе Q - низкий потенциал, кото: :й поступает на второй вход элемента 21: НЕ и блокирует его, а на аго инверсном выходе 5 - высокий положите/шный потенциал, который запирает клю. М, оба выходных транзистора 15 обоих каналов 13 м 14 закрыты.

Формула изобретений Формирователь биполярных сигналов, содержащий два входа, выход, двухполярный источник питания, общий вывод которого соединен с общей шиной формирователя, резистор, один вывод которого соединен с положительным полюсом двухполярного источника питания, два канала, каждый из которых содержит выходной транзистор, диод и первый резистивный делитель, при этом коллекторы выходных транзисторов обоих каналов объединены с выходом формиро вателя, а мх базы подключены к обидему выводу резисторов первых резистивных делителей, первые выводы которых подключены соответственно к положительному и отрицательному полюсам двухполярного источника питания, причем второй канал содержит дополнительно ключ, проводимость транзистора которого противоположна проводимости выходного транзистора первого канала, отличающийся тем, что, с целью защиты от перегрузкидю току, повышения быстродействия и амплитуды входного сигнала, в него введены RS-триггер с интегрирующей RC-цепью, общий вывод резистора и конденсатора которой подключена к Sвходу этого триггера,-а вторые выводы резистора и конденсатора подключе1-:ь соответственно к положительному полюсу двухполярного источника питания и к общей шине, а также два дополнительных диода, анод из которых подключен к инверсному Q-выходу RS-триггера, а его катод - к аноду второго дополнительного диода, причем в каж,цы1;| канал введены два дополнительных транзистора, проводимость которых в первом канале противоположна, а во втором - одинакова с проводимостью выходного транзистора, дополнительный резистивный делитель и два резистора, кроме того, впервый канал введен элемент2И-НЕ, а во второй - двухполярный ключ, положительный и отрицательный выводы питания которого подключены соответственно к положительному и отрицательному полюсам двухполярного источника п.-гтания, при этом коллекторы первых дополнительных транзисторов пеового и второго каналов соединены с вторым выводом реэь-стора и с R-входом RS-триггеps, параллельно змиттериым переходам этих транз ;сторов подключен первый резистир, перйый abfFJOA которого соединен с эмиггером второго дополнительного транзистора, а его коллектор соединен с эмиттером выходного транзистора и через второй резистор - с общей шиной, а база второго дополнительного транзистора подключена к общему выводу резисторов дополнительного резистизного делителя, первый вывод которого к nepBO / каиаяе подключен к положительному полюсу двухполярного источника питания и к базе первого дополнительного транзистора, эмиттер которого соединен с гнодом диода, а его катод - с эмиттером выходного транзистора, второй вывод дополнительного резистивного делителя объединен с вторым выводом резистивного делителя и выходом элемента , первый вход которого соединен с первьм рхсдом срормирователя, а второй его вход с прямым -выходом RS-триггера, второй вход форм;;рователя соединен с входом дпухполярного ключа второго канала, к выходу которого подключены катод второго дополнительного диода и вход ключа, а его выход соединен с вторыми выводами первого и дополнительного резистивных делителей, первый вывод дополнительного резистианогоделителя второго канала подключен к отрицательному полюсу двухполярного источника питания и эмиттеру первого дополнительного транзистора, база которого соеди-гена с катодом диода, а ИГО анод - с эмиггером выходного транзистора второго канала.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОПТОЭЛЕКТРОННОЕ УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДИСКРЕТНЫХ СИГНАЛОВ В ЛИНИЮ СВЯЗИ | 2006 |

|

RU2313914C1 |

| Импульсный понижающий стабилизатор постоянного напряжения | 1990 |

|

SU1786477A1 |

| Формирователь двухполярного образцового напряжения | 1983 |

|

SU1115037A1 |

| Источник вторичного электропитания для сети постоянного напряжения | 1990 |

|

SU1786476A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

| Генератор импульсов | 1978 |

|

SU790109A1 |

| Формирователь импульсов | 1977 |

|

SU702499A1 |

| ДВУХПОЛЯРНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ | 1992 |

|

RU2013799C1 |

| Стабилизированный источник питания | 1981 |

|

SU993228A1 |

| Формирователь биполярных импульсов | 1977 |

|

SU690618A1 |

Изобретение относится к импульсной и вычислительной технике и может быть мс- пользовано в магистральном последовз-тельном интерфейсе с центральным управлением, применяемом в системе электронных модулей в качестве передающего устройства. Формирователь содержит два входа 1 и 2. выход 3, двухполярный источник 4 питания, два канала 13 и 14. каждый из которых содержит выходной транзистор 15. диод 18 и первый резистивный делитель 19. RS-триггер 9 с интегрирующей цепью 10. два дополнительных диода 11 и 12, два дополнительных транзистора 16 и 17. дополнительный резистивный делитель 20. два резистора 21 и 22. эл-емент 2И-НЕ 23, двухполярный ключ 25 во втором канале. 2 ил.ел-J 1ДXI 00оелCh

| Формирователь биполярных импульсов | 1977 |

|

SU690618A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

Авторы

Даты

1992-12-07—Публикация

1990-10-02—Подача