Фиг i

Изобретение относится к вычислительной технике и может использоваться при кодировании и декодировании телевизионных и речевых сигналов.

Известна система кодирования и декодирования сигналов, в которой передающая сторона содержит последовательно соединенные компаратор, триггер и первый местный декодер, состоящий из последовательно соединенных регистра сдвига, логического б,лок|, слогового фильтра, сумматора, усилител я, амплитудно-импульсного модулятора и интегратора, соединенного с одним из входов компаратора, а приемная сторона содержит второй местный декодер, аналогичный первому.

Недостатком этой системы является низкое быстродействие.

Наиболее близкой по технической сущности к заявляемому изобретению является система, содержащая канал связи, на передающей стороне - аналого-цифровой преобразователь, информационный вход которого является информационным входом системы, выходы аналого-цифрового преобразователя соединены с первыми входами кодера выходного сигнала, первый и второй блоки памяти, на приемной стороне - первый блок памяти м блок восстановления сигнала, выход которого является выходом системы 2.

Недостатком системы является низкое быстродействие, обусловленное последовательной передачей по каналам связи отдельных разрядов многоразрядных кодов выборок, и невысокая точность преобразования, ограниченная допустимой частотой формирования отсчетов при данном способе передачи информации и заданной полосе пропускания каналов связи.

Целью изобретения является повышение быстродействия и точности системы за счет сокращения времени, затрачиваемого на кодирование каждой выборки, представления каждой выборки одним двоичным разрядом, и применением при кодировании перестраиваемых шкал квантования,

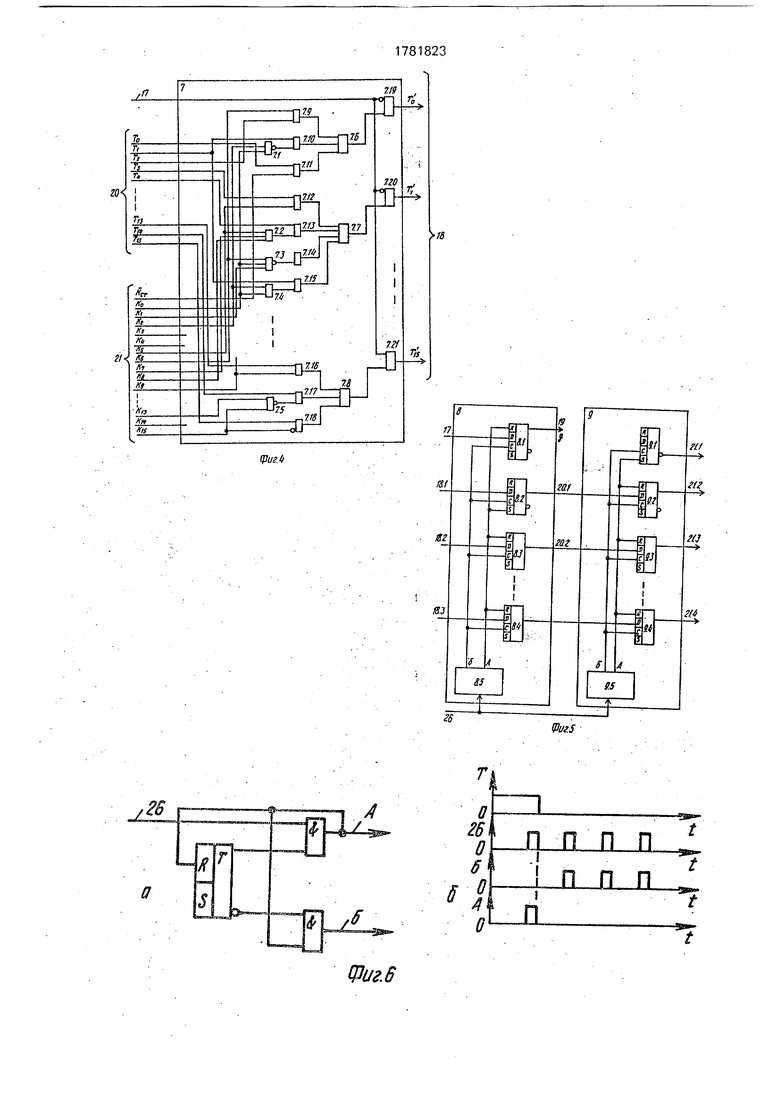

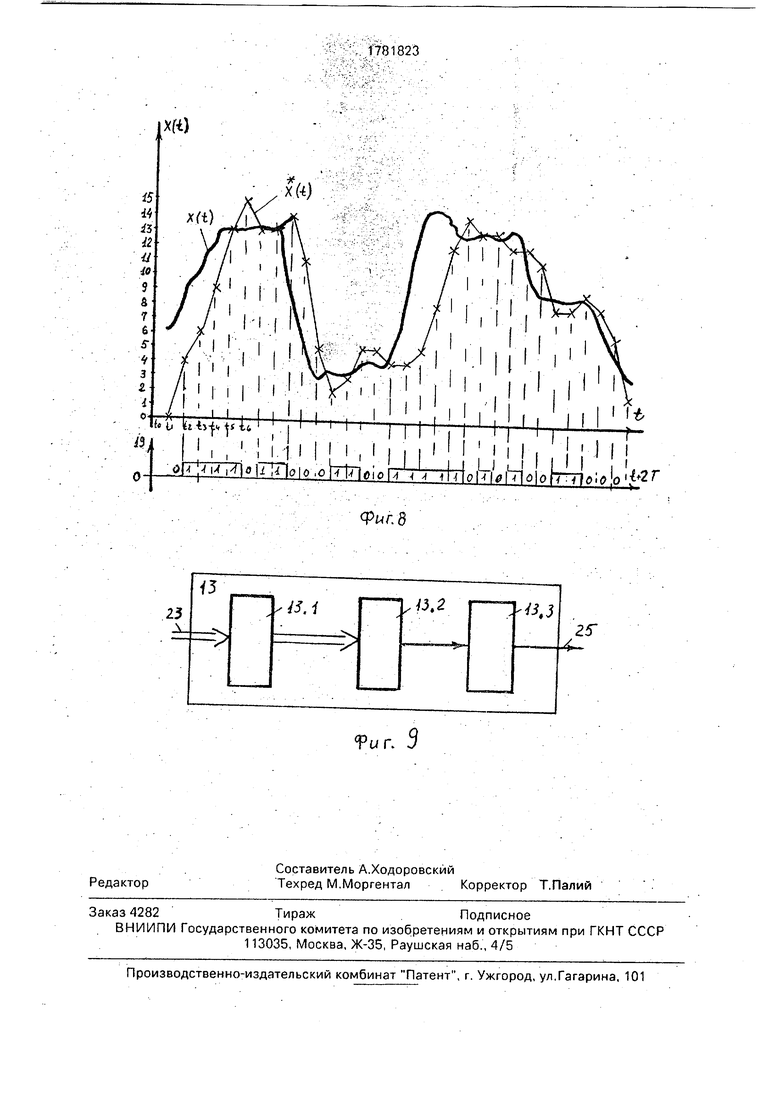

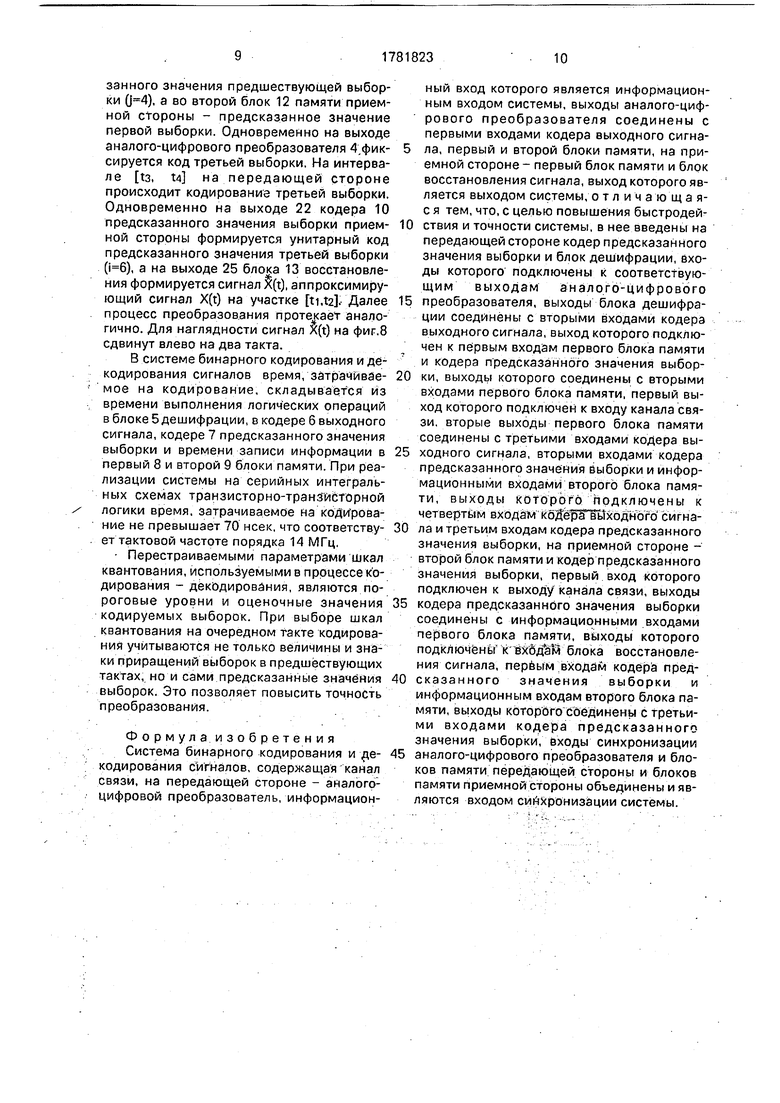

На фиг.1 приведена структурная схема системы; на фиг.2 - структура блока дешифрации; на фиг.З - структура кодера выходного сигнала; на фиг.4 - структура кодера предсказанного значения выборки; на фиг.5

-функциональная схема первого и второго блоков памяти с цепью управления; на фиг.б

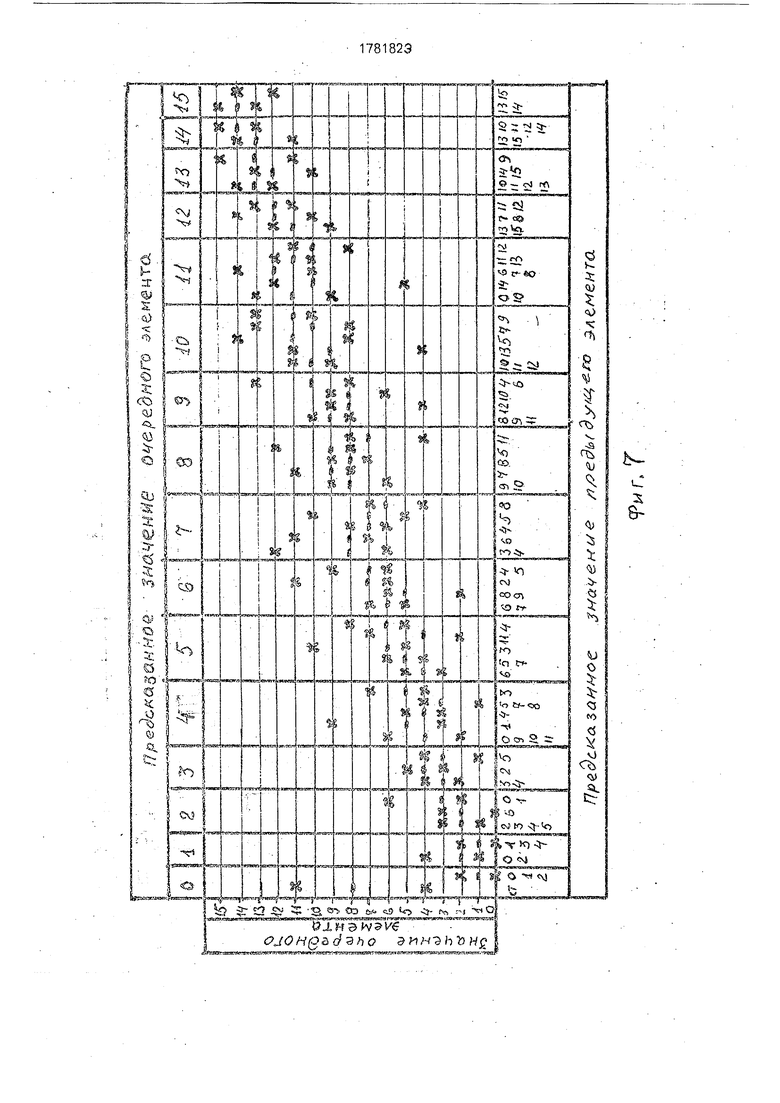

-схема (а) и временная диаграмма (б) работы блока формирования сигналов управления; на фиг.7 - таблица шкал квантования, используемых в рассматриваемом примере реализации системы; на фиг 8 -диаграмма, поясняющая работу системы; на фиг.9 - структура блока восстановления.

Система бинарного кодирования и декодирования сигналов состоит из передающей 1 и приемной 2 сторон, связанных между собой через канал связи 3. Передающая сторона 1 содержит аналого-цифровой преобразователь 4, блок 5 дешифрации, кодер б выходного сигнала, кодер 7 предсказанного значения выборки, первый 8 и второй 9 блоки памяти. Приемная сторона 2

содержит кодер 10 предсказанного значения выборки, первый 11 и второй 12 блоки памяти, блок 13 восстановления сигналов. Первый вход аналого-цифрового преобразователя 4 соединен с информационным

входом 14 системы, а выход 15 - с входом блока 5 дешифрации и с первым входом кодера 6 выходного сигнала. Выход 16 блока 5 дешифрации соединен с вторым входом кодера 6 выходного сигнала, выход 17 которого соединен с первым входом первого блока 8 памяти и с входом кодера 7 предсказанного значения выборки, соединенного выходом 18с вторым входом первого блока 8 памяти. Первый выход 19 первого блока 8

памяти является выходом передающей стороны, а второй выход 20 соединен с третьим входом кодера б выходного сигнала, с вторым входом кодера 7 предсказанного значения выборки и с первым входом второго

блока 9 памяти. Выход 21 второго блока 9 памяти соединен с четвертым входом кодера б выходного сигнала и с третьим входом кодера 7 предсказанного значения выборки. Вход приемной стороны 2 соединен с

входом кодера 10 предсказанного значения выборки, соединенного выходом 22 с первым входом первого блока 11 памяти, выход которого соединен с первым входом второго блока 12 памяти, с входом блока 13

восстановления сигнала и с вторым входом кодера 10 предсказанного значения выборки, третий вход которого соединен с выходом 24 второго блока 12 памяти. Выход 25 блока 13 восстановления сигнала является

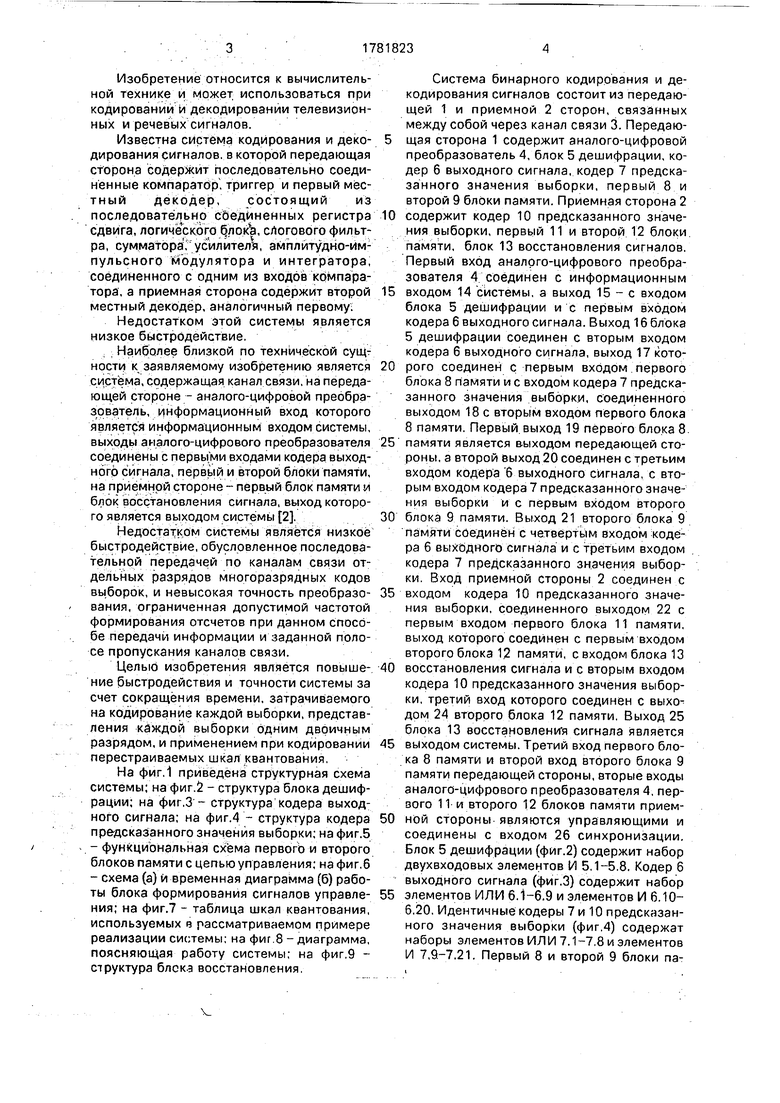

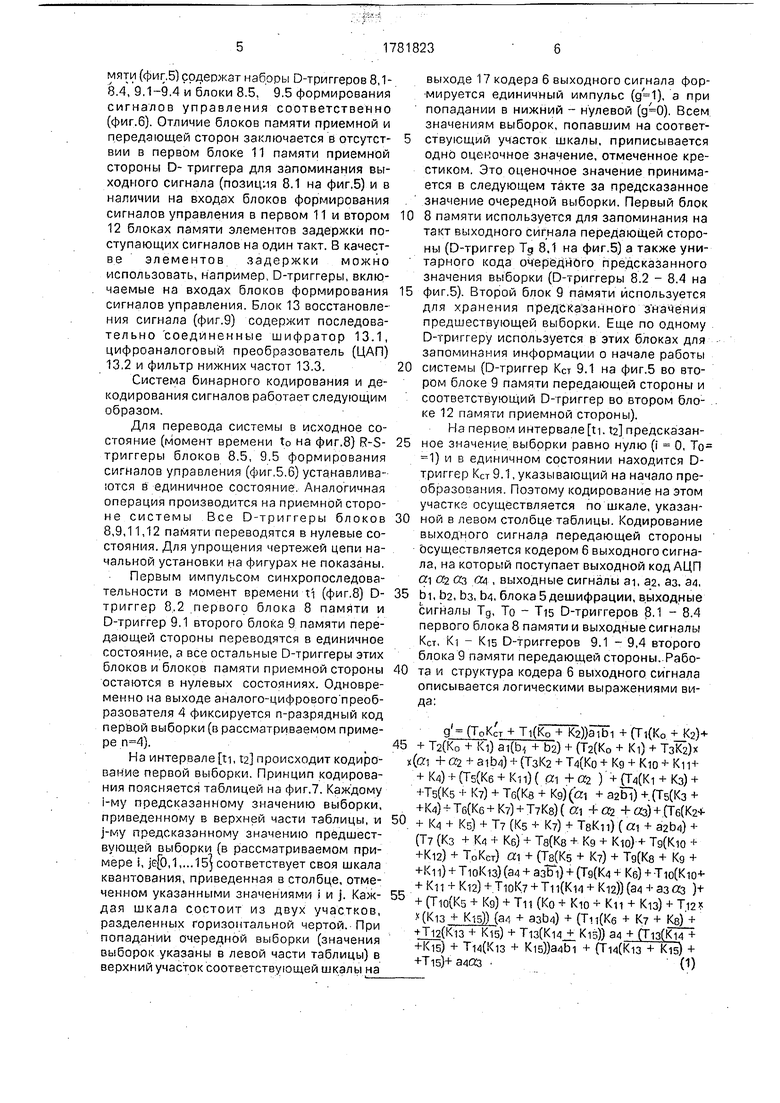

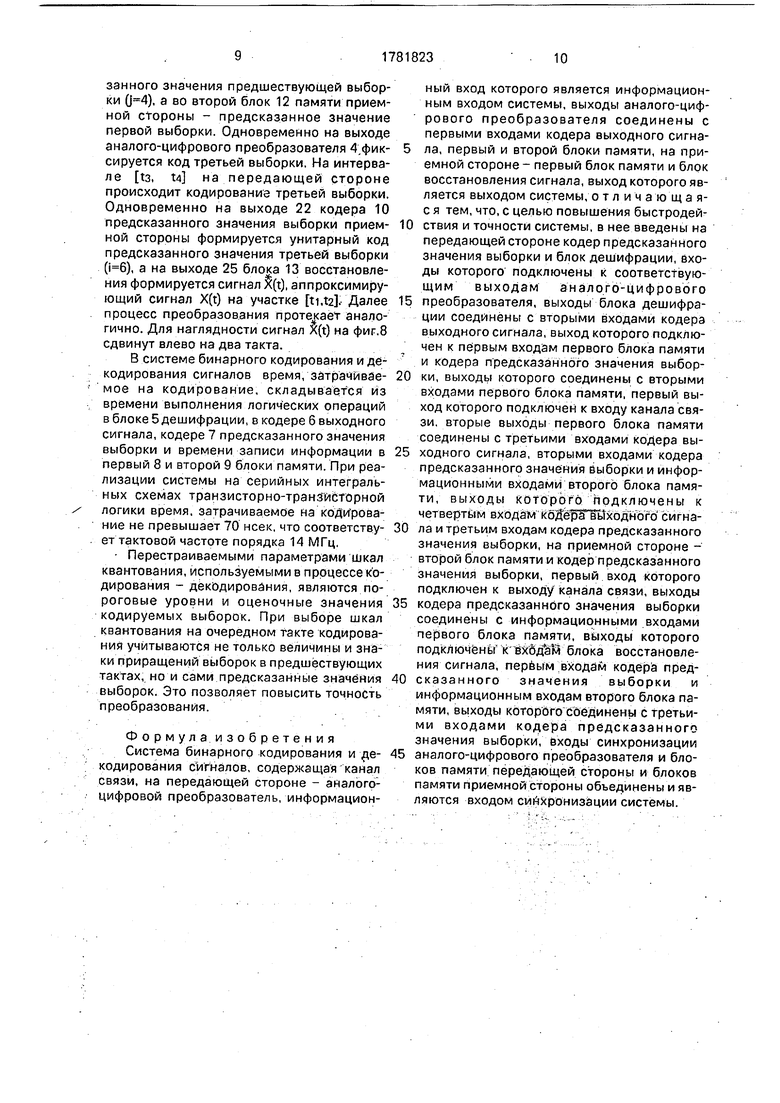

выходом системы. Третий вход первого блока 8 памяти и второй вход второго блока 9 памяти передающей стороны, вторые входы аналого-цифрового преобразователя 4, первого 11 и второго 12 блоков памяти приемной стороны являются управляющими и соединены с входом 26 синхронизации. Блок 5 дешифрации (фиг.2) содержит набор двухвходовых элементов И 5.1-5.8. Кодер 6 выходного сигнала (фиг.З) содержит набор

элементов ИЛИ 6.1-6,9 и элементов И 6.10- 6.20. Идентичные кодеры 7 и 10 предсказанного значения выборки (фиг.4) содержат наборы элементов ИЛ И 7.1-7.8 и элементов И 7,9-7.21. Первый 8 и второй 9 блоки памяти (фиг.5) содержат наРоры D-триггеров 8,1- 8.4, 9,1-9.4 и блоки 8.5, 9.5 формирования сигналов управления соответственно (фиг.6). Отличие блоков памяти приемной и передающей сторон заключается в отсутствии в первом блоке 11 памяти приемной стороны D- триггера для запоминания выходного сигнала (позиция 8.1 на фиг.5) и в наличии на входах блоков формирования сигналов управления в первом 11 и втором 12 блоках памяти элементов задержки поступающих сигналов на один такт. В качестве элементов задержки можно использовать, например, D-триггеры, включаемые на входах блоков формирования сигналов управления. Блок 13 восстановления сигнала (фиг.9) содержит последовательно соединенные шифратор 13.1, цифроаналоговый преобразователь (ЦАП) 13,2 и фильтр нижних частот 13.3.

Система бинарного кодирования и декодирования сигналов работает следующим образом.

Для перевода системы в исходное состояние (момент времени to на фиг.8) R-S- триггеры блоков 8.5, 9.5 формирования сигналов управления (фиг.5,6) устанавливаются в единичное состояние. Аналогичная операция производится на приемной сторо- не системы Все D-триггеры блоков 8,9,11,12 памяти переводятся в нулевые состояния. Для упрощения чертежей цепи начальной установки на фигурах не показаны.

Первым импульсом синхропоследова- тельности в момент времени ti (фиг.8) D- триггер 8.2 первого блока 8 памяти и D-триггер 9.1 второго блока 9 памяти передающей стороны переводятся в единичное состояние, а все остальные D-триггеры этих блоков и блоков памяти приемной стороны остаются в нулевых состояниях. Одновременно на выходе аналого-цифрового преобразователя 4 фиксируется n-разрядный код первой выборки (в рассматриваемом примере ).

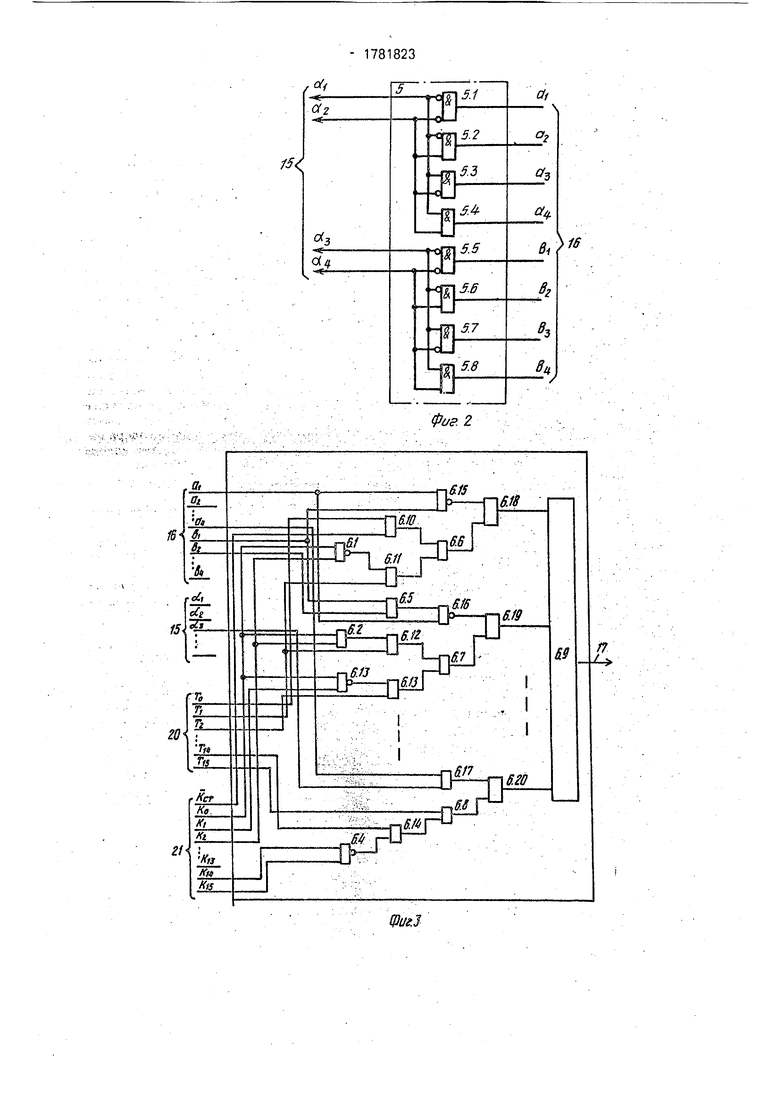

На интервале ti, 12} происходит кодирование первой выборки. Принцип кодирования поясняется таблицей на фиг,7. Каждому i-му предсказанному значению выборки, приведенному в верхней части таблицы, и j-му предсказанному значению предшествующей выборки (в рассматриваемом примере i, ,1,... 15) соответствует своя шкала квантования, приведенная в столбце, отмеченном указанными значениями i и j. Каждая шкала состоит из двух участков, разделенных горизонтальной чертой. При попадании очередной выборки (значения выборок указаны в левой части таблицы) в верхний участок соответствующей шкалы на

выходе 17 кодера 6 выходного сигнала формируется единичный импульс (), а при попадании в нижний - нулевой (). Всем значениям выборок, попавшим на соответ- 5 ствующий участок шкалы, приписывается одно оценочное значение, отмеченное крестиком. Это оценочное значение принимается в следующем такте за предсказанное значение очередной выборки. Первый блок

0 8 памяти используется для запоминания на такт выходного сигнала передающей стороны (D-триггер Tq 8,1 на фиг.5) а также унитарного кода очередного предсказанного значения выборки (D-триггеры 8.2 - 8.4 на

5 фиг.5). Второй блок 9 памяти используется для хранения предсказанного З начения предшествующей выборки. Еще по одному D-триггеру используется в этих блоках для запоминания информации о начале работы

0 системы (D-триггер Кет 9.1 на фиг.5 во втором блоке 9 памяти передающей стороны и соответствующий D-григгер во втором блоке 12 памяти приемной стороны).

На первом интервале ti. 12 предсказан5 ное значение выборки равно нулю (i 0, То 1) и в единичном состоянии находится D- триггер Кет 9.1, указывающий на начало преобразования. Поэтому кодирование на этом участке осуществляется по шкале, указан0 ной в левом столбце таблицы. Кодирование выходного сигнала передающей стороны осуществляется кодером 6 выходного сигнала, на который поступает выходной код АЦП а с&аз СЦ , выходные сигналы ai, az, аз, 34,

5 bi, , Ьз, b4, блока 5 дешифрации, выходные сигналы Тд, То - Tis D-триггеров 8.1 - 8.4 первого блока 8 памяти и выходные сигналы Кет, Ki - KIS D-триггеров 9.1 - 9,4 второго блока 9 памяти передающей стороны. Рабо0 та и структура кодера б выходного сигнала описывается логическими выражениями вида:

д (ТоКст + Ti())a7bi + (Ti(K0 )+ 5 + Т2(К0 + Ki) ai(b + ba) + (К0 + Ki) + T3K2)x x(ai + аг + aiN) + (ТзК2 + TXKo + Kg + Кю + Kn+ + M f (Тб(Кб + Kn) ( ai + oa ) + OXKi + K3) + (К5 -i- Ky) + Тб(К8 + Кэ)(Д1 + aabi) + (Т5(Кз + +К«) -- Тб(К6 + К) + TyKs) ( щ + аг + од) + (Т6(К2ч- + К4 + КБ) + Ту (Кб + Ку) + ТвКп) («1 + 32b4) + (Ту (Кз + К4 i Кб) + Ta(KS + Kg + Кю) + Тд(Кю + +К12) + ТоКст) «1 + OXKs + К) + Тд(К8 + Kg + +Kn) + TioKi3)(a4 + a3bi) + (T9(K4+K6) + Tio(Kio-«- + Ki i + Ki2) + ТюКу + Ti i(Ki4 + Ki2)) (34 + аз аз }+ 5 + (Тю(К5 + Kg) + In (Ко + Кю + Kn + KIS) + Ti2 (K13 + Kis)) (34 + азЬ4) + (Tii(Ke + Ky + Ks) +

+ T12(K13 + K15) + T13( К15)) 34 + (T13(K14 + +Kis) + T14(K13 + Kl5))34bl + (T14(K13 + Kis) + +Ti5)+a403 (1)

0

Сигналы, соответствующие переменным а и Ь, используемым в этом выражении, формируются на выходе 16 блока 5 дешифрации, работа и структура которого описываются формулами:5

Ь1 03(24 Ь2 ОЗОД Ьз «3«4 D4 «3 ОСА (2)

В результате обработки на выходе 17 кодера 6 выходного сигнала формируется сигнал д , соответствующий участку шкалы, внутри которого находится код первой выборки (в нашем примере д 0). Этот сигнал поступает одновременно на D-вход D-триг- гера 8,1 первого блока 8 памяти и на вход кодера 7 предсказанного значения выборки. На другие входы кодера 7 предсказание- го значения выборки подается унитарный код ToTi.,.Ti5 предсказанного значения выборки (на первом интервале - это код 100...0) и код КСтКоК1...К15 с выхода 21 второго блока 9 памяти. На первом интервале - это код 100...0. Работа и структура кодера предсказанного значения выборки описывается логическими выражениями:

Т о СТоКТт + Ti(Kp + К2) +

T i (Ti(Ko + K2) + Т2(Ко + Ki + Кб) + ТзК5 + +Тл(К5 + К ))g 1

Т 2 (ТоКсг + Ti(Ko + К2))д + (Т2(Ко + Ki) + +Тз(Кз + К4) + Т4(Ко + Kg + Кю + Kn) + TsKn + +Т6(К8 + Кд))д

Т з (Т2(Ко + Ki -|- Кб) + Г2К6)д + (ТзК2 + +T4(Ki + Ю|) + ТдКб)д

Т 4 (Ti(Ko - К2) + Тз (Кз + К4 + Ks) + Т4(Кв+

+ к + Ks))g + (ТоКст + т4Кз + т5(к51- к) + Т7к8

+ T8Kn+TgKi2 + TioKi3)g

Т 5 (Т3К2 f Т4К4 + Т5Кб)д + (Т5(Кз + К4) +

+Тб(Кб + К7) + + тпК14)д

Т б (Т2(К0 + Ki) + Т4(Ко 4 Kg -t Кю + Kn) + +Т5(К5 + К) + Т6(К8 + Kgjg1 + (Т6(К2 + К4 + К5) + +Т(Кз + К4 + К) + Т8(Кд + Кю) + ТэКюЙ1

Ту (T4K3J ТбКп + Тб(Кв + К) + Т7К8)д +

+{Т7Кб + Т8К8)д

Та - (Т5К4 + Т7К7 + ТвКц)д + (Т8(К5 + К7 + T9(Kio+Ki2HTio(Ks + K7))g

Т э (Т4К1 - Т6(К4 + Ks) + Т8(К8 + Kg + Кю)+ + T9(Ko + Ki2))g + (Tio(Kio+Kii + Ki2) + Tii(Ko+ + K10) + T12(Ki3+Ki5))g

Т ю (Т5Кз н Т7К5 + Тд(К8 + Kg ч Кц))д + -КТюКэ + Тц(Ке + К + Кв + Ki i + Ki3) + Ti2 (К7+ + К8) + Ti3(Ki4 - Kis))g

Тц(Т0Кст-ИбК2 + Т7Кб+ ТвК7+Тю(Кю+ Kn + Ki2 + Km) + TnKi2) g + (Kii + Kiz) + +Ti3Kg + Ti4(Kir. + Ki5))g

0

5

5

5

0

0

о

5

0

5

Т 12 (T7(K3 + M + T8K5 + Tii(Kn + Ki3 + +Км) + Ti2(Ki3 + Kis))g + (Ti3(Kg + Ki4 + Ki5) + - Ti5Ki5)g

T i3 (Tg(K4 + K6) + Тю (K + Kg) + Tn(Kp + +Kio) + Ti2(K 11 + Ki2) + Tis(Ki4 + К1ф + (Ti/i( + К15)+ )5

Т 14 (ТюК5 + Tii(Ke + K7 + KB) + T12(K7 + +K8) + Ti3(K9 + Км + Kis) + Ti4(Ki3 + Kis) + +Ti5Ki5)g

T l5 (Tl3K9 + Tl4(K13+Kl5) + Tl5Kl5)g (3)

В результате выполнения указанных вычислений на выходе 18 кодера 7 предсказанного значения выборки формируется унитарный код Т1 оТ - T 2...T i5 (в нашем случае - это код четырех : 000010...0). Таким образом, к концу первого такта на D-вход соответствующего D-триггера первого блока 8 памяти подается единичный сигнал. Единичный сигнал присутствует в это время и на D-входе D-триггера 9.2 второго блока 9 памяти. Следующим тактовым импульсом в момент времени t2 указанные триггеры переводятся в единичное состояние. Одновременно в единичное состояние устанавливаются D-триггеры То и Кет первого 11 и второго 12 блоков памяти приемной стороны. Таким образом, состояние D-триггеров первого 11 и второго 12 блоков памяти приемной стороны повторяют состояния соответствующих триггеров первого 8 и второго 9 блоков памяти передающей стороны в предшествующем такте. Все остальные триггеры блоков памяти переводятся в нулевые состояния. Одновременно на выходе 15 аналого-цифрового преобразователя 4 фиксируется код второй выборки.

В соответствии с таблицей на фиг.7 кодирование на интервале t2, ts осуществляется по шкале, соответствующей предсказанному значению выборки, равному четырем () и нулевому предсказанному значению предшествующей выборки ). На этом интервале на выходе 17 кодера выходного сигнала 6 формируется сигнал д 1, а на выходе 18 кодера 7 предсказанного значения выборки унитарный код ToT i...T 6...T i5 (00000010.,.0), соответствующий i 6. Одновременно с выхода 23 первого блока 11 памяти приемной стороны снимается унитарный код предсказанного значения первой выборки, а на входах D-триггеров этого блока формируется унитарный код предсказанного значения второй выборки. Следующим тактовым импульсом в момент ts в первый блок 8 памяти заносится унитарный код предсказанного значения очередной выборки (i 6), а во второй блок 9 памяти передающей стороны и первый блок 11 памяти приемной стороны заносится унитарный код предсказанного значения предшествующей выборки (), а во второй блок 12 памяти приемной стороны - предсказанное значение первой выборки. Одновременно на выходе аналого-цифрового преобразователя 4 фиксируется код третьей выборки. На интервале ts, t/i на передающей стороне происходит кодирование третьей выборки. Одновременно на выходе 22 кодера 10 предсказанного значения выборки приемной стороны формируется унитарный код предсказанного значения третьей выборки ), а на выходе 25 блока 13 восстановления формируется сигнал (t), аппроксимирующий сигнал X(t) на участке ti.ta. Далее процесс преобразования протекает аналогично. Для наглядности сигнал X(t) на фиг.8 сдвинут влево на два такта.

В системе бинарного кодирования и декодирования сигналов время, затрачиваемое на кодирование, складывается из времени выполнения логических операций в блоке 5 дешифрации, в кодере 6 выходного сигнала,кодере 7 предсказанного значения выборки и времени записи информации в первый 8 и второй 9 блоки памяти. При реализации системы на серийных интегральных схемах транзисторно-транзисторной логики время, затрачиваемое на кодирование не превышает 70 нсек, что соответствует тактовой частоте порядка 14 МГц.

Перестраиваемыми параметрами шкал квантования, используемыми в процессе кодирования - декодирования, являются пороговые уровни и оценочные значения кодируемых выборок. При выборе шкал квантования на очередном такте кодирования учитываются не только величины и знаки приращений выборок в предшествующих тактах, но и сами предсказанные значения выборок. Это позволяет повысить точность преобразования.

Формула изобретения Система бинарного кодирования и декодирования сигналов, содержащая канал связи, на передающей стороне - аналого- цифровой преобразователь, информационный вход которого является информационным входом системы, выходы аналого-цифрового преобразователя соединены с первыми входами кодера выходного сигна- 5 ла, первый и второй блоки памяти, на приемной стороне - первый блок памяти и блок восстановления сигнала, выход которого является выходом системы, отличающая- с я тем, что, с целью повышения быстродей0 ствия и точности системы, в нее введены на передающей стороне кодер предсказанного значения выборки и блок дешифрации, входы которого подключены к соответствующим выходам аналого-цифрового

5 преобразователя, выходы блока дешифрации соединены с вторыми входами кодера выходного сигнала, выход которого подключен к первым входам первого блока памяти и кодера предсказанного значения выбор0 ки, выходы которого соединены с вторыми входами первого блока памяти, первый выход которого подключен к входу канала связи вторые выходы первого блока памяти соединены с третьими входами кодера вы5 ходного сигнала, вторыми входами кодера предсказанного значения выборки и информационными входами второго блока памяти, выходы которого подключены к четвертым входам кбд ёр1ПШходного сигна0 ла и третьим входам кодера предсказанного значения выборки, на приемной стороне - второй блок памяти и кодер предсказанного значения выборки, первый вход которого подключен к выходу канала связи, выходы

5 кодера предсказанного значения выборки соединены с информационными входами первого блока памяти, выходы которого подключены к входШ блока восстановления сигнала, первым входам кодера пред0 сказанного значения выборки и информационным входам второго блока памяти, выходы которого соединены с третьими входами кодера предсказанного значения выборки, входы синхронизации

5 аналого-цифрового преобразователя и блоков памяти передающей стороны и блоков памяти приемной стороны объединены и являются входом синхронизации системы.

2f

VueS

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство передачи и приема цифрового телевизионного сигнала | 1988 |

|

SU1681406A1 |

| Система передачи телевизионного сигнала с дифференциальной импульсно-кодовой модуляцией | 1988 |

|

SU1575324A1 |

| ВОСЬМИЗНАЧНОЕ УСТРОЙСТВО ПРИЕМА И ПЕРЕДАЧИ ДАННЫХ | 1992 |

|

RU2012061C1 |

| Устройство для сжатия цифровых телевизионных сигналов | 1983 |

|

SU1107319A1 |

| Система передачи информации с решающей обратной связью | 1984 |

|

SU1167746A1 |

| УСТРОЙСТВО ДИСТАНЦИОННОЙ СИГНАЛИЗАЦИИ | 1992 |

|

RU2032229C1 |

| МНОГОПАРАМЕТРИЧЕСКАЯ АДАПТИВНАЯ СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 2010 |

|

RU2441330C1 |

| Устройство для передачи информации со сжатием данных | 1978 |

|

SU746672A1 |

| Устройство кодирования и декодирования | 1988 |

|

SU1663777A1 |

| СПОСОБ КОМПРЕССИИ-ДЕКОМПРЕССИИ ДАННЫХ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2011 |

|

RU2488960C2 |

Изобретение относится k вычислительной технике. Его использование для кодирования и декодирования телевизионных и речевых сигналов позволяет повысить быстродействие и точность системы. Передающая сторона 1 содержит аналого-цифровой преобразователь 4, кодер 6 выходного CHI нала и блоки 8,9 памяти Приемная сторона 2 содержит блок 11 памяти и блок 13 восстановления. Благодаря введению на передающей стороне 1 блока 5 дешифрации и кодера 7 предсказанного значения выборки, а на приемной стороне 2 - кодера 10 предсказанного значения выборки и блока 12 памяти, в системе обеспечивается представление каждой выборки одним двоичным разрядом с применением перестраиваемых шкал квантования.9 ил.

JL

Ш

ери г. 6

/

А

s&

stv (- «g -t ffa 5 со «э «5 2; иг Ј2 -5

nfrtt гу-- Улц Дт /- - 1 j&asjups3KGfjiaii ib AfjxiKff jicta fijga jjaaitiJjaju btatJit asui

-9 х

i

W

N

Ј29 tea

13

li ki j- у U I

I I I I 1 I I IJ I

Ло| ОрГ|7 0|оМ 14 1

ol

и LJ I Ш

И1 71о|оГ7ПГ :

И:2г

Фыг.8

ft/Г 3

| Котович Т.Н., Ламекин В.Ф Проектирование дельта-преобразователей речевых сигналов | |||

| - М.: Радио и связь, 1986, стр | |||

| Способ изготовления звездочек для французской бороны-катка | 1922 |

|

SU46A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Полунавесная дисковая борона | 1960 |

|

SU133697A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-12-15—Публикация

1990-11-14—Подача