Изобретение относится к автоматике и вычислительной технике и предназначено для использования в позиционных системах программного управления.

Известно устройство для программного управления содержащее блок памяти, счетчик импульсов, счетчик адреса, генератор, первый и второй регистры, триггер, первый и второй элементы ИЛИ, элемент И.

Недостатком этого устройства является невозможность формирования управляющих сигналов произвольной длительности на обьект управления.

Известно устройство управления, содержащее блок памяти, регистр адреса, счетчик, триггер микрокоманд, элементы И, ИЛИ, НЕ задержки генератор.

Недостатками этого устройства являются контроль выполнения только одного ждущего логического условия, невозможность проверки обычных логических условий, невозможность проверки ждущих логических условий с различными допустимыми интервалами времени ожидания, переход при невыполнении ждущего логического условия (за допустимый временной интервал) по фиксированному адресу, что увеличивает временной интервал) по фиксированному адресу, что увеличивает время восстановления процесса управления.

Наиболее близким к предлагаемому устройству по технической сущности и достигаемому положительному эффекту является устройство для программного управления, содержащее генератор, блок памяти счетVI

со

ю со ю

чик адреса, счетчик импульсов, первый и второй регистры, триггер, первый-третий элементы ИЛИ, первый-третий элементы И, элемент НЕ, первый и второй элементы задержки, мультиплексор, причем второй эле- мент задержки подключен входом к выходу формирователя импульсов и к первому управляющему входу мультиплексора, а выходом к входу обнуления первого регистра, соединённого вторым информационным вхЪдом с выходом второго элемента ИЛИ, а разрядными Выходами - с первым информа- ци оннйм йходбм мультиплексора, связанного вторыми информационными входами устройства, вторым управляющим входом - с входом запуска устройства, а выходами - с входами первого элемента ИЛИ и с установочными входами счетчика адреса, подключенного счетным входом к выходу второго элемента И, соединенного первым входом с выходом первого элемента задержки, а прямым входом - с прямым входом триггера и с первым входом третьего элемента И, связанного вторым входом с выходом генератора тактовых импульсов, выходом - с входом первого элемента задержки и с управляющим входом блока па мяти, а третьим выходом с выходом элемента НЕ, подключенного входом к второму входу первого элемента И и к выходу третьего элемента ИЛИ, связанного входами с разрядными входами счетчика импульсов, подключенного установочными входами к третьим информационным выходам блока памяти, соединенного управляю- щим выходом с входом обнуления триггера и входом формирователя импульса, причем вход второго элемента ИЛИ подключен к второму информационному входу устройства.

Недостатками устройства-прототипа являются ограниченная область применения, низкая достоверность функционирования.

Ограниченная область применения уст- ройства обусловлена тем, что в устройстве не проверяются ждущие логические условия и изменение CHI налов логических условий никак не влияет на момент окончания выполняемой команды. Кроме того, в про- цессе функционирования устройства не осуществляется селекция сигналов логических условий, что позволяет использовать устройство-прототип только для реализации простых алгоритмов контроля и управле- ния.

Низкая достоверность функционирования обусловливается отсутствием в устрой- стве-прототипе средств контроля правильности формирования управляющих

сигналов В то же время в процессе выдачи управляющих сигналов на выходе 22 устройства большинство элементов и узлов устройства простаиваети не контролируется их исправность.

Целью изобретения является расширение области применения устройства и повышение достоверности функционирования.

CyaiHocTb изобретения заключается: в расширении области применения устройства путем придания устройству свойства контроля множества простых логических условий и множества ждущих логических условий с различным временем ожидания вы- полнения; обеспечения окончания выполнения очередной команды в момент выполнения Проверяемого ждущего логического условий; перехода к подпрограмме восстановления процесса управления при невыполнении ждущего логического условия за допустимый интервал времени; в по- вышении- достоверности функционирования устройства- путем контроля о интервале ожидания выполнения проверяемого ждущего логического условия содержимого ячеек блока памяти .останова устройства при возникновении искажения информации, принадлежащей сегменту памяти, где размещена выполняемая программа,

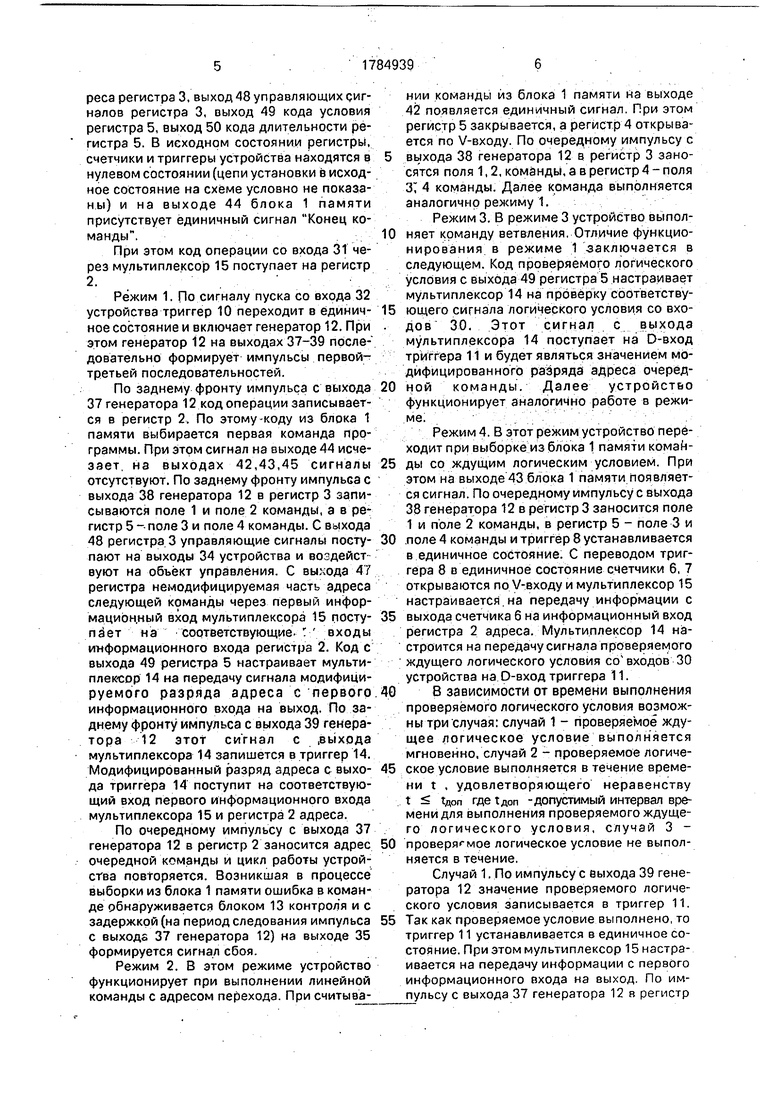

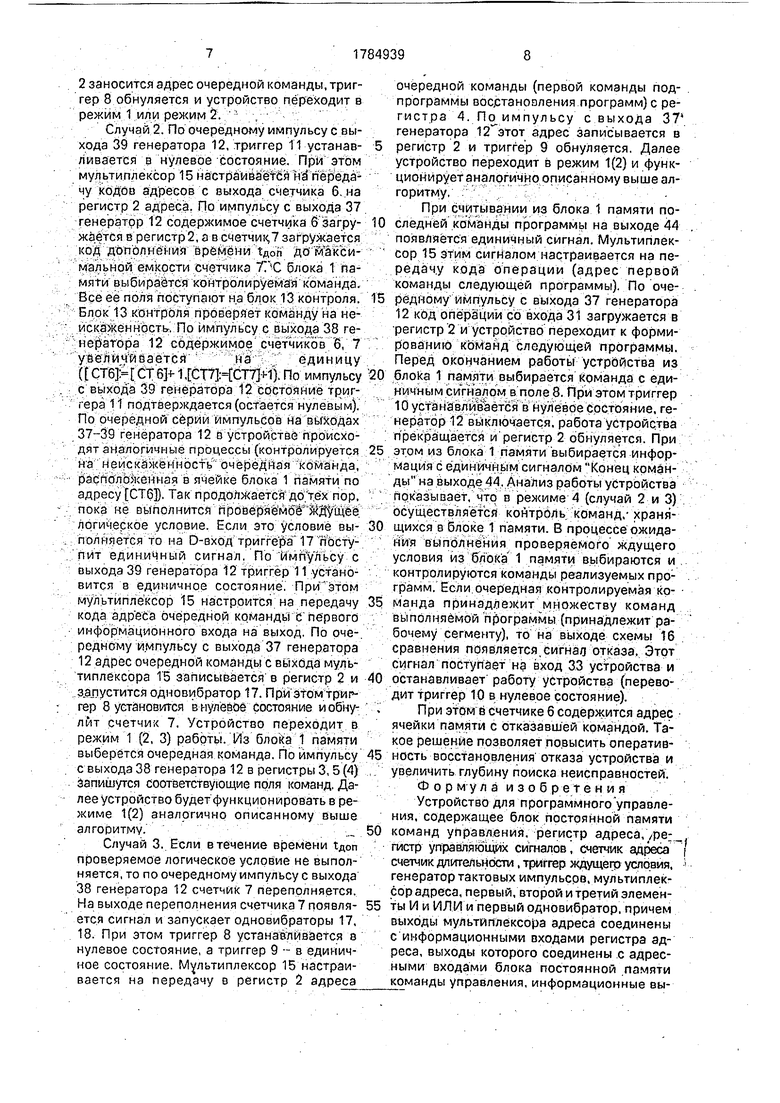

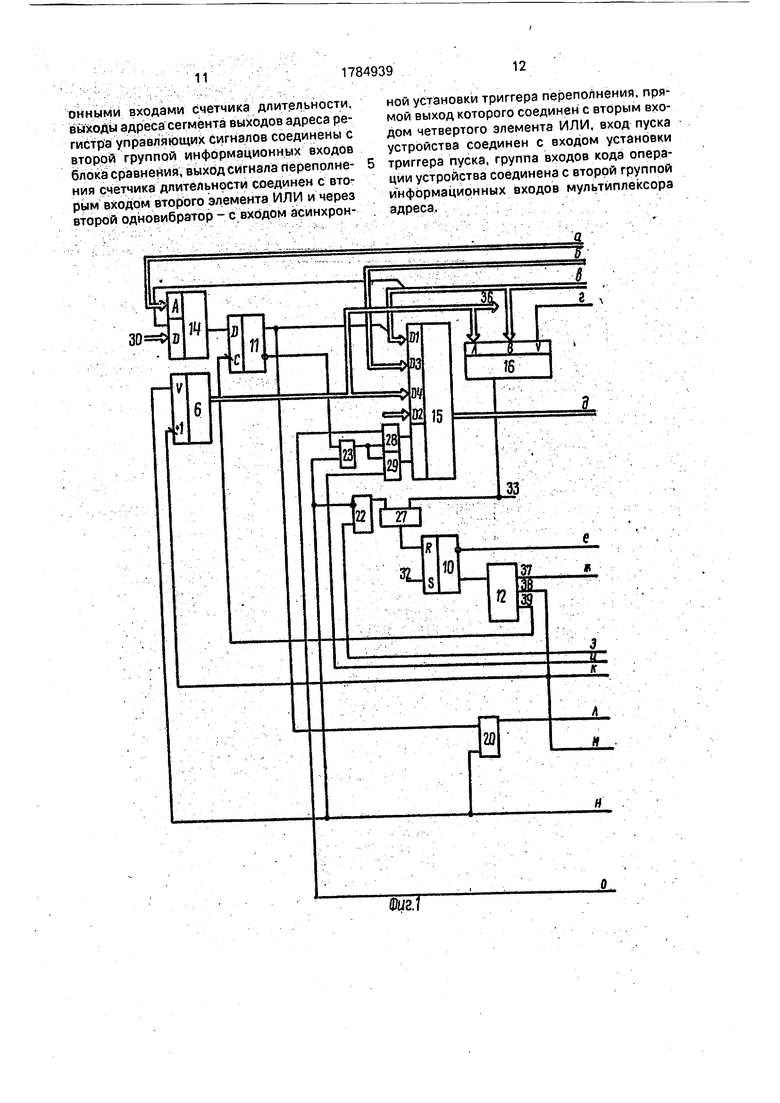

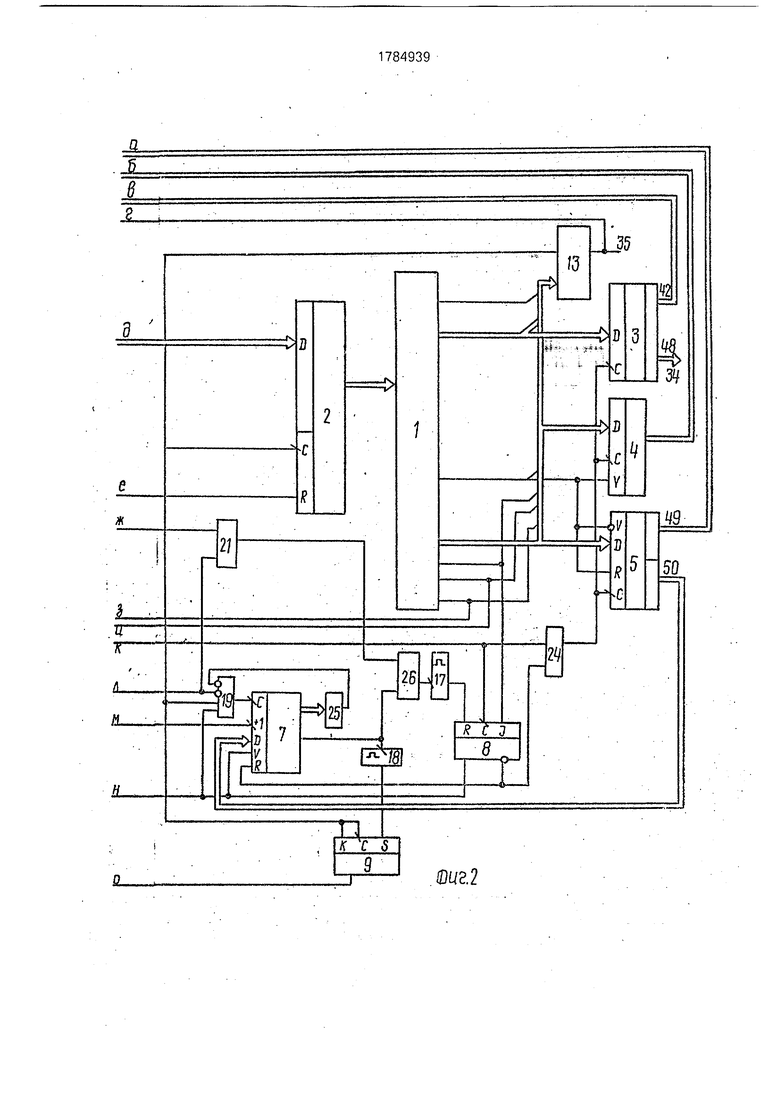

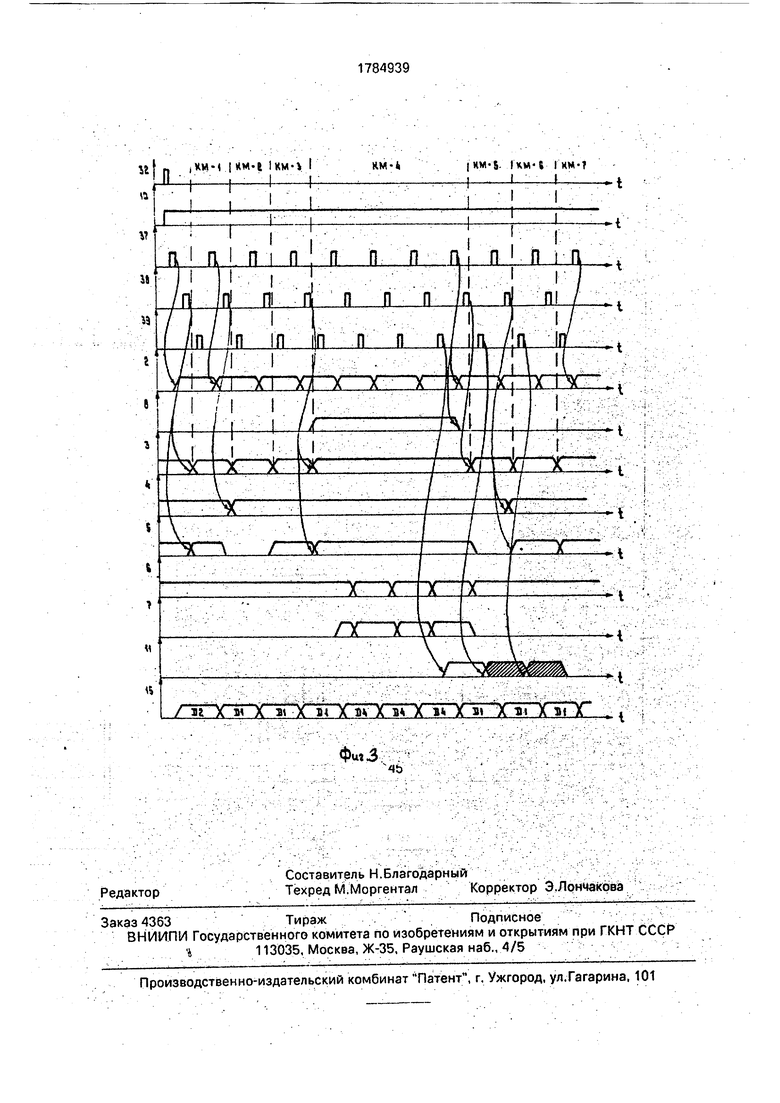

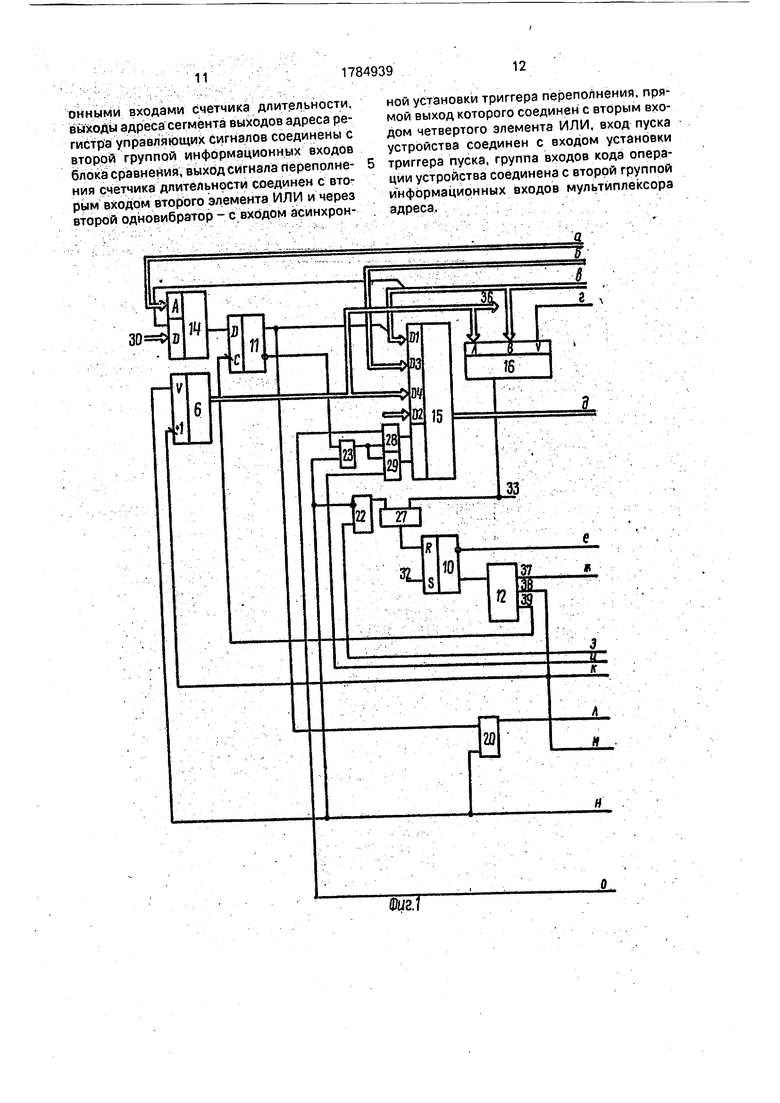

На фиг.1 и 2 приведена функциональная схема устройства; на фиг.З - временные диаграммы работы устройства.

Самоконтролируемое устройство для программного управления (фиг.1) содержит блок 1 постоянной памяти команд управления с информационными выходами 40, выходами 41 кода логического условия и времени ожидания, выходом 42 сигнала перехода, выходом 43 сигнала ждущего условия, выходом сигнала конца программы, выходом 45 сигнала конца работы устройства, выходом 46 контрольного разряда, регистр 2 адреса, регистр 3 управляющих сигналов, регистр 4 адреса перехода, регистр 5 условия,счетчик 6 адреса,счетчик 7 длительности, триггер 8 ждущего условия, триггер 9 переполнения, триггер 10 пуска, триггер 11 проверяемого условия, генератор 12 с первым - третьим выходами 27-39. блок 13 контроля на четность, мультиплексор 14 условий, мультиплексор 15 адреса, схему 16 сравнения, первый и второй одно- вибраторы 17, 18 первый-шестой элементы 19-24, первый-пятый элементы ИЛИ 25-29, входы 30 сигналов логических условий, вход 31 кода операций, вход 32 пуска, вход 33 сигнала останова при отказе, выход 34 управляющих сигналов, выход 35 сигнала сбоя, выход 36 адреса отказа, выход 47 адреса регистра 3, выход 48 управляющих риг- налов регистра 3, выход 49 кода условия регистра 5, выход 50 кода длительности регистра 5. В исходном состоянии регистры, счетчики и триггеры устройства находятся в нулевом состоянии (цепи установки в исходное состояние на схеме условно не показа- ны) и на выходе 44 блока 1 памяти присутствует единичный сигнал Конец команды.

При этом код операции со входа 31 через мультиплексор 15 поступает на регистр 2.

Режим 1, По сигналу пуска со входа 32 устройства триггер 10 переходит в единичное состояние и включает генератор 12. При этом генератор 12 на выходах 37-39 последовательно формирует импульсы первой- третьей последовательностей.

По заднему фронту импульса с выхода 37 генератора 12 код операции записывается в регистр 2. По этому-коду из блока 1 памяти выбирается первая команда программы. При этом сигнал на выходе 44 исче- зает на выходах 42,43,45 сигналы отсутствуют. По заднему фронту импульса с выхода 38 генератора 12 в регистр 3 записываются поле 1 и поле 2 команды, а в регистр 5 - поле 3 и поле 4 команды. С выхода 48 регистра 3 управляющие сигналы поступают на выходы 34 устройства и восдейст вуют на объект управления. С выхода 4 регистра немодифицируемая часть адреса следующей команды через первый информационный вход мультиплексора 15 посту- па е т на соответствующие. входы информационного входа регистра 2. Код с выхода 49 регистра 5 настраивает мультиплексор 14 на передачу сигнала модифицируемого разряда адреса с первого информационного входа на выход. По заднему фронту импульса с выхода 39 генера- тора 12 этот си гнал с .выхода мультиплексора 14 запишется в триггер 14. Модифицированный разряд адреса с выхода триггера 14 поступит на соответствующий вход первого информационного входа мультиплексора 15 и регистра 2 адреса.

По очередному импульсу с выхода 37 генератора 12 в регистр 2 заносится адрес очередной команды и цикл работы устройства повторяется. Возникшая в процессе выборки из блока 1 памяти ошибка в команде обнаруживается блоком 13 контроля и с задержкой (на период следования импульса с выходе 37 генератора 12) на выходе 35 формируется сигнал сбоя.

Режим 2. В этом режиме устройство функционирует при выполнении линейной команды с адресом перехода. При считывании команды из блока 1 памяти на выходе 42 появляется единичный сигнал. При этом регистр 5 закрывается, а регистр 4 открывается по V-входу. По очередному импульсу с 5 выхода 38 генератора 12 в регистр 3 заносятся поля 1,2, команды, а в регистр 4 - поля 31 4 команды. Далее команда выполняется аналогично режиму 1.

Режим 3. В режиме 3 устройство выпол0 няет команду ветвления, Отличие функционирования в режиме 1 -заключается в следующем. Код проверяемого логического условия с выхода 49 регистра 5 настраивает мультиплексор 14 на проверку соответству5 ющего сигнала логического условия со входов 30. Этот сигнал с выхода мультиплексора 14 поступает на D-вход триггера 11 и будет являться значением модифицированного разряда адреса очеред0 ной команды. Далее устройство функционирует аналогично работе в режиме.

Режим 4. В этот режим устройство переходит при выборке из блока 1 памяти комай5 ды со ждущим логическим условием. При этом на выходе 43 блока 1 памяти появляется сигнал. По очередному импульсу с выхода 38 генератора 12 в регистр 3 заносится поле 1 и поле 2 команды, в регистр 5 - поле 3 и

0 поле 4 команды и триггер 8 устанавливается в единичное состояние. С переводом триггера 8 в единичное состояние счетчики 6, 7 открываются по V-входу и мультиплексор 15 настраивается на передачу информации с

5 выхода счетчика б на информационный вход регистра 2 адреса. Мультиплексор 14 настроится на передачу сигнала проверяемого ждущего логического условия со входов 30 устройства на D-вход триггера 11.

0 В зависимости от времени выполнения проверяемого логического условия возможны три случая: случай 1 - проверяемое ждущее логическое условие выполняется мгновенно, случай 2 - проверяемое логиче5 ское условие выполняется в течение времени t , удовлетворяющего неравенству t Гдоп где Хдоп -допустимый интервал времени для выполнения проверяемого ждущего логического условия, случай 3 0 проверяемое логическое условие не выполняется в течение.

Случай 1. По импульсу с выхода 39 генератора 12 значение проверяемого логического условия записывается в триггер 11.

5 Так как проверяемое условие выполнено, то триггер 11 устанавливается в единичное состояние. При этом мультиплексор 15 настраивается на передачу информации с первого информационного входа на выход. По импульсу с выхода 37 генератора 12 в регистр

2 заносится адрес очередной команды, триггер 8 обнуляется и устройство переходит в режим 1 или режим 2.

Случай 2. По очередному импульсу с выхода 39 генератора 12, триггер 11 устанавливается в нулевое состояние. При этом мультиплексор 15 настраивается на передачу кодов адресов с выхода счетчика 6 на регистр 2 адреса. По импульсу с выхода 37 генератор 12 содержимое счетчика б загружается в регистр 2, а в счетчик, загружается код дополнения времени гдоп до м акси- мальной емкости счетчика 77 С блока 1 памяти выбирается контролируемая команда, Все ее поля поступают на блок 13 контроля. Блок 13 контроля проверяет команду на не- искаженность-. По импульсу с выхода 38 генератора 12 содержимое счетчиков б, 7 увеличиваетсянаединицу

(f CT6J- СТ 6 1 ,СПНСТ7 И). По импульсу с выхода 39 генератора 12 состояние триггера 11 подтверждается (остается нулевым). По очередной серии импульсов на выходах 37-39 генератора 12 в устройстве происходят аналогичные процессы (контролируется на неискаженность очередная команда, расположенная в ячейке блока 1 памяти по адресу СТ6). Так продолжается до тех пор, пока не выполнится проверяёмбТГжОДщее логическое условие. Если это условие выполняется то на D-вход триггера 17 поступит единичный сигнал, По импульсу с выхода 39 генератора 12 триггер 11 установится в единичное состояние. При этом мультиплексор 15 настроится на передачу кода адреса очередной команды с первого информационного входа на выход. По очередному импульсу с выхода 37 генератора 12 адрес очередной команды с выхода мультиплексора 15 записывается в регистр 2 и запустится одновибратор 17. При этом триггер 8 установится в нулевое состояние и обнулит счетчик 7. Устройство переходит в режим 1 (2, 3) работы. Из блока 1 памяти выберется очередная команда. По импульсу с выхода 38 генератора 12 в регистры 3,5 (4) Запишутся соответствующие поля команд. Далее устройство будет функционировать в режиме 1(2) аналогично описанному выше алгоритму.

Случай 3. Если в течение времени т.ДОп проверяемое логическое условие не выполняется, то по очередному импульсу с выхода 38 генератора 12 счетчик 7 переполняется. На выходе переполнения счетчика 7 появляется сигнал и запускает одновибраторы 17, 18. При этом триггер 8 устанавливается в нулевое состояние, а триггер 9 - в единичное состояние. Мультиплексор 15 настраивается на передачу в регистр 2 адреса

очередной команды (первой команды подпрограммы восстановления программ) с регистра 4. По импульсу с выхода 371 генератора адрес записывается в

регистр 2 и триггер 9 обнуляется. Далее устройство переходит в режим 1(2) и функционирует аналогично описанному выше алгоритму,

При считывании из блока 1 памяти последней команды программы на выходе 44 . появляется единичный сигнал. Мультиплексор 15 этим сигналом настраивается на передачу кода операции (адрес первой команды следующей программы). По очередному импульсу с выхода 37 генератора 12 код операции со входа 31 загружается в регистр 2 и устройство переходит к формированию кЬманд следующей программы. Перед окончанием работы устройства из

блока 1 памяти выбирается команда с единичным сигналом в поле 8. При этом триггер 10 уста на вливается в нулевое состояние, генератор 12 выключается, работа устройства прекращается и регистр 2 обнуляется. При

этом из блока 1 памяти выбирается информация с единичным сигналом Конец команды на выходе 44. Анализ работы устройства показывает, что в режиме 4 (случай 2 и 3) осуществляется контроль команд,- хранящихся в блоке 1 памяти. В процессе ожидания выполнения проверяемого ждущего условия из блока 1 памяти выбираются и контролируются команды реализуемых программ. Если очередная контролируемая команда принадлежит множеству команд выполняемой программы (принадлежит рабочему сегменту), то на выходе схемы 16 сравнения появляется .сигнал отказа. Этот сигнал поступает на вход 33 устройства и

останавливает работу устройства (переводит триггер 10 в нулевое состояние).

При этом в счетчике 6 содержится адрес ячейки памяти с отказавшей командой. Такое решение позволяет повысить оперативиость восстановления отказа устройства и увеличить глубину поиска неисправностей. Формула изобретения Устройство для программного управления, содержащее блок постоянной памяти

команд управления, регистр адреса, /ре: гистр управляющих сигналов, счетчик адреса счетчик длительности, триггер ждущего условия, генератор тактовых импульсов, мультиплексор адреса, первый, второй и третий элементы И и ИЛИ и первый одновибратор. причем выходы мультиплексора адреса соединены с информационными входами регистра адреса, выходы которого соединены с адресными входами блока постоянной памяти

команды управления, информационные выходы которого соединены с информационными входами регистра управляющих сигналов, выходы немодифицированных разрядов которого соединены с входами немодифицированных разрядов адреса первой группы информационных входов мультиплексора адреса, выходы счетчика длительности соединены с входами первого элемента ИЛИ, выход которого соединен с первым инверсным входом первого элемента И, выход которого соединен с синхровхо- дом счетчика длительности, выходы управляющих сигналов регистра управляющих сигналов являются выходами управляющих сигналов устройства, отличающее- с я тем, что, с целью повышения достоверности выдачи управляющих сигналов, в него дополнительно введены регистр адреса перехода, регистр условия, триггер переполнения, триггер пуска, триггер прове ряёмого условия, блок контроля на четность, мультиплексор условий, блок сравнения, второй одновибратор, четвертый, пятый и шестой элементы И, четвертый и пятый элементы ИЛИ, причем выходы регистра адреса перехода соединены с третьей группой информационных входов мультиплексора адреса, модифицируемый разряд адреса выходов адреса регистра управляющих сигналов соединен с информационным входом мультиплексора условий, выход которого соединен с информационным входом триггера проверяемого условия. прямой выход которого соединен с входом модифицированного разряда первой группы информационных входов мультиплексора адреса и с первым входом второго элемента И, выход которого соединен с вторым инверсным входом пер- вого эяемента И и первым входом третьего элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с входом первого одно- вибратора, выход которого соединен с входом сброса триггера ждушего условия, прямой выход которого соединен с входом разрешения счетчика длительности, с третьим прямым входом первого элемента И, с вторым входом второго элемента И, с инверсным входом четвертого элемента И, с первым входом пятого элемента И и с входом разрешения счетчика адреса, выходы которого соединены с четвертой группой информационных входов мультиплексора адреса, с первой группой информационных входов блока сравнения и являются группой выходов адреса отказа устройства, выход которого является выходом сигнала останова при отказе и соединен с первым входом третьего элемента ИЛИ, выход которого соединен с входом сброса триггера пуска, инверсный выход которого соединен с входом сброса регистра адреса, а прямой выход - с входом пуска генератора тактовых импульсов, первый выход которого соединен с вто- 5 рым входом третьего элемента И, с входом записи регистра адреса, с улра вляющим входом блока контроля на четность, с четвертым прямым входом первого элемента И, с К и С-входом триггера переполнения,

10 второй выход генератора тактовых импульсов соединен с входами прямого счетчика счетчиков адреса и длительности, с С-входом триггера ждущего условия и первым входом шестого элемента И, третий выход

15 генератора тактовых импульсов соединен с входом синхронизации триггера условия, инверсный выход которого соединен с вторым входом пятого элемента И, -выход которого соединен с первыми входами

0 четвертого и пятого элементов ИЛИ, выходы которых соединены соответственно с первым и вторым адерсными входами мультиплексора адреса, выход сигнала перехода блока постоянной памяти команд управлё5 ния соединен с входами разрешения регистра адреса перехода, регистра условия и входом сброса регистра условия, выходы ко да логического условия и времени бжидгния блока постоянной памяти команд управле0 ния соединены с информационными входами регистра адреса, пе рехода и регистра условия, выход сигнала ждущего условия блока постоянной памяти команд управления соединен с l-входом триггера ждущего

5 условия, выход сигнала конца программы блока постоянной памяти команд управления соединен с вторым входом пятого элемента ИЛИ, выход сигнала конца работы блока постоянной памяти команд управле0 ния соединен с вторым входом четвертого элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ, входы сигналов логических условий устройства соединены с группой информационных вхо5 дов мультиплексора условий, группа выходов блока постоянной памяти объединена и соединена с информационными входами блока контроля на четнос ть, выход которого является выходом сигнала сбоя ус0 тройства 1 соединен с управляющим входом блока сравнения, инверсный выход триггера ждущего условия соединен с входом сброса счетчика длительности и вторым входом шестого элемента И, выход которого

5 соединен с входами записи регистра управляющих сигналов, регистра адреса перехода и регистра условия, выходы кода условия регистра условия соединено с адресными входами мультиплексора условий выходы кода длительности соединены с информационными входами счетчика длительности, выходы адреса сегмента выходов адреса регистра управляющих сигналов соединены с второй группой информационных входов блока сравнения, выход сигнала переполнения счетчика длительности соединен с вторым входом второго элемента ИЛИ и через второй одновибратор - с входом асинхронной установки триггера переполнения, прямой выход которого соединен с вторым входом четвертого элемента ИЛИ, вход пуска устройства соединен с входом установки триггера пуска, группа входов кода операции устройства соединена с второй группой информационных входов мультиплексора адреса.

,КМ-( | HM-i iKM V I

t

KM -4

|HM-$. ТЧМ-S I

-t

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультимикропрограммное устройство управления с контролем | 1985 |

|

SU1272333A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1278847A1 |

| Устройство для программного управления | 1990 |

|

SU1716482A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142833A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Программируемый контроллер | 1988 |

|

SU1642446A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1242946A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1381506A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1282121A1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в позиционных системах программного управления. Цель изобретения - повышение достоверности выдачи управляющих сигналов. Поставленная цель достигается введением в устройство регистра адреса перехода, регистра условия, триггера переполнения, триггера пуска, триггера проверяемого условия, блока контроля на четность, мультиплексора условия, блока сравнения, четвертого-шестого элементов И, пятого элемента ИЛИ. Сущность изобретения заключается в придании устройству свойства контроля множества простых логических условий и множества ждущих логических условий с произвольным временем ожидания выполнения, переходе к подпрограмме восстановления процесса управления при невыполнении ждущего логического условия за допустимый временной интервал и повышении быстродействия (путем контроля в интервалах ожидания выполнения условий содержимого ячеек блока памяти, останова устройства при искажении информации в сегментах памяти, принадлежащих выполняемой программе). 3 ил. (Л С

ФмЗ:

:

| Микропрограммное устройство управления | 1984 |

|

SU1236475A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для программного управления | 1985 |

|

SU1251032A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| : | |||

Авторы

Даты

1992-12-30—Публикация

1990-06-04—Подача