1

Изобретение отлосится к аитоматн- ке и вычислительной технике i может быть }гспользоваио в устройствах управления и диагиостиронания дискрет -1Х Об7ЛМ ТОВ.

Мелью изобрстення Я1зллетс.я повышение надежности устройства за счет сокращения оборудованияблокоп памяти. I

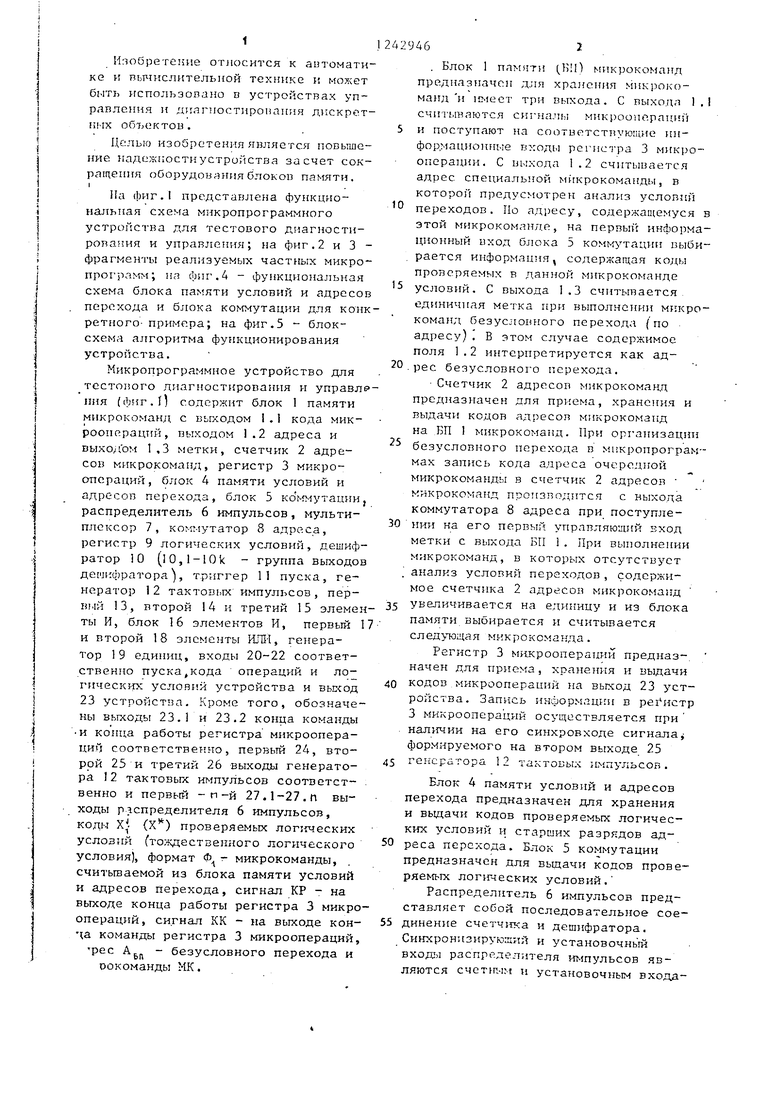

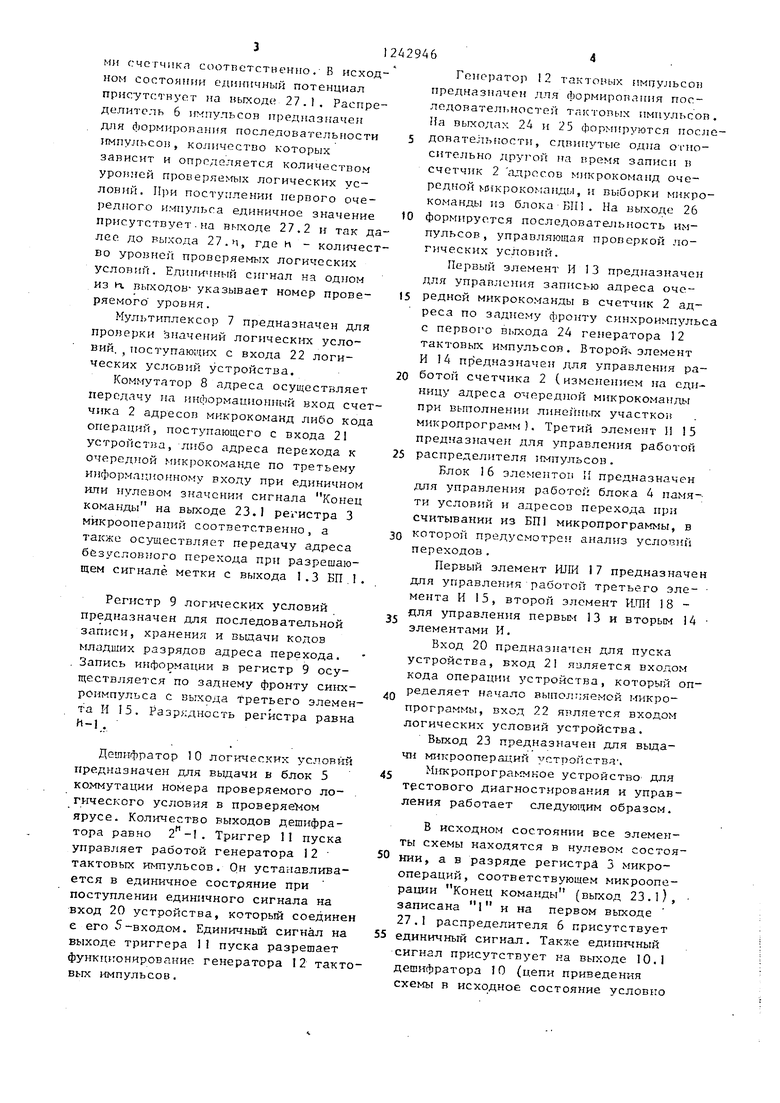

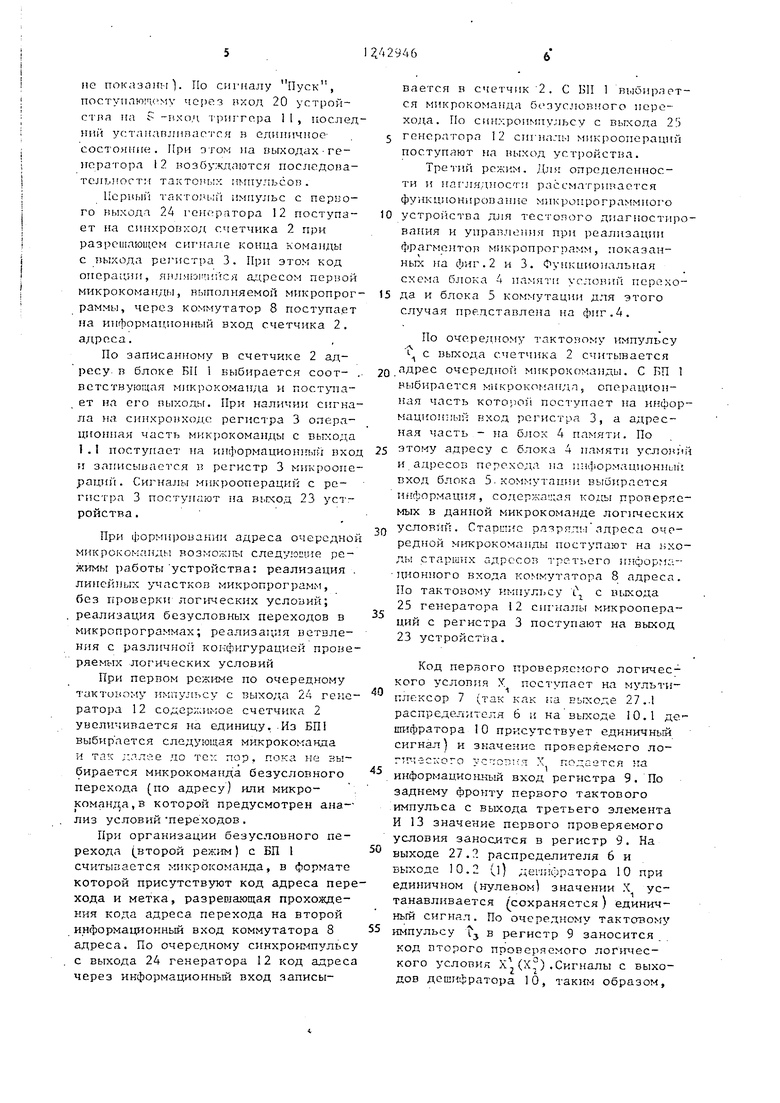

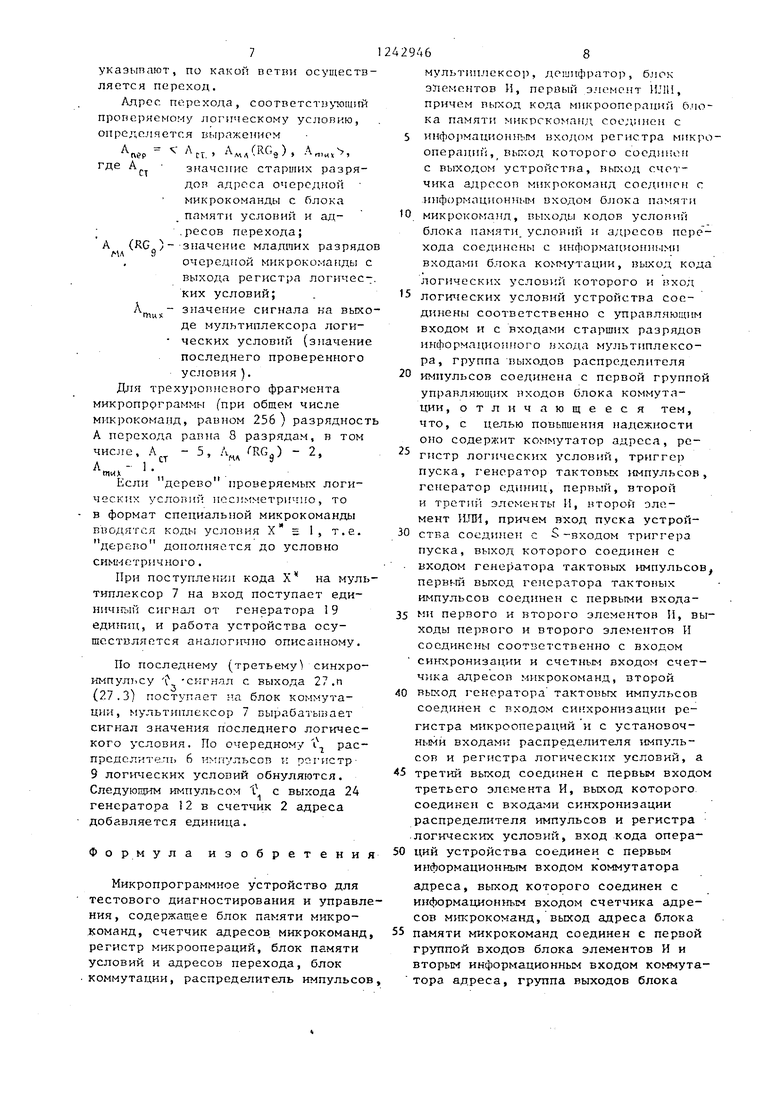

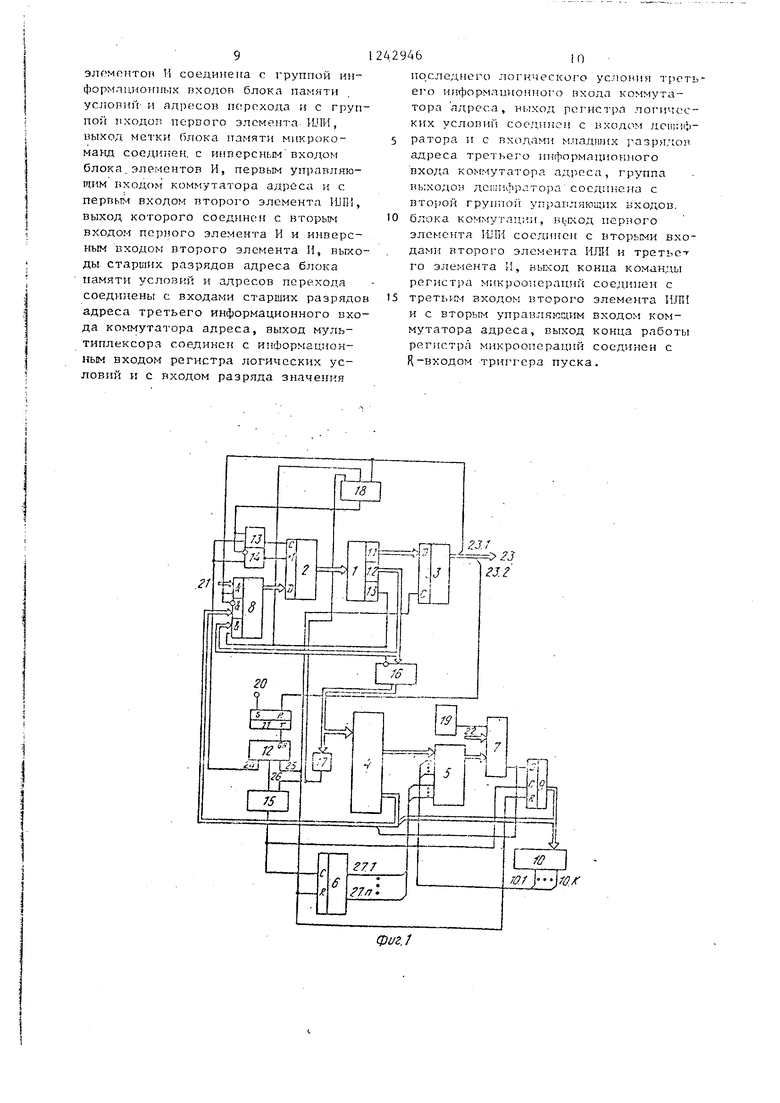

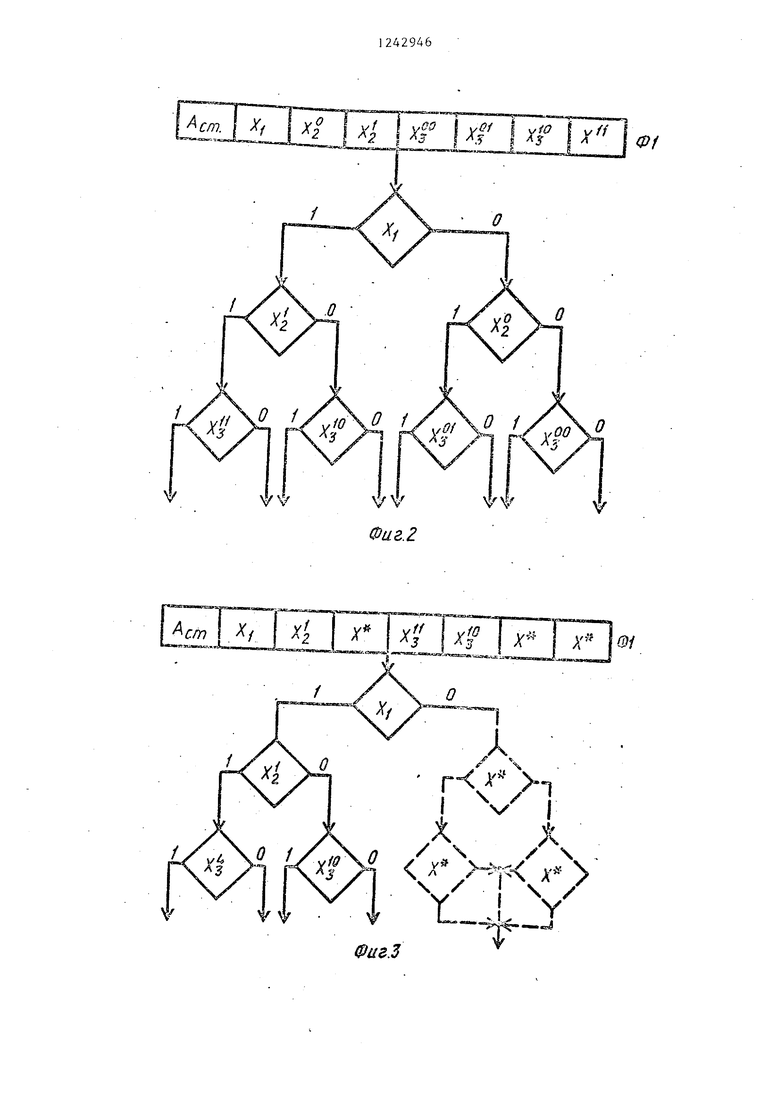

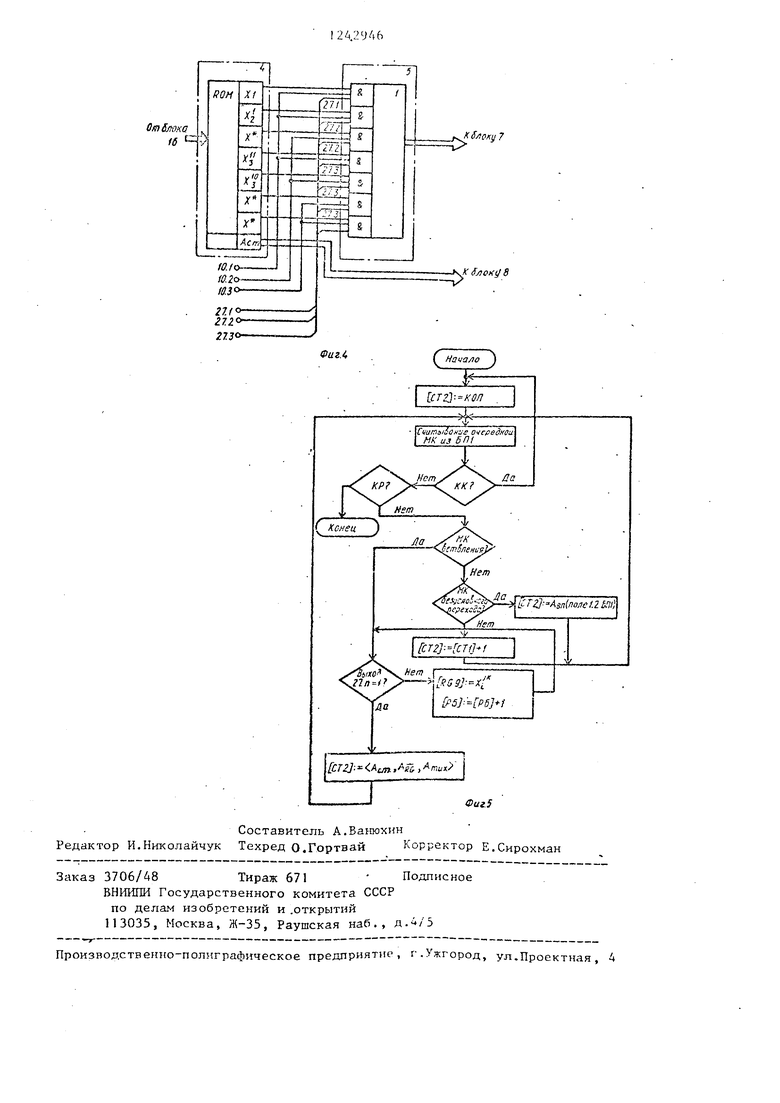

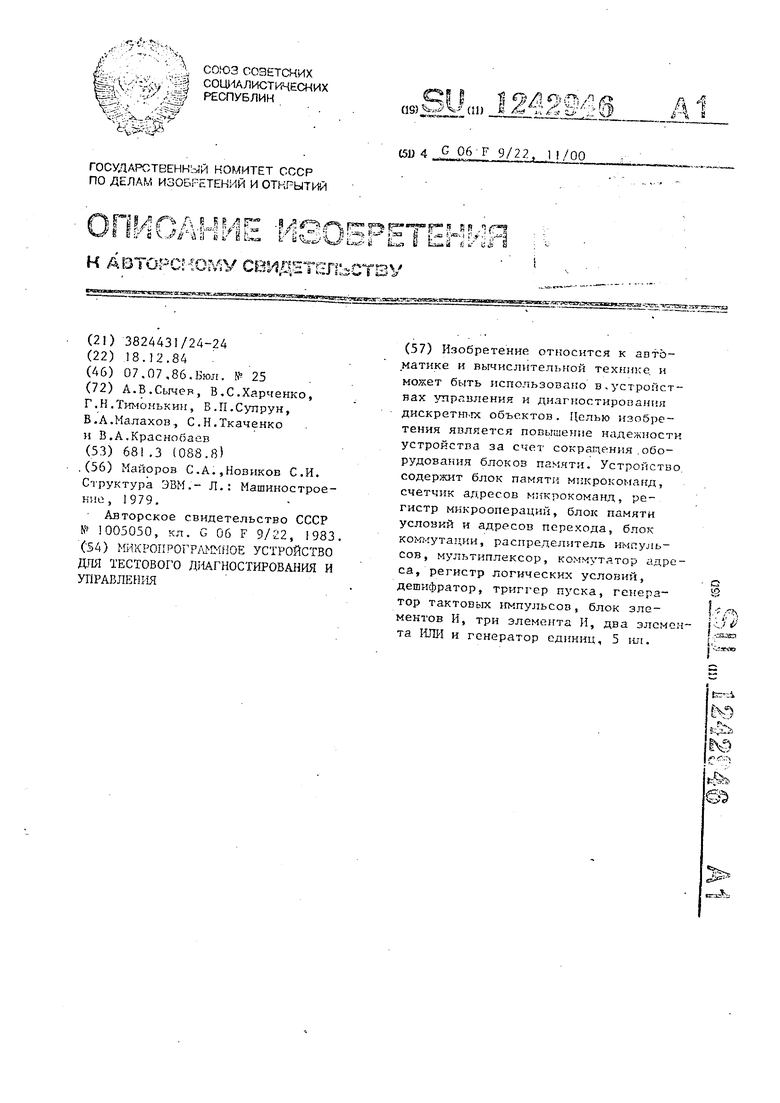

На фиг.1 представлена функциональная схема микропрограммного устройства для тестового диагностирования и управления; на фиг.2 и 3 - фрагменты реализуемых частных микропрограмм; на фиг.А - функциональная схема блока условий и адресов перехода и блока коммутации для конкретного- примера; на фиг.5 - блок- схема алгоритма функционирования устройства.

MpiKponporpaMMHoe устройство для тестового диагностирования и управления (фиг.П содержит блок 1 памяти микрокоманд с вькодом I.1 кода микроопераций, выходом 1.2 адреса и выходом 1,3 метки, счетчик 2 адресов микрокоманд, регистр 3 микроопераций, блок 4 памяти условий и адресов перехода, блок 5 KoViMyramm, распределитель 6 импульсов, мультиплексор 7, комг- утатор 8 адреса, регистр 9 логических условий, дешифратор 10 (10,1-10k - группа выходов дегииоЬратора), триггер 11 пуска, генератор 12 тактовых импульсов, первый 13, второй 14 и третий 15 элементы И, блок 16 элементов И, первый 1 и второй 18 элементы ИЛИ, генератор 19 единиц, входы 20-22 соответственно пуска,кода операций и логических условий устройства и выход 23 устройства. Кроме того, обозначены выходы 23.1 и 23.2 конца команды и конца работы регистра микроопераций cooTBeTCTBet Ho, первый 24, второй 25 и третий 26 выходы генератора 12 тактовых импульсов соответст- веяно и первый - п-и 27.1-27.П выходы распределителя 6 импульсов, коды Ху (X) проверяемых лопгческнх условий (то;«дественного логического условия), формат Ф микрокоманды, считьшаемой из блока памяти условий и адресов перехода, сигнал КР - на выходе конца работы регистра 3 микроопераций, сигнал КК - на выходе кон- команды регистра 3 микроопераций, рее - безусловного перехода и

оокоманды МК.

10

15

429462

. Блок 1 памяти (.НИ) микрокоманд предназначен для хранения микрокоманд и имеет три выхода. С выхода 1,1 считываются сигналр: микроопсраци

5 и поступают на соответствующие ин- фор.мационные входы pei-истра 3 микрооперации. С выхода 1.2 считывается адрес специальной мйкрокомандЕ,, в которой предусмотрен анализ условий переходов. По адресу, содержащемуся в этой микрокоманде, на нервыт информационный вход блока 5 коммутации выбирается информация, содерлсагцая коды проверяемых в данной микрокоманде условий. С выхода 1.3 считывается единичная метка при выполнении микрокоманд безусловного перехода (но адресу). В этом случае содержимое поля 1.2 интернретируется как .рее безусловного перехода.

- Счетчик 2 адресов микрокоманд предназначен для приема, хранения и выдачи кодов адресов микрокоманд на БП 1 микрокоманд. При орт лнизации

безусловного перехода в микропрограммах запись кода адреса очередной микрокоманды в счетчик 2 адресов микрокоманд произподтится с выхода коммутатора 8 адреса при поступле30 НИИ на его первый управляющий вход метки с выхода БП 1. При выполнении микрокоманд, в которых отсутствует анализ условий переходов, содержимое счетчика 2 адресов микрокоманд

35 увеличивается на единицу и из блока памяти выбирается и считывается следую1дая микрокоманда.

Регистр 3 микроопераций предназ-. начен для приема, хранения и выдачи кодов микроопераций на выход 23 устройства. Запись информацрги в рех истр 3 микроопераций осуществляется при наличии на его синхровходе сигналаj формируемого на втором выходе 25

40

45 reiicparopa

я гактоБых ;ьмпульсов

Блок 4 памяти условий и адресов перехода предназначен для хранения и вьщачи кодов проверяемых логических условий и старших разрядов адреса перехода. Блок 5 коммутации

предназначен для выдачи кодов проверяемых логрг- еских условий.

Распределитель 6 импульсов представляет собой последовательное соединение счетчика и дешифратора. Синхронизирующий и установочньш распределителя ш-тульсов являются счет1г.-1м и установочным входами счсгчикл cooTncTCTHtmno . Б исход нo состоянии единичный потенциал присутствует иа вьгходк 27.1. Распределитель 6 ifMny.TbcoB предназначен для djopMHponaHifH последовательности импульсов, количество которых зависит и определяется количеством уровней пpoвepя fыx логических условий. IIjiH поступлении первого очередного импульса единичное значение присутствует. на ньгходе 27.2 и так длее до выхода 27. и, где и - кол1-гчес во уровней проверяемых логических условий. Единичный сп1-нал на одном из и. выходов- указывает номер проверяемого уровня.

Мультиплексор 7 предназначен для проверки значений логических условий. , 1юступаю1 1их с входа 22 логических условий у-стройства.

Коммутатор 8 адреса осуществляет передачу на. информационный вход счетчика 2 адресов микрокоманд либо кода операций, поступающего с входа 21 устройства, либо адреса перехода к очередной микрокоманде по третьему И)форм.1ционному входу при единичном или нулевом значении сигнала Конец команды на выходе 23.1 регистра 3 микроопераций соответственно, а также осуществляет передачу адреса безусловного перехода при разрешающем сигнале метки с выхода 1.3 БП.1.

Регистр 9 логических условий предназначен для последовательной записи, хранения и выдачи кодов младших разрядов адреса перехода. Запись и формации в регистр 9 осуществляется по заднему фронту синхроимпульса с выхода Третьего элемента И 15. Разр :дность регистра равна .г

Дешифратор 10 логически:-: условий предназначен для выдачи в блок 5 когмутации номера проверяемого логического условия в проверяе -iOM ярусе. Количество выходов дешифратора равно . Триггер 11 пуска управляет работой генератора 12 тактовых ш-тульсов. Он устанавливается в единичное состряние при поступлении единичного сигнала на вход 20 устройства, который соединен е его ч -входом. Единичный сигнал на выходе триггера 1I пуска разрешает функционирование генератора 12 тактовых импульсов.

А29464

Генератор 12 тактовых импульсов предназначен для формиропл(П1я пос- ледователт,ностей тлктопых импульсов. На выходах 2А и 25 форм1 руются nocjie5 довате 1ьпости, сдвинутые одна относительно другой га время записи в счетчик 2 адресов икpoкoмaнд очередной NOiKpOKOf.saiwLi, и выборки микрокоманды из блока . На выходе 26

10 формируется последовательность импульсов, управляющая проверкой логических условий.

Первый элемент И I3 предназначен для управле П1я записью адреса оче15 редкой микрокоманды в счетчик 2 адреса по зад1{ему фронту синхроимпульса с первого выхода 24 генератора 12 тактовых импульсов. Второй элемент И 14 предназначен для управления ра20 ботой счетчика 2 (изменением па единицу адреса очередной микрокома1гды при выполнении линеГгньгх участко микропрограмм). Третий элемент И 15 предназначен для управления работой

25 распределителя импульсов.

Блок 16 злемеито И предназначен для управления работой блока 4 памя-- ти условий и адресов перехода при считывании из БП1 микропрограммы, в

которой предусмотрен анализ условий переходов.

Первый элемент ИЛИ 17 предназначен для управле ия работой третьего эле- мента И 15, второй элемент ИШ-1 18 - для управления первым 13 и вторым 14 элементами И.

Вход 20 предназначен для пуска устройства, вход 21 является входом кода операции устройства, который оп35

ределяет начало выполняемой микропрограммы, вход 22 является входом логических условий устройства.

Выход 23 предназначеи для выдачи микрооперах Ий устройства .

Mикpoпpoгpa п lкoe устройство для тестового диагностирования и управления работает следую1чим образом.

В исходном состоянии все элементы схемы находятся в нулевом состояНИИ, а в разряде регистра 3 микроопераций, соответствующе м микрооперации Конец команды (выход 23.), записана I и на первом выходе 27.1 распределителя 6 присутствует

единичный сигнал. Также едигатчный сигнал присутствует на выходе 10.1 ешифратора 10 (цепи приведения схемы в исходное состояние услов1го

не показа1П-г). По curtiajiy Пуск, поступлюгч - му через вход 20 устройства на -nxo/i, триггора I 1 , последний ycTaitanjinBacTc.H в елиничиое- состо пгие . При этом )а выходах ге- 1горатора 12 возбуждаются последова- телы ост:г такто 1)х -;мпу.чьсоп .

Первый такто; 1.;й импульс с первого выхода 24 reitnpnropa 12 поступает на синхровход счетчика 2 при разреи1аюи(ем с П нале Kovnj,a команды с выхода регистра 3. При этом код операции, явл.чюи .иГгся адресом первой микрокоманды, выполняемой микропрограммы, через коммутатор 8 поступает на инфорь ационный вход счетчика 2. адреса.

По записанному в счетчике 2 ад- ресу в блоке БП 1 выбирается соот- . встствую цая микрокоманда и поступает на его вьгходы. При наличии сигнала на синхровходе регистра 3 опера- часть микрокоманды с выхода I.I поступает на информапионный вход и записывается в регистр 3 М1п роопе- рациГ. Сигналы мик юопераций с регистра 3 поступают на вькод 23 устройства .

При формироварп1и адреса очередной микрокоманды BOSNIOKI&I следующие режимы работы устройства: реализация . линей)ых участков микропрограмм, без проверки логических условий; реализация безусловных переходов в микропрограммах; реализаг ия ветвления с различно конфигурацией проверяемых логических условий

При первом режиме по очередному тактово:- у импулт су с выхода 2А генератора 12 coдep;:л 5oe счетчика 2 увеличивается па единицу.-Из БП1 выбир ается следующая микрокоманда и так г,алйе .до те:-: пор. пока не зь;- бирается микрокоманда безусловного перехода (по адресу) или микро- кoмaн a, в которой предусмотрен анализ условий переходов.

При организации безусловного перехода (второй режим) с БП 1 считывается микрокоманда, в формате которой присутствуют код адреса перехода и метка, разрешающая прохождения кода адреса перехода на второй информационный вход коммутатора 8 адреса. По очередному синхроге- пульсу с выхода 24 генератора 12 код адреса через информационный вход записывается в счетчик 2. С БП 1 выоирает- ся микрокоманда безусловного перехода. По синхроимпульсу с выхода 23 5 генератора 12 сигналы микроопераций поступают на выход устройства.

Третий режим. Для определенности и 1гаг лядности рассматривается функционирование микропрограммног о

0 устройства для тестового диагностирования и управле иия при реализации фрагментов микропрограмм, показанных на Лиг. 2 и 3. С|ун сциональная схема блока 4 памяти ус.-извий перехо5 да и блока 5 коммутации для этого случая представлена на фиг.4.

По очередному тг1ктоу ому импульсу с выхода счетчика 2 считывается

Q адрес очередной микрокоманды. С БП 1 выбирается микрокоман;,л, операционная часть KOTopoii поступает на информационный вход регистра 3, а адресная i iacTb - на блок 4 . По

5 этому адресу с блока 4 памяти условий и адресов перехода на 11нформ;гционньи1 вход блока З.коммутапии выбирается информация, содержавшая проверяемых в данной микрокоманде лопгчсских

0 условий. Старшие разряды адреса оче- микрокоманды поступают на i;xo- ды старших адресов третьего И}1форм:ч- ционного входа коммутатора 8 адреса. По тактовому 1- Мпул1)Су i .j с выхода 25 генератора 12 сигналы микроопераций с регистра 3 поступают на выход 23 устройства.

5

Код первого проверяе юго логического условия X поступает на мульт1г-7 - -1 , плексор / так как на вькоде /7.Л

распределителя 6 и на вьгкоде 10.1 де.-- шифратора 10 присутствует единичный сигнал) и значение проверяемого ло- гтг-ч-зского с гоп - я л подеется на

информационный вход регистра 9. По заднему фронту первого тактового импульса с выхода третьего элемента И 13 значение первого проверяемого условия занослтся в регистр 9. На

выходе 27. . распределителя 6 и

выходе 10.2 (l) дешифратора 10 при единичном (нулевом) значении Х устанавливается (сохраняется ) единичный сигнал. По очередному тактовому

ш-шульсу fj в регистр 9 заносится код второго проверяемого логугчес- кого условия Х.,(Х°) .Сигналы с выходов дешифратора 10, таким образом,

7

указывают, по какой ветвн осуществляется переход.

Адрес перехода, соответстц тощий проверяемому логическому условию, определяется вмражеином

rvep Чт. ), Л„,,, где А з(аче1гис старших разрядов адреса очередной микрокоманды с блока памяти условий и ад- .ресов перехода;

А (RG )--значение младших разрядо 9

очередной микрокоманды с

выхода регистра логических условий; . тш значение сигнала на выходе мультиплексора логи- ческих условий (значение последнего проверенного условия ).

Для трехуровневого фрагмента микропррграммн (при общем числе микрокоманд, равном 256) разрядност А перехода равна 8 разрядам, в том числе, А - 5, Л G) - 2,

„

Если дерево проверяемых логически.х услопий нсс м етрич го, то в формат специальной микрокоманды вводятся коды условия Х 1, т.е. дьрепо дополняется до условно снм1-1етричного .

При поступленин кода Х на мультиплексор 7 на вход поступает еди- ,1й сигнал от генератора 19 , и работа устройства осуществляется аналогично описанному.

По последнему (третьему синхро- импул71су С -сигнал с выхода 27 .п (27.3) поступает на блок коммутации, мультиплексор 7 вырабатывает сигнал значения последнего логического условия. По о-чередному i распределитель 6 и r/льcoв li регистр- 9 логических условий обнуляются. Следующим импульсом С с выхода 24 генератора 12 в счетчик 2 адреса добавляется единица.

Формула изобретения

Микропрограммное устройство для тестового диагностирования и управления, содержащее блок памяти микрокоманд, счетчик адресов микрокоманд, регистр микроопераций, блок памяти условий и адресов перехода, блок коммутации, распределитель импульсов.

з

0

15 20

25

30 . .

35

40

45

55

429468

мультиплексор, дешифратор, блок элементов И, перВЕЛй элемент ИЛИ, причем выход кода микроопераций б.чо- ка памяти микрокоманд соединен с информацион П:,1м входс м регистра микро- операци, которого соединен с выходоь устройстг а, нькод счетчика адресов микрокоманд соединен с ,инф(;рмац1 онн,1м входом блока памяти микpoкo aнд, выходы кодов условий блока памяти условий и адресов пере - хода соединены с информационными входами блока кo tмyтaции, выход кода логических условий которого и вход логических условий устройства соединены соответственно с управляющт1м входом и с входами старших разрядов информационного входа мультиплексора, группа ВЫХОДОВ распределителя импульсов соединена с первой группой управляющих входов блока коммутации, отличающееся тем, что, с дапью повьпиения надежности оно содержит коммутатор адреса, регистр логических условий, триггер пуска, генератор тактовых импульсов, генер 1тор единиц, первый, второй и третий И, второй элемент H.nii, причем вход пуска устройства соединен с S-входом триггера пуска, выход которого соединен с входом генератора тактовых импульсов первьй выход генератора тактоных импульсов соединен с первыми входами первого и второго элементов И, выходы первого и второго элементов И соединены соответственно с входом синхронизации и счетньм входом счетчика адресов микрокоманд, второй выход генератора тактовых импульсов соединен с входом синхронизации регистра микроопераций и с установочными входами распределителя импульсов и регистра логических условий, а третий выход соединен с первьм входом третьего элемента И, выход которого соединен с входами синхронизации распределителя импульсов и регистра логических условий, вход кода операций устройства соединен с первым информационным входом коммутатора

адреса, выход которого соединен с информационным входом счетчика адресов мгасрокоманд, выход адреса блока памяти микрокоманд соединен с первой группой входов блока элементов И и вторьи информационным входом коммутатора адреса, группа выходов блока

9

элементов И соединена с группой ин- формлииоьгиых входои блока naiMHTH услопни- и ад11есов перехода и с груп ной пходол первого элемента Ш1Н, выход метки блока памяти мнкроко- маьщ соеяипеп. с инверсным входом блока.элементов И, первым управляющим входом коммутатора адреса и с первьм входом второго элемента 11101, выход которого соедннсмг с вторым входом первого элемента И и инверсным входом второго элемента И, выходы старших разрядов адреса блока памяти условр й и адресов перехода соединены с входами старших разрядо адреса третьего информационного входа коммутатора адреса, выход мультиплексора соединен с информационным входом регистра логических условий и с входом разряда значения

242946

10

последне1Ч1 лопгческого условия третьего информационного входа коммутатора адреса, ныход регистра лотчгк с- ких условий соединсм с входом де1 ифратора и с входами младших разрядов адреса третьет о информацион)1ого входа коммутатора адреса, группа выходов дешифратора соединена с второй rpyrinoii управляющих входов.

блока коммутации, вькод первого

элеморгта lUIli соединен с вторыми входами второго элемента HJIIi и третье- го элемента И, вьпчод конца команды регистра М жроо11ераций соединен с

третьге-f входом второго элемента ИЛ11 и с вторым управляк гцим входом коммутатора адреса, выход конца работы регистра микроопераций соединен с Н-входом триггера пуска.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1984 |

|

SU1211724A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1270772A1 |

| Устройство для микропрограммного управления | 1983 |

|

SU1198520A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1179338A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142834A1 |

Изобретение относится к авто- .матике и вычислительной тех{1ике. и может быть использова о в,устройствах управления и диагностирования дискретш.гх объектов. Целью изобретения является повышение надежности устройства за счет сокращения .оборудования блоков памяти. Устройство. содержит блок памяти микрокоманд, счетчик адресов микрокоманд, регистр микроопераций, блок памяти условий и адресов перехода, блок ко гмутации, распределитель импульсов, мультиплексор, коммутатор гшрс- са, регистр логических условий, дешифратор, триггер пуска, генератор тактовых импульсов, блок эла- мектов И, три элемента И, два элемента ИЛИ и генератор единиц, 5 ил. о to У к) .-.-jijsa (S- ci 1чэ ff .-

Ф1

Фиг.З

7} А Л

Y V

Авторы

Даты

1986-07-07—Публикация

1984-12-18—Подача