Изобретение относится к области автоматики и вычислительной техники и может найти применение в отказоустойчивых вычислительных системах автоматического управления и контроля для повышения их надежности и помехоустойчивости.

Известно резервированное устройство, содержащее в каждом из каналов резервируемый блок, мажоритарный элемент контроля, элемент неравнозначности, интегрирующий элемент, элемент памяти, элемент ИЛИ - И и восстанавливающий орган

1.

Недостатком устройства является низкая надежность и помехоустойчивость вследствие того, что в нем не обеспечивается защита от дружественных сбоев и враждебных неисправностей резервируемых блоков.

Наиболее близким по технической сущности к изобретению является резервированное устройство, содержащее в каждом из каналов резервируемый блок, первый элемент И, первый вход которого соединен с выходом элемента памяти (триггера), элемент неравнозначности, первый вход которого соединен с выходом мажоритарного элемента, входы которого подсоединены к выходам восстанавливающих блоков каждого канала, второй элемент И 2.

Недостаток данного устройства состоит втом, что надежность и помехоустойчивость остаются достато }Но нйзкими, поскольку в нем не обеспечивается защита от враждебных неисправностей резервируемых блоков.

Целью изобретения является повышение надежности и помехоустойчивости устройства.

Указанная цель достигается тем, что в резервированное устройство, содержащее в каждом из N каналов резервируемый блок, группу элементов И, первые входы которых соединены с инверсным выходом триггера, элемент неравнозначности, первый вход которого соединен с выходом мажоритарного элемента, входы которого соединены с выходами восстанавливающих блоков каждого канала, элемент И, дополнительно введена в каждом канале схема контроля на;ичия

(Л С

vj

00

ел

lo

IGO

|ЧЗ

враждебной неисправности, входы которой соединены через группу элементов задержки с соответствующими резервированными выходами резервируемого блока и с вторыми входами соответствующих элементов И группы, первый выход схемы контроля наличия враждебной неисправности соединен с вторым входом элемента неравнозначности, выход которого соединен1 1 &fTep § QM входом первого элемента ИЛИ и через первый элемент НЕ с первым входом элемента И, второй выход схемы контроля наличия враждебной неисправности соединен с вторым входом первого элемента ИЛИ и через второй элемент НЕ с вторым входом элемента И, выход первого элемента ИЛИ соединен с входом установки в состояние 1 триггера, вход установки в состояние О которого соединен с выходом второго элемента ИЛИ, первый вход которого соединен с выходом элемента И, а второй вход -- с входами установки в состояние О устройства и блоков взаимной информационной согласованности всех каналов, вход синхронизации блока взаимной информационной согласованности соединен с входами синхронизации блоков взаимной информационной согласованности других каналов, через элемент задержки с входами синхронизации устройства и резервируемых блоков всех каналов, группа информационных входов блока взаимной информационной согласованности соединена с соответствующим выходом группы элементов И всех каналов, группа обменных информационных выходов блока взаимной информационной согласованности соединена с группой обменных информационных входов блоков взаимной информационной согласованности других каналов, группа информационных выходов соединена с группой входов восстанавливающего блока, выход которого является Информационным выходом устройства.

Кроме того, блок взаимной информационной согласованности каждого канала содержит регистр, информационные входы которого соединены с группой информационных входов блока, входы установки в состояние О и синхронизации соединены, соответственно, с входами установки в состояние О и синхронизации блока, соответствующие вь1хо ды регистра соединены с группой обменных информационных выходов блока и с соответствующими входами программируемой логической матрицы, другие входы которой соединены с группой обменных информационных входов блока, выходы программируемой логической матрицы соединены с группой информационных выходов блока.

Сущность изобретения заключается в следующем. Известно, что в компонентах

вычислительной системы возможно возникновение дружественных и враждебных неисправностей. Под дружественными понимаются те неисправности, в результате которых все приемники от неисправновного

0 передатчика получают одно и то же значение, т.е. неисправный источник по отношению к приемникам ведет себя одинаковым образом. Под враждебными понимаются те неисправности, в результате которых од5 ни приемники от неисправного источника получают одно значение, а остальные - другие, т.е. неисправный источник по отношению к приемникам ведет себя непредсказуемо Следовательно, для обеспечения

0 отказоустойчивости вычислительной системы по отношению к дружественным неисправностям целесообразно использование известных резервированных устройств. Использование традиционных методов оказы5 вается недостаточным для обеспечения отказоустойчивости против враждебных неисправностей. В связи с этим отсутствие специальных средств защиты от враждебных неисправностей В связи с этим отсут0 ствме специальных средств от враждебных неисправностей приводит к существенному снижению надежности и по- j мехе-устойчивости резервированных устройств

5В предлагаемом устройстве в качестве

специального средства защиты от дебных неисправностей использован детерминированный алгоритм обеспечения взаимной информационной согласованно0 сти (Pease M., Shostak R., Lamport L. Reaching agreement in the presence of faults //J ACM 1980. V 27 N 2. P. 228-237). Суть алгоритма состоит в том, что определенный уровень избыточности вычислителей, на5 ряду с использованием итерационной процедуры многораундового обмена информацией между вычислителями, приводит к таким наборам значений полученной каждым из исправных вычислителей инфор0 мации, для которых применение некоторое правила выбора, например, правила мажоритарного голосования, дает один и тот ж е результат вне зависимости от информации, переданной неисправными вычислителями.

5 Алгоритмы обеспечения взаимной информационной согласованности сроятся как по- следовательность раундов обмена информацией между вычислителями. Если в m вычислителях возникают враждебные неисправности, то детерминированный алгоритм обеспечивает взаимную информационную согласованности не менее, чем за (т t- 1) раундов, при условии, что общее число вычислителей N Зт + 1.

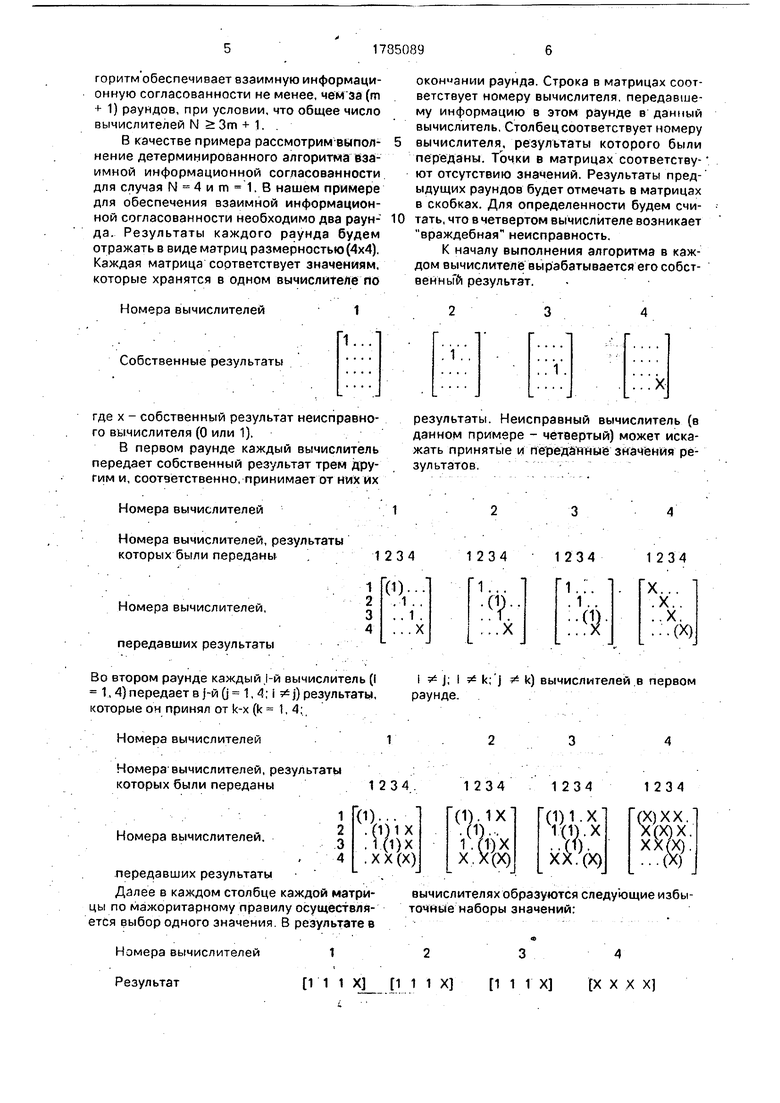

В качестве примера рассмотрим выполнение детерминированного алгоритма взаимной информационной согласованности для случая N 4 и m 1. В нашем примере для обеспечения взаимной информационной согласованности необходимо два раунда. Результаты каждого раунда будем отражать в виде матриц размерностью(4x4). Каждая матрица соответствует значениям, которые хранятся в одном вычислителе по

Номера вычислителей1

окончании раунда. Строка в матрицах соответствует номеру вычислителя, передавшему информацию в этом раунде в данный вычислитель, Столбец соответствует номеру

вычислителя, результаты которого были переданы. Точки в матрицах соответствуют отсутствию значений. Результаты предыдущих раундов будет отмечать в матрицах в скобках. Для определенности будем считать, что в четвертом вычислителе возникает враждебная неисправность.

К началу выполнения алгоритма в каждом вычислителе вырабатывается его собствен ньГй результат.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное устройство | 1991 |

|

SU1830575A1 |

| Адаптивное четырехканальное резервированное устройство | 1990 |

|

SU1742821A1 |

| Трехканальное резервированное устройство | 1979 |

|

SU946018A1 |

| Резервированное устройство | 1980 |

|

SU928685A1 |

| Резервированное устройство | 1989 |

|

SU1605236A1 |

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

| Резервированное устройство для управления электропневмоклапанами | 1989 |

|

SU1647512A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ РЕЗЕРВИРОВАННОЙ С ВЫБОРОМ СРЕДНЕГО АРИФМЕТИЧЕСКОГО ЗНАЧЕНИЯ ВЫХОДНЫХ ПАРАМЕТРОВ СИСТЕМОЙ | 2013 |

|

RU2551813C1 |

| Адаптивное многоканальное резервиро-BAHHOE уСТРОйСТВО | 1978 |

|

SU798847A1 |

| Мажоритарно-резервированная управляющая система | 1984 |

|

SU1221658A1 |

Сущность изобретения: устройство содержит элемент задержки и в каждом из N каналов резервируемый блок, группу элементов И, триггер, элемент неравнозначности, мажоритарный элемент, восстанавливающий блок, элемент И, блок контроля, группу элементов задержки, элемента ИЛИ, 2 элемента НЕ, блок взаимной информационной согласованности. 1 з.п лы, 2 ил

Собственные результаты

где х - собственный результат неисправного вычислителя (0 или 1).

В первом раунде каждый вычислитель передает собственный результат трем другим и, соответственно, принимает от них их

Номера вычислителей

Номера вычислителей, результаты которых были переданы

Номера вычислителей, передавших результаты

Во втором раунде каждый 1-й вычислитель (I 1,4) передает в j-й О 1, 4; i j) результаты, которые оч принял от k-x (k 1,4;

Номера вычислителей

Номера вычислителей, результаты

которых были переданы1234

Номера вычислителей.

передавших результаты

Далее в каждом столбце каждой матрицы по мажоритарному правилу осуществляется выбор одного значения В результате в

Номера вычислителей Результат

12

1 1 1 X 1 1 1 X

результаты. Неисправный вычислитель (в данном примере - четвертый) может искажать принятые и переданные значения результатов.

1 234

1234

1 234

1 234

2 3

4

(1)..

X

I 5й j, I k; j & k) вычислителей в первом раунде.

234

1 234

(1)1.Х

.X

(X)

1234

(Х)ХХ. Х(Х)Х.

хх(Х). ...(У)

вычислителях образуются следующие избыточные наборы значений;

1 1 1 X X X

Таким образом, в результате выполнения детерминированного алгоритма взаимной информационной согласованности во всех исправных вычислителях образовались одинаковые наборы значений вне зависимости от информации, переданной неисправным вычислителем.

Алгоритм взаимной информационной согласованности реализуентся с помощью блоков взаимной информационной согласованности, введенных во все каналы, и соответствующих связей между ними.

Существенными отличительными признаками вуказанной выше совокупности являются введенные элемент задержки и в каждом канале схема контроля наличия враждебной неисправности, группа элементов задержки, первый и второй элементы ИЛИ, первый и второй элементы НЕ и блок взаимной информационной согласованности, содержащий регистр и программируемую логическую матрицу.

Устойчивая взаимосвязь указанных признаков обеспечит появление у заявляемого устройства нового свойства, предопределяющего положительный эффект, сформированный в цели изобретения. Это новое свойство заявляемого объекта состоит в парировании враждебных неисправностей.

Поскольку указанное свойство не проявляется ни в одном из известных авторам объектов, содержащих признаки, сходные с отличительными признаками заявляемого устройства, порознь или в их сочетании, авторы считают заявляемое решение соответствующим критерию существенные отличия.

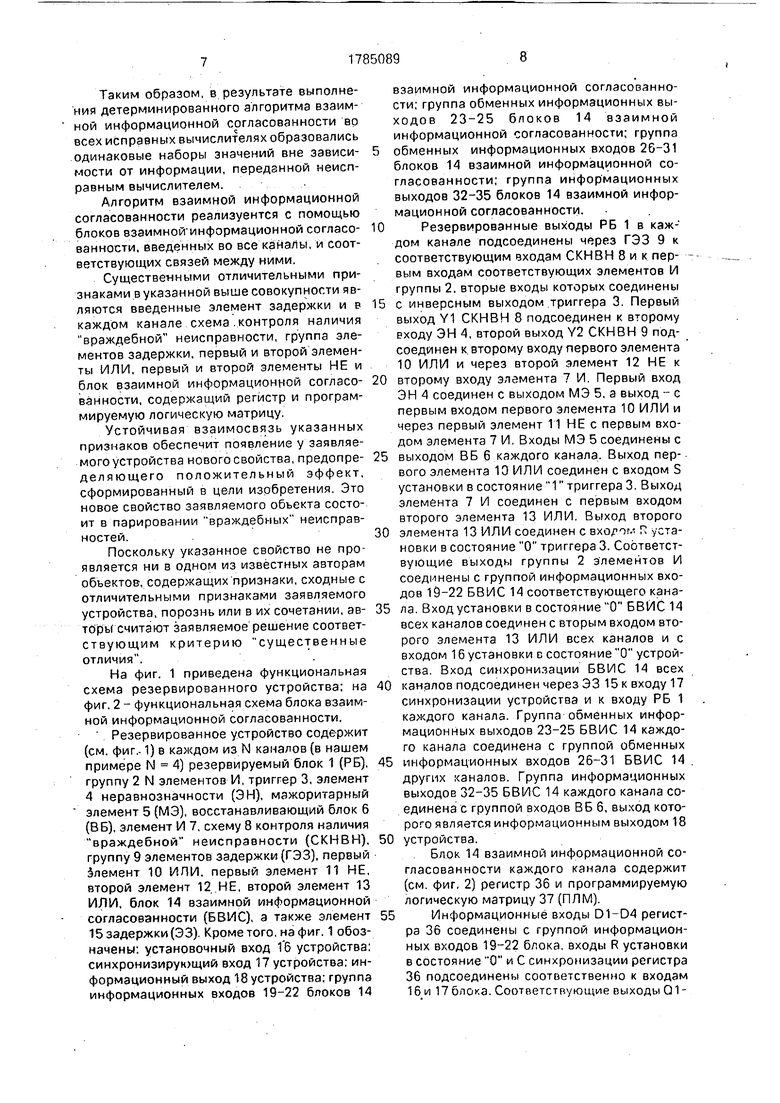

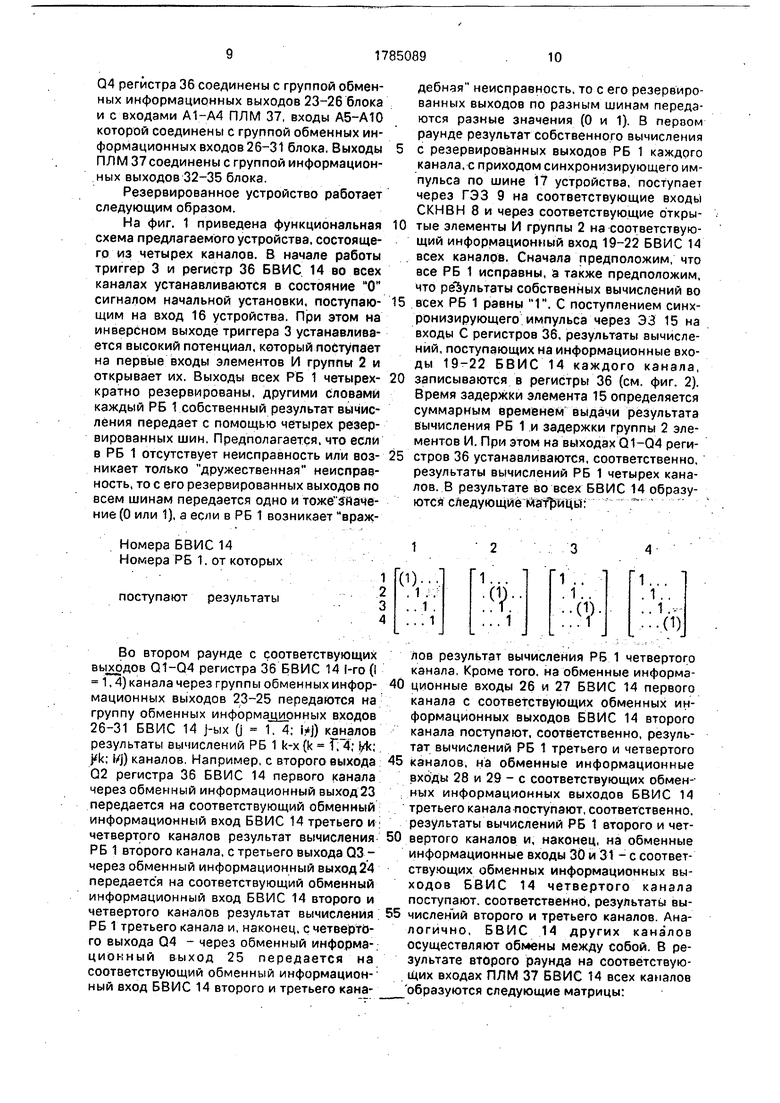

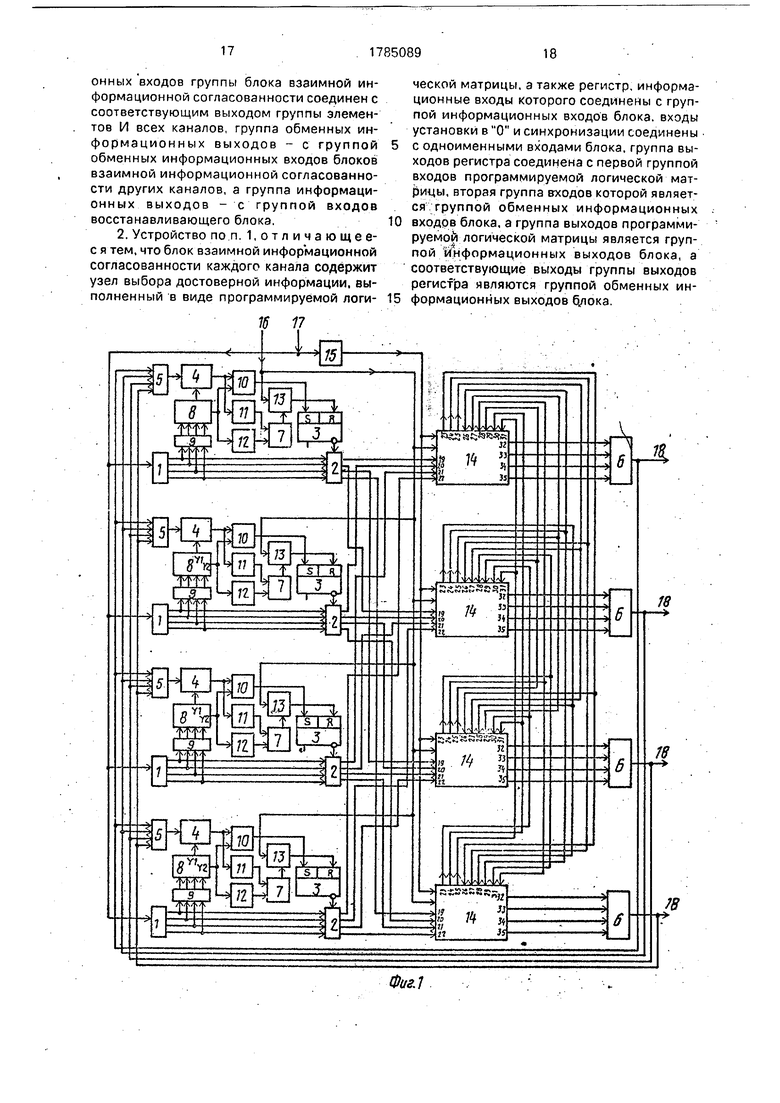

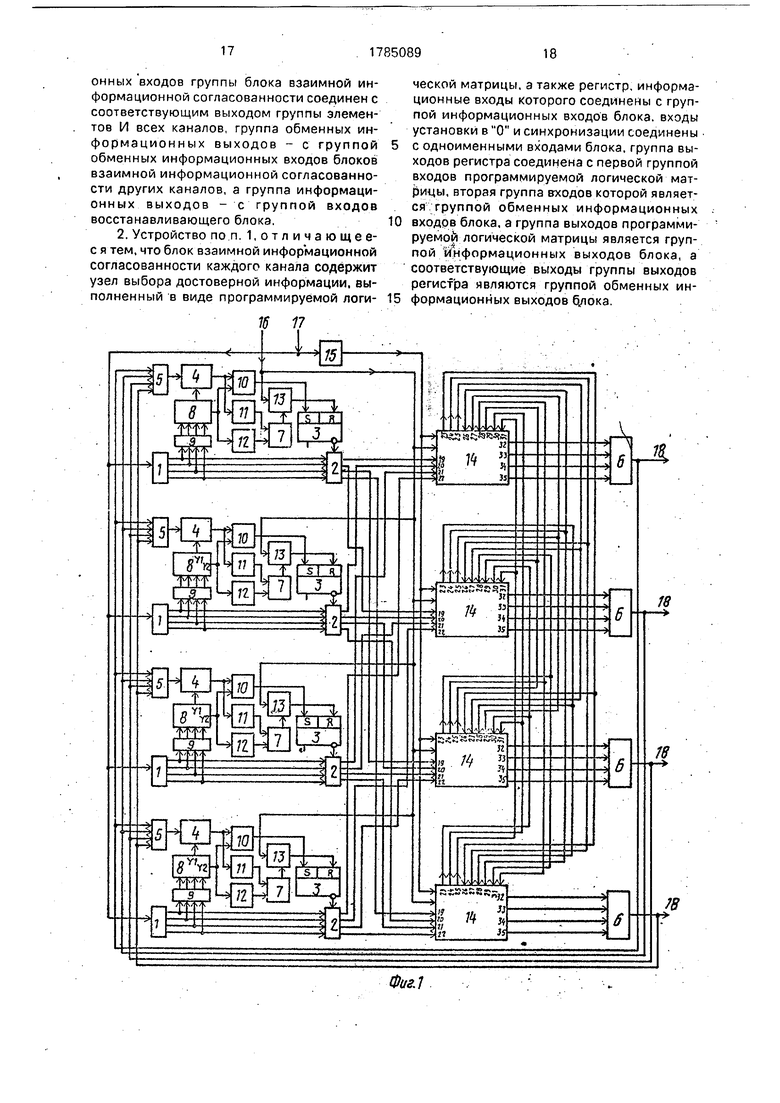

На фиг. 1 приведена функциональная схема резервированного устройства; на фиг. 2 - функциональная схема блока взаимной информационной согласованности.

Резервированное устройство содержит (см. фиг.-1) в каждом из N каналов (в нашем примере N 4) резервируемый блок 1 (РБ), группу 2 N элементов И, триггер 3, элемент 4 неравнозначности (ЭН), мажоритарный элемент 5 (МЭ), восстанавливающий блок 6 (В Б), элемент И 7, схему 8 контроля наличия враждебной неисправности (СКНВН), группу 9 элементов задержки (ГЭЗ), первый элемент 10 ИЛИ, первый элемент 11 НЕ, второй элемент 12 НЕ, второй элемент 13 ИЛИ, блок 14 взаимной информационной согласованности (БВИС), а также элемент 15 задержки (ЭЗ). Кроме того, на фиг. 1 обозначены: установочный вход устройства: синхронизирующий вход 17 устройства; информационный выход 18 устройства; группа информационных входов 19-22 блоков 14

взаимной информационной согласованности; группа обменных информационных выходов 23-25 блоков 14 взаимной информационной согласованности; группа

обменных информационных входов 26-31 блоков 14 взаимной информационной согласованности; группа информационных выходов 32-35 блоков 14 взаимной информационной согласованности.

0 Резервированные выходы РБ 1 в каж- дом канале подсоединены через ГЭЗ 9 к соответствующим входам СКНВН 8 и к первым входам соответствующих элементов И группы 2, вторые входы которых соединены

5 с инверсным выходом триггера 3. Первый выход Y1 СКНВЧ 8 подсоединен к второму входу ЭН 4, второй выход Y2 СКНВН 9 подсоединен к второму входу первого элемента 10 ИЛИ и через второй элемент 12 НЕ к

0 второму входу элемента 7 И. Первый вход ЭН 4 соединен с выходом МЭ 5, а выход - с первым входом первого элемента 10 ИЛИ и через первый элемент 11 НЕ с первым входом элемента 7 И. Входы МЭ 5 соединены с

5 выходом В Б 6 каждого канала. Выход первого элемента 10 ИЛИ соединен с входом S установки в состояние 1 триггера 3. Выход элемента 7 И соединен с первым входом второго элемента 13 ИЛИ. Выход второго

0 элемента 13 ИЛИ соединен с входом 7 установки в состояние О триггера 3. Соответствующие выходы группы 2 элементов И соединены с группой информационных входов 19-22 БВИС 14 соответствующего кана5 ла. Вход установки в состояние О БВИС 14 всех каналов соединен с вторым входом второго элемента 13 ИЛИ всех каналов и с входом 16 установки в состояние О устройства. Вход синхронизации БВИС 14 всех

0 каналов подсоединен через ЭЗ 15 к входу 17 синхронизации устройства и к входу РБ 1 каждого канала. Группа обменных информационных выходов 23-25 БВИС 14 каждого канала соединена с группой обменных

5 информационных входов 26-31 БВИС 14 других каналов. Группа информационных выходов 32-35 БВИС 14 каждого канала соединена с группой входов В Б 6, выход которого является информационным выходом 18

0 устройства.

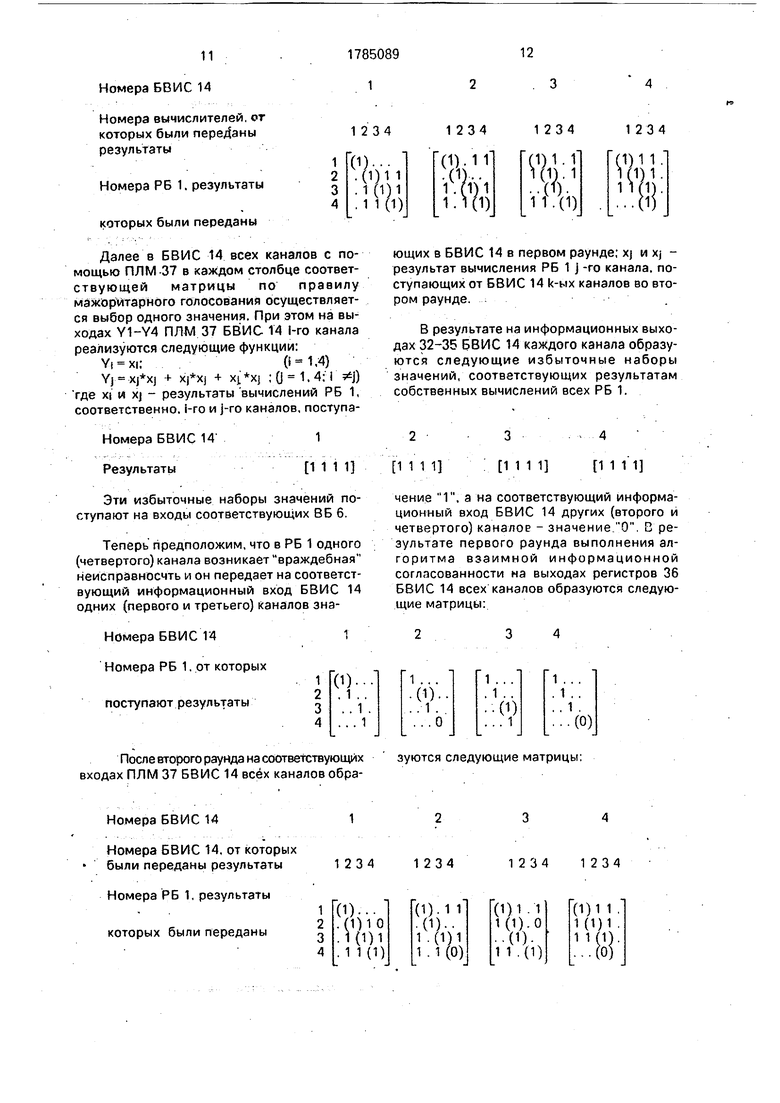

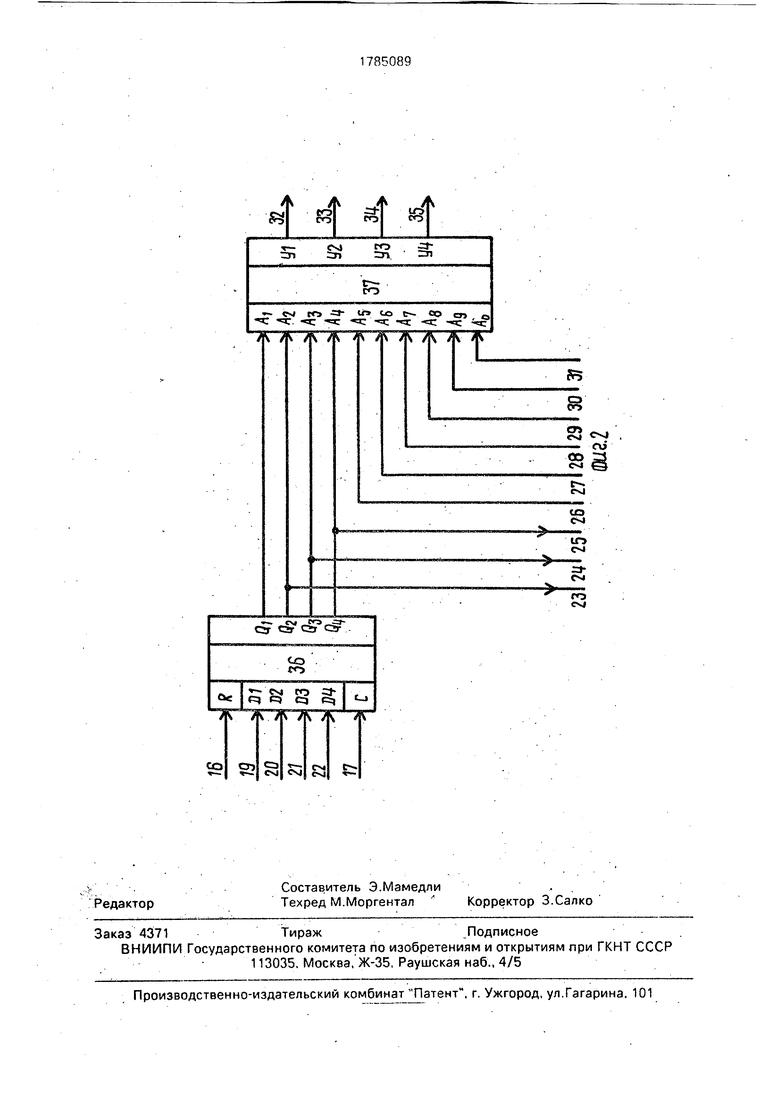

Блок 14 взаимной информационной согласованности каждого канала содержит (см. фиг, 2) регистр 36 и программируемую логическую матрицу 37 (ПЛМ).

5 Информационные входы D1-D4 регистра 36 соединены с группой информационных входов 19-22 блока, входы R установки в состояние О и С синхронизации регистра 36 подсоединены соответственно к входам 17 блока. Соответствующие выходы 01Q4 регистра 36 соединены с группой обменных информационных выходов 23-26 блока и с входами А1-А4 ПЛМ 37, входы А5-А10 которой соединены с группой обменных информационных входов 26-31 блока. Выходы ПЛМ 37соединены с группой информационных выходов 32-35 блока.

Резервированное устройство работает следующим образом.

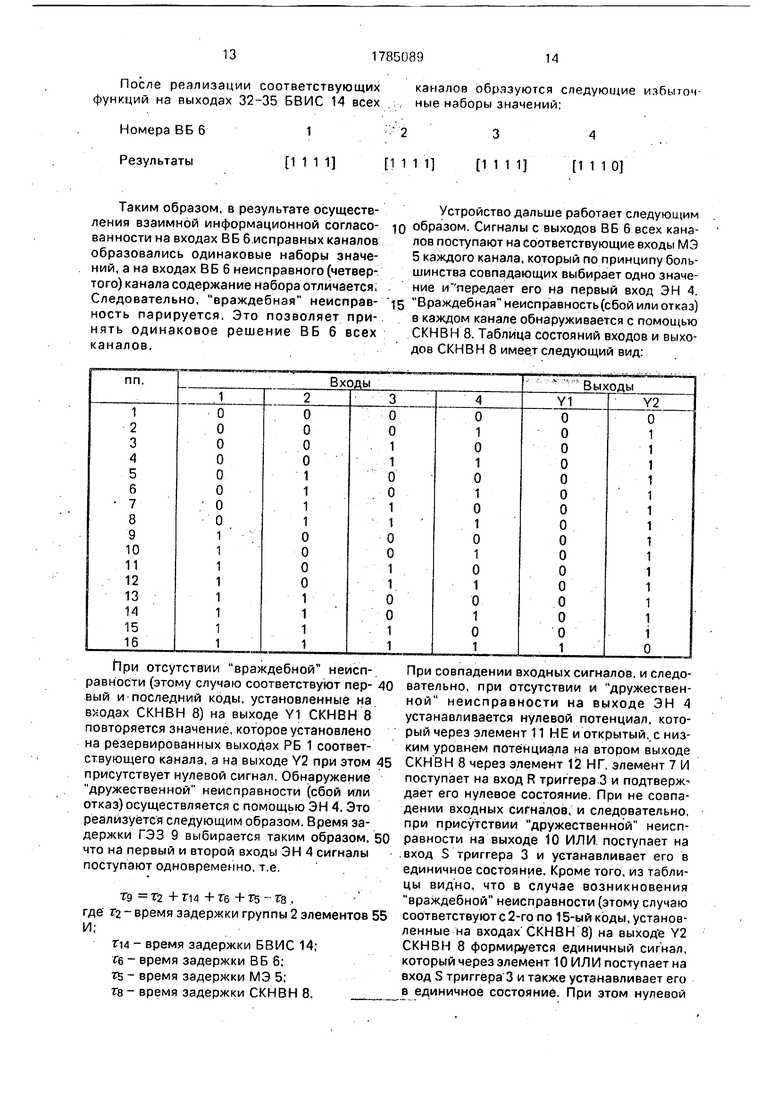

На фиг. 1 приведена функциональная схема предлагаемого устройства, состоящего из четырех каналов. В начале работы триггер 3 и регистр 36 БВИС 14 во всех каналах устанавливаются в состояние О сигналом начальной установки, поступаю- щим на вход 16 устройства. При этом на инверсном выходе триггера 3 устанавливается высокий потенциал, который поступает на первые входы элементов И группы 2 и открывает их. Выходы всех РБ 1 четырех- кратно резервированы, другими словами каждый РБ 1 собственный результат вычисления передает с помощью четырех резервированных шин, Предполагается, что если в РБ 1 отсутствует неисправность или воз- никает только дружественная неисправность, то с его резервированных выходов по всем шинам передается одно и тожё Значе- ние (0 или 1), а если в РБ 1 возникает вражНомера БВИС 14 Номера РБ 1. от которых

поступают результаты

Во втором раунде с соответствующих выходов Q1-Q4 регистра 36 БВИС 14 1-го (I 1,4) канала через группы обменных информационных выходов 23-25 передаются на группу обменных информационных входов 26-31 БВИС 14 -ых 0 - 1.4; И) каналов результаты вычислений РБ 1 k-x (k Г, 4; Щ) каналов Например, с второго выхода Q2 регистра 36 БВИС 14 первого канала через обменный информационный выход 23 передается на соответствующий обменный информационный вход БВИС 14 третьего и четвертого каналов результат вычисления РБ 1 второго канала, с третьего выхода Q3 - через обменный информационный выход 24 передается на соответствующий обменный информационный вход БВИС 14 второго и четвертого каналов результат вычисления РБ 1 третьего канала и, наконец, с четвертого выхода Q4 - через обменный информационный выход 25 передается на соответствующий обменный информационный вход БВИС 14 второго и третьего канадебная неисправность, то с его резервированных выходов по разным шинам передаются разные значения (0 и 1). В первом раунде результат собственного вычисления с резервированных выходов РБ 1 каждого канала, с приходом синхронизирующего импульса по шине 17 устройства, поступает через ГЭЗ 9 на соответствующие входы СКНВН 8 и через соответствующие открытые элементы И группы 2 на соответствующий информационный вход 19-22 БВИС 14 всех каналов. Сначала предположим, что все РБ 1 исправны, а также предположим, что результаты собственных вычислений во всех РБ 1 равны 1. С поступлением синхронизирующего импульса через ЭЗ 15 на входы С регистров 36, результаты вычислений, поступающих на информационные входы 19-22 БВИС 14 каждого канала, записываются в регистры 36 (см. фиг. 2). Время задержки элемента 15 определяется суммарным временем выдачи результата вычисления РБ 1 и задержки группы 2 элементов И. При этом на выходах Q1-Q4 регистров 36 устанавливаются, соответственно, результаты вычислений РБ 1 четырех каналов. В результате во всех БВИС 14 образуются следующие матрицы:

1

$

.1..

()

...(1)

лов результат вычисления РБ 1 четвертого канала, Кроме того, на обменные информационные входы 26 и 27 БВИС 14 первого канала с соответствующих обменных информационных выходов БВИС 14 второго канала поступают, соответственно, результат вычислений РБ 1 третьего и четвертого

каналов, на обменные информационные входы 28 и 29 - с соответствующих обменных информационных выходов БВИС 14 третьего канала поступают, соответственно, результаты вычислений РБ 1 второго и четвертого каналов и, наконец, на обменные информационные входы 30 и 31 - с соответствующих обменных информационных выходов БВИС 14 четвертого канала поступают, соответственно, результаты вычислений второго и третьего каналов. Аналогично, БВИС 14 других кана лов осуществляют обмены между собой. В результате второго раунда на соответствующих входах ПЛМ 37 БВИС 14 всех каналов образуются следующие матрицы:

Номера БВИС 14

Номера вычислителей, от которых были лереДаны результаты

Номера РБ 1. результаты которых были переданы

Далее в БВИС 14 всех каналов с помощью ПЛМ-37 в каждом столбце соответствующей матрицы по правилу мажоритарного голосования осуществляется выбор одного значения. При этом на выходах Y1-Y4 ЛЛМ 37 БВИС 14 1-го канала реализуются следующие функции: YI-XI;(1-1,4)

YJ - + xj.xj ;(J 1.4:1 j) где xi и xj - результаты вычислений РБ 1, соответственно, i-ro и j-ro каналов, поступаНомера БВИС 14 Результаты

1

1111

Эти избыточные наборы значений поступают на входы соответствующих В Б 6.

Теперь предположим, что в РБ 1 одного (четвертого) канала возникает враждебная неисправносчть и он передает на соответствующий информационный вход БВИС 14 одних (первого и третьего) каналов знаНомера БВИС 141

Номера РБ 1, от которых

1234

1 234

1234

1234

%.

л 4 л. л

ющих в БВИС 14 в первом раунде; xj и xj - результат вычисления РБ 1 j -го канала, поступающих от БВИС 14 k-ых каналов во втором раунде.

В результате на информационных выходах 32-35 БВИС 14 каждого канала образуются следующие избыточные наборы значений, соответствующих результатам собственных вычислений всех РБ 1.

1111

1111

1111

чение 1, а на соответствующий информационный вход БВИС 14 других (второго и четвертого) каналов - значение О С результате первого раунда выполнения алгоритма взаимной информационной согласованности на выходах регистров 36 БВИС 14 всех каналов образуются следующие матрицы:

После реализации соответствующих функций на выходах 32-35 БВИС 14 всех

Номера ВБ 6 Результаты

1

(1111

Таким образом, в результате осуществления взаимной информационной согласованности на входах ВБ б исправных каналов образовались одинаковые наборы значений, а на входах ВБ 6 неисправного (четвертого) канала содержание набора отличается, Следовательно, враждебная неисправность парируется. Это позволяет принять одинаковое решение ВБ б всех каналов.

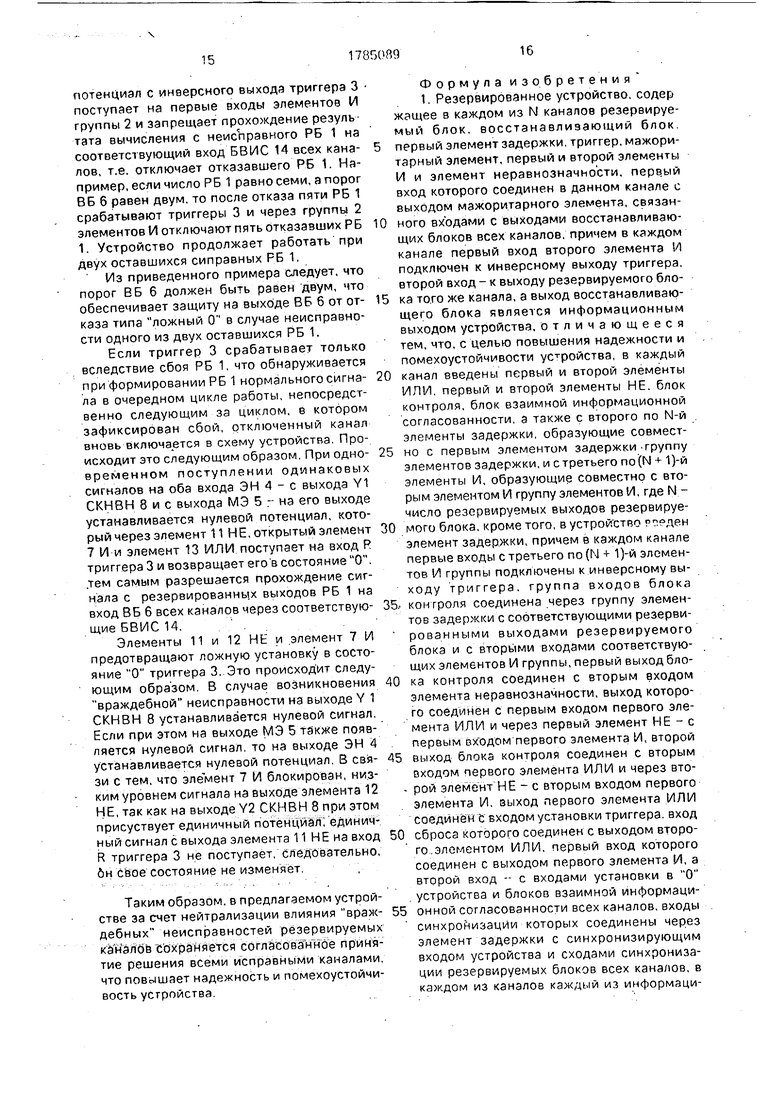

При отсутствии враждебной неисправности (этому случаю соответствуют пер- вый и последний коды, установленные на входах СКНВН 8) на выходе Y1 СКНВН 8 повторяется значение, которое установлено на резервированных выходах РБ 1 соответствующего канала, а на выходе Y2 при этом присутствует нулевой сигнал. Обнаружение дружественной неисправности (сбой или отказ) осуществляется с помощью ЭН 4. Это реализуется следующим образом. Время задержки ГЭЗ 9 выбирается таким образом, что на первый и второй входы ЭН 4 сигналы поступают одновременно, т.е.

Тд Т2 4- Г14 + Тб Н- - Т8 .

где Г2 - время задержки группы 2 элементов И;

ri4 - время задержки БВИС 14;

re - время задержки В Б 6:

Т5 - время задержки МЭ 5;

те - время задержки СКНВН 8.

каналов образуются следующие избыто1 ные наборы значений:

2

111

3 1111

4 1110

Устройство дальше работает следующим образом. Сигналы с выходов ВБ б всех каналов поступают на соответствующие входы МЭ 5 каждого канала, который по принципу большинства совпадающих выбирает одно значение и передает его на первый вход ЭН 4. Враждебная неисправность (сбой или отказ) в каждом канале обнаруживается с помощью СКНВН 8. Таблица состояний входов и выходов СКНВН 8 имеет следующий вид:

При совпадении входных сигналов, и следовательно, при отсутствии и дружественной неисправности на выходе ЭН 4 устанавливается нулевой потенциал, который через элемент 11 НЕ и открытый, с низким уровнем потенциала на втором выходе СКНВН 8 через элемент 12 НГ, элемент 7 И поступает на вход R триггера 3 и подтверждает его нулевое состояние При не совпадении входных сигналов, и следовательно, при присутствии дружественной неисправности на выходе 10 ИЛИ поступает на вход S триггера 3 и устанавливает его в единичное состояние. Кроме того, из таблицы видно, что в случае возникновения враждебной неисправности (этому случаю соответствуют с 2-го по 15-ый коды, установленные на входах СКНВН 8) на выход е Y2 СКНВН 8 формируется единичный сигнал, который через элемент 10 ИЛИ поступает на вход S триггера 3 и также устанавливает его в единичное состояние, При этом нулевой

потенциал с инверсного выхода триггера 3 поступает на первые входы элементов И группы 2 и запрещает прохождение резуль тата вычисления с неисправного РБ 1 на соответствующий вход БВИС 14 всех каналов, т.е. отключает отказавшего РБ 1. Например, если число РБ 1 равно семи,а порог ВБ б равен двум, то после отказа пяти РБ 1 срабатывают триггеры 3 и через группы 2 элементов И отключают пять отказавших РБ 1. Устройство продолжает работать при двух оставшихся сиправных РБ 1.

Из приведенного примера следует, что порог ВБ б должен быть равен двум, что обеспечивает защиту на выходе ВБ б от отказа типа ложный 0 в случае неисправности одного из двух оставшихся РБ 1.

Если триггер 3 срабатывает только вследствие сбоя РБ 1, что обнаруживается при формировании РБ 1 нормального сигнала в очередном цикле работы, непосредственно следующим за циклом, в котором зафиксирован сбой, отключенный канал вновь включается в схему устройства Происходит это следующим образом При одно- временном поступлении одинаковых сигналов на оба входа ЭН 4 - с выхода Y1 СКНВН 8 и с выхода МЭ 5 - на его выходе устанавливается нулевой потенциал, который через элемент 11 НЕ, открытый элемент 7 И и элемент 13 ИЛИ поступает на вход Р триггера 3 и возвращает его в состояние О .тем самым разрешается прохождение сигнала с резервированных выходов РБ 1 на вход ВБ б всех каналов через соответствующие БВИС 14.

Элементы 11 и 12 НЕ и элемент 7 И предотвращают ложную установку в состояние О триггера 3. Это происходит следующим образом В случае возникновения враждебной неисправности на выходе Y 1 СКНВН 8 устанавливается нулевой сигнал Если при этом на выходе МЭ 5 также появляется нулевой сигнал то на выходе ЭН 4 устанавливается нулевой потенциал В связи с тем. что эле мент 7 И блокирован, низким уровнем сигнала на выходе элемента 12 НЕ, так как на выходе Y2 СКНВН 8 при этом присуствует единичный потенциал, единичный сигнал с выхода элемента 11 НЕ на вход R триггера 3 не поступает, следовательно, он свое состояние не изменяет

Таким образом, в предлагаемом устройстве за счет нейтрализации влияния враждебных неисправностей резервируемых каналов сохраняется согласованное принятие решения всеми исправными каналами, что повышает надежность и помехоустойчивость устройства

Формула изобретения 1 Резервированное устройство, содер жащее в каждом из N каналов резервируемый блок, восстанавливающий блок

первый элемент задержки триггер, мажоритарный элемент, первый и второй элементы И и элемент неравнозначности, первый вход которого соединен в данном канале с выходом мажоритарного элемента, связан0 ного входами с выходами восстанавливающих блоков всех каналов, причем в каждом канале первый вход второго элемента И подключен к инверсному выходу триггера, второй вход - к выходу резервируемого бло5 ка того же канала, а выход восстанавливающего блока является информационным выходом устройства, отличающееся тем, что, с целью повышения надежности и помехоустойчивости устройства, в каждый

0 канал введены первый и второй элементы ИЛИ первый и второй элементы НЕ. блок контроля, блок взаимной информационной согласованности а также с второго по М-й элементы задержки, образующие совмест5 но с первым элементом задержки группу элементов задержки, и стретьего no(N + 1)-й элементы И, образующие совместно с вторым элементом И группу элементов И, где N - число резервируемых выходов резервируе0 мого блока, кроме того, в устройство элемент задержки, причем в каждом канале первые входы с третьего no (N + 1)-й элементов И группы подключены к инверсному выходу триггера, группа входов блока

5- контроля соединена через группу элементов задержки с соответствующими резерви- рованными выходами резервируемого блока и с вторыми входами соответствующих элементов И группы, первый выход бло0 ка контроля соединен с вторым входом элемента неравнозначности, выход которого соединен с первым входом первого элемента ИЛИ и через первый элемент НЕ - с первым входом первого элемента И, второй

5 выход блока контроля соединен с вторым

входом первого элемента ИЛИ и через вто- рой элемент НЕ - с вторым входом первого

элемента И. выход первого элемента ИЛИ

соединен t входом установки триггера вход

0 сброса которого соединен с выходом второго элементом ИЛИ, первый вход которого соединен с выходом первого элемента И, а второй вход -- с входами установки в О устройства и блоков взаимной информаци5 онной согласованности всех каналов, входы синхронизации которых соединены через элемент задержки с синхронизирующим входом устройства и сходами синхронизации резервируемых блоков всех каналов, в каждом из каналов каждый из информационных входов группы блока взаимной информационной согласованности соединен с соответствующим выходом группы элементов И всех каналов группа обменных информационных выходов - с группой обменных информационных входов блоков взаимной информационной согласованности других каналов, а группа информационных выходов - с группой входов восстанавливающего блока.

ческой матрицы, а также регистр, информационные входы которого соединены с группой информационных входов блока, входы установки в О и синхронизации соединены с одноименными входами блока, группа выходов регистра соединена с первой группой входов программируемой логической матрицы, вторая группа в-ходов которой является группой обменных информационных входов блока, а группа выходов программируемой логической матрицы является группой Информационных выходов блока, а соответствующие выходы группы выходов perncf pa являются группой обменных информационных выходов §/юка

af sf sf tef

т-СЧ1ГОCJ

m i л л

T- ЈH toc--cocn e

кся с «1:1ч: :«:-ч;-ч:-«а:-«с i

vv/r/v:7rir;v /ГУГА

- CN car ca сэ5S 8

t

/v / yv

0}

ем

NJ

Гч txj

1

S3 oj

ro

CO

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| РЕЗЕРВИРОВАННОЕ УСТРОЙСТВОE:?^'iJV. -, | 0 |

|

SU314206A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1992-12-30—Публикация

1991-06-17—Подача