Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении управляющих вычислительных устройств высокой надежности. .

Цель изобретения - повьшение надежности системы путем передачи функций отказавшего вычислительного блока вычислительному блоку другого канала .

На фиг. 1 представлена структурная схема мажоритарно-резервированной управляющей вычислительной системы для конкретного случая, соответствующего числу каналов h 3, на фиг. 2 - ма резервируемого вычислительного блока; на фиг. 3 - схема контроля; на фиг. 4 - схема коммутатора режима работы ; на фиг. 5 - схема элемента связи; на фиг. 6 - схема блока ввода-вьшодаходов.

на 16. входов и 16ц выcxe

Мажоритарно-резервированная система (фиг. 1) содержит каналы t, в казкдый из которых входит резервируе- мый вычислительный блок 2, блок 3 контроля, триггер 4 цикла, коммутатор 5 режима работы, первьй 6 и .второй 7 элементы связи, блок 8 ввода- вьшода. В каждом канале 1 содержатся управлякщий выход 9 блока контроля, входы-выходы 10 вычислительного блока, соединенные с первыми входами- выходами элементов 6 и 7 связи и входами блока 3 контроля, первый вход 11, второй вход 12 и третий вход 13 коммутатора 5 режима работы, первый выход 14 и второй выход 15 коммутатора 5 режима работы, соединенные с входами управления элементов 6 и 7 связи соответственно.Мажоритарно резервированная система содержит также адресно-информационно- управляющие шины 16 - 18 первого, второго и третьего каналов соответственно, а также входы 19 системы,мажоритарные элементы 20 (по числу выходов) , подключенные к выходам 2 Г блоков 8 ввода-вывода, и выходы 22 системы. Вторые входы-выходы элемента 6 связи в каждом i -ом канале ( 1 1, 2..., ц) подключены к адрес но-информационно-управляющей шине своего канала, & вторые входы-выходы элемента 7 - к адресно-информационно управляющей шине последующего (-nl)-го канала, каждая ,из адресно-йнфор- мационно-управляющих шин подключена

cx

k входам-выходам блока ввода-вьшода своего канала управляющий выход 9 блока 3 контроля ()-го канала подключен к входу 11 коммутатора 5 режима работы (i+1)-ro канала и входу 12 коммутатора 5 режима работы j -го канала, сйнхровыход блока 3 кон30

35

40

55

троля подключен к входу триггера 4 цикла, выход которого соединен с 10 третьим входом 13 коммутатора 5 режима работы.

Резервируемый вычислительный блок содержит (фиг. 2) арифметико-логическое устройство (АЛУ) 23 с микропрог- f5 раммной управляющей памятью (УП) 24, системный контроллер 25 с УП 26,ре- гистр 27 адреса запоминакнцего устройства (ЗУ), накопитель ЗУ и контроллер 29 ЗУ. 20 Вычислительньй блок содержит также входы 30,-ЗОэ адреса модуля ЗУ, адресно-информационные входы-выходы ,j , выход }0„ синхросигнала адреса, выход 10 25 нйя данных, выход 10

18

УO

сигнала чте- ,9 сигнала запи- сигнала ответа

сигнала начальной уста45

50

си данных, вход 10, и выход 10,; новки.

На фиг. 3 приведены схема 31 срав- нения, триггер 32 адреса, генератор 33 импульсов, двоичный счетчик 34, триггер 35, логический элемент И 36, логический элемент ИЛИ 37, элемент 38 временной задержки, образунядие блок 3 контроля. Блок 3 контроля имеет входы 39, установки адреса адресно-информационные входы схемы 31 соединены с входо-выходами , блока 2, С-вход триггера 32 - с выходом блока 2, R -вход триггера 35 - С выходом lOj, блока 2, а один из входов элемента И 36 - с выходом 10( блока 2.

Ком татор 5 содержит (фиг. 4) элементы НЕ 40-42, элементы И 43 и 44, элемент ИЛИ 45 и элементы И 46- 47, с открыть коллектором.

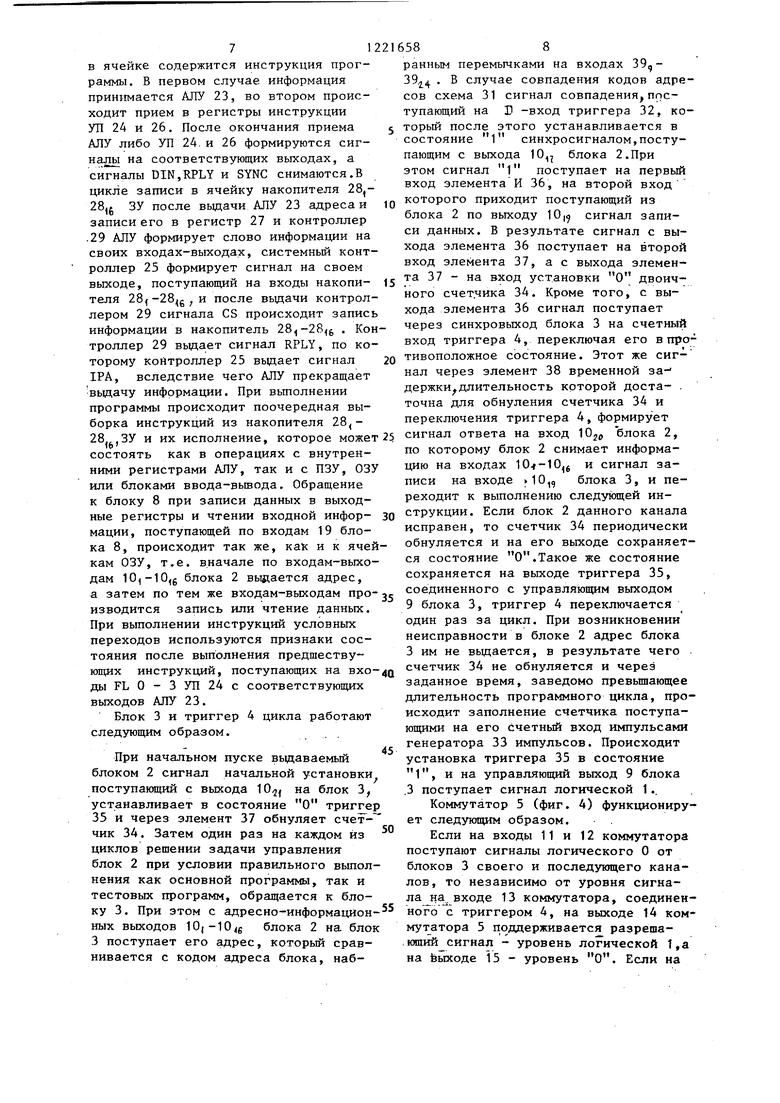

Элементы связи содержат (фиг. 5) приемопередатчики 48, ,состоящие из элементов ИЛИ-НЕ 49, элемента И- НЕ 50 с состоянием высокого импеданса- элемента НЕ 51 и элемента 52 с состоянием высокого импеданса, и при- емо-передатчики 53,-534 входами 54 и 55 состоящие из элементов НЕ 56 и элемента 57 с состоянием высокого импеданса.

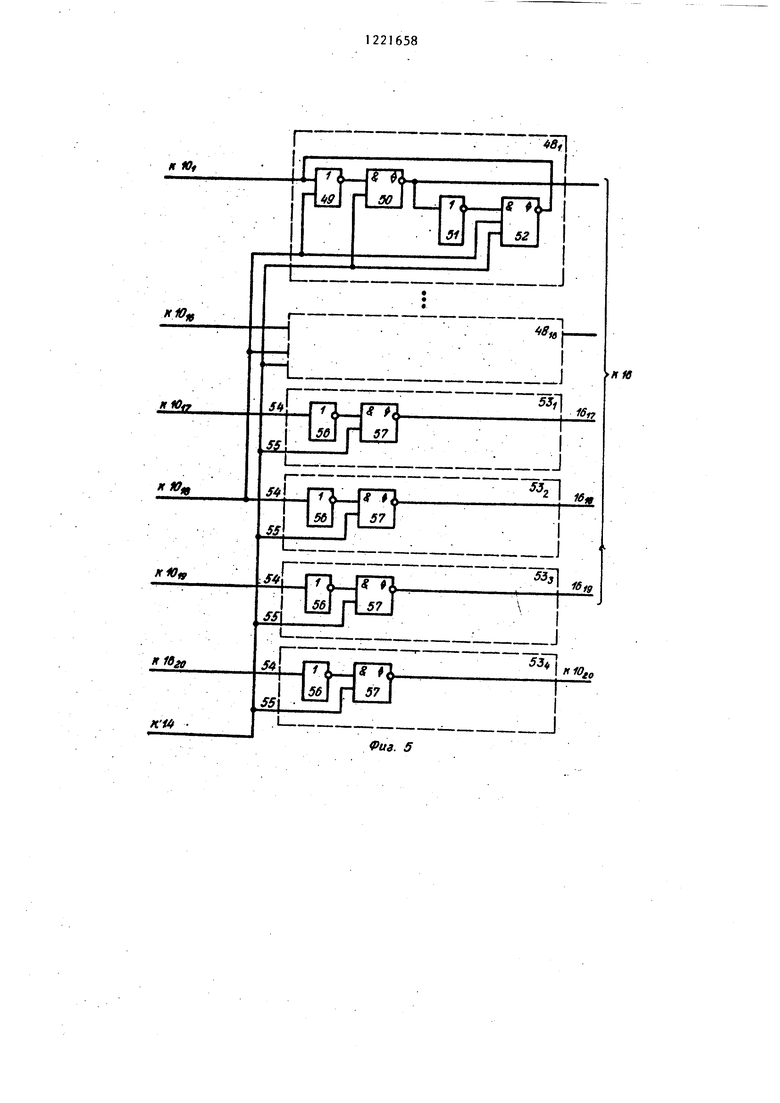

Блок ввода-вьшода 8 содержит {фиг. 6) магистральные элементы 58,

58 . выходные регистры 59к , регистр 60 адреса, дешифраторы 61 и 62 адреса, элементы И 63, , 63, 64, и 64 и , элемент ИЛИ 65 и элемент 66 задержки.

В мажоритарйо-резервированной управляющей вычислительной системе каналы 1 функционируют независимо и асинхронно, решая задачу управления многократно на следующих друг . за другом циклах, при этом длительность одного цикла решения зддачи управления обеспечивается заведомо меньшей, чем допустимое (по условиям управляемого объекта) время запазды вания в вьща,че изменения управляющего воздействия. При любой рассинхро- низации задержка выдачи достоверных сигналов на выходах мажоритарных элементов 20 не превосходит длительнос

ти одного цикла решения задачи управ ; ления и, следовательно допустимого за- паздьюания.

Мажоритарно-резервированная управляющая вычислительная система работает следующим образом.

Блоки 2 каждого из каналов в соответствии с заложенными в их ПЗУ одинаковыми программами решают задачу управления, производя опрос источников информации и вырабатывая в качестве результата выходные дискретные сигналы управления. Входная дискре-Р- ная информация поступает на входы 19 и затем на входы блоков 8 ввода- вывода всех каналов 1, откуда по запросам блоков 2 передается по адрес- но-информационно-управляющим шинам 16-18 в каждом канале через элементы 6 в блоки 2. Результаты решения выдаются блоками 2 последовательно через элементы 6 на соответствующие каналам адресно-информационно-управ- ляющие шины 16 - 18 и принимаются в блоки 8, откуда через выходы 21 поступают на входы элементов 20, выходы KOTopbJX являются выходами 22 -системы и могут быть соединены с исполнительными органами управляемого объекта.

При исправном блоке 2 после окончания решения им заданного алгоритма управления и проведения всех пре- дусмотренньк программой тестовых проверок завершается цикл работы и автоматически начинается следукпций цикл работы блока 2 по той же программе. Длительность цикла не должна

10

5

20

2216584

превьш1ать допустимого (по условиям управляемого объекта) времени запаз- дьшания реакции управляющей системы на изменение входной информации;бло, ки 2 каналов 1.не взаимодействуют и работают асинхронно. Блок 3 проверяет правильность прохождения программ по окончании- каждого цикла работы блока 2 своего канала, формируя при этом сигнал об исправности блока 2. Сигнал об исправности с управляющего выхода 9 блока 3 поступает на вход 11 коммутатора 5 своего (i -го) канала (i 1, 2, 3,...,п) и на вход 12 коммутатора 5 предшествующего ( 1 -1-го) канала (для первого канала предшествующим является и -и. Если исправны блоки i -го и последующего («+1)-го каналов (для п -го канала последующим является первый), то сигналы исправности, поступающие на входы 11 и 12 коммутатора 5 || -го канала, независимо от сигнала, поступающего на вход 13 того

25 же блока, обеспечивают выбор режима, при котором с выхода 14 блока 5 nocf тупает сигнал разрешения на вход управления элемента 6, а с выхода 15 не поступает сигнал разрешения на вход элемента 7 связи. При этом блок 2 i -го канала через элемент 6 подключен к адресно-информационно- упра вляющей шине своего }.-го канала и через нее связан с блоком ввода- вьгаода своего канала. Таким образом, ,

при исправных блоках 2 всех каналоэ в системе не происходит никаких переключений потоков информации между каналами. Например, при формировании блоками 3 сигналов исправности блоков второго и третьего каналов в блок 2 второго канала через элемент 6 подключен к адресно-информационно-управ- ляющей шине 17 своего второго канала. При исправности блоков 2 всех каналов каждый из них связан своей адресно-информационно-управляющей шиной с блоком 8 своего канала и все каналы функционируют независимо друг от друга.

При возникновении неисправности в блоке 2 канала, приводящей к невыполнению за время цикла работы основной программы или к непрохождению тестовых программ, производится пере55 распределение потоков информации между каналами, тем самым система переводится в более отказоустойчивое состояние. В случае возникновения неис46

45

50

5

правности блока 2 ()-гo канала orta обнаруживается в своем канале блоком 3 и на его управляющем выходе 9 формируется сигнал о неисправности блока 2, который поступает на вход 11 коммутатора 5 режима работы (i+1)-ro канала и вход 12 коммутатора 5 i-го канала. При этом коммутатор 5(1+1)-го канала переводится в состояние, в котором с его выходов 14 и 15 сигналы разрешения не вьздаются и элементы 6 и 7 (iH-l)-ro канала отключены.

Если при этом блок 2 -го канала исправен, то сигнал об исправном его состоянии, поступающий на вход 11 коммутатора 5 i -го канала, и сигнал о неисправности блока (i+1)-ro канала, поступающий н а вход 12 того же коммутатора, обеспечивают выбор режима, в котором состояние выходов 14 и 15 коммутатора 5 i -го канала определяется сигналом, поступающим на его вход 13 с выхода триггера 4. Состояние триггера 4 изменяется в

но-управляющие шины 16 и 17 соответственно первого и второго каналов. Более того если обнаруживается неисправность еще в одном из оставших- 5 ся блоков 2, принадлежащих первому или третьему каналам, то и в этом случае система сохранит работоспособность,, так как исправный блок 2 одного из каналов, например, третьего

10 через адресно-информационно-управля- ющие шины 18 и 16 попеременно (через цикл) обслуживают блоки 8 своего третьего и первого каналов соответственно. При этом элементы 20, получа15 ющие одинаковую информацию по двум входам из трех, формируют на своих выходах 22 достоверные сигналы управления.

Блок 2 (фиг. 2) работает следую20 щим образом.

После включения напряжения питания УП 24 и 26 вьщают серии микроин- , струкций, соответствуклцие микропрогконце каждого программного цикла сиг-25 рамме начального пуска. После появ- налом, поступакидим на его счетный ления очередных микроинструкций на вход с синхровыхода блока 3. На следующих один за другим -программных циклах коммутатором 5 i -го канала

выходах MIN& УП 24 и 26 они записьгоа- ются в регистры микроинструкций АЛУ 23 и системного контроллера 25 по

сигналам, поступающим на их входы С.

попеременно вьщаются сигналы разреше- 30

ния либо с выхода 14 на вход управ- ления элемента 6, либо с выхода 15 на вход управления элемента 7, так что блок 2 1 -го канала связывается через соответствующие адресно-инфор- мационно-управляющие шины попеременно с блоками 8 i -го и (i +1)-го каналов. Таким образом, при возникновении неисправности блока 2 B(j+1)-M канале его функции берет на себя блок 2 i -го канала. Поскольку обмен информацией с блоками 8 j-го и (i +1)-го каналов происходит последовательно в разные по времени программные циклы, то сохраняется асин- jcpoHHocTb работы блоков 2 и блоков В

Если, например, в трехканальной системе (фиг. 1) обнаруживается неисправность блока 2 второго канала, в то время как блок 2 первого канал исправен, то с выхода 9 блока 3 второго канала сигнал о неисправности блока 2 поступает на вход 11 коммутатора 5 второго канала и вход 12 коммутатора 5 первого канала. В результате, элементы 6 и 7 второго канала отключены, а элементы 6 и 7 первого канала попеременно через цикл работают на адресно-информацион

216586

но-управляющие шины 16 и 17 соответственно первого и второго каналов. Более того если обнаруживается неисправность еще в одном из оставших- 5 ся блоков 2, принадлежащих первому или третьему каналам, то и в этом случае система сохранит работоспособность,, так как исправный блок 2 одного из каналов, например, третьего

10 через адресно-информационно-управля- ющие шины 18 и 16 попеременно (через цикл) обслуживают блоки 8 своего третьего и первого каналов соответственно. При этом элементы 20, получа15 ющие одинаковую информацию по двум входам из трех, формируют на своих выходах 22 достоверные сигналы управления.

Блок 2 (фиг. 2) работает следую20 щим образом.

рамме начального пуска. После появ- ления очередных микроинструкций на

выходах MIN& УП 24 и 26 они записьгоа- ются в регистры микроинструкций АЛУ 23 и системного контроллера 25 по

рамме начального пуска. После появ- ления очередных микроинструкций на

сигналам, поступающим на их входы С.

Закончив вьтолнение очередных микроинструкций, АЛУ 23 и контроллер 25 выдают сигналы F, по которым УП 24 и 26 выдают следующие микроинструкции. В цикле чтения ЗУ УП 24 и 26 вы-г дают микроинструкции, по которым АЛУ формирует на входах-выходах DA адрес ячейки накопителя ЗУ, а системный контроллер выдает сигнал SYNCL по которому адрес записьшается частично в регистр 27, а частично-- в контроллер 29 ЗУ. Затем системный контроллер вьщает сигнал DIN.Если код адреса, принятьй контроллером 29 ЗУ по входам,совпадает с адресом модуля ЗУ, набранным перемычками на входах 30, -302 и 30 блока 2, то контроллер 29 формирует на выходе сигнал выбора кристалла, по которому накопитель 28j-28 g вьщает содержимое выбранной ячейки на свои входы-выходы. Контроллер 29 сопровождает выдаваемую накопителем ЗУ информацию сигналом ответа по выходу RPLY. По этому сигналу системный контроллер 25 формирует сигнал на своем входе-выходе ОРА I, если в выбранной ячейке накопителя ЗУ содержится числовой операнд, либо на выходе ОРА 2, если

71

в ячейке содержится инструкция программы. В первом случае информация принимается АЛУ 23, во втором происходит прием в регистры инструкции УТТ 24 и 26, После окончания приема АЛУ либо УП 24. и 26 формируются сигналы на соответствующих выходах, а сигналы DINjRPLY и SYNC снимаются.В цикле записи в ячейку накопителя 28,28

1Ё

ЗУ после выдачи АЛУ 23 адреса и записи его в регистр 27 и контроллер .29 АЛУ формирует слово информации на своих входах-выходах, системный контроллер 25 формирует сигнал на своем вьгкоде, поступающий на входы накопи- теля 28f-28 g, и после выдачи контроллером 29 сигнала CS происходит запись информации в накопитель . Контроллер 29 вьщает сигнал RPLY, по которому койтроллер 25 вьщает сигнал IPA, вследствие чего АЛУ прекращает вьиачу информации. При вьтолнении программы происходит поочередная выборка инструкций из накопителя 28(- 28 ЗУ и их исполнение, которое может состоять как в операциях с внутренними регистрами АЛУ, так и с ПЗУ, ОЗУ или блоками ввода-вьшода. Обращение к блоку 8 при записи данных в выходные регистры и чтении входной инфор- мации, поступающей по входам 19 блока 8, происходит так же, как и к ячейкам ОЗУ, т.е. вначале по входам-выходам 10,-10,g блока 2 выдается адрес, а затем по тем же входам-выходам производится запись или чтение данных. При выполнении инструкций условных переходов используются признаки состояния после выполнения предшествующих инструкций, поступающих на входы FL О - 3 УП 24 с соответствующих выходов АЛУ 23.

Блок 3 и триггер 4 цикла работают следующим образом.

При начальном пуске вьвдаваемый блоком 2 сигнал начальной установки поступающий с выхода 10 на блок 3, устанавливает в состояние О триггер 35 и через элемент 37 обнуляет счет- чик 34. Затем один раз на каждом из циклов решении задачи управления блок 2 при условии правильного выполнения как основной программы, так и тестовых программ, обращается к блоку 3. При этом с адресно-информацйонных вькодов 10, блока 2 на блок 3 поступает его адрес, который сравнивается с кодом адреса блока, наб6588

ранным перемычками на входах 39,- 39 . В случае совпадения кодов адресов схема 31 сигнал совпадения,поступающий на Б -вход триггера 32, который после этого устанавливается в состояние 1 синхросигналом,поступающим с выхода 10, блока 2.При этом сигнал 1 поступает на первый вход элемента И 36, на второй вход которого приходит поступающий из блока 2 по выходу 10, сигнал записи данных. В результате сигнал с выхода элемента 36 поступает на второй вход элемента 37, а с выхода элемента 37 - на вход установки О двоичного счетчика 34. Кроме того, с выхода элемента 36 сигнал поступает через синхровыход блока 3 на счетный вход триггера 4, переключая его в противоположное состояние. Этот же сигнал через элемент 38 временной за-- держки длительность которой доста- . точна для обнуления счетчика 34 и переключения триггера 4, формирует сигнал ответа на вход блока 2, по которому блок 2 снимает информацию на входах и сигнал записи на входе 10,, блока 3, и переходит к выполнению следукяцей инструкции. Если блок 2 данного канала исправен, то счетчик 34 периодически обнуляется и на его выходе сохраняется состояние О.Такое же состояние сохраняется на выходе триггера 35, соединенного с управляющим вьгходом 9 блока 3, триггер 4 переключается один раз за цикл. При возникновении неисправности в блоке 2 адрес блока 3 им не вьщается, в результате чего счетчик 34 не обнуляется и через заданное время, заведомо превышающее длительность программного цикла, происходит заполнение счетчика поступающими на его счетный вход импульсами генератора 33 импульсов. Происходит установка триггера 35 в состояние 1, и на управляющий выход 9 блока .3 поступает сигнал логической 1..

Коммутатор 5 (фиг. 4) функционирует следующим образом.

Если на входы 11 и 12 коммутатора поступают сигналы логического О от блоков 3 своего и последующего каналов, то независимо от уровня сигнала на входе 13 коммутатора, соединенного с триггером 4, на выходе 14 коммутатора 5 поддерживается разреша- ющий сигнал - уровень логической 1,а на быходе 15 - уровень О. Если на

91

вход 11 коммутатора поступает сигнал 1, то с выходов 14 и 15 коммутатора выдаются сигналы О. Если на входе 11 коммутатора - логический О, а на входе 12 коммутатора - логическая 1, то сигналы на выходах 14.-и 15 коммутатора имеют противоположные значения, определяемые уровнем сигнала на входе 13 коммутатора.

Элемент 6 (фиг. 5) работает еле- дующим образом.

Если с выхода 14 на вход элемента 6 поступает разрешающий сигнал 1, а с выхода lOjg блока 2 - О (чтение данных отсутствует), то происходит передача информации от входов-выхо-. дов 10|-10i6 блока 2 к входам-выходам через элементы 49 и 50 приемопередатчиков 48,-48(6, при этом выходы элементов 52 находятся в высокоимпе- дансном состоянии. Если сигнал с выхода 10,g соответствует логической 1 (происходит чтение данных), то передача информации идет от шины 16 к входам-выходам 10|-10 g блока 2 через элементы 51 и 52, при этом в высоко- импедансном состоянии находятся элементы 50. В обоих случаях происходит передача управлякнцих сигналов от выходов 1017 блока 2 к шине 16 и к входу через элементы 56 и 57. Если с выхода 14 на вход элемента 6 поступает сигнал логического О,то выходы элементов 50, 52 и 57 находятся в высокоимпедансном состоянии и ий- формация через элемент 6 связи не передается, так как он отключен как от блока 2, так и. от адресно-информа- ционно-управляющей шины 16. Работа элемента 7 связи аналогична работе элемента 6.

Блок 8 ввода-вьшода (фиг. 6) работает следующим образом.

Адрес одного из шестнадцати разрядных слов входной информации, пос- тупающей на блок 1 с входа 19 системы, вьщается блоком 2 через элемент 6, адресно-информационно-управля15щую шину 16 на блок 8 и по синхросигналу

приема адреса, поступающему тем же

путем на вход блока 8, записывается в регистр 60 адреса. После дешифрации адреса дешифратором 61 поступает сигнал на первый вход одного из элементов И 63,.-63,„ соответствующего 55 адресу слова входной информации. При поступленин на вторые входы элементор И 63,-63т с входа блока 8 сигнала

5

ю

is 20 25 о 5 д

0

5

65810

чтения данных на управляющий вход одного из элементов 58 -58jy, поступает сигнал 1, открывая его для прохождения слова входной информации, присутствующего на его входах, на входы-вьгходы с шины 16 и далее через шину. 16 и элемент 6 поступает на входы-выходы блока 2. Выходы остальных элементов 584-58 остаются при этом в высокоимпедансном состоянии. Через элемент ИЛИ 65 и элемент 66, длительность задержки которого достаточна для установления информации на входах-выходах 10,- 10(g блока 2, на выход блока 8 вьщается сигнал ответа, при поступлении которого на вход блока 2 информация принимается блоком 2. ,Цля записи слова данных в один из регистров 59;,-59 блока 8 адрес, регистра аналогичным образом выдается блоком 2 в регистр 60 адреса блока 8, с выхода дешифратора 62 поступает сигнал на первый вход соответствующего адресу слова элемента И . Затем блок 2 выдает на входы-выходы слово данных, поступающее через элемент 6 и шину 16 на входы блока ввода-вывода, и сигнал записи данных, поступающий тем же путем на вход блока 8 и далее на вторые входы элементов (;. С выхода выбранного элемента 64 -64 поступает сигнал на синхровход записи соответствующего данного адресу регистра 59, -59. и данные записываются в этот регистр. Сигнал ответа, формируемьй элементами 65 и 66, поступает на выход и далее в блок-2, который снимает слово данных с входов-выходов 10 -10i6 и сигнал записи данных с выхода 10 , переходя к выполнению следующей инструкции программы. С выходов 21.- 21k (6 блока 8 обновленная информация поступает на входы элементов 20.

: В предлагаемой мажоритарно-резервированной управляющей вычислительной системе повьштается отказоустойчивость вследствие того, что функции отказавшего вычислительного блока передаются вычислительному блоку другого канала. Ввиду того, что в известных мажоритарно-резервированных уп- равляющих вычислительных системах наибольший вклад в вероятность отказа системы обусловлен сочетаниями неисправности вычислительного блока одного из каналов с неисправностью одного

n

или нескольких входов-выходов блока ввода-вьтода другого канала, применение в предлагаемой системе замещения вычислительных блоков позволяет значительно повысить надежность.

Формула изобретения

Мажоритарно-резервированная , угг- равляющая система, содержащая в каждом канале резервируемый вычислитель- ньш блок, входы-выходы которого подключены к входам блока контроля и через первый элемент связи - к адрес- но-информационно-управляющей шине канала, подключенной к блоку ввода- вывода, причем выходы блоков ввода- вьгаода всех каналов подключены к соответствующим входам мажоритарных элементов, отличающаяся тем, что, с целью повышения надеж- ности системы, в каждьш канал введе65812

ны второй элемент связи, триггер цикла и коммутатор режима работы, первы входы-выходы второго элемента связи подключены к входам-выходам резервируемого вычислительного блока данного канала, вторые входы-выходы - к адресно-информационно-управляющей шине последующего канала, первый вход коммутатора режима работы подключен к управляющему выходу блока контроля данного канала, второй вход к управляющему выходу блока контроля последующего канала, третий вхоД - к выходу триггера цикла, счетный вход которого соединен с синхровьгхо- дом блока контроля данного канала, первьй выход коммутатора режима работы подключен к входу управления первого элемента связи, второй выход - к входу управления второго элемента связи.

16 17 18

. 1

22

. 2

OmlOf

От lOiS

15

39„

В

31

D

32

От 10ti

Л

f-1

СТ2

54

Г

J5

От Ю.

19

rtU

Зв

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОПРОЦЕССОРНАЯ УПРАВЛЯЮЩАЯ СИСТЕМА | 1993 |

|

RU2054710C1 |

| Мажоритарно-резервированный интерфейс памяти | 1980 |

|

SU953639A1 |

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| Трехканальная мажоритарно-резервированная система | 1981 |

|

SU1104696A1 |

| Резервированная система | 1982 |

|

SU1101827A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2474868C1 |

| Многоканальная система программного управления объектами | 1985 |

|

SU1278813A1 |

| Микропроцессорная система | 1989 |

|

SU1686454A1 |

| Программируемый контроллер | 1987 |

|

SU1442976A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении управляющих вычислительных устройств высокой надежности. Целью иэоб- ретения является повьшение надежное- ти системы за счет передачи функций отказавшего вычислительного блока вычислительному блоку другого канала. Мажоритарно-резервированная система содержит в каждом канале резервируе мый вычислительный блок, блок контроля, триггер цикла, коммутатор режима работы, элементы связи и блок ввода- вьшода. Цель изобретения Достигается за счет того, что при обнаружении неисправности блока одного из каналов сигнал неисправности поступает на вход коммутаторов,которые подключают соседний исправный канал попеременно (через такт) на место отказавшего канала и па свое место. 6 ил. (Л

Рие. 3

// 12

tiO

41

«г

/

ts

f

47

| УСТРОЙСТВЮ ДЛЯ ПЕРЕКЛЮЧЕНИЯ КАНАЛОВ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 0 |

|

SU383047A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения упрочненного металломатричного композита на основе среднеэнтропийного сплава | 2023 |

|

RU2813079C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1986-03-30—Публикация

1984-08-25—Подача