ходов каждого из каналов. В паузах между управляющими словами проверяется блок 4 ключей подачей сигналов Лог.Г и Лог.О на его входы. Выходные сигналь блока 4 ключей контролируются элементами 17, 15, 16. Считывание сигналов ошибки и подача управляюп|их воздействий обеспечиваются блоком 9 управления резервом. Сигналы ошибки через элемент ИЛИ 19 воздействуют на элемент И-НЕ 20, со- единение которых в трех каналах образует трехфазный триггер, подключающий выходы блока 4 ключей одного из исправных каналов к общей магистрали, 1 з.п. ф-лы, 4 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное устройство | 1989 |

|

SU1635185A1 |

| Многоканальное устройство управления резервированной системой | 1978 |

|

SU744571A1 |

| Устройство для приема информации | 1988 |

|

SU1552216A1 |

| Многоканальное устройство управления резервированной системой | 1975 |

|

SU526893A1 |

| Устройство для обработки информации | 1990 |

|

SU1758649A1 |

| Устройство для обмена данными | 1985 |

|

SU1297067A1 |

| Четырехканальная резервированная система | 1990 |

|

SU1746383A1 |

| Многоканальное устройство управления резервированной системой | 1979 |

|

SU866558A2 |

| Резервируемая вычислительная система | 1989 |

|

SU1695317A1 |

| Многоканальный коммутатор | 1988 |

|

SU1541764A1 |

Резервированное устройство относится к вычислительной технике и может быть использовано при построении надежных устройств управления исполнительными элементами. Цель изобретения - повышение надежности за счет отключения отказавшего канала. Контроль канала осуществляется за счет последовательного поразрядного сравнения информационных выходов каждого из каналов. В паузах между управляющими словами проверяется блок 4 ключей подачей сигналов лог. "1" и лог. "0" на его входы. Выходные сигналы блока 4 ключей контролируются элементами 17, 15, 16. Считывание сигналов ошибки и подача управляющих воздействий обеспечиваются блоком 9 управления резервированием. Сигналы ошибки через элемент ИЛИ 19 воздействуют на элемент И-НЕ 20, соединение которых в трех каналах образует трехфазный триггер, подключающий выходы блока 4 ключей одного из исправных каналов к общей магистрали. 1 з.п. ф-лы, 4 ил.

15

Изобретение относится к вычислительной технике и может быть использовано при построении надежных устройств управления исполнительными элементами о.2о

Цель изобретения - повышение надежности устройства за счет отключения неисправных каналов.

На фиг.1 приведена блок-схема устройства; на фиг.2 - схема коммутато- 25 ра; на фиг.З - схема группы элемен- тов; на фиг.4 - схема блока управления.

Устройство содержит три резервируемых канала и в каяадом канале резер- зо вируемый блок 1, коммутатор 2, группу элементов ИЛИ 3, блок 4 ключей, согласующие резисторы 5, выходную магистраль 6, счетчик 7, мультиплексор 8, блок 9 управления резервам, элемент ИЛИ 10, мажоритарный элемент 11, схему 12 сравнения,элемент НЕ 13, элементы И 14-16, элемент И-НЕ 17, элемент ИЛИ 18, элемент ИЛИ 19, элемент И-НЕ 20, входы 21-23 устройст40

40

ва, входы 24-27 каналов, выходы 28 и 29 устройства, таймер 30, выполненный в виде счетчика.

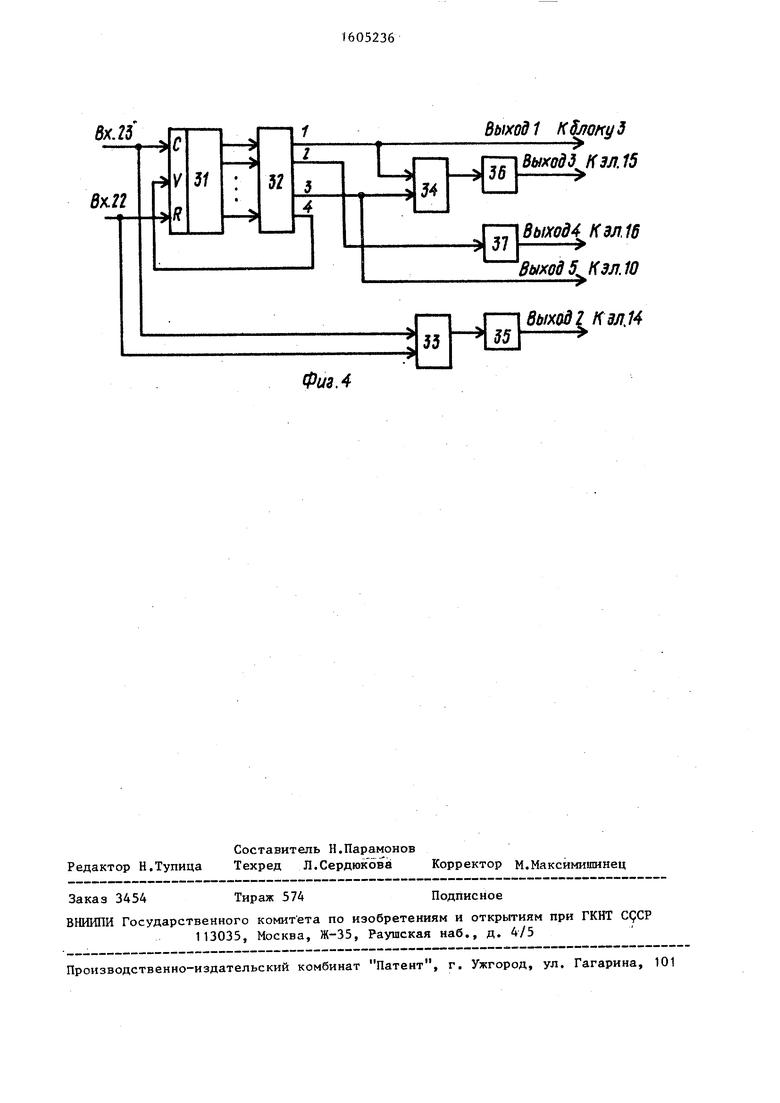

Блок 9 управления резервом (фиг.4) содержит счетчик 31, дешифратор 32, 45 элементы И 33, ИЛИ 34, элементы 35 - 37 задержки.

Резервируемый блок 1 представляет собой регистр, в которьй внешнее устройство записывает параллельный код управляющего слова, причем синхронно в блоки 1 всех каналов. Блок 4 ключей при определенном состоянии управляющего сигнала переходит в состояние Отключено и имеет высокое сопротивление.

Устройство работает следующим образом.

о

5

о

0

5

0

Перед началом работы сигнал начальной установки по входу 21 устройства устанавливает в нулевое положение блоки 1 и счетчики 7 во всех каналах.

В исходном положении отсутствует сигнал на выходе элемента ИЛИ 19 и таймер 30 отрабатывает заданное время, т.е. счетчик заполняется тактовыми импульсами до появления единичного сигнала на его выходе. Еди- ничный сигнал с выхода таймера 30 подается на его управляющий вход, запрещающий дальнейший счет импульсов, и на первый вход элемента И-НЕ 20.

Соединение элементов И-НЕ 20 в трех каналах образует трехфазный триггер, которьш в исходном положении устанавливается произвольно в одно из трех своих состояний, например, первым закрьшается элемент И-НЕ 20 первого канала и на его выходе формируется нулевой сигнал. Этот сигнал действует по входам 26 второго и третьего каналов и удерживает их элементы И-НЕ 20 в открытом состоянии, на выходе которьк формируются eдишiчныe сигналы. Эти сигналы подаются на входы 26 и 27 первого канала и, таким образом, на трех входах элемента И-НЕ 20 первого кана- ла действуют единичные сигналы,удерживающие данное состояние трехфазного триггера.

Единичные сигналы с триггеров элементов И-НЕ 20 во втором и третьем каналах через соответствующие элементы ИЛИ 10 поступают на управляющие входы блоков 4 ключей, и эти блоки переходят в отключенное состояние с высоким сопротивлением,т.е. второй и третий каналы отключены от общей магистрали 6. Нулевой сигнал

с выхода элемента И-НЕ 20 первого канала через элемент ИЛИ 10 поступает на управляющий вход соответствую- блока 4 ключей и переводит его в открытое состояние. Таким образом, к общей магистрали 6 подключаются выходы блока 4 ключей первого канала.

Управляющее слово в виде параллельного кода записывается синхронно в блоки 1, с выходов которых поступает на входы коммутатора 2.

После этого по входу 22 устройства подается сигнал резрешения высокого уровня, который удерживает в нулевом положении счетчик 31, разреша ет счет тактовых импульсов в счетчике 7} открывает коммутатор 2 и через элементы И 33 и задержки 35 опрашивает элемент И 14. С выходов коммутатора 2 код управляющего слова подается на входы блока 4 ключей -и информационные входы мультиплексора 8. Тактовые импульсы по входу 23 заполняют счетчик 7, который с помощью мультиплексора 8 последовательно опрашивает все разряды кода управляющего слова. На управляющий вход блока 4 ключей с выхода элемента ИЛИ 10 подается сигнал нулевого уровня. Это соответствует открытому состоянию ключей блока 4. При этом код управляющего слова через блок 4 поступает на общую выходную магистраль 6.

При последовательном опросе всех разрядов управляющего слова на выходе мультиплексора 8 формируются соответствующие сигналы, которые, подаются на вход мажоритарного элемента 11. При исправной работе всех каналов , значение контролируемых в данном такте разрядов управляющего слова совпадает и схема 12 сравнения формирует сигнал, который через элемент НЕ 13 закрывает элемент И 14, и сигнал ошибки не формируется. В случае неисправности какого-либо из элементов в первом канале сигнал на выходе мультиплексора 8 не совпадает с сигналом на выходе мажоритарного элемента 11, схема 12 сравнения не формирует сигнал совпадения и элемент И 14 подготавливается к открыванию. Тактовый импульс с выхода элемента 35 задержки открьшает элемент И 14 и через элемент ИЛИ 19 обнуляет таймер 30 При этом подается нулевой сигнал с вькода таймера 30 на первый вход элемента И-НЕ 20, который открьшается

5

0

5

0

5

0

5

0

5

и формирует на своем выходе единич- нът сигнал. При этом ключи в блоке 4 первого канала переходят в закрытое состояние и отключают неисправный ка- нал от магистрали 6. Трехфазный триггер переходит в новое положение, например нулевой сигнал формируется раньше на выходе элемента И-НЕ 20 второго канала. Соответственно к магистрали 6 подключаются выходы блока 4 ключей второго канала и т.д.

В паузах между посылками кодов управляющих слов производится контроль состояния блоков 4 ключей во всех каналах. Этот контроль осуществляется следуюищм образом. Для контроля ключей блока 4 по входу 22 подается управляющий сигнал низкого уровня. Этот сигнал закрывает элементы И коммутатора 2, элемент И 33 и разрешает счетчику 31 счет тактовых импульсов по входу 23. Счетчик 31 соединенный с дешифратором 32, образует распределитель, который формирует распределенные во времени три импульсных сигнала .

Импульс с первого выхода дешифратора 32 через элементы ИЛИ 3 в виде единичных сигналов организует проверку по единицам и передается на входы всех ключей блока 4, через элементы ИЛИ 34 и задержки 36 опрашивает элемент И 15. При исправной работе ключей блока 4 на всех его выходах формируются единичные сигналы, которые закрывают элемент И-НЕ 17 и, соответственно, элемент И 15, т.е. сигнал ошибки не формируется. Если какой-либо из ключей неисправен и формирует на выходе сигнал нулевого уровня, то элемент И-НЕ 17 открывает элемент И 15 и через элемент ИЛИ 19 обнуляет таймер 30, нулевой сигнал с его выхода подается на вход элемента И-НЕ 20. При этом трехфазный триггер меняет свое положение и ;неисправный канал отключается от ма- 1гистрали 6 описанным выше образом.

Импульс с второго выхода дешифратора 32 организует проверку по нулям, так как после сброса импульса с первого выхода дешифратора 32 на входы блока 4 ключей с выходов элемента ИЛИ 3 подаются нулевые сигналы. На всех выходах 1шючей блока 4 при их исправной работе также формируются нулевые сигналы, при этом элемент

ИЛИ 18 и, соответственно, элемент И 16 остаются закрытыми и сигнал ошибки не формируется. Если какой-либо из ключей неисправен и формирует j на выходе единичньй сигнал, то открываются элементы ИЛИ 18, И 16 и импульс с выхода элемента 37 задержки через элемент ИЛИ 19 обнуляет таймер 30 и аналогично описанному вьппе 10 изменяет состояние элемента И-НЕ 20, неисправный канал отключается.

Сигнал с третьего выхода дешифратора 32 организует проверку отключенного состояния ключей и через эле- 15 мент ИЛИ 10 переводит блок 4 ключей в отключенное состояние. В этом состоянии на выходах всех ключей блока 4 формируется потенциал источника питания , снимаемый через согласующие ре- 20 зисторы 5, например единичные потен- .циальные сигналы. В случае, если все ключи исправны и отключены, то на входе элемента И-НЕ 17 сигнал ошибмногократно проверки ключей блока 4 и опрос разрядов управляющего сл ва с помощью счетчика 7 и мультиплексора 8.

Во время проверки ключей блока внешние исполнительные элементы из за большого времени срабатьюания и отпускания не изменяют своего со стояния при смене сигналов на выхо дах ключей.

Формула изобретени

ки не формируется. В случае, если ка- входом первого ключа И, о т л и ч

кой-либо ключ неисправен и не отключен, на его выходе формируется нулевой сигнал. При этом на входе элемента И-НЕ 17 формируется единичньй сигнал, а импульс с третьего выхода дешифратора 32 через элементы ИЛИ 34, задержки 36 и И 15 считьшает сигнал ошибки.

Сигнал с четвертого выхода дешифратора 32 подается на управляющий вход счетчика 31, запрещает счет тактовых импульсов, и процесс контроля блока 4 ключей прекращается. Ло- дачей управляющего сигнала высокого , уровня по входу 22 устройство снова переходит в режим приема следующего управляющего слова в блок 1. В случае, если сигнал ошибки случайный, то после обнуления таймер 30 отрабатывает заданное задержки и подает единичный сигнал на элемент И-НЕ 20, т.е. обеспечивает возможность последующего подключения даню щ е е с я тем, что, с целью повышения надежности устройства за счет отключения неисправных каналов, в каждый канал введены коммутатор,груп

30 па элементов ИЛИ, мультиплексор, блок ключей, блок управления резервом, первьш и второй элементы И-НЕ, причем входы установки, управляющий и тактовый устройства являются одно,с именными входами каждого из каналов, информационные выходы которых являются одноименным выходом устройства, выходы сравнения и выбора канала Каж дого из каналов соединены с соответ40 ствующими одноименными входами соседних каналов и в каждом канале информационные входы канала соединень с информационными входами резервируемого блока,выходы которого соедине45 ны с информационными входами коммутатора, выходы которого соединены с первыми входами элемента ИЛИ группы, выходы которых соединены с информа- ционньми входами блока ключей и муль

ного канала к магистрали 6. Если сиг- 50 типлексора, выходы блока ключей сонал ошибки за время задержки сраба- тьшания таймера 3.. повторяется, то таймер 30 периодически устанавливается в нулевое положение и неисправность данного канала подтверждается нулевым сигналом на входе элемента И-НЕ 20. Время задержки срабатыва- кия таймера выбирается таким образом, чтобы за это время вьшолнялись

55

единены с информационным-выходом канала входами первого элемента ИЛИ и первого элемента И-НЕ, вход установки канала соединен с одноименным входом резервируемого блока и входом сброса счетчика, управляющий вход ка нала соединен с одноименными входами коммутатора, блока управления резервом и счетчика, тактовьй вход канала

многократно проверки ключей блока 4 и опрос разрядов управляющего слова с помощью счетчика 7 и мультиплексора 8.

Во время проверки ключей блока 4 внешние исполнительные элементы из- за большого времени срабатьюания и отпускания не изменяют своего состояния при смене сигналов на выходах ключей.

Формула изобретения

входом первого ключа И, о т л и ч

а ю щ е е с я тем, что, с целью повышения надежности устройства за счет отключения неисправных каналов, в каждый канал введены коммутатор,группа элементов ИЛИ, мультиплексор, блок ключей, блок управления резервом, первьш и второй элементы И-НЕ, причем входы установки, управляющий и тактовый устройства являются одноименными входами каждого из каналов, информационные выходы которых являются одноименным выходом устройства, выходы сравнения и выбора канала Каждого из каналов соединены с соответствующими одноименными входами соседних каналов и в каждом канале информационные входы канала соединень с информационными входами резервируемого блока,выходы которого соединены с информационными входами коммутатора, выходы которого соединены с первыми входами элемента ИЛИ группы, выходы которых соединены с информа- ционньми входами блока ключей и мультиплексора, выходы блока ключей со

единены с информационным-выходом канала входами первого элемента ИЛИ и первого элемента И-НЕ, вход установки канала соединен с одноименным входом резервируемого блока и входом сброса счетчика, управляющий вход канала соединен с одноименными входами коммутатора, блока управления резервом и счетчика, тактовьй вход канала

соединен с тактовым входом блока управления резервом и тактовыми входа- .ми- таймера и счетчика, разрядные выходы которого соединены с адресными входами мультиплексора, выход которого соединен с выходом сравнения канала, вторым входом блока сравнения и первым входом мажоритарного элемента, второй и третий входы которого соединены соответственно с первым и вторым входами сравнения канала, первый выход блока управления резервом соединен с вторыми входами элементов ШШ группы, второй выход - с вторым входом первого элемента И,третий вход - с первым входом второго элемента И, второй вход которого соединен с выходом первого элемента

1605236

первым и вторым входами выбора канала, а выход соединен с выходом выбора канала и первым входом третьего эле мента ИЛИ, второй вход которого соединен с пятым выходом блока управления резервом, а выход - с управляющим входом блока ключей.

., .-..х, ,u,v,iiii4ij ja. 1 wpa l liCJJJJOlM

И-НЬ, четвертый выход блока управления Л) выходом блока и первым входом элемен ОвЧ Т ИПМ Г OOnfJ-UuTT л 1-t -. н.- ттттгтт.

резервом соединен с первым входом третьего элемента И, второй вкод которого соединен с выходом первого элемента ИЛИ, выходы первого, второго и третьего элементов И соединены с соответствующими входами второго элемента ИЛИ, выход которого соединен с входом установки таймера, вькод которого соединен со своим управляющим входом и первым входом второго элемента И-НЕ, второй и третий входы которого соединены соответственно с

та ИЛИ, второй выход дешифратора через первый элемент задержки соединен с четвертью выходом блока, третий выход дешифратора соединен с пя25 тым выходом блока и вторым входом элемента ИЛИ, выход которого через второй элемент задержки соединен с третьим выходом блока, выход элемента И через третий элемент задержки

30 соединен с вторым выходом блока, а выход счетчика соединен с информационным входом дешифратора.

1605236

10

первым и вторым входами выбора канала, а выход соединен с выходом выбора канала и первым входом третьего элемента ИЛИ, второй вход которого соединен с пятым выходом блока управления резервом, а выход - с управляющим входом блока ключей.

-..х, ,u,v,iiii4ij ja. 1 wpa l liCJJJJOlM

выходом блока и первым входом элемен Л) выходом блока и первым входом элемен- ттттгтт.

та ИЛИ, второй выход дешифратора через первый элемент задержки соединен с четвертью выходом блока, третий выход дешифратора соединен с пя25 тым выходом блока и вторым входом элемента ИЛИ, выход которого через второй элемент задержки соединен с третьим выходом блока, выход элемента И через третий элемент задержки

30 соединен с вторым выходом блока, а выход счетчика соединен с информационным входом дешифратора.

Фив А

Редактор Н.Тупица

Составитель Н.Парамонов

Техред Л.СердюковаКорректор М.Максимишинец

Заказ 3454

Тираж 574

ВНИИПИ Государственного комит ета по изобретениям и открытиям при ГКНТ ClyCP 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Подписное

| Адаптивное резервированное устройство | 1981 |

|

SU962959A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Адаптивное резервированное устройство | 1983 |

|

SU1174929A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-11-07—Публикация

1989-01-12—Подача