ел

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ определения собственных частот колебаний лобовых частей обмотки статора электрической машины | 1990 |

|

SU1786601A1 |

| Приемник частотно-манипулированных сигналов | 1985 |

|

SU1312753A1 |

| СПОСОБ И УСТРОЙСТВО АВТОМАТИЧЕСКОЙ РЕГУЛИРОВКИ УСИЛЕНИЯ И ИСКЛЮЧЕНИЯ СМЕЩЕНИЯ ПОСТОЯННОЙ СОСТАВЛЯЮЩЕЙ В ПРИЕМНИКЕ С КВАДРАТУРНОЙ ДЕМОДУЛЯЦИЕЙ | 1995 |

|

RU2241304C2 |

| СПОСОБ И УСТРОЙСТВО АВТОМАТИЧЕСКОЙ РЕГУЛИРОВКИ УСИЛЕНИЯ И ИСКЛЮЧЕНИЯ СМЕЩЕНИЯ ПОСТОЯННОЙ СОСТАВЛЯЮЩЕЙ В ПРИЕМНИКЕ С КВАДРАТУРНОЙ ДЕМОДУЛЯЦИЕЙ | 1995 |

|

RU2156538C2 |

| ИНФРАКРАСНЫЙ ТРЕХСПЕКТРАЛЬНЫЙ ИЗВЕЩАТЕЛЬ ПЛАМЕНИ | 2011 |

|

RU2443023C1 |

| ЛИНИЯ РАДИОСВЯЗИ | 2000 |

|

RU2173025C1 |

| РАДИОДАЛЬНОМЕР | 2000 |

|

RU2197000C2 |

| ФАЗОВЫЙ ПЕЛЕНГАТОР | 2011 |

|

RU2458355C1 |

| РАДИОПРИЕМНИК ПРЯМОГО ПРЕОБРАЗОВАНИЯ | 1995 |

|

RU2175463C2 |

| РАДИОДАЛЬНОМЕР | 2000 |

|

RU2197001C2 |

Использование: прием частотно-мани- пулированных сигналов в системах передачи дискретной информации. Сущность изобретения: приемник содержит смесители 1 и 2, высокочастотный генератор 3, фазовра- щатель 4, фильтры 5 и 6 нижних частот, ограничители 7 и 8. решающий блок 9, дешифратор 10, 1 анализатор 11 наличия сигнала. Повышение помехоустойчивости достигается путем защиты от ошибок первого рода за счет запрета расшифровки команд выходного сигнала при отсутствии сигнала манипулированной по частоте информационным потоком несущей на входе, Приемник может отличаться выполнением анализатора 11 наличия сигнала. 1 з.п. ф-лы, 3 ил,

XI 00 Ох О 00 О

Изобретение относится к связи и может быть использовано в системах передачи дискретной информации для приема частотно- манипулированных (ЧМн) сигналов, например, в вызывных системах.

Известен приемник ЧМн сигналов, содержащий высокочастотный (ВЧ) смеситель, ВЧ управляемый генератор, управляющий низкочастотный (НЧ) генератор, линию задержки, первый фильтр нижних частот (ФНЧ), блок преобразования частоты, фазовый дискриминатор, второй ФНЧ и ограничитель.

В известном приемнике при наличии нестабильности частоты ВЧ генератора для обеспечения работоспособности приемника ЧМн сигналов необходимо расширять полосу пропускания первого ФНЧ, что приведет к снижению соотношения сигнал/шум на входе фазового дискриминатора, а следовательно, к снижению помехоустойчивости известного приемника ЧМн сигналов.

Наиболее близким по технической сути к заявляемому является приемник ЧМн сигналов, содержащий два смесителя, фазов- ращатель, ВЧ-генератор. два фильтра, два ограничителя, решающий блок и дешифратор. Первые входы смесителей соединены между собой и выполнены входом приемника, выход ВЧ-генератора соединен с вторыми входами смесителей, причем с одним из них непосредственно, а с другим - через фазовращатель, выход каждого смесителя соединен со входом соответствующего ФНЧ, выходы которых соединены со входами соответствующих ограничителей, входы решающего блока соединены с выходами ограничителей, выход решающего блока соединен со входом дешифратора, выход которого выполнен выходом приемника.

Недостатком известного приемника ЧМн сигналов является низкая помехоустойчивость, обусловпенная отсутствием защиты приемника от ошибок первого рода (ложная тревога), когда принимается ошибочное решение сигнал есть, возникающее вследствие того. что шум принимается за сигнал.

Целью изобретения является повышение помехоустойчивости известного приемника ЧМн сигналов пугем вчедения защиты от ошибок первого рода за счет запрета расшифровки дешифратором выходного сигнала решающего блока при отсутствии сигнала манипулированной по частоте информационным потоком несущей на входе приемника.

Поставленная цель достигается тем, что в приемник частотно-манипулированных

сигналов, содержащий первый смеситель, первый вход которого является входом приемника и соединен с первым входом второго смесителя, к второму входу которого

подключен выход фазовращателя, вход которого соединен с выходом высокочастотного генератора и с вторым входом первого смесителя, выход которого и выход второго смесителя подключены соответственно к

0 входам первого и второго фильтров нижних частот, выходы которых соединены соответственно с входами первого и второго ограничителей, выходы которых подключены к входам решающего блока, первый выход ко5 торого соединен с первым входом дешифратора, введен анализатор наличия сигнала, первый, второй и третий входы и выход которого соединены соответственно с выходами первого и второго ограничителей, со

0 вторым выходом решающего блока и со вторым входом дешифратора, выход которого является выходом приемника.

Кроме того, анализатор наличия сигнала содержит последовательно соединенные

0 компаратора фаз являются соответственно первым и вторым входами анализатора, третьим входом и выходом которого являются соответственно первый вход блока управления знаком и выход ключевого блока.

5Конструктивное выполнение приемника ЧМн сигналов по изобретению с введением анализатора наличия сигнала позволило повысить помехоустойчивость приемника, т.к. расшифровка видеосигнала решающего

0 блока дешифратором и формирование выходного сигнала приемника производятся только при наличии манипулированной по частоте информационным потоком несущей на его входе. Тогда независимо от структуры

5 модулирующего цифрового потока сигналы на входах компаратора фаз в анализаторе наличия сигнала в основном имеют постоянный фазовый сдвиг 90°, который изменяется на короткое время, не превышающее

0 периода частоты девиации, в момент смены знака информационной посылки на противоположный. При этом выходной сигнал компаратора фаз, отфильтрованный фильтром нижних частот, превышает порог срав5 нения схемы сравнивания и удерживает ключевую схему в открытом состоянии, пропуская через нее видеосигнал решающего блока на вход дешифратора. В случае отсутствия сигнала несущей и наличия на входе приемника только шумового сигнала выходной сигнал решающего блока не проходит в дешифратор, поскольку при этом сдвиг фаз сигналов на входах компаратора фаз меняется случайным образом. Тогда выходной сигнал компаратора фаз, отфильтрованный фильтром нижних частот, ниже порога сравнения и схема сравнения удерживают ключевую схему в закрытом состоянии, не пропуская через нее видеосигнал решающего блока на вход дешифратора. Таким образом обеспечивается защита от ошибок первого рода (ложная тревога), поскольку набираемые решающим блоком из шумового сигнала ложные команды (ложные тревоги) не поступают в дешифратор команд.

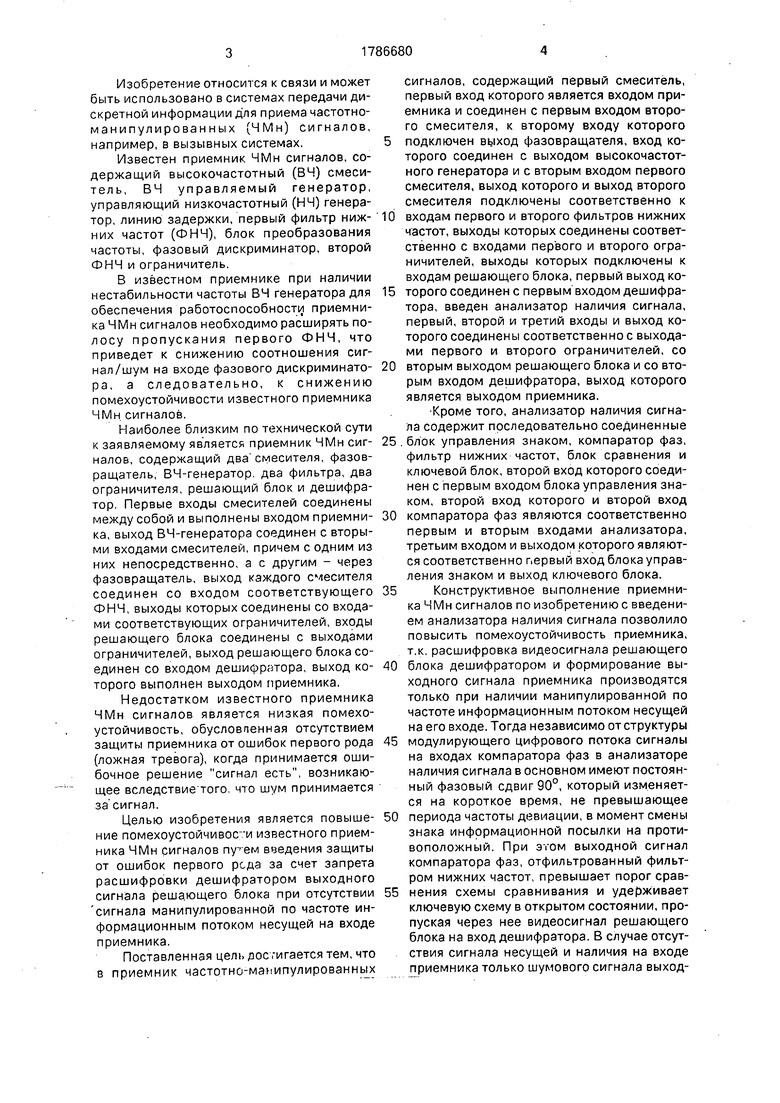

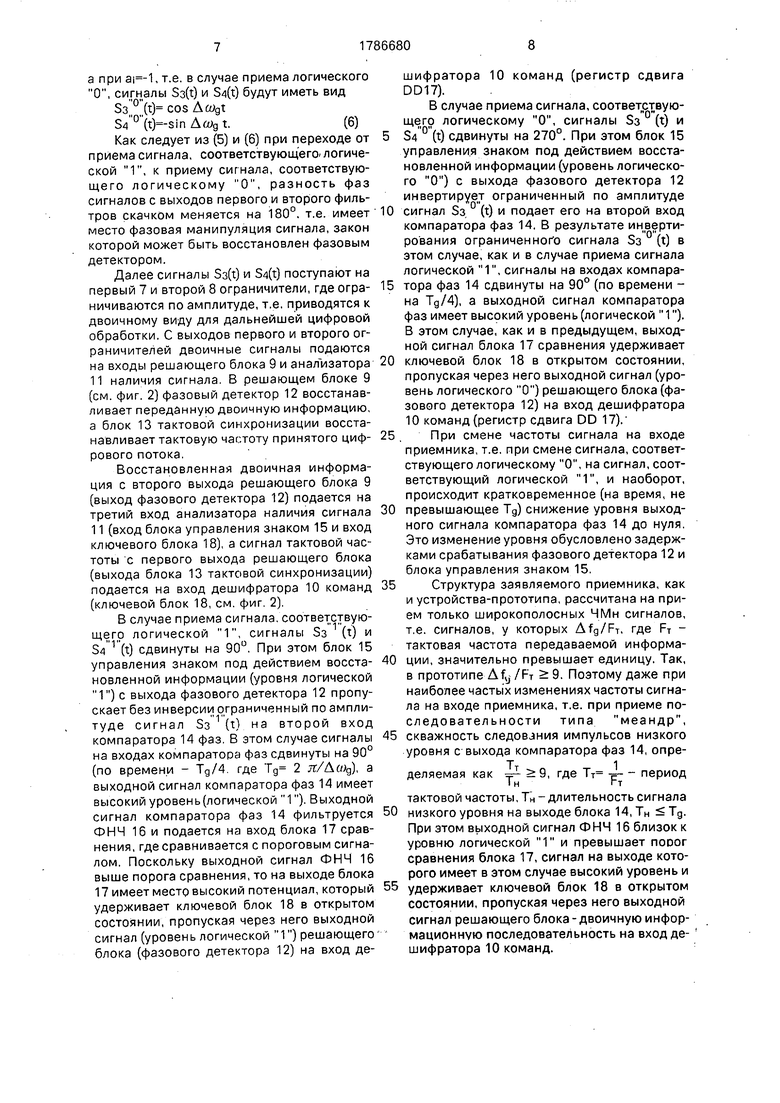

На фиг. 1 дана структурная функциональная схема заявляемого приемника ЧМн сигналов; на фиг. 2 - структурная функциональная схема анализатора наличия сигнала в составе приемника; на фиг. 3временные диаграммы, поясняющие работу приемника в конкретном варианте конструктивного выполнения.

Приемник ЧМн сигналов содержит первый 1 и второй 2 смесители, ВЧ генератор 3, фазовращатель 4, первый 5 и второй 6 фильтры нижних частот(ФНЧ), первый 7 и второй 8 ограничители, решающий блок 9, дешифратор 10 и анализатор 11 наличия сигнала (см. фиг. 1). Первый вход первого смесителя

I является входом приемника и соединен с первым входом второго смесителя 2, к второму входу которого подключен выход фа- зовращателя 4, вход которого соединен с выходом ВЧ генератора 3 и с вторым входом первого смесителя 1, ныход которого и выход второго смесителя 2 подключены соответственно к входам первого 5 и второго 6 фильтров нижних частот, выходы которых соединены соответственно с входами пер- вого 7 и второго 8 ограничителей, выходы которых подключены к входам решающего блока 9, первый выход которого соединен с первым входом дешифратора 10, а первый, второй и третий входы и выход анализатора

II наличия сигнала соединены соответственно с выходами первого 7 и второго 8 ограничителей, с вторым выходом решающего блока 9 и вторым входом дешифратора 10, выход которого является выходом при- емника.

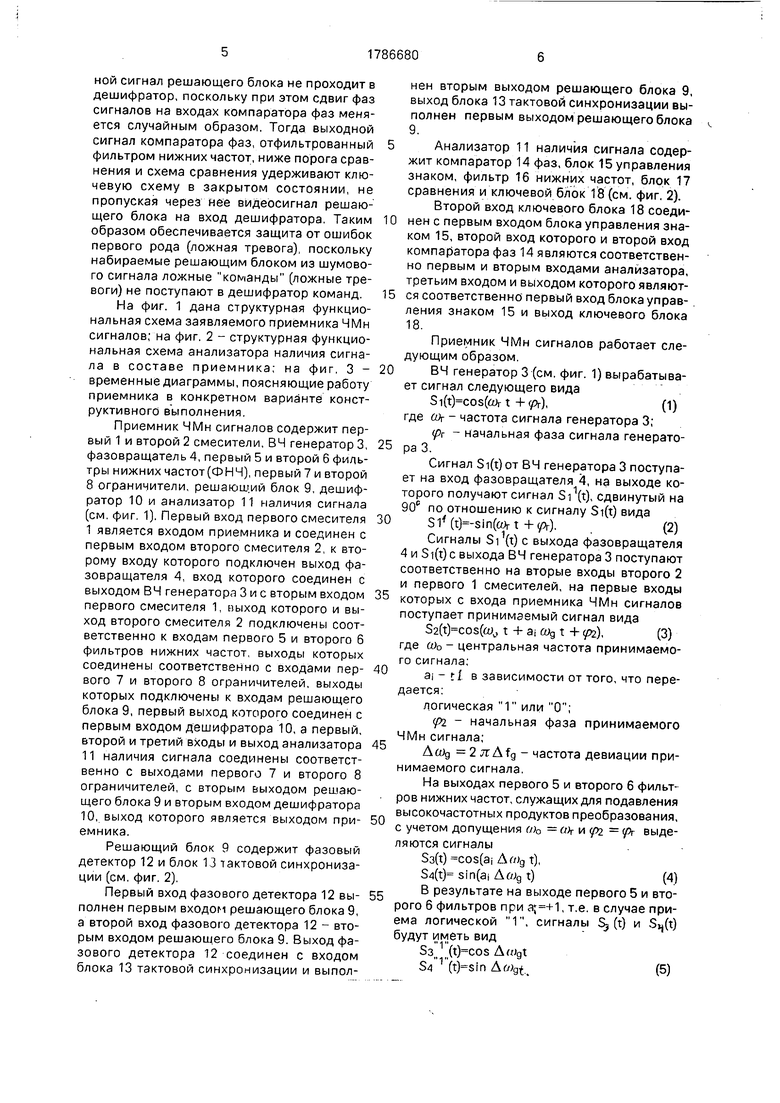

Решающий блок 9 содержит фазовый детектор 12 и блок 13 тактовой синхронизации (см. фиг. 2).

Первый вход фазового детектора 12 вы- полнен первым входом решающего блока 9, а второй вход фазового детектора 12 - вторым входом решающего блока 9. Выход фазового детектора 12 соединен с входом блока 13 тактовой синхронизации и выполнен вторым выходом решающего блока 9, выход блока 13 тактовой синхронизации выполнен первым выходом решающего блока 9.

Анализатор 11 наличия сигнала содержит компаратор 14 фаз, блок 15 управления знаком, фильтр 16 нижних частот, блок 17 сравнения и ключевой блок 18 (см. фиг. 2).

Второй вход ключевого блока 18 соединен с первым входом блока управления знаком 15, второй вход которого и второй вход компаратора фаз 14 являются соответственно первым и вторым входами анализатора, третьим входом и выходом которого являются соответственно первый вход блока управления знаком 15 и выход ключевого блока 18.

Приемник ЧМн сигналов работает следующим образом.

ВЧ генератор 3 (см. фиг. 1) вырабатывает сигнал следующего вида

Si(t)COs((Wrt + рг),(1)

где Ok - частота сигнала генератора 3;

(рг - начальная фаза сигнала генератора 3.

Сигнал Si(t)oT ВЧ генератора 3 поступает на вход фазовращателя 4, на выходе которого получают сигнал Si1(t), сдвинутый на 90е по отношению к сигналу Si(t) вида

Sl (t)-sin(«rt +(рг). .(2)

Сигналы Si1(t) с выхода фазовращателя 4 и Si(t) с выхода ВЧ генератора 3 поступают соответственно на вторые входы второго 2 и первого 1 смесителей, на первые входы которых с входа приемника ЧМн сигналов поступает принимаемый сигнал вида

S2(t)cos(wv, t H- ai t + p2},(3) где со0 - центральная частота принимаемого сигнала;

а - ti в зависимости от того, что передается:

логическая 1 или

рг - начальная фаза принимаемого ЧМн сигнала;

Асод 2 ;rAfg - частота девиации принимаемого сигнала.

На выходах первого 5 и второго 6 фильтров нижних частот, служащих для подавления высокочастотных продуктов преобразования, с учетом допущения (ik и pi выделяются сигналы

S3(t)cos(aj Awgt),

$4(t) sin(ai Aftjg t)(4)

В результате на выходе первого 5 и второго 6 фильтров при , т.е. в случае приема логической 1, сигналы Sj (t) и (t) будут иметь вид

S3,,1(t)cos Awgt

84 1 (t)sin Awgt..(5)

а при , т.е. в случае приема логического О, сигналы Зз(г) и S4(t) будут иметь вид S3, °it(t) cos

SV° (t)-Sin Atogt.(6)

Как следует из (5) и (6) при переходе от приема сигнала, соответствующего/ логической 1, к приему сигнала, соответствующего логическому О, разность фаз сигналов с выходов первого и второго фильтров скачком меняется на 180°. т.е. имеет место фазовая манипуляция сигнала, закон которой может быть восстановлен фазовым детектором.

Далее сигналы Ss(t) и S4(t) поступают на первый 7 и второй 8 ограничители, где ограничиваются по амплитуде, т.е. приводятся к двоичному виду для дальнейшей цифровой обработки. С выходов первого и второго ограничителей двоичные сигналы подаются на входы решающего блока 9 и анализатора 11 наличия сигнала. В решающем блоке 9 (см. фиг. 2) фазовый детектор 12 восстанавливает переданную двоичную информацию, а блок 13 тактовой синхронизации восстанавливает тактовую частоту принятого цифрового потока.

Восстановленная двоичная информация с второго выхода решающего блока 9 (выход фазового детектора 12) подается на третий вход анализатора наличия сигнала 11 (вход блока управления знаком 15 и вход ключевого блока 18), а сигнал тактовой частоты с первого выхода решающего блока (выхода блока 13 тактовой синхронизации) подается на вход дешифратора 10 команд (ключевой блок 18, см. фиг. 2).

В случае приема сигнала, соответствующего логической 1, сигналы Зз (t) и $4 1 (t) сдвинуты на 90°. При этом блок 15 управления знаком под действием восстановленной информации (уровня логической 1) с выхода фазового детектора 12 пропускает без инверсии ограниченный по амплитуде сигнал Зз 1 (t) на второй вход компаратора 14 фаз. В этом случае сигналы на входах компаратора фаз сдвинуты на 90° (по времени - Тд/4. где Тд 2 я/Awg), а выходной сигнал компаратора фаз 14 имеет высокий уровень (логической 1). Выходной сигнал компаратора фаз 14 фильтруется ФНЧ 16 и подается на вход блока 17 сравнения, где сравнивается с пороговым сигналом. Поскольку выходной сигнал ФНЧ 16 выше порога сравнения, то на выходе блока 17 имеет место высокий потенциал, который удерживает ключевой блок 18 в открытом состоянии, пропуская через него выходной сигнал (уровень логической 1) решающего блока (фазового детектора 12) на вход дешифратора 10 команд (регистр сдвига DD17).

В случае приема сигнала, соответствующего логическому О, сигналы 5з ° (t) и

SA ° (t) сдвинуты на 270°. При этом блок 15 управления знаком под действием восстановленной информации (уровень логического О) с выхода фазового детектора 12 инвертирует ограниченный по амплитуде

сигнал Зз (t) и подает его на второй вход компаратора фаз 14, В результате инвертирования ограниченного сигнала Зз ° (t) в этом случае, как и в случае приема сигнала логической 1, сигналы на входах компаратора фаз 14 сдвинуты на 90° (по времени - на Тд/4), а выходной сигнал компаратора фаз имеет высокий уровень (логической 1). В этом случае, как и в предыдущем, выходной сигнал блока 17 сравнения удерживает

ключевой блок 18 в открытом состоянии, пропуская через него выходной сигнал (уровень логического О) решающего блока (фазового детектора 12) на вход дешифратора 10 команд (регистр сдвига DD 17)/

. При смене частоты сигнала на входе приемника, т.е. при смене сигнала, соответствующего логическому О, на сигнал, соответствующий логической 1, и наоборот, происходит кратковременное (на время, не

превышающее Тд) снижение уровня выходного сигнала компаратора фаз 14 до нуля. Это изменение уровня обусловлено задержками срабатывания фазового детектора 12 и блока управления знаком 15.

Структура заявляемого приемника, как и устройства-прототипа, рассчитана на прием только широкополосных ЧМн сигналов, т.е. сигналов, у которых Afg/FT, где FT - тактовая частота передаваемой информации, значительно превышает единицу. Так, в прототипе Afy/FT 9. Поэтому даже при наиболее частых изменениях частоты сигнала на входе приемника, т.е. при приеме последовательности типа меандр,

скважность следования импульсов низкого уровня с выхода компаратора фаз 14, определяемая как i 9, где Тт -g- - период I нгт

тактовой частоты, Тн -длительность сигнала низкого уровня на выходе блока 14, Тн Тд. При этом выходной сигнал ФНЧ 16 близок к уровню логической 1 и превышает ПОРОГ сравнения блока 17, сигнал на выходе которого имеет в этом случае высокий уровень и удерживает ключевой блок 18 в открытом состоянии, пропуская через него выходной сигнал решающего блока - двоичную информационную последовательность на вход дешифратора 10 команд.

В случае приема дискретной информации частота принимаемого сигнала изменяется псевдослучайным образом. Тогда импульсы низкого уровня на выходе компаратора фаз 14 появляются еще реже, чем в случае приема сигнала, модулированного по частоте меандром, При этом и выходной сигнал фильтра 16 превышает как уровень, формирующийся в случае приема сигнала типа меандр, так и порог блока 17 сравнения, выходной сигнал которого удерживает блок 18 в открытом состоянии, пропуская через него информационную последовательность на вход дешифратора 10,

Дешифратор 10 команд преобразует принятую двоичную последовательность из последовательного кода в параллельный, осуществляет контроль по четности кода и выдает получателю информации сигнал ошибки по четности, сигнал кодовая последовательность принята и 15-битовый код соответственно с первого, второго и кодового выходов дешифратора 10 команд.

Уровень логической 1 поступающий с выхода анализатора 11 наличия сигнала на информационный вход дешифратора 10 команд, соответствует режиму ожидания дешифратора 10, т.к. в основу работы последнего положен старт-стоповый принцип работы. Дешифратор 10 команд рассчитан на обработку 17-битовых кадров, причем кадр включает:

1) стартовый бит (уровень логического О);

2) 15-битовую кодовую последовательность (14 информационных бит и бит контроля по четности);

3) столовый бит (уровень логической 1).

Согласно изобретению был изготовлен макет заявляемого приемника, на котором проводились сравнительные испытания. Сравнение проводилось с макетом приемника ЧМн сигналов, выбранного в качестве прототипа заявляемого устройства. В макетах сравниваемых приемников первый и второй смесители, фазовращатели, ВЧ-ге- нераторы, первый и второй ФЧН, первый и второй ограничители, решающие блоки и дешифраторы имели идентичные электрические параметры.

Анализатор 11 наличия сигнала в конкретном конструктивном исполнении содержит:

DD1 -- инвертор;

DD2 - сумматор по модулю

DD3 - триггер;

DD4 - схема 2И-НЕ,

DA1 - компаратор.

В анализаторе 11 наличия сигнала на триггере DD3 выполнен компаратор фаз, на элементах DD1, DD2 -блокуправления знаком; на элементах 1С1 - фильтр нижних частот; на элементах DA1, R2, R3 - блок сравнения; на элементе DD4 - ключевой блок.

Решающий блок 9 в конкретном конструктивном исполнении содержит: 0DD5, DD7, DD8, DD11...DD14 - триггеры:

DD6, DD10, DD15 - схемы 2И-НЕ;

DD9 - сумматор по модулю два;

VQ - кварцевый генератор, 5 В решающем блоке 9 на триггере DD5 выполнен фазовый детектор, который по разности фаз сигналов на D- и С-входах определяет значение частоты на входеi Приёмника и формирует цифровой поток 0 (последовательность логических О и 1) переданной информации. Остальные элементы блока 9 реализуют систему тактовой синхронизации, работающей по старт-стопному принципу.

5 Дешифратор 10 команд в конкретном конструктивном исполнении содержит:

DD16 - схема 2И-НЕ ;

DD17 - регистр сдвига;

DD18-схема 0DD19 - двоичный счетчик;

DD20 - сумматор по модулю два;

DD21-схема 4И.

В дешифраторе 10 на схеме 2И-НЕ DD16 выполнен обнаружитель стартового 5 бита 17-битового кадра, на схеме 2И DD18 - ключевой блок, на регистре сдвига DD17 - 15-разрядный преобразователь последовательного кода в параллельный, на элементах DD19, DD21 - счетчик по модулю 16, 0 на элементах С4, R6 - цепь предустанов- ки двоичного счетчика DD19 в состояние 15, на сумматоре по модулю два DD20 - блок контроля на четность, 15-битового кода.

5Ошибка первого рода в устройстве-прототипе возникает в среднем каждую минуту. В заявленном устройстве при введении анализатора наличия сигнала за время измерения т. ч ошибки первого рода не 0 возникали.

Таким образом, в заявляемом приемнике ЧМн сигналов повышение помехоустойчивости обеспечивается путем защиты от ошибок первого рода за счет запрета рас- 5 шифровки дешифратором команд выходного сигнала решаюшего блока при отсутствии сигнала манипулированной по частоте информационным потоком несущей на входе приемника, который реализуется введенным анализатором наличия сигнала.

Формула изобретения

анализатор наличия сигнала,первый,второй и третий входы и выход которого соединены соответственно с выходами первого и второго ограничителей, с вторым выходом решающего блока и с вторым входом дешифратора, выход которого является выходом приемника.

| Кевин Смит Высокочувствительный однокристальный приемник персонального вызова | |||

| Электроника, 1932, № 10, с | |||

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

Авторы

Даты

1993-01-07—Публикация

1990-04-02—Подача