Изобретение относится к специализированным средствам информационно-измерительной техники и предназначено для исследования частотных свойств случайных процессов.

Цель изобретения - повышение точности анализатора.

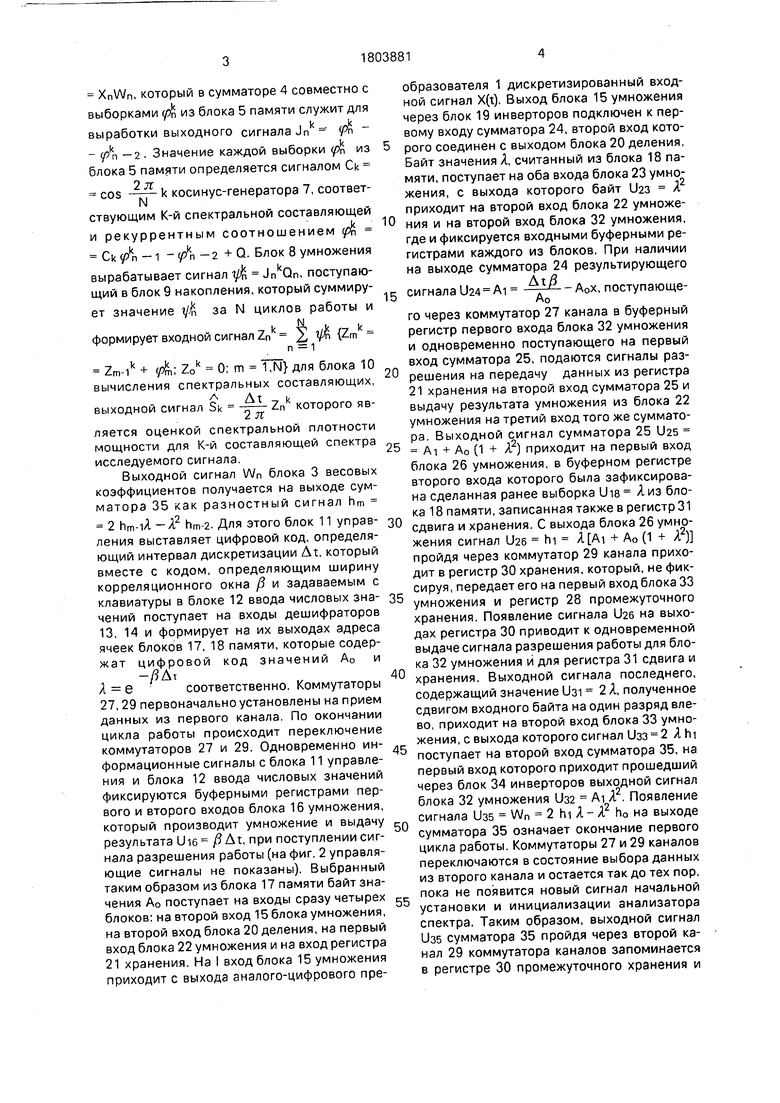

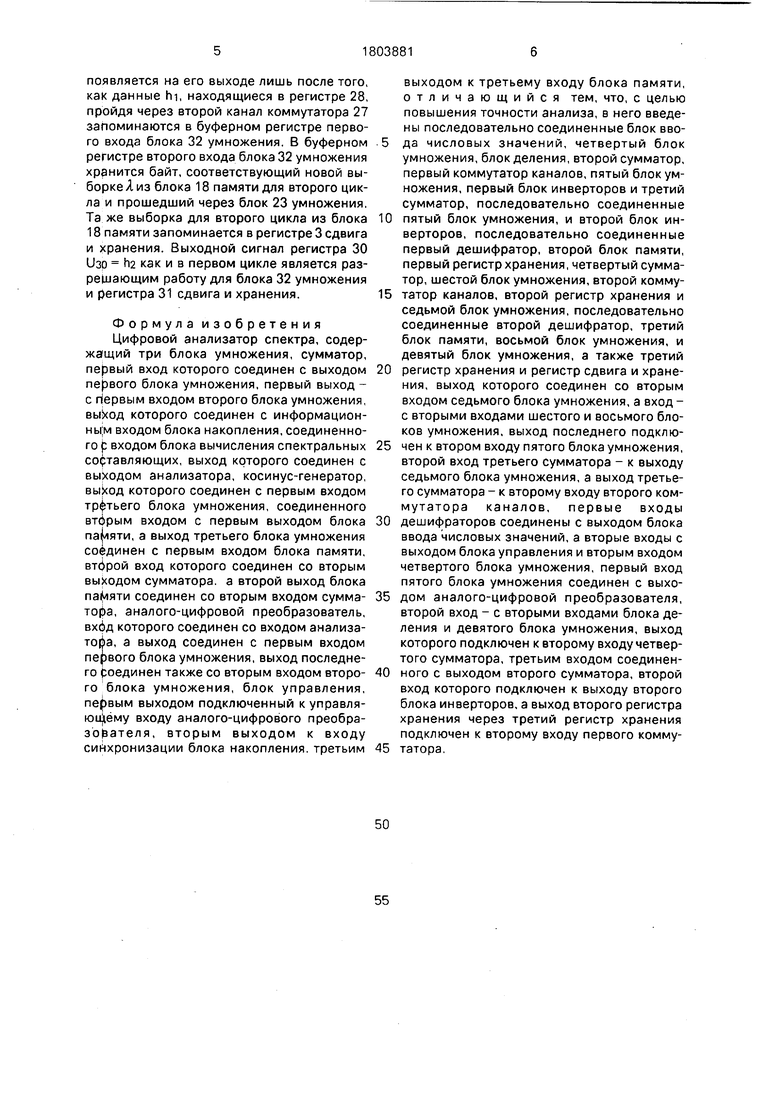

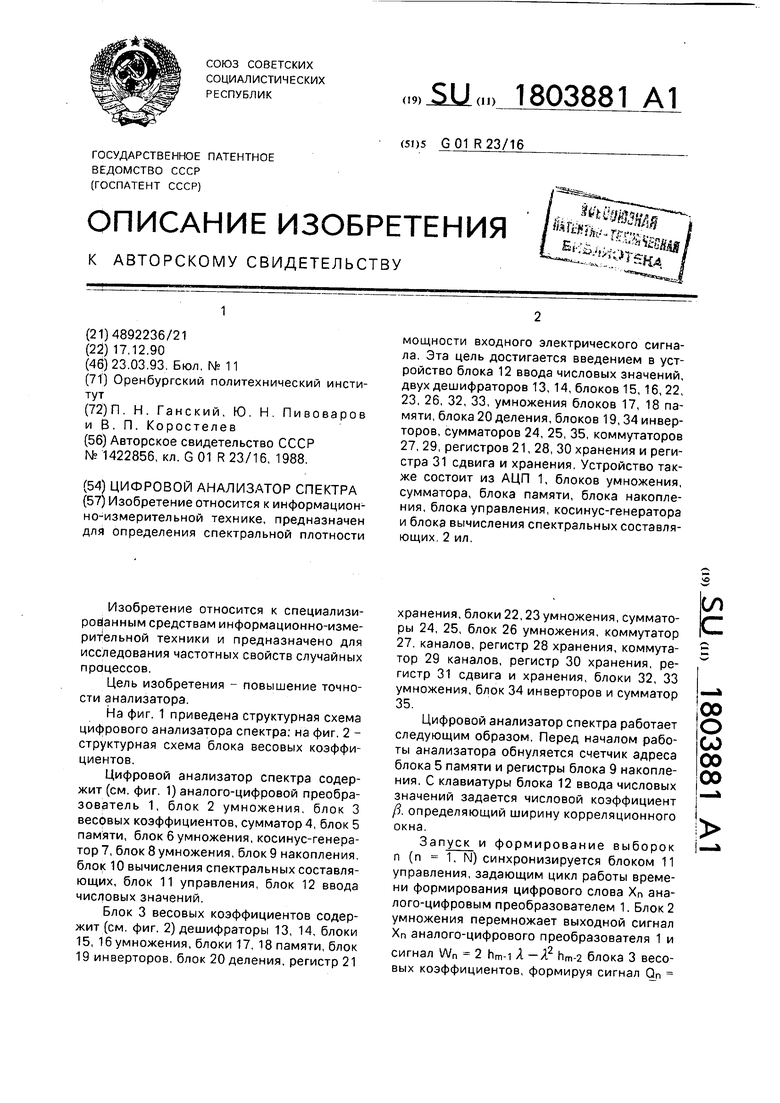

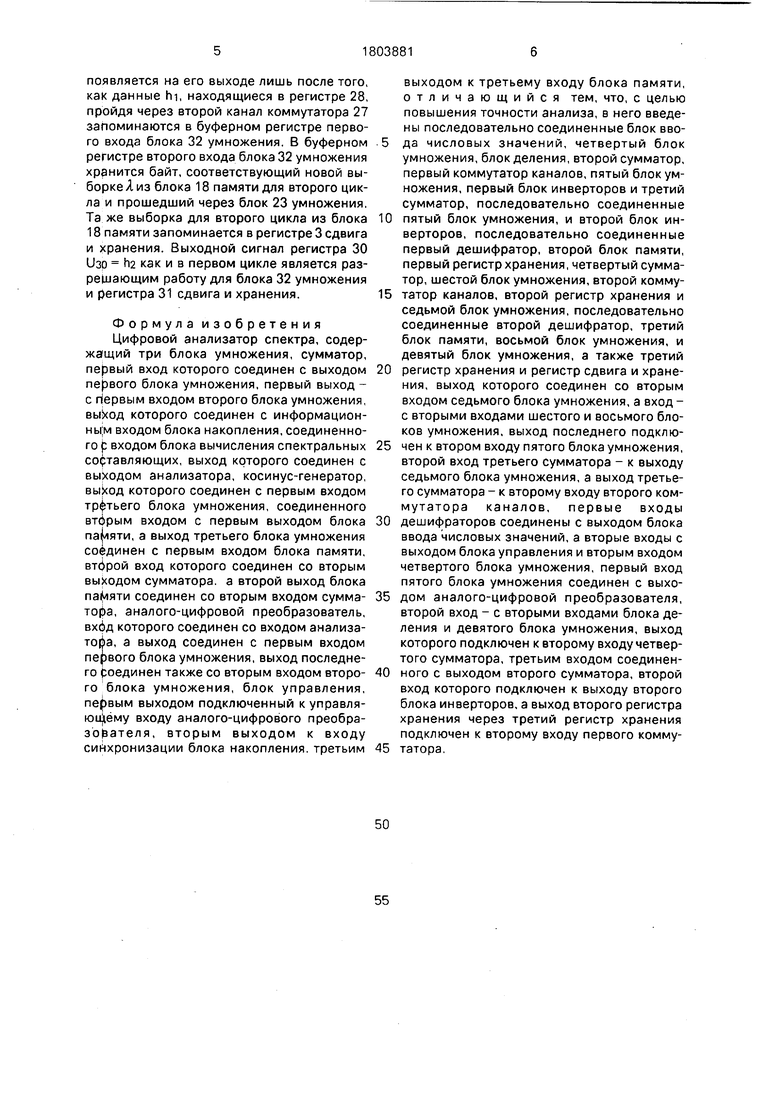

На фиг. 1 приведена структурная схема цифрового анализатора спектра; на фиг. 2 - структурная схема блока весовых коэффициентов.

Цифровой анализатор спектра содержит (см. фиг. 1) аналого-цифровой преобразователь 1, блок 2 умножения, блок 3 весовых коэффициентов, сумматор 4, блок 5 памяти, блок 6 умножения, косинус-генератор 7, блок 8 умножения, блок 9 накопления, блок 10 вычисления спектральных составляющих, блок 11 управления, блок 12 ввода числовых значений.

Блок 3 весовых коэффициентов содержит (см. фиг. 2) дешифраторы 13, 14, блоки 15, 16 умножения, блоки 17, 18 памяти, блок 19 инверторов, блок 20 деления, регистр 21

хранения, блоки 22,23 умножения, сумматоры 24, 25, блок 26 умножения, коммутатор 27, каналов, регистр 28 хранения, коммутатор 29 каналов, регистр 30 хранения, регистр 31 сдвига и хранения, блоки 32, 33 умножения, блок 34 инверторов и сумматор 35.

Цифровой анализатор спектра работает следующим образом. Перед началом работы анализатора обнуляется счетчик адреса блока 5 памяти и регистры блока 9 накопления. С клавиатуры блока 12 ввода числовых значений задается числовой коэффициент /. определяющий ширину корреляционного окна.

Запуск и формирование выборок л (п 1, N) синхронизируется блоком 11 управления, задающим цикл работы времени формирования цифрового слова Хп ана- лого-цифровым преобразователем 1. Блок 2 умножения перемножает выходной сигнал Хп аналого-цифрового преобразователя 1 и

сигнал Wn 2 hm-1 Я -Я2 hm-2 блока 3 весовых коэффициентов, формируя сигнал Qn

ел

С

|00

о GJ

00

00

XnWn, который в сумматоре 4 совместно с выборками (рп из блока 5 памяти служит для выработки выходного сигнала Jnk - 9 - уЛ - 2 . Значение каждой выборки (р из блока 5 памяти определяется сигналом Ck

cos -г- k косинус-генератора 7, соответствующим К-й спектральной составляющей и рекуррентным соотношением рп Ck рп - 1 - kn - 2 + Q. Блок 8 умножения

вырабатывает сигнал i/Ј JnkQn, поступающий в блок 9 накопления, который суммирует значение t/ft 3a N циклов работы и

м

17 k- t-rn Sv

формирует входной сигнал Zn

п 1

Zm-ik + $n Z0k 0; m TTN} для блока 10 вычисления спектральных составляющих,

выходной сигнал Sk которого является оценкой спектральной плотности мощности для К-й составляющей спектра исследуемого сигнала.

Выходной сигнал Wn блока 3 весовых коэффициентов получается на выходе сумматора 35 как разностный сигнал hm

2 hm-iA - Я2 hm-2. Для этого блок 11 управления выставляет цифровой код, определяющий интервал дискретизации At, который вместе с кодом, определяющим ширину корреляционного окна / и задаваемым с клавиатуры в блоке 12 ввода числовых значений поступает на входы дешифраторов 13, 14 и формирует на их выходах адреса ячеек блоков 17, 18 памяти, которые содержат цифровой код значений А0 и

-/ЗДт Я есоответственно. Коммутаторы

27,29 первоначально установлены на прием данных из первого канала. По окончании цикла работы происходит переключение коммутаторов 27 и 29. Одновременно информационные сигналы с блока 11 управления и блока 12 ввода числовых значений фиксируются буферными регистрами первого и второго входов блока 16 умножения, который производит умножение и выдачу результата Ui6 /J At, при поступлении сигнала разрешения работы (на фиг. 2 управляющие сигналы не показаны). Выбранный таким образом из блока 17 памяти байт значения АО поступает на входы сразу четырех блоков: на второй вход 15 блока умножения, на второй вход блока 20 деления, на первый вход блока 22 умножения и на вход регистра 21 хранения. На I вход блока 15 умножения приходит с выхода аналого-цифрового пре0

образователя 1 дискретизированный входной сигнал X(t). Выход блока 15 умножения через блок 19 инверторов подключен к первому входу сумматора 24, второй вход которого соединен с выходом блока 20 деления. Байт значения Я, считанный из блока 18 памяти, поступает на оба входа блока 23 умножения, с выхода которого байт 1)23 Я2 приходит на второй вход блока 22 умножения и на второй вход блока 32 умножения, где и фиксируется входными буферными регистрами каждого из блоков. При наличии на выходе сумматора 24 результирующего

At/З л --г-1- - А0х, поступающе5 сигнала 1)24 Аг

W

го через коммутатор 27 канала в буферный регистр первого входа блока 32 умножения и одновременно поступающего на первый вход сумматора 25, подаются сигналы разрешения на передачу данных из регистра 21 хранения на второй вход сумматора 25 и выдачу результата умножения из блока 22 умножения на третий вход того же сумматора. Выходной сигнал сумматора 25 1)25 AI + АО (1 + Я2) приходит на первый вход блока 26 умножения, в буферном регистре второго входа которого была зафиксирована сделанная ранее выборка Uie Я из блока 18 памяти, записанная также в регистр 31 сдвига и хранения. С выхода блока 26 умножения сигнал U26 hi + А0 (1 + Я2) пройдя через коммутатор 29 канала приходит в регистр 30 хранения, который, не фиксируя, передает его на первый вход блока 33 умножения и регистр 28 промежуточного хранения. Появление сигнала U26 на выходах регистра 30 приводит к одновременной выдаче сигнала разрешения работы для блока 32 умножения и для регистра 31 сдвига и хранения. Выходной сигнала последнего, содержащий значение Uai 2 Я, полученное сдвигом входного байта на один разряд влево, приходит на второй вход блока 33 умножения, с выхода которого сигнал Узз 2 Я hi поступает на второй вход сумматора 35, на первый вход которого приходит прошедший через блок 34 инверторов выходной сигнал блока 32 умножения U32 AI Я2. Появление сигнала Uss Wn 2 hi Я- Я2 h0 на выходе сумматора 35 означает окончание первого цикла работы. Коммутаторы 27 и 29 каналов переключаются в состояние выбора данных из второго канала и остается так до тех пор, пока не появится новый сигнал начальной установки и инициализации анализатора спектра. Таким образом, выходной сигнал 1)з5 сумматора 35 пройдя через второй канал 29 коммутатора каналов запоминается в регистре 30 промежуточного хранения и

0

5

0

5

0

5

0

5

появляется на его выходе лишь после того, как данные hi, находящиеся в регистре 28, пройдя через второй канал коммутатора 27 запоминаются в буферном регистре первого входа блока 32 умножения. В буферном регистре второго входа блока 32 умножения хранится байт, соответствующий новой выборке Я из блока 18 памяти для второго цикла и прошедший через блок 23 умножения. Та же выборка для второго цикла из блока 18 памяти запоминается в регистре 3 сдвига и хранения. Выходной сигнал регистра 30 изо ha как и в первом цикле является разрешающим работу для блока 32 умножения и регистра 31 сдвига и хранения.

Формула изобретения Цифровой анализатор спектра, содержащий три блока умножения, сумматор, первый вход которого соединен с выходом первого блока умножения, первый выход - с Первым входом второго блока умножения, выход которого соединен с информационны входом блока накопления, соединенного Ј входом блока вычисления спектральных составляющих, выход которого соединен с выходом анализатора, косинус-генератор, которого соединен с первым входом трфтьего блока умножения, соединенного вторым входом с первым выходом блока памяти, а выход третьего блока умножения соединен с первым входом блока памяти, второй вход которого соединен со вторым выходом сумматора, а второй выход блока памяти соединен со вторым входом сумматора, аналого-цифровой преобразователь, вхбд которого соединен со входом анализатора, а выход соединен с первым входом первого блока умножения, выход последнего Соединен также со вторым входом второго блока умножения, блок управления, первым выходом подключенный к управля- юЦёму входу аналого-цифрового преобразователя, вторым выходом к входу синхронизации блока накопления, третьим

выходом к третьему входу блока памяти, отличающийся тем, что, с целью повышения точности анализа, в него введены последовательно соединенные блок ввода числовых значений, четвертый блок умножения, блок деления, второй сумматор, первый коммутатор каналов, пятый блок умножения, первый блок инверторов и третий сумматор, последовательно соединенные

пятый блок умножения, и второй блок инверторов, последовательно соединенные первый дешифратор, второй блок памяти, первый регистр хранения, четвертый сумматор, шестой блок умножения, второй коммутатор каналов, второй регистр хранения и седьмой блок умножения, последовательно соединенные второй дешифратор, третий блок памяти, восьмой блок умножения, и девятый блок умножения, а также третий

регистр хранения и регистр сдвига и хранения, выход которого соединен со вторым входом седьмого блока умножения, а вход - с вторыми входами шестого и восьмого блоков умножения, выход последнего подключен к втором входу пятого блока умножения, второй вход третьего сумматора - к выходу седьмого блока умножения, а выход третьего сумматора - к второму входу второго коммутатора каналов, первые входы

дешифраторов соединены с выходом блока ввода числовых значений, а вторые входы с выходом блока управления и вторым входом четвертого блока умножения, первый вход пятого блока умножения соединен с выходом аналого-цифровой преобразователя, второй вход - с вторыми входами блока деления и девятого блока умножения, выход которого подключен к второму входу четвертого сумматора, третьим входом соединенного с выходом второго сумматора, второй вход которого подключен к выходу второго блока инверторов, а выход второго регистра хранения через третий регистр хранения подключен к второму входу первого коммутатора.

Фиг

| название | год | авторы | номер документа |

|---|---|---|---|

| РАДИОМОДЕМ | 2024 |

|

RU2830959C1 |

| Цифровой анализатор спектра речевого сигнала | 1982 |

|

SU1126969A1 |

| Устройство для реализации быстрого преобразования Фурье | 1984 |

|

SU1233166A1 |

| Цифровой анализатор спектра | 1982 |

|

SU1126892A1 |

| Цифровой анализатор спектра фурье | 1976 |

|

SU614440A1 |

| Анализатор спектра | 1981 |

|

SU1013970A1 |

| Многоканальный цифровой коррелометр | 1982 |

|

SU1040492A1 |

| Цифровой генератор спектра фурье | 1973 |

|

SU446063A1 |

| Система ввода телевизионных изображений в ЭВМ | 1989 |

|

SU1665391A1 |

| Цифровой анализатор | 1979 |

|

SU834581A1 |

Изобретение относится к информационно-измерительной технике, предназначен для определения спектральной плотности мощности входного электрического сигнала. Эта цель достигается введением в устройство блока 12 ввода числовых значений, двух дешифраторов 13, 14, блоков 15, 16, 22, 23, 26, 32, 33, умножения блоков 17, 18 памяти, блока 20 деления, блоков 19, 34 инверторов, сумматоров 24, 25, 35, коммутаторов 27, 29, регистров 21,28, 30 хранения и регистра 31 сдвига и хранения. Устройство также состоит из АЦП 1, блоков умножения, сумматора, блока памяти, блока накопления, блока управления, косинус-генератора и блока вычисления спектральных составляющих. 2 ил.

Редактор Г.Мельникова

Составитель Л.Устинова

Техред М.МоргенталКорректор Н.Ревская

| Авторское свидетельство СССР № 1422856, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1993-03-23—Публикация

1990-12-17—Подача