Изобретение относится к электрои радиоизмерительной технике и может быть использовано для измерения спек тра, взаимного спектра и коэффициента когерентности. Известен цифровой анализатор, содержащий/логарифмический аналого-цифровой преобразователь, два сумматора, преобразователь логарифмического кода в линейный, соединённый со вторым сумматором, оперативное запоминающее устройство, соединенное цепями перезаписи кодов с втором сум матором, постоянное запоминающее уст ройство, блок управления, соединен- ный со всеми блоками . Однако известный цифровой анализатор не позволяет измерить взаимный спектр и коэффициент когерентности, а также представить результаты измерения в полярных координатах и в логарифмическом масштабе. Цель изобретения - расширение диапазона анализа. Поставленная цель достигается тем, что в цифровой анализатор, содержащий аналоговый коммутатор, подключенный ко входу логарифмического аналого-цифрового преобразователя, два сумматора, преобразователь логарифмического кода в линейный, оперативное запоминающее устройство, постоянное запоминающее устройство, преобразователь линейного кода в логарифмический и блок управления, дополнительно введены регистр сдвига, регистр памяти, преобразователь линейного кода; в код арктангенса и цифровой коммутатор, входы которого связаны с одним из выходов первого сумматора, выходом постоянного запоминающего устройства, выходом логарифмического аналого-цифрового преобразователя, с выходом преобразователя линейного кода в логарифмический и с выходом регистра памяти, причем второй сумматор включен между выходом преобразователя логариф-

мического кода в линейный и выходом оперативного запоминающего устройства, первый сумматор включен между выходом цифрового коммутатора и входом регистра сдвига, выход которого подключен ко входу регистра памяти и одновременно к последовательно соединенным преобразователю логарифмического кода в линейный, преобразователю линейного кода в код арктангенса и оперативному запоминающему устр-ойству, второй вход которого подключе к выходу преобразователя линейного кода в логарифмический, соединенному также со вторым входом регистра памяти, третий вход подключен к выходу второго сумматора и одновременно ко входу преобразователя линейного кода в логарифмический.

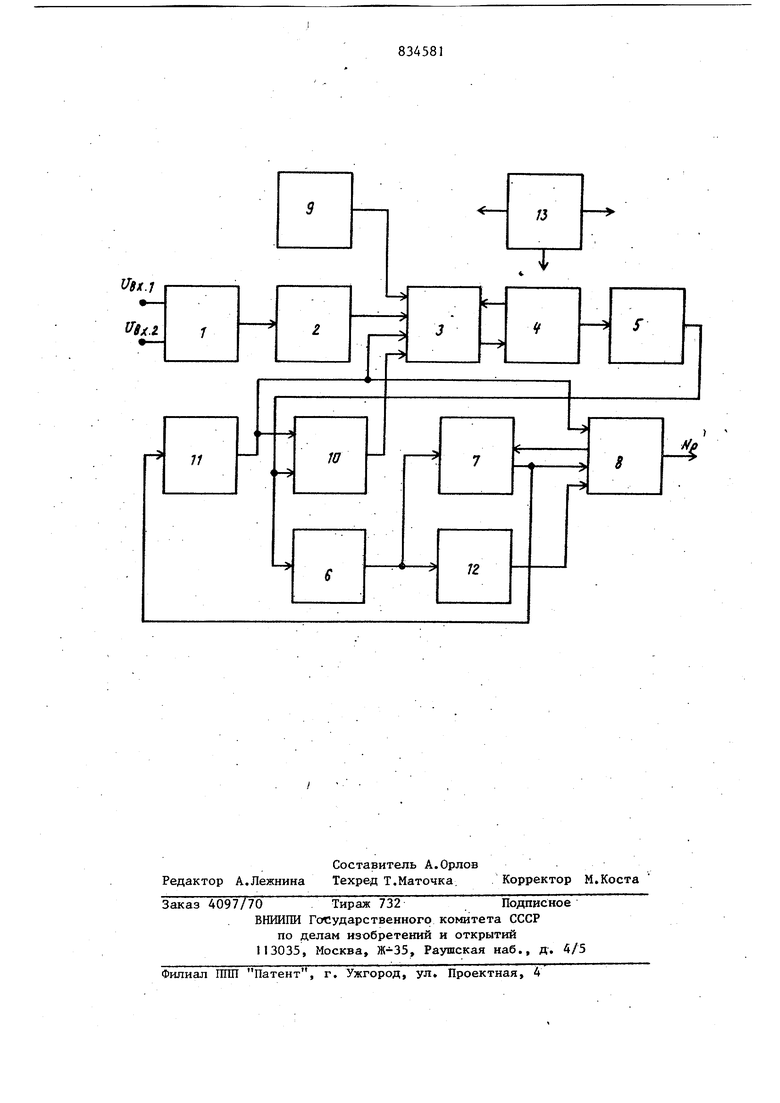

На чертеже приведена структурная схема цифрового анализатора,

Схема включает последовательно соединенные, аналоговый коммутатор 1, соединенный с входами анализатора LLvjH ит,уо,логарифмический анаВл i Az;/

ЛОГО-1ДИФРОВОЙ преобразователь (АЦП; 2, цифровой коммутатор 3, первый сумматор 4, регистр 5 сдвига, преобразователь 6 логарифмического кода Б линейный, второй сумматор 7, опеpaTHBiioe запоминающее устройство 8, выходной код которого представляет собой результат измерения, а также постоянное запоминающее устройство 9, выход которого подключен к входу цифрового коммутатора 3, регистр 10 памяти, преобразователь П линейного кода в логарифмический, преобразователь 12 линейного кода в код арктангенса, блок 13 управления, соедииенньй со всеми блоками. Вход лреобразохзателя 11 линейного кода в ло1арифмйческий подклю.чен к выходу второго сумматора, а выход соединен со входами оперативного запоминающего устройства .8, регистра 10 и цифрового коммутатора 3. Регистр 10 содержит, кроме того, второй вход, который подключен к выходу регистра 5 сдвига, а выход 10 регистра соединен с входом .цифрового коммутатора 3. Вход преобразователя 12 линейного кода в код арктангейса подключен к выходу преобразователя 6 логарифмического кода в лин ейный, а выход - к входу оперативного запоминающего устройства 8,

Анализатор работает следующим образом.

При измерении составляющих преобразования Фурье производится подключение первого входного., сигнала к входу преобразователя 2, логарифмичекое аналого-цифровое преобразование (АЦП) этого сигнала с помощью преобразователя 2, передача кодов логарифмического АЦП и постоянного запоминающего устройства 9 на сумматор 4. С выхода сумматора 4 сумма логарифмов входного напряжения и sin cos- составляющих, хранящихся в устройстве 9, подается через регистр 5 сдвига (без сдвига в этом режиме) на преобразователь.6 логарифмического кода в линейный, после чего производится накопление sin-, cosсоставляющих с помощью второго сумматора 7 и оперативного запоминающего устройства 8. При этом в оперативном запоминающем устройстве 8 каждому исследуемому сигналу, каждой частоте соответствует четыре ячейки: две--для хранения и накопления sin-, cos- составляющих, две - для хранения и накопления модуля и фазы спектра, кроме того, в устройстве 8 каждой частоте соответствует еще 3 ячейки: две- для хранения и накопления модуля и фазы взаимного спектра, а третья - для хранения вычисленного значения коэффициента когерентности. После измерения и вычисления одной дискреты по первому каналу коммутатор 1 подключает второй канал (Ug--) к входу преобразователя 2, и производится аналогичное измерение и вычисление при тех же значениях sin-, cos- составлякицих, извлекаемых из устройства 9. После вычисления одной дискреты по всем каналам извлекается следунщее значение составляющих из постоянного запоминающего устройства 9, снова аналоговьтй коммутатор 1 подключает к преобразователю 2 первый канал (Upj(), и производятся аналогичные измерения и вычисления. Измерение частоты ортогональных составляющих достигается изменением.тактовой частоты опроса ячеек постояниого запоминающего устройства 9 После окончания измерения sin-, cos- составляющих по всем частотам и каналам на первом участке исследуемого сигнала производится их преобразование в полярную сиетему координат с модулем К - и фазой 1 на частоте ив j-том канале. Уравнение преобразования координат имеет следую01ий пяд: V 09 4 og ant i log2logS--«-anti logZlogGj, f rrarctg -4- arctg ant i log logS, 1 « Т li . J.- -logG j sin- составляющая j-того входного сигнала на частоте ; cos- составляющая j-того входного сигнала на частоте f -. реализации уравнения (1) состав ляющая S.-: считывается из оперативного за,поминающего устройства 8, передается через второй сумматор 7, преобразуется в логарифмический код в преобразователе 11, затем передается через цифровой коммутатор 3 и сумматор 4 на регистр 5 где происходит удвоение кода путем сдвига, после чего информация через преобразователь 6 логарифмического кода в линейный и через сумматор 7 записывается в третью ячейку оперативного запоминающего устройства 8, со ответствующую частоте , к j-тому каналу. Аналогичное преобразование производится 1|ад G :, после чего производится суммирование двух анти логарифмов в сумматоре 7, затем пре образование полученной суммы в прео разователе 11, передача через комму татор 3 и сумматор 4, сдвиг в сторо ну младших разрядов в регистре 5 га, что соответствует умножению на , далее преобразование в линейный код в преобразователе 6, и, наконец., вычисленное значение R,-; записывается через сумматор 7 в оперативное запоминающее устройство 8. Для реализации уравнения (2) составляющая считывается, передаётся через сумматор 7, преобразуется в логарифмический код в преобразовэ.. еле 11 и запоминается в регистре О, после чего считывается из запоминающего устройства 8 составлякицая и преобразуется в логарифмический код в преобразователе I1. Затем полученные значения логарифмов передЧаются через коммутатор 3 на сумма тор 4, где производится их вычитание- далее информация без сдвига сд 81 . 6 передается через регистр 5 сдвига : преобразуется в линейный код в преобразователе 6, после чего преобразуется в код арктангенса .в преобразователе 12 и эаписывае.тся в устройство 8 в четвертую ячейку, соответствуницую j-тому каналу. Для получения логарифмического представления (log и log Kf) производится считывание соответствуня их ячеек из устройства 8, передача через сумматор 7 на преобразователь 11, после чего преобразованная информация вновь записывается в оперативное запоминаницее устройство 8. Определение модуля и фазы взаимного спектра 1-той частоты каналов j и (j+l) производится в соответствии с уравнениями: V /.V °9 ( g -(i+oV ) Для реализации уравнения (Э) СЧИтьшается из устройства 8, передается через сумматор 7, преобразуется в преобразователе 11 и запоминается в регистре 10. Затем считывается , передается через сумматор 7, преобразуется в преобразователе 1I« после чего полученные логарифмические коды через коммутатор 3 поступают на сумматор 4, где суммируется. Результат суммирования без сдвига передается через регистр 5 сдвига, преобразуется в линейный код в преобразователе 6 и через сумматор 7 записывается в устройство 8. Реализация уравнения (4) осуществляется с помощью вычитания в сумматоре 7 кодов, считанных из устройства 8. Для уменьшения погрешности из-за флюктуации измеряемых спектральных характеристик исследуемого случайного сигнала в анализаторе производится усреднение этих характеристик между участками сигнала. Усреднение производится путем накоппенця измеренных на каждом участке характеристик с помощью второго сумматоа 7 и оперативного запоминающего стройства 8. В результате усреднеия получаются средние значения . -/4 )Определение коэффициента когеретности между j-тьм и (j +1) каналами на i -той частоте производится в соответствии с уравнением: i-j, + -1 i-n Г - antitog- tog МН ,. i jj-H -T-(og R,-- (.,f Для реализации уравнения (5) считывается из устройства 8, через сумматор 7 подается на преобразователь 11, а затем преобразованный код запоминается в регистре 10. Далее считывается из устройства 8 и также через сумматор 7 подается на преобразователь 11. Логарифмические коды с выходов преобразователя П и регистра 10 через коммутатор 3 поступают на сумматор 4, где определяется их сумма, которая поступает на вход регистра 5 сдвига Последний сдвигает сумму на один разряд в сторону младших разрядов, чем обеспечивается умножение на 4Затем информа1щя с выхода регистра 5 сдвига поступает на-регистр 10, Далее считывается Г 7 из устройства 8 и через сумматор 7 подает ся на преобразователь 11, после чего логарифмические коды с выходов преобразователя 11 и регистра 10 поступают через коммутатор 3 на сум матор 4, где производится вычитание Полученный результат без сдвига передается через регистр 5 сдвига, преобразуется в линейный код в прео разователе б и через сумматор 7 за-письшается в устройстве 8. Такш- образом, цифровой анализатор с использованием логарифмических преобразований позволяет измери взаимнь1й спектр и коэффициент когерентности, а также представить результаты измерения в полярных коорд Iкатах и логарифмичеёком масштабе. Это дает возможность применить его для автоматизации научного зксперимента, что обеспечивает повышение производительности труда при измерении статистических характеристик случайных сигналов. Применение анализатора в радиотехнической и радио электронной промышленностях позволи повысить оперативность получения ха рактеристик случайных сигналов и достоверность измерительной информа 834581.8 ции за счет исследования большего числа информативных характеристик случайных сигналов, Формула изобретения Цифровой анализатор, содержащий аналоговый коммутатор, подключенный ко входу логарифмического аналогоцифрового преобразователя, два сумматора, преобразователь логарифмического кода в линейный , -оперативное запоминающее устройство, постоянное запоминающее устройство, преобразователь линейного кода в логарифмический и блок управления, отличающийся тем, что, с целью расширения диапазона анализа, в него дополнительно введены регистр сдвига, регистр памяти, преобразователь линейного кода в код арктангенса и цифровой коммутатор, входы которого связаны с одним из выходов первого сумматора, выходом постоянного запоминающего устройства, выходом логарифмического аналого-цифрового преобразователя, с выходом преобразователя линейного кода в логарифмический и с выходом регистра памяти, причем второй сумматор включен между выходом преобразователя логарифмического кода в линейньш и выходом оперативного запоминающего устройства, первый сумматор включен между выходом цифрового коммутатора и входом регистра сдвига, выход которого подключен ко входу регистра памяти и одновременно юпослёдовательно соединенным преобразователю, логарифмического кода в линейный, . преобразователю линейного кода в код арктангенса и оперативному запоми- . нающему устройству, второй вход которого подключен к выходу преобразователя линейного кода в логарифмический, соединенному также со вторым входом регистра памяти, третий вход подключен к выходу второго сумматора и одновременно ко входу преобразователя линейного кода в логарифмический . Источники информации, принятые во внимание при экспертизе 1. AjBTOpcKoe свидетельство СССР № 473118, кл. G 01 R 237.16, 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой одноканальный инфранизкочастотный фазометр | 1987 |

|

SU1472831A1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ КОЭФФИЦИЕНТА ГАРМОНИКИ НАПРЯЖЕНИЯ | 1990 |

|

RU2030753C1 |

| Электрогирационное устройство для бесконтактного измерения высоких напряжений | 1985 |

|

SU1298669A1 |

| Логарифмический преобразователь | 1985 |

|

SU1269126A1 |

| Логарифмический преобразователь | 1984 |

|

SU1196860A1 |

| Анализатор спектра | 1979 |

|

SU851282A1 |

| Устройство измерения параметров дисбаланса | 1990 |

|

SU1795318A1 |

| УСТРОЙСТВО ЦИФРОВОЙ КОГЕРЕНТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1990 |

|

SU1818989A1 |

| Логарифмический преобразователь | 1981 |

|

SU959073A1 |

| Вентильный электропривод | 1987 |

|

SU1480084A1 |

Авторы

Даты

1981-05-30—Публикация

1979-01-16—Подача