Изобретение относится к автоматическим регуляторам.

Цель изобретения - уменьшение указанных недостатков.

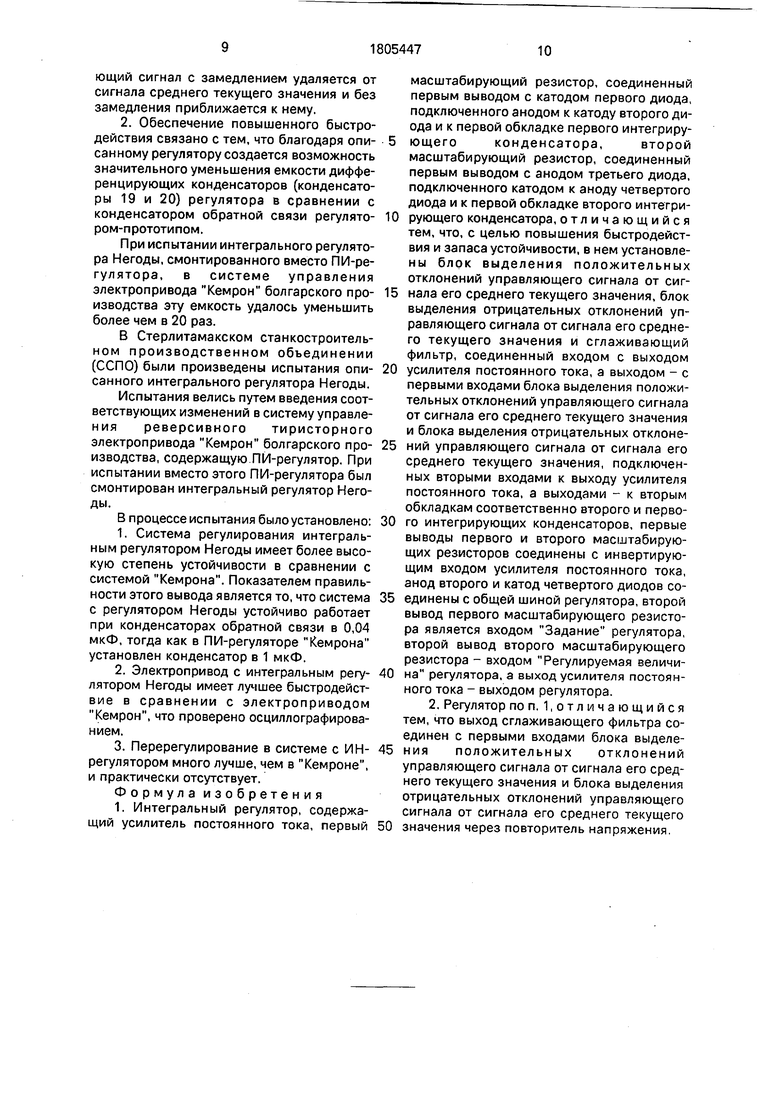

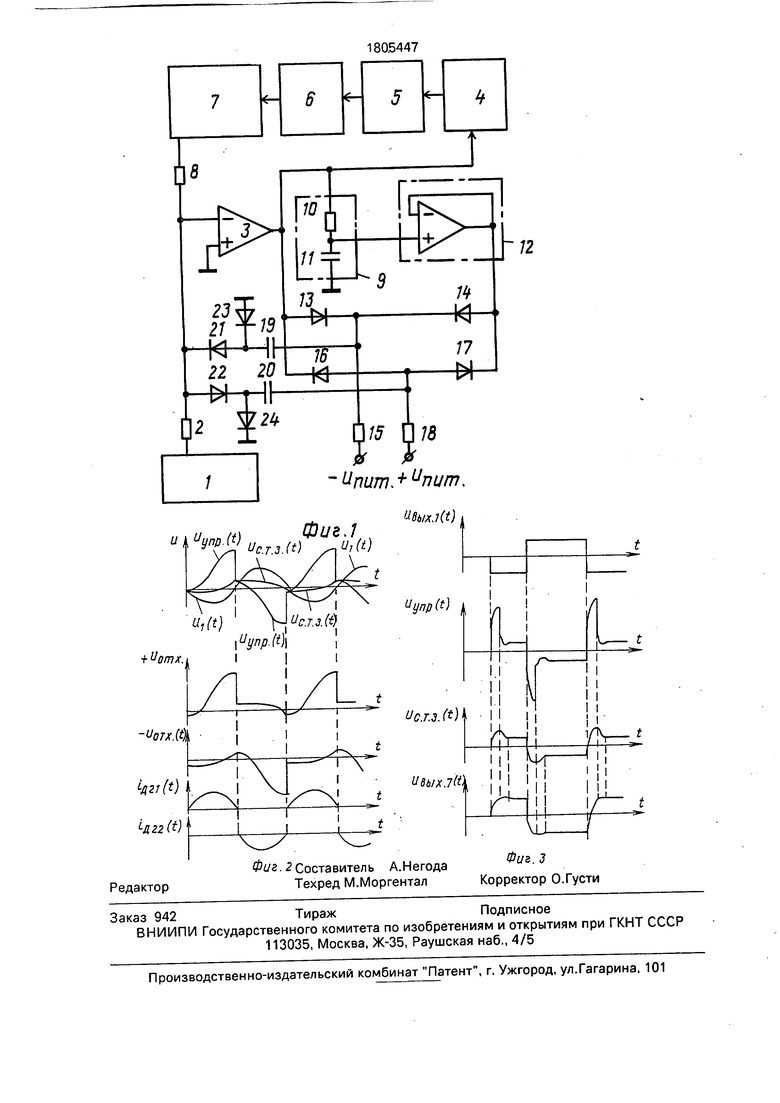

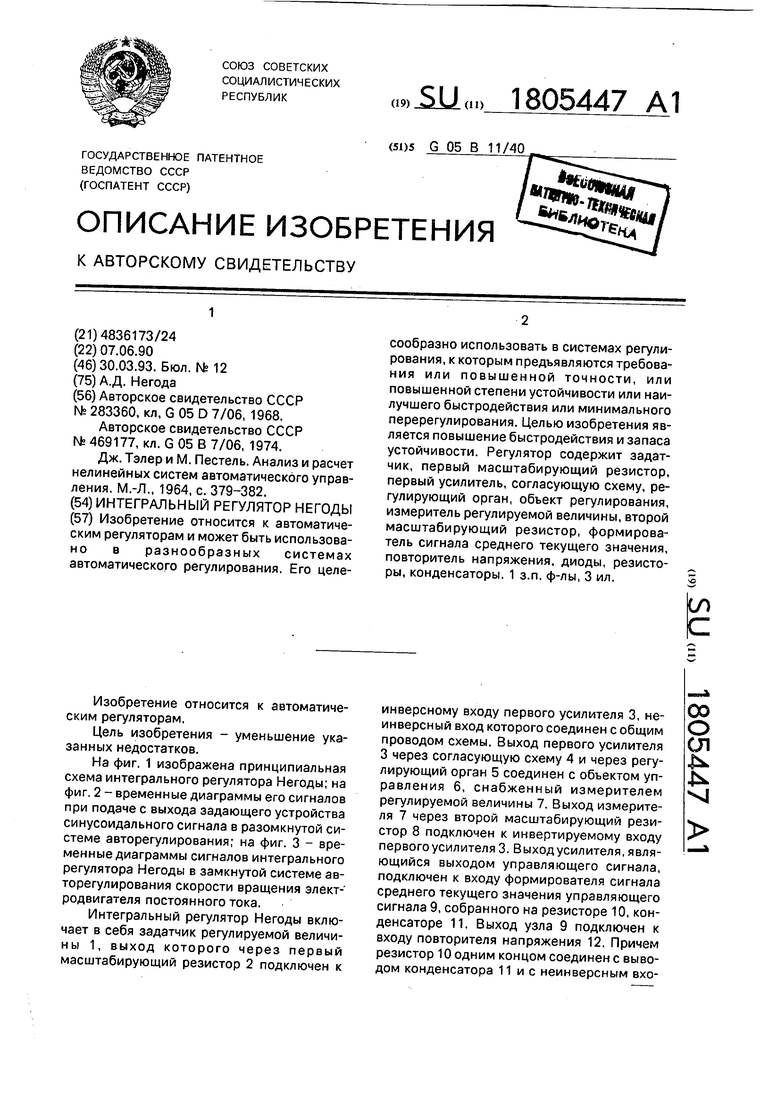

На фиг. 1 изображена принципиальная схема интегрального регулятора Негоды; на фиг. 2 - временные диаграммы его сигналов при подаче с выхода задающего устройства синусоидального сигнала в разомкнутой системе авторегулирования; на фиг. 3 - временные диаграммы сигналов интегрального регулятора Негоды в замкнутой системе авторегулирования скорости вращения электродвигателя постоянного тока.

Интегральный регулятор Негоды включает в себя задатчик регулируемой величи- ны 1, выход которого через первый масштабирующий резистор 2 подключен к

инверсному входу первого усилителя 3, неинверсный вход которого соединен с общим проводом схемы. Выход первого усилителя 3 через согласующую схему 4 и через регулирующий орган 5 соединен с объектом управления 6, снабженный измерителем регулируемой величины 7. Выход измерителя 7 через второй масштабирующий резистор 8 подключен к инвертируемому входу первого усилителя 3. Выход усилителя, являющийся выходом управляющего сигнала, подключен к входу формирователя сигнала среднего текущего значения управляющего сигнала 9, собранного на резисторе 10, конденсаторе 11, Выход узла 9 подключен к входу повторителя напряжения 12. Причем резистор 10 одним концом соединен с выводом конденсатора 11 и с неинверсным вхо00

о ел

Јь -N

дом операционного усилителя 12. Инверсный вход усилителя 12 соединен с выходом этого же усилителя, а второй вывод конденсатора 11 соединен с общим проводом схе- мы. Блок выделения положительных отклонений управляющего сигнала от сигнала его среднего текущего значения собран на диодах 13 и 14, а также на резисторе 15.4 Катоды диодов 13 и 14 соединены между собой и соединены с одним выводом резистора 15, второй вывод которого подключен к источнику минусового отрицательного напряжения. Анод диода 13 соединен с выходом первого усилителя 3, а анод диода 14 - с выходом усилителя 12. Блок выделения отрицательных отклонений собран на диодах 16, 17, а также на резисторе 18. Аноды диодов 16 и 17 соединены между собой и соединены с одним выводом резистора 18. Второй вывод которого подключен к положительному источнику питания. Катод диода 16 подключен к выходу первого усилителя 3, а катод диода 17 - к выходу усилителя 12; общие точки диодов 13 и 14, а также диодов 16 и 17 соответственно через первый и второй интегрирующие конденсаторы 19 и 20, а также соответственно через первый диод 21 и через третий диод 22 соединены с входом первого усилителя 3. Общие точки диода 21 и конденсатора 19, а также диода 22 и конденсатора 20 соответственно через второй диод 23 и через чвет- вертый диод 24 подключены к общему проводу схемы.

Интегральный регулятор Негоды, изображенный на фиг. 1, работает следующим образом.

С выхода задатчика 1 снимается задающее напряжение регулируемой величины. С выхода измерителя регулируемой величины 7 снимается напряжение, пропорциональное регулируемой величине, которое пропорционально напряжению задания.

Цепь инверсного входа первого усилителя 3 является сумматором токов задатчика 1 через масштабирующий резистор 2, измерителя регулируемой величины 7 - через масштабирующий резистор 8, положительной составляющей тока конденсатора 19 - через диод 20 и отрицательной составляющей тока конденсатора 22 - через диод 23. Напряжение, снимаемое с выхода первого усилителя 3, является управляющим сигналом (напряжением) и подается через согласующую схему 4 на вход объекта управления 6, а также через согласующий RC-фильтр, являющийся формирователем сигнала среднего текущего значения управляющего сигнала, на вход повторителя напряжения 12. Усилитель 12 собран на схема дифференциального усилителя. С его выхода снимается напряжение, равное напряжению на конденсаторе 11. Сигнал среднего текущего значения управляющего сигнала с выхода

усилителя 12, а также управляющий сигнал с выхода первого усилителя 3 подаются на входы блоков выделения положительных и отрицательных отклонений управляющего сигнала от сигнала его среднего текущего

значения.

Терминологическое определение положительных и отрицательных отклонений уп- равляющего сигнала от сигнала его среднего текущего значения. Положительные и отрицательные отклонения получаются при сравнении напряжений управляющего сигнала и сигнала его среднего текущего значения. Положительные отклонения формируются при положительной

разности между управляющим сигналом и сигналом среднего текущего значения. Отрицательные отклонения формируются при отрицательной этой разности. При наличии положительных отклонений выходное напряжение положительных отклонений равно напряжению управления, а в промежутках между положительными отклонениями или при сигнале рассогласования, равном нулю, это напряжение равно

напряжению среднего текущего значения управляющего сигнала. Аналогично при наличии отрицательных отклонений выходное напряжение отрицательных отклонений также равно напряжению управления, а в

промежутках между отрицательными отклонениями или при сигнале рассогласования, равное нулю, также равно сигналу среднего текущего значения.

Математическое определение сигнала

положительных отклонений управляющего сигнала от сигнала его среднего текущего значения:

+Uo-noi(t) Uynp(t) при Uynp(t) - Uc-т.з. О, т.е. при ic.p. О

+UoT10l(t) Uc.T.3.(t) ПРИ Uynp(t) - Uc.T.3.(t) О,

т.е. при ic.p.(t) 0 или при ic.p.(t) О

Математическое определение отрица- тельных отклонений:

-UoTWi(t) Uynp(t) при Uynp(t) - Uc.T.3.(t) О,

т.е. при ic.p.(t) О

-и0ткл(х) Uc.T.3.(t) При Uynp(t)- Uc.T.3.(t) О

т.е. при ic.p.(t) 0 или при ic.p.(t) 0.

Выделение положительных и отрицательных отклонений осуществляется не относительно нулевого потенциала, а относительно напряжения сигнала среднего текущего значения. Поэтому, например, положительное отклонение управляющего сигнала возможно при отрицательном напряжении на выходе блока выделения поло- жительных отклонений, что не противоречит вышеприведенным определениям.

Блок выделения положительных отклонений, собранный на диодах 13 и 14 и на резисторе 15, работает следующим образом. Напряжение отрицательного источника питания, подключенного к резистору 15, выбирается значительно большим, например раза в два, чем отрицательное напряже- ние питания усилителей 3 и 12. При равенстве напряжений на выходах усилителей 3 и 12 оба диода 13 и 14 открыты, а напряжение на их общей точке равно напряжению на выходе усилителей 3 и 12.

При положительных отклонениях напряжения на выходе первого усилителя 3 по отношению к напряжению на выходе усилителя 12 диод 14 запирается, а напряжение общей точки диодов 13 и 14, если пренебречь потенциалом отпирания диода 13, будет равно напряжению на выходе усилителя 3. При отрицательных отклонениях управляющего сигнала запирается диод 13, а напряжение общей точки диодов 13 и 14 будет равно напряжению на выходе усилителя 12. Таким образом напряжение общей точки диодов 13 и 14 (напряжение на выходе блока выделения положительных отклонений) всегда равно большему в положительную сторону из выходных напряжений первого усилителя 3 и усилителя 12, т.е. при наличии положительного отклонения управляющего сигнала от сигнала его среднего текущего значения напряжения на выходе диодов 13 и 14 равно напряжение управляющего сигнала, а при отрицательных отклонениях-на- пряжению сигнала среднего текущего значения. Блок выделения отрицательных отклонений выполнено на диодах 16 и 17 и на резисторе 18. Величина питающего положительного источника напряжения, подключенного к резистору 18, выбирается значительно большей (например, раза в два), чем положительное напряжение питания усилителей 3 и 12. Блок выделения отрицательных отклонений работает аналогично блоку выделения положительных отклонений. Напряжение на выходе этого блока (общая точка диодов 16, 17 и резистора 18 равно или управляющему сигналу- при наличии отрицательных отклонений управляющего сигнала от сигнала его среднего текущего значения, или сигналу среднего текущего значения управляющего сигнала - при положительных отклонениях.

Емкостные токи конденсаторов 19 и 20 пропорциональны производным от выходных напряжений соответственно устройства выделения положительных отклонений и устройства выделения отрицательных отклонений. Масштаб дифференцирования сигналов отклонений пропорционален величине конденсаторов 19 и 20. Проводимость диодов 21 и 22 выполнена такой, что

емкостные токи этих конденсаторов проходят в сторону инверсного входа операционного усилителя 3 только при нарастании во времени модуля отклонения управляющего сигнала от уровня сигнала его среднего текущего значения. При всяких приближениях управляющего сигнала к сигналу среднего текущего значения диоды 21 и 22 оказываются запертыми.

Работа интегрального регулятора Негоды может быть пояснена с помощью временных диаграмм, изображенных на фиг. 2, выполненных для случая подачи с выхода задатчика 1 синусоидального сигнала при разомкнутой системе авторегулирования

при разрыве цепи, например, в резисторе 8. При отрицательной полуволне задающего напряжения для управляющего сигнала, снимаемого с выхода усилителя 3, можно записать:

Uynp(t) k

Hra(t) + lflzi(t) где Uynp(t) - сигнал управления;

k - коэффициент усиления усилителя 3; iR2(t) - задающий ток через резистор 2;

1д21(т) - ток через диод 21.

При нарастании положительного отклонения управляющего сигнала

40

1д21(т) icig(t) Gig

d Uynp.ft) dt

где icig(t) - ток дифференцирующего конденсатора 19.

Подставив полученное выражение в предыдущее уравнение, получим

Uynp(t)k -HR2(t)+Cl9 d

Заметим, что величина Uynp(t) на выходе усилителя 3 вызвана соответствующим то- ком через инверсный электрод этого усилителя

т.е. Uynp(t) k 1Инв.эл.(1), где 1инв.эл.(т) - ток через инверсный электрод усилителя 3. Следовательно,

k 1инв.эл.(у

k HR2(t)+ C19

В связи с очень большим коэффициентом усиления усилителя 3 ток инверсного электрода можно принять равным нулю в сравнении с током через резистор 2 и через конденсатор 19. Поэтому последнее уравнение можно переписать так:

d UynP.(t) 1 at Ci

iR2(t)

Проинтегрировав это уравнение, получим:

,оТкл К2 + С

В случаях замкнутой САР управляющий сигнал в интегральном регуляторе Негоды формируется по таким же алгоритмам - удаление управляющего сигнала от сигнала

своего среднего текущего значения осуществляется замедленно - по интегральному закону, а приближение быстро- по пропорциональному закону.

Поскольку в случае замкнутой САР на

вход усилителя 3 подается ток не только с выхода резистора 2, но и ток с выхода резистора 8, а сумма этих токов, как известно, равна току сигнала рассогласования, то последние интегральные уравнения можно

обобщить в следующем виде:

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕГРАЛЬНЫЙ РЕГУЛЯТОР НЕГОДЫ | 1990 |

|

RU2020536C1 |

| ПРОПОРЦИОНАЛЬНО-ИНТЕГРАЛЬНЫЙ РЕГУЛЯТОР НЕГОДЫ | 1990 |

|

RU2020534C1 |

| ИНТЕГРАЛЬНЫЙ РЕГУЛЯТОР НЕГОДЫ | 1990 |

|

RU2020535C1 |

| Регулятор постоянного тока | 1990 |

|

SU1817075A1 |

| Электронный коммутатор | 1990 |

|

SU1781448A1 |

| Электронная система зажигания | 1981 |

|

SU992791A1 |

| ТИРИСТОРНЫЙ ЭЛЕКТРОПРИВОД НЕГОДЫ | 1989 |

|

RU2020715C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ТИРИСТОРНЫМ ПРЕОБРАЗОВАТЕЛЕМ | 1990 |

|

RU2024169C1 |

| РЕВЕРСИВНЫЙ ЭЛЕКТРОПРИВОД | 1990 |

|

RU2020720C1 |

| ОКТАН-КОРРЕКТОР | 1991 |

|

RU2044154C1 |

Изобретение относится к автоматическим регуляторам и может быть использова- но в разнообразных системах автоматического регулирования. Его целесообразно использовать в системах регулирования, к которым предъявляются требования или повышенной точности, или повышенной степени устойчивости или наилучшего быстродействия или минимального перерегулирования. Целью изобретения является повышение быстродействия и запаса устойчивости. Регулятор содержит задат- чик, первый масштабирующий резистор, первый усилитель, согласующую схему, регулирующий орган, объект регулирования, измеритель регулируемой величины, второй масштабирующий резистор, формирователь сигнала среднего текущего значения, повторитель напряжения, диоды, резисторы, конденсаторы. 1 з.п. ф-лы, 3 ил. ё

где 1нач.откл - время начала последнего положительного отклонения управляющего сигнала от сигнала его среднего текущего значения С Uc,T.3.(tHa4.oTKfl.),

где ис.т.з.(Тнач.откл.) - уровень сигнала среднего текущего значения управляющего сигнала, какой он был в момент времени начала последнего положительного отклонения. То есть, для участка нарастания положительного отклонения величина управляющего сигнала принимает вид:

Uynp(t) Uc.T.3-(tHa4.0TWi.) +

+ -T--SIiraffldt

Cl9 нач.откл

Аналогично, при отрицательных отклонениях:

Uynp(t) .з.(1нач.откл.)

-тД- (t)dt

С20 нач.откл v

В промежутки же времени приближения управляющего сигнала к сигналу своего среднего текущего значения при положительном отклонении конденсатор 19 перезаряжается током противоположной полярности в сравнении с током при нарастании положительного отклонения. Ток конденсатора 19 при уменьшении положительного отклонения проходит через диод 23, конденсатор 19 и через резистор 15. При этом токи обратной связи через диоды 21 и 22 отсутствуют, а приближение управляющего сигнала к сигналу своего среднего текущего значения осуществляется по закону

Uynp(t) k -|R2(t).

Аналогичным образом происходит формирование управляющего сигнала и при отрицательных отклонениях.

0

5

0

5

0

5 0

5

Uynp(t)Uc.T.3.(tHa4.0TO.) ± -р /.ic.p.(t)dt, {, нач.откл. к

Причем 1нач.откл. t 1конца откл.,

где Тконца откл. - время конца отклонения;

ic.p.(t) - сигнал рассогласования.

На фиг. 2 показаны временные диаграммы сигналов интегрального регулятора Негоды в замкнутом САР при синусоидальном изменении сигнала задания.

На фиг. 3 показаны те же сигналы, что и на фиг. 2, а также сигнал измерителя регулируемой величины 7 при ступенчатом изменении сигнала задания.

Сигналы регулятора показаны для случая, когда этот регулятор работает в режиме регулятора скорости, а вообще ИН-регуля- тор может работать с любыми практическими объектами управления, в том числе в качестве регулятора положения,

Усилитель 12 не является обязательным. Без него схема также остается работоспособной, но при этом значительно следует увеличить емкость конденсатора 11 и уменьшить величину резистора 10. Усилитель 12 служит для уменьшения емкости конденсатора 11 и для увеличения резистора 10.

Как показали экспериментальные исследования, наилучшие показатели регулятора получаются при использовании в качестве диодов 21-24 диодов с минимальным потенциалом отпирания, т.е. в качестве этих диодов целесообразно использовать германиевые диоды.

Преимуществами интегрального регулятора Негоды является следующее:

При испытании интегрального регулятора Негоды, смонтированного вместо ПИ-ре- гулятора, в системе управления электропривода Кемрон болгарского производства эту емкость удалось уменьшить более чем в 20 раз.

В Стерлитамакском станкостроительном производственном объединении (ССПО) были произведены испытания описанного интегрального регулятора Негоды.

Испытания велись путем введения соответствующих изменений в систему управления реверсивного тиристорного электропривода Кемрон болгарского производства, содержащую ПЙ-регулятор. При испытании вместо этого ПИ-регулятора был смонтирован интегральный регулятор Него- ды.

В процессе испытания было установлено:

Формула изобретения 1. Интегральный регулятор, содержащий усилитель постоянного тока, первый

масштабирующий резистор, соединенный первым выводом с катодом первого диода, подключенного анодом к катоду второго диода и к первой обкладке первого интегрирующего конденсатора,второй масштабирующий резистор, соединенный первым выводом с анодом третьего диода, подключенного катодом к аноду четвертого диода и к первой обкладке второго интегрирующего конденсатора, отличающийся тем, что, с целью повышения быстродействия и запаса устойчивости, в нем установле- ны блок выделения положительных отклонений управляющего сигнала от сигнала его среднего текущего значения, блок выделения отрицательных отклонений управляющего сигнала от сигнала его среднего текущего значения и сглаживающий фильтр, соединенный входом с выходом

усилителя постоянного тока, а выходом - с первыми входами блока выделения положительных отклонений управляющего сигнала от сигнала его среднего текущего значения и блока выделения отрицательных отклонений управляющего сигнала от сигнала его среднего текущего значения, подключенных вторыми входами к выходу усилителя постоянного тока, а выходами - к вторым обкладкам соответственно второго и первого интегрирующих конденсаторов, первые выводы первого и второго масштабирующих резисторов соединены с инвертирующим входом усилителя постоянного тока, анод второго и катод четвертого диодов соединены с общей шиной регулятора, второй вывод первого масштабирующего резистора является входом Задание регулятора, второй вывод второго масштабирующего резистора - входом Регулируемая величина регулятора, а выход усилителя постоянного тока - выходом регулятора.

значения через повторитель напряжения.

| РЕЛЕЙНОЕ УПРАВЛЯЮЩЕЕ УСТРОЙСТВО | 0 |

|

SU283360A1 |

| Гиперболоидное гнездо | 1972 |

|

SU469177A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Дж | |||

| Талер и М | |||

| Пестель | |||

| Анализ и расчет нелинейных систем автоматического управления | |||

| М.-Л., 1964, с | |||

| Дальномер | 1922 |

|

SU379A1 |

Авторы

Даты

1993-03-30—Публикация

1990-06-07—Подача