. Изобретение относится к области приема сигналов связи при недостатке априорной информации о вероятностных моделях и статистических характеристиках сигналив и помех, поступающих на вход приемного устройства.. .

Целью изобретения является повышение вероятности правильного обнаружения М ортогональных сигналов с априорно неизвестными амплитудой и начальной фазой в гауссовском стационарном шуме с априорно неизвестными дисперсией и корреляционной функцией. Для достижения указанной цели в каждый из М каналов инвариантного приемника дополнительно введены: аналого-циф-. ров ой преобразователь (АЦП), компаратор, сумматор, буферное ЗУ, блрк компараторов, дешифратор, делитель и блок совпадения.

Передаваемые сигналы имеют вид:

00

М

CV

UM едеcosf..t+ VlJ(t) +

+ (р ош 0 t г Swtf .

О, t 0, t т,

где UM - амплитуда, р of начальная фаза; Ј.- закон амплитудной модуляции; ip® - закон фазовой модуляции; со о - несущая частота; 1 1, т.

Правило приема таких ортогональных сигналов в гауссдвскрм стационарном шуме с априорно неизвестными дисперсией и корреляционной функцией включает в себя установление надежности передачи сигнала (безразлично какого именно) и решение о том, какой именно сигнал передан. Правило приема имеет вид:

ел ел Jb ю

(),(iiH при всех k« 1,m j

(0,... ,4kH-10,...;OlecA(

o

.() Я eqex.j k, j -UT,

где величины xi, yi при достаточно большом n (n 2 A f I) пропорциональны косинусной и синусной сб сҐавляющим отклика фильтра, согласованного с сигналом S(t) , f 1, m.

При выполнении условия, записанного в верхней строке выражения (1), принимается решение о надежной передаче сигнала устанавливается факт передачи на приемном конце); при одновременном выполнении условий, записанных во 2-й и 3-й;, строках выражения (1), принимается решение о приеме именно k-ro из m возможных сигналов. То есть предлагаемое устройство, работающее в соответствии с приведенным правилом (1), одновременно решает задачу обнаружения сигнала и задачу распознавания (т.е. какой из m возможных сигналов принят).

Предлагаемое устройство обладает: минимальной полной вероятностью ошибки; независимостью (инвариантностью) вероятности а решения о передаче сигнала, когда в действительности его нет, от априорно неизвестных характеристик шума; наибольшей вероятностью правильного приема при любых отношениях сигнал/шум; оптимальностью (по критерию Неймана-Пирсона) в классе инвариантных к изменениям параметров сигнала и шума устройств, а также устройство свободно от недостатков, присущих прототипу.

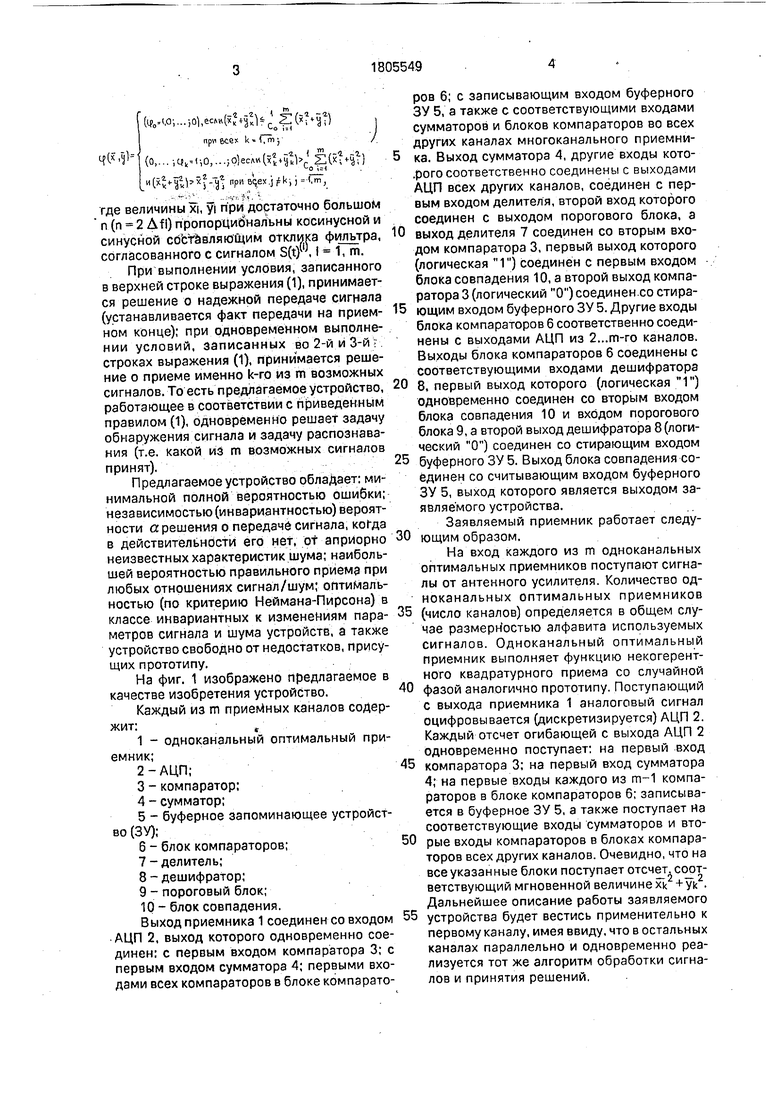

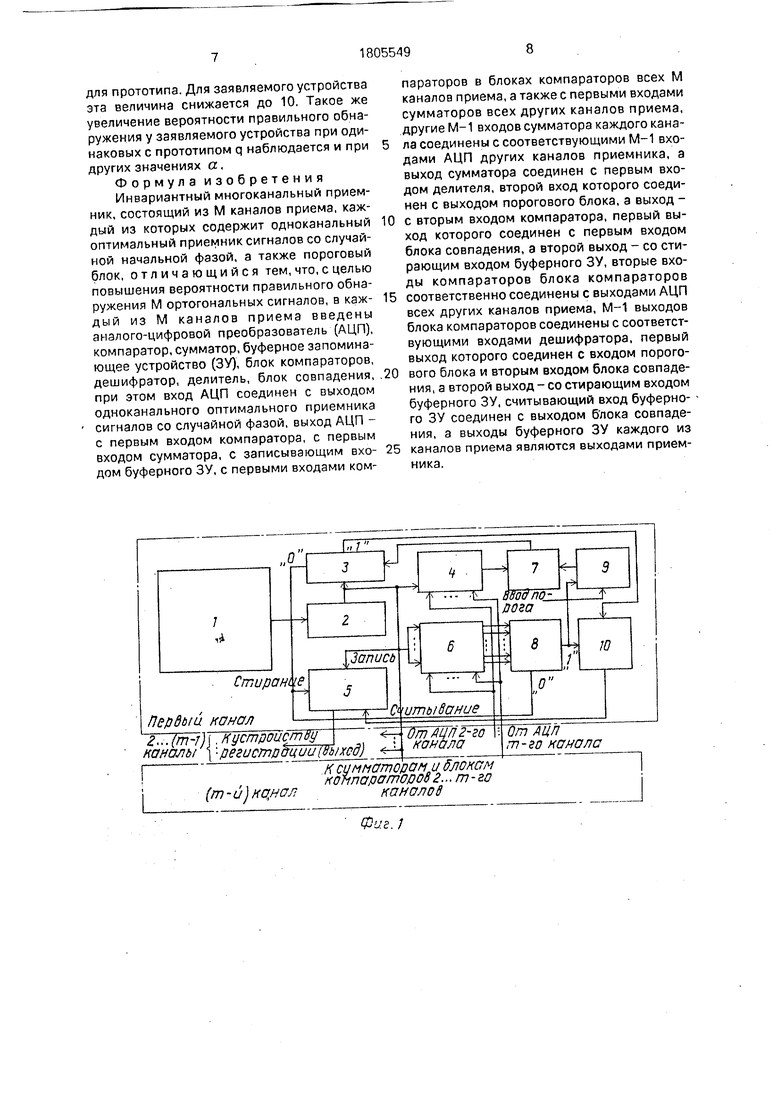

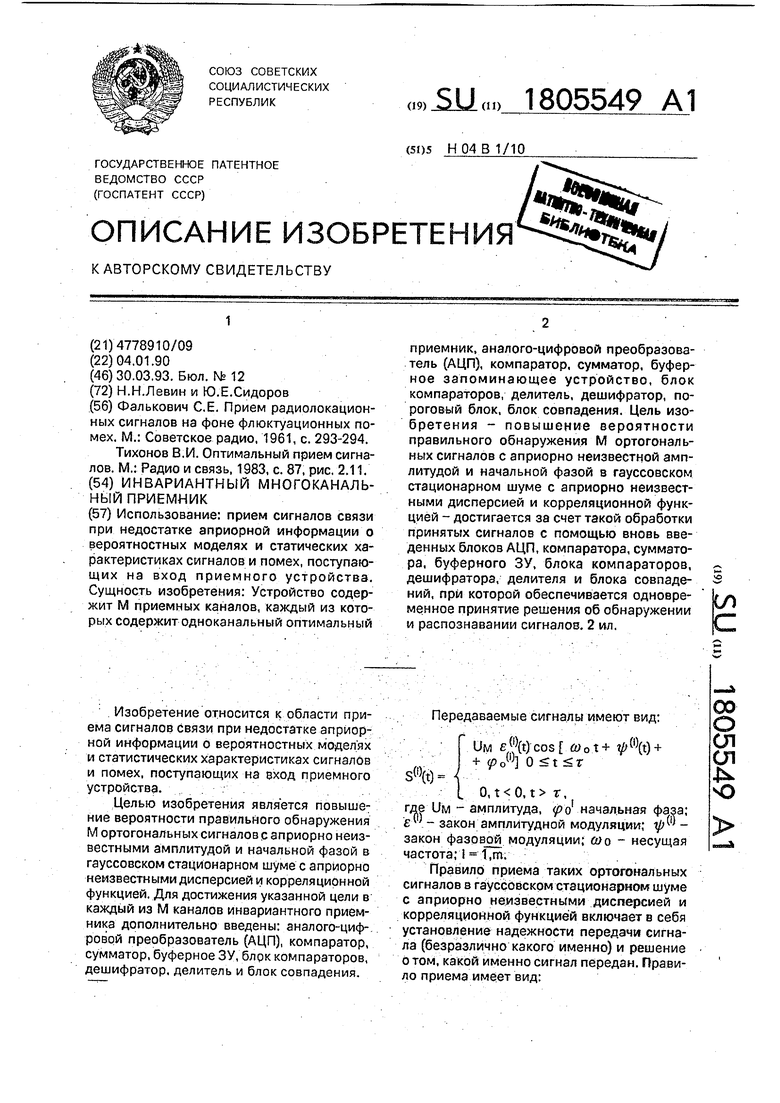

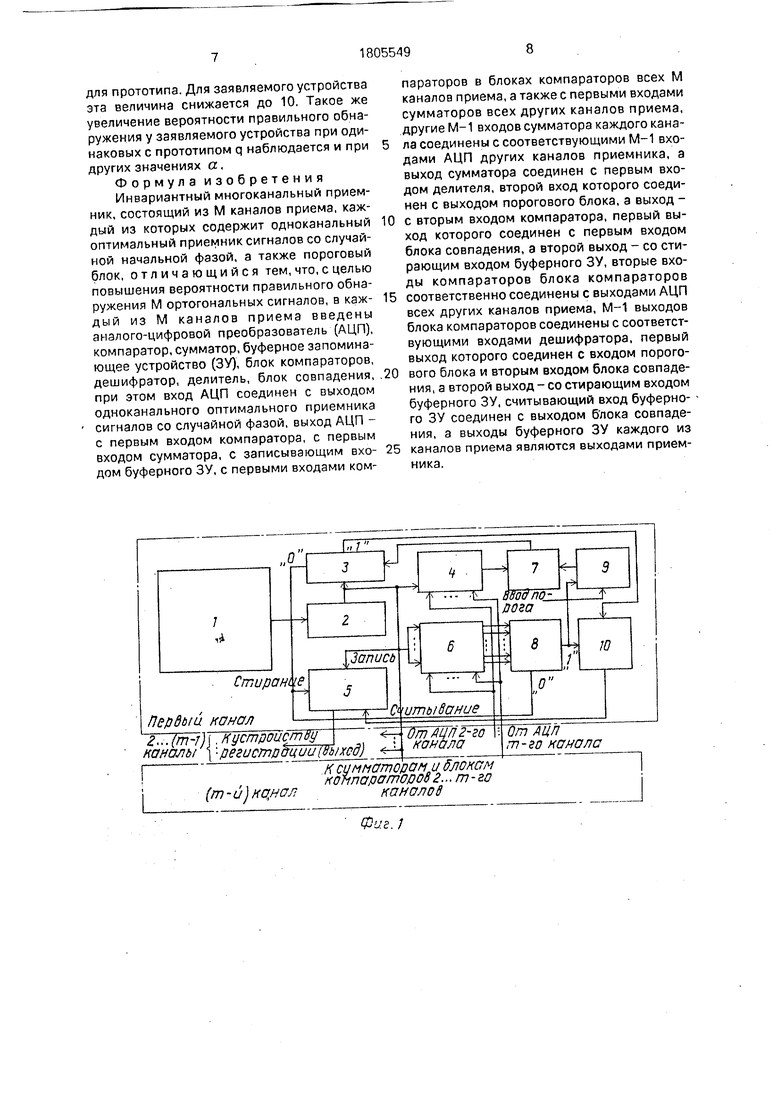

На фиг. 1 изображено предлагаемое в качестве изобретения устройство.

Каждый из m приемных каналов содержит:t

1 - одноканальный оптимальный приемник;

2 - АЦП;

3 - компаратор;

4 - сумматор;

5 - буферное запоминающее устройство (ЗУ);

6 - блок компараторов; 7-делитель;

8 - дешифратор;

9 - пороговый блок;

10 - блок совпадения.

Выход приемника 1 соединен со входом АЦП 2, выход которого одновременно соединен: с первым входом компаратора 3; с первым входом сумматора 4; первыми входами всех компараторов в блоке компараторов 6; с записывающим входом буферного ЗУ 5, а также с соответствующими входами сумматоров и блоков компараторов во всех других каналах многоканального приемника. Выход сумматора 4, другие входы кото- ,рого соответственно соединены с выходами АЦП всех других каналов, соединен с первым входом делителя, второй вход которого соединен с выходом порогового блока, а

выход делителя 7 соединен со вторым входом компаратора 3, первый выход которого (логическая 1) соединён с первым входом блока совпадения 10, а второй выход компаратора 3 (логический О) соединен.со стирающим входом буферного ЗУ 5. Другие входы блока компараторов 6 соответственно соединены с выходами АЦП из 2...т-го каналов. Выходы блока компараторов 6 соединены с соответствующими входами дешифратора

8, первый выход которого (логическая 1) одновременно соединен со вторым входом блока совпадения 10 и входом порогового блока 9, а второй выход дешифратора 8 (логический О) соединен со стирающим входом

буферного ЗУ 5. Выход блока совпадения соединен со считывающим входом буферного ЗУ 5, выход которого является выходом заявляемого устройства.

Заявляемый приемник работает следующим образом.

На вход каждого из m одноканальных оптимальных приемников поступают сигналы от антенного усилителя. Количество одноканальных оптимальных приемников

(число каналов) определяется в общем случае размерностью алфавита используемых сигналов. Одноканальный оптимальный приемник выполняет функцию некогерентного квадратурного приема со случайной

фазой аналогично прототипу. Поступающий с выхода приемника 1 аналоговый сигнал оцифровывается (дискретизируется) АЦП 2. Каждый отсчет огибающей с выхода АЦП 2 одновременно поступает: на первый вход

компаратора 3; на первый вход сумматора 4; на первые входы каждого из т-1 компараторов в блоке компараторов 6; записывается в буферное ЗУ 5, а также поступает на соответствующие входы сумматоров и вторые входы компараторов в блоках компараторов всех других каналов. Очевидно, что на все указанные блоки поступает отсчет, соответствующий мгновенной величине Xk +7k2. Дальнейшее описание работы заявляемого

устройства будет вестись применительно к первому каналу, имея ввиду, что в остальных каналах параллельно и одновременно реализуется тот же алгоритм обработки сигналов и принятия решений.

тами остальных каналов, т.е. проверка неравенства хг + У1

На другие входы сумматора 4 поступают мгновенные отсчеты xi2 + yi2 с выходов АЦП 2... m-ro каналов, которые одноврейен- но поступают и на вторые входы соответствующих компараторов в блоке компараторов 6. В блоке компараторов 6, таким образом, происходит сравнение отсчета первого канала с аналогичными отсчез. реализуется У12 xj2 + 7j2. Если во всех компараторах блока 6 выполняется условие А В (т.е. отсчет первого канала больше отсчетов любого другого канала), то на выходах всех компараторов блока б образуются сигналы логическая 1. В результате на выходе блока 6 образуется кодированный сигнал все 1, который является разрешенным для дешифратора 8. Дешифратор 8 декодирует сигнал все 1 и на одном из его выходов появляется сигнал логическая 1. Этот сигнал поступает на считывающий вход порогового блока 9 и, одновременно, на один из входов блока совпадения 10.

В пороговом блоке 9 заранее записывается в цифровой форме рассчитанное значение порога Со для достижения заданных вероятностных характеристик приема информации. Это значение по сигналу от дешифратора 8 считывается в делитель 1 в качестве делителя. В качестве делимого в делитель 7 поступает двоичное число с выхода сумматора 4. Не трудно убедиться, что это число представляет собой значение выm „ о

ражения 2( +yi ). Результат деления это-

го числа на значение порога (Со) поступает на второй вход компаратора 3, где происходит его сравнение с величиной ранее записанного отсчета xi + yi . Если выполняется условие А В (т.е. отсчет в первом канале больше частного отделения суммы всех отсчетов, взятых в данный момент времени в других каналах, на заданное значение порога), что следует из выражения + yk2

1 m „ „

2 (xi + у, ), то на одном из выходов

Со | 1

компаратора 3 формируется сигнал логическая 1, который поступает на другой вход блока совпадения 10. Таким образом, при одновременном выполнении условий;

xk2 + yk2 -pJ- 2 ( + у,2)

Lo i 1 и

-9-99 9

Xk + yk i + yj (где k 1 для первого канала).

0

5

0

на оба входа блока совпадения 10 поступят сигналы логическая 1. В этом случае на выходе блока совпадения 10 формируется сигнал, который поступает на считывающий вход буферного ЗУ 5 и отсчет, ранее записанный в нем, считается в регистрирующее устройство для дальнейшего использования.

В том случае, если условие xi2 + xj + yj не выполняется, на выходе блока компараторов 6 появится кодовая комбинация, отличная от комбинации все 1. Естественно, что в этом случае дешифратор 8 не дешифрирует эту комбинацию и на одном из его выходов появится сигнал логический О, который поступает на стирающий вход буферного ЗУ 5. Аналогичным образом, если в компараторе 3 не выполнится условие А В (т.е. не выполняется неравенство

- - 2

хГ + УГ

J Со,

лт.2 , л.2

2 (xi + yi ), то на одном из

5

0

5

0

5

0

5

выходов компаратора 3 формируется сигнал логический О, который также поступает на стирающий вход буферного ЗУ 5. Синхронно с первым каналом аналогичным образом работают устройства и в остальных т-1 каналах заявляемого устройства.

Блоки заявляемого устройства, реализующие его основные отличительные признаки, выполняются на стандартных элементах цифровой техники: компаратор 3 и компараторы в блоке компараторов б - в виде устройств сравнения кодов; сумматор

4 - в виде счетчика импульсов; буферное ЗУ

5 - в виде регистра памяти со стиранием при . считывании; дешифратор 8 - в виде дешифратора кодовых комбинаций; АЦП 2; делитель 7 - на элементах логической арифметики; блок совпадения 10 - в виде схемы И; пороговый блок - в виде регистра памяти без стирания при считывании.

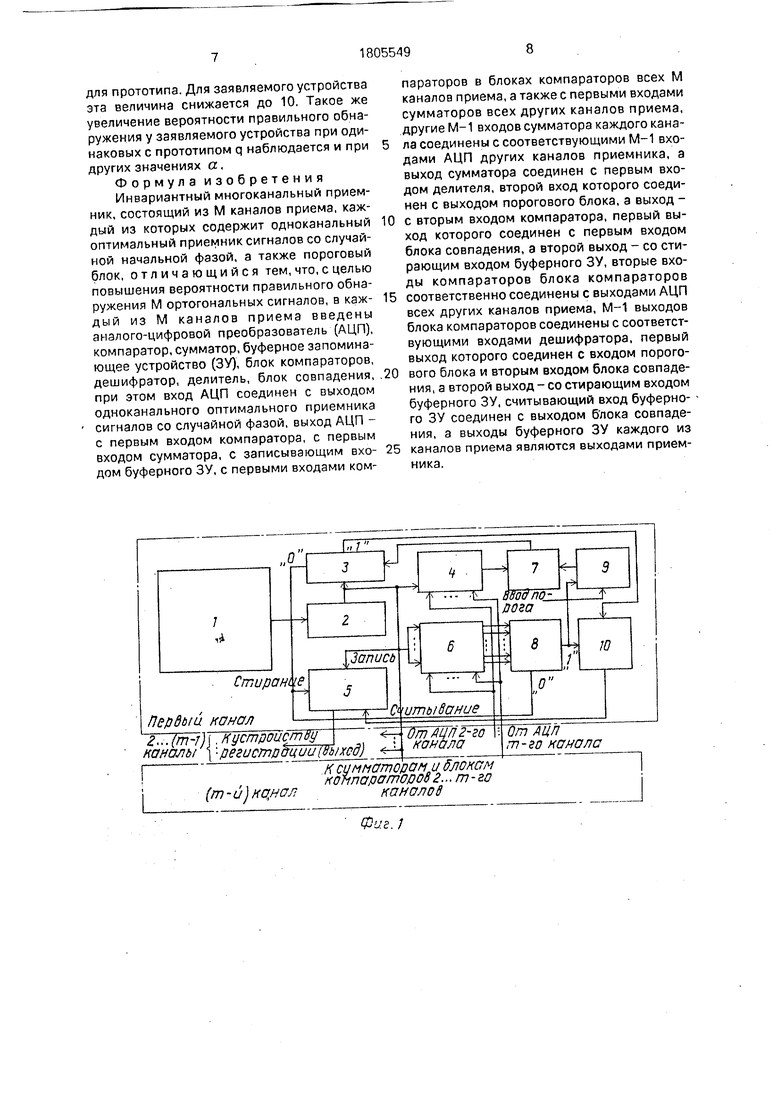

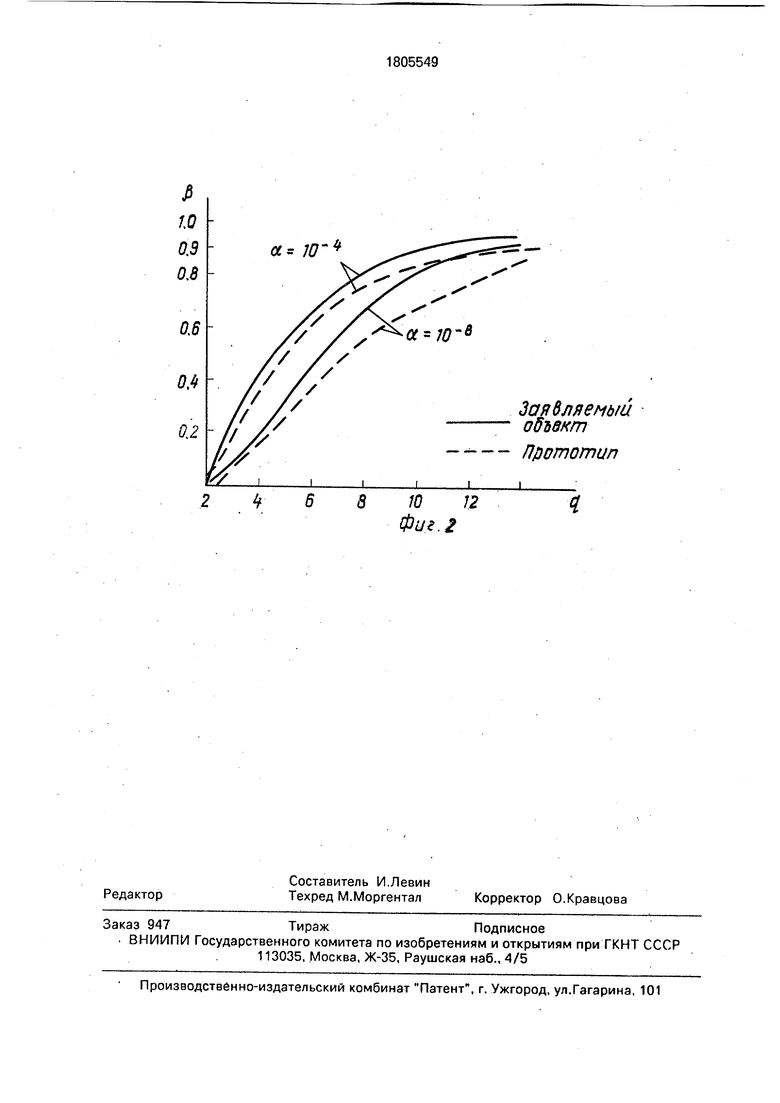

Технико-экономическая эффективность предлагаемого инвариантного многоканального приемника заключается в следующем. Одинаковая с прототипом вероятность правильного приема (обнаружения)/ достигается при меньших отношениях сигнал/шум на входе приемника (см. фиг. 2). Расчеты проводились с помощью таблиц распределения Релея-Райса. Значения вероятности ложного решения «принимались равными 10 и 10 при одном сигнале вида DM cos( + if} + } на фоне гауссов- ской стационарной помехи. Заявляемый объект в этих расчетах оценивался только как обнаружитель (верхняя строка в выражении 1). Из фиг. 2 видно, например, что при а- для достижения /3 0,9 необходимо иметь отношение сигнал/шум q. равное 12,5

для прототипа. Для заявляемого устройства эта величина снижается до 10, Такое же увеличение вероятности правильного обнаружения у заявляемого устройства при одинаковых с прототипом q наблюдается и при других значениях а.

Формула изобретения Инвариантный многоканальный приемник, состоящий из М каналов приема, каждый из которых содержит одноканальный оптимальный приемник сигналов со случайной начальной фазой, а также пороговый блок, отличающийся тем, что, с целью повышения вероятности правильного обнаружения М ортогональных сигналов, в каждый из М каналов приема введены аналого-цифровой преобразователь (АЦП), компаратор, сумматор, буферное запоминающее устройство (ЗУ), блок компараторов, дешифратор, делитель, блок совпадения, при этом вход АЦП соединен с выходом одноканального оптимального приемника сигналов со случайной фазой, выход АЦП - с первым входом компаратора, с первым входом сумматора, с записывающим входом буферного ЗУ, с первыми входами компараторов в блоках компараторов всех М каналов приема, а также с первыми входами сумматоров всех других каналов приема, другие М-1 входов сумматора каждого кана5 ла соединены с соответствующими М-1 входами АЦП других каналов приемника, а выход сумматора соединен с первым входом делителя, второй вход которого соединен с выходом порогового блока, а выход 0 с вторым входом компаратора, первый выход которого соединен с первым входом блока совпадения, а второй выход - со стирающим входом буферного ЗУ, вторые входы компараторов блока компараторов

5 соответственно соединены с выходами АЦП всех других каналов приема, М-1 выходов блока компараторов соединены с соответствующими входами дешифратора, первый выход которого соединен с входом порого0 вого блока и вторым входом блока совпадения, а второй выход-со стирающим входом буферного ЗУ, считывающий вход буферного ЗУ соединен с выходом блока совпадения, а выходы буферного ЗУ каждого из

5 каналов приема являются выходами приемника.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство приема сложных сигналов | 1989 |

|

SU1786664A1 |

| ЦИФРОВОЙ СОГЛАСОВАННЫЙ ФИЛЬТР СИГНАЛОВ С ДИСКРЕТНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1992 |

|

RU2114514C1 |

| УСТРОЙСТВО НАЧАЛЬНОЙ СИНХРОНИЗАЦИИ В СЕТЯХ С КОДОВРЕМЕННЫМ УПЛОТНЕНИЕМ КАНАЛОВ | 2008 |

|

RU2416168C2 |

| УСТРОЙСТВО КОМПЕНСАЦИИ ПОМЕХ | 1994 |

|

RU2097921C1 |

| Устройство компенсации в приемнике частотной расстройки, возникающей в передатчике и приемнике при передаче-приеме фазокодоманипулированных сигналов | 2020 |

|

RU2741066C1 |

| Многоканальный приемник с кодовым разделением каналов для приема сигналов с квадратурной m-ичной амплитудно-инверсной модуляцией | 2017 |

|

RU2669371C1 |

| ФАЗОВЫЙ ПЕЛЕНГАТОР | 2011 |

|

RU2458355C1 |

| Устройство третьей решающей схемы ускоренного поиска и эффективного приема широкополосных сигналов | 2020 |

|

RU2766859C1 |

| Устройство синхронизации приемника многочастотных сигналов | 1984 |

|

SU1185627A1 |

| Устройство для стабилизации средней частоты шумовых выбросов над пороговым уровнем | 1980 |

|

SU902269A1 |

Использование: прием сигналов связи при недостатке априорной информации о вероятностных моделях и статических характеристиках сигналов и помех, поступающих на вход приемного устройства. Сущность изобретения: Устройство содержит М приемных каналов, каждый из которых содержит одноканальный оптимальный приемник, аналого-цифровой преобразователь (АЦП), компаратор, сумматор, буферное запоминающее устройство, блок компараторов, делитель, дешифратор, пороговый блок, блок совпадения. Цель изобретения - повышение вероятности правильного обнаружения М ортогональных сигналов с априорно неизвестной амплитудой и начальной фазой в гауссовском стационарном шуме с априорно неизвестными дисперсией и корреляционной функцией - достигается за счет такой обработки принятых сигналов с помощью вновь введенных блоков АЦП, компаратора, сумматора, буферного ЗУ, блока компараторов, дешифратора, делителя и блока совпадений, при которой обеспечивается одновременное принятие решения об обнаружении и распознавании сигналов. 2 ил. ел С

(т-7). к устройству +. каналы -регистрации(выход)

к сумматорам и блокам

компараторов 2...т-го

каналов

Фиг. /

От АЦП 2-го -. канала

От АЦП

т-so канапе

- J

8

Ю 12 Фи. 2

| Фалькович С.Е | |||

| Прием радиолокационных сигналов на фоне флюктуационных помех | |||

| М.: Советское радио, 1961, с | |||

| ПРИСПОСОБЛЕНИЕ ДЛЯ ПОДАЧИ УГЛЯ В ТЕНДЕР ПАРОВОЗА | 1920 |

|

SU293A1 |

| Тихонов В.И | |||

| Оптимальный прием сигналов | |||

| М.: Радио и связь, 1983, с | |||

| Торфодобывающая машина с вращающимся измельчающим орудием | 1922 |

|

SU87A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1993-03-30—Публикация

1990-01-04—Подача