Изобретение относится к области автоматики и вычислительной техники и может быть использовано для вывода информации из ЭВМ.

Цель изобретения - повышение быстродействия устройства.

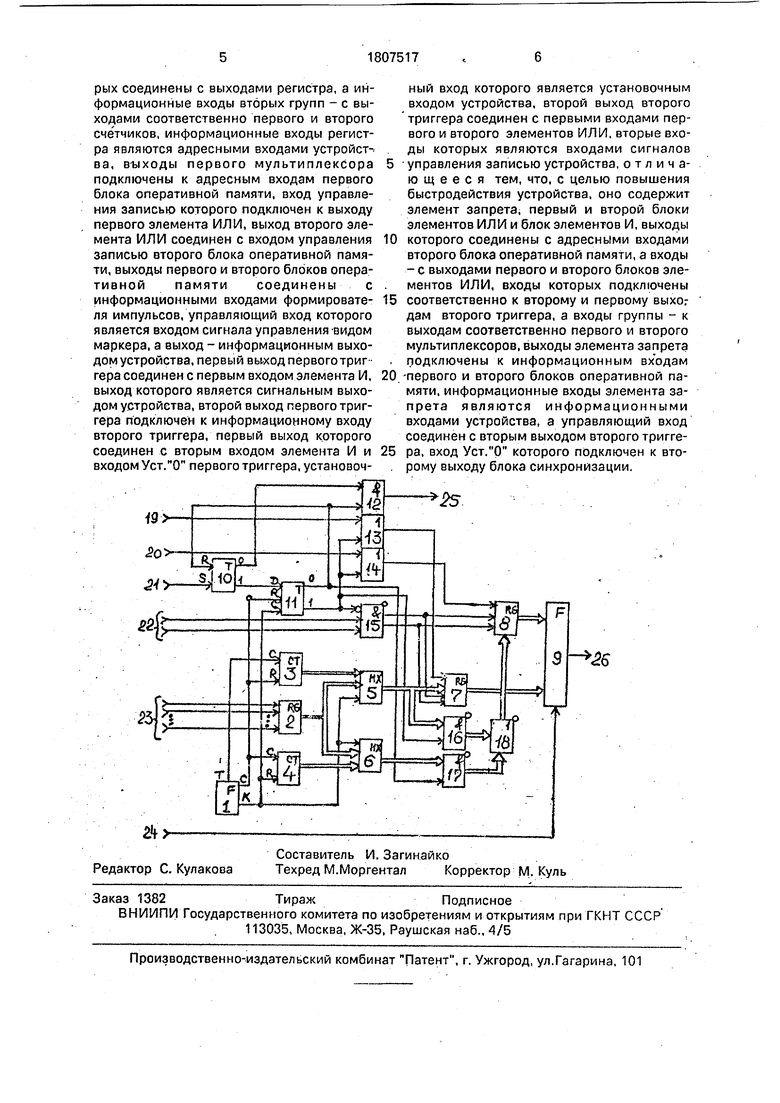

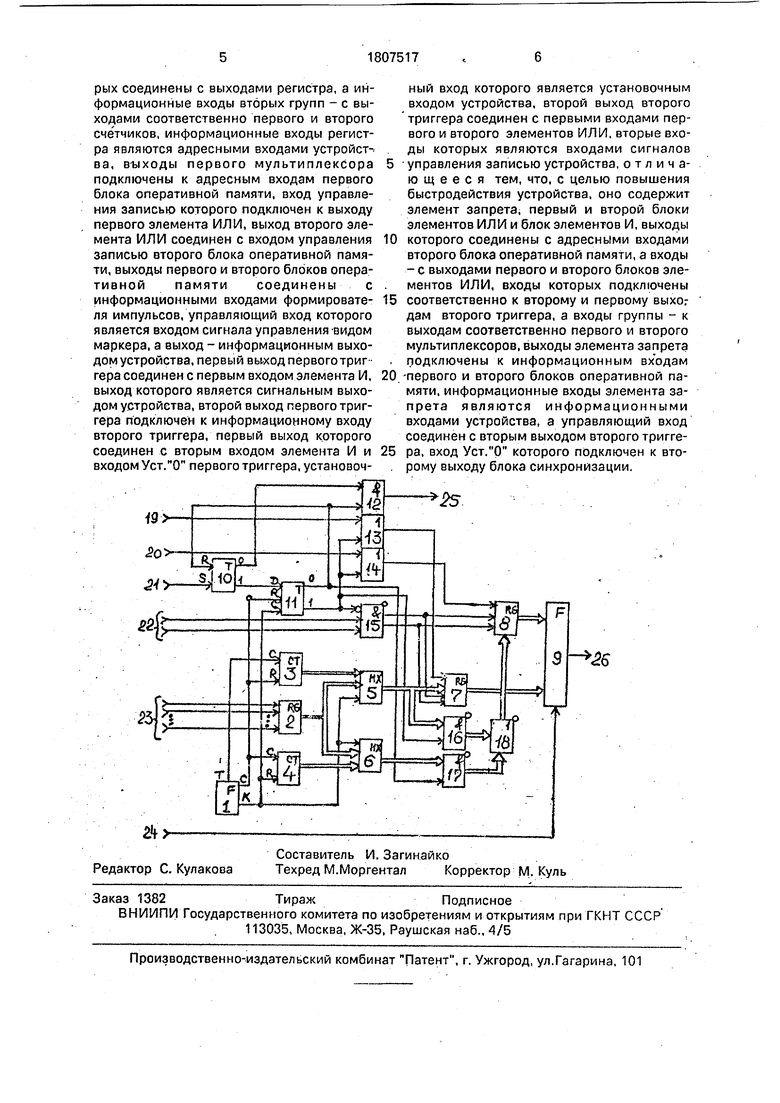

Н а чертеже п редста влена фу н кционал ь- ная схема устройства.

Устройство содержит блок 1 синхронизации, регистр 2, счетчики 3 и 4, мультиплексоры 5 и 6, блок 7 и 8 оперативной памяти, формирователь 9 импульсов, триггеры 10 и 11, элемент 12 И, элементы 13 и 14 ИЛИ, элемент 15 запрета, блоки 16 и 17элементов ИЛИ. блок 18 элементов И.

Позициями 19 и 20 обозначены входы сигналов управления записью устройства, 21 - установочный вход, 22 - информационные входы, 23 - адресные входы, 24 - вход сигнала управления видом маркера, 25 - сигнальный выход, 26 - информационный выход устройства.

Устройство работает следующим образом.

Устройство формирует на экране телевизионного индикатора (на чертеже не показан) маркер ь виде прямоугольника или взаимно перпендикулярных линий в площади этого прямоугольника. Для формирования сигнала подсвета, поступающего на видеовход телевизионного индикатора, необходимо выделить точки растра, составляющие отображаемый обьект.

Для каждой точки телевизионного растра возможны три состояния, характеризующие данную точку: точка принадлежит прямоугольной форме, точка принадлежит взаимно перпендикулярным линиям, точка не принадлежит ни одному из отображаемых объектов.

Таким образом, для кодирования трех состояний каждой точки растра необходимы два разряда: 01 - для точек, составляющих прямоугольную фигуру; 10 - для точек, составляющих взаимно-перпендикулярныб линии; 00 - для точек, не принадлежащих ни одному из отображаемых объектов.

in

00

о ч ел

J

Информация о точках растра в закодированном виде заносится и хранится в блоках 7 (ось X) и 8 (ось Y) по адресам, соответствующим положению точек на экране ЭЛТ индикатора. При отображении считываемой из блоков 7 и 8 код поступает на логику формирования сигнала подсвета прямоугольных фигур и взаимно перпендикулярных линий в формирователе 9.

Предварительно устройство переводится в исходное состояние. Для этого сигналом на входе 21 триггер 10 устанавливается в 1. Сигнал кадрового синхроимпульса с третьего выхода блока 1 поступающий на синхровход триггера 11 переписывает в него единичное состояние триггера 10. В результате этого на входы управления записью блоков 7 и 8 через элементы 13,14 ИЛИ соответственно поступает сигнал, разрешающий запись нулевого кода по адресам, генерируемым счетчиками 3 и 4, работающими в режиме сканирования информации. Сигнал уровня О с выхода триггера 11 поступает на вход Уст.0 триггера 10 и сбрасывает его , что приводит к появлению на входе элемента 12 И единичного сигнала. Следующий сигнал кадрового синхроимпульса устанавливает триггер 11. в О. После этого:,на выходе элемента 12 И появляется сигнал с уровнем 1, который поступает на вход 25 в виде сигнала окончания очистки оперативной памяти устройст- ва и означает, что все ячейки памяти блоков 7 и 8 обнулены. Таким образом, устройство находится в исходном состоянии. :

При построении взаимно перпендикулярных линий на двухразрядную шину входов 22 выставляется код 10 и в регистр 2 по шине адреса входов 23 заносится значение., соответствующее координате X точек, составляющих вертикальный отрезок.

По сигналу во время обратного хода по кадру, переключающему адресные входы блока 7 через мультиплексор 5 на входы регистра 2, управляющим сигналом на входе 19 осуществляется запись кода 10 в блок 7. Запись кода 10 в блок 8 происходит аналогично, по управляющему сигналу на входе 20.

Затем на двухразрядную шину данных входов 22 выставляется вход 01и для построения прямоугольной фигуры. По сигналу готовности код 01 точек, составляющих два вертикальных отрезка, записывается в блок 7 по адресам, соответствующим координатам этих точек по оси X. Запись кода 01 точек, составляющих два горизонтальных отрезка, в блок 8 осуществляется аналогично по адресам, соответствующим координатам этих точек по оси Y.

При отображении информации во время движения луча по строке тактовые импульсы с выхода блока 1 синхронизации, соответствующие каждой отображаемой точке, поступают на вход счетчика 3 (точек в строке). Сигналы с выходов счетчика 3 через мультиплексор 5 поступают на адресные входы блока 7. При переходе на новую строку синхронно с работой отклоняющей системы

строчный синхроимпульс с выхода блока 1 поступает на входУст.0 счетчика 3 и сбрасывает его в нулевое состояние.

Таким образом, при отображении каждой новой строки процесс считывания кода

из блока 7 повторяется.

Считывание кода из блока 8 (оси Y) осуществляется аналогично, причем на адресные входы блока 8 через мультиплексор 6

поступают сигналы с выходов счетчика 4

(строк в кадре), у которого на счетный вход подаются строчные синхроимпульсы, а на вход Уст.0 - кадровые синхроимпульсы с выхода блока 1.

Подробнее, обнуление (очистка) памяти

осуществляется следующим образом. После установки триггера 11 в единичное состояние элементом 15 запрещается передача информации с входов 22 в блоки 7,8, чем достигается возможность внешней системе .

по каналу общего пользования работать с другими устройствами на время самостоятельной (автономной) очистки памяти блоков 7,8.

При этом время очистки памяти сокращается за счет одновременности подачи в блоки 7,8 как команды разрешения записи нулевой информации элемента 15 от триггера 11 через элементы 13, 14, так и адресов счетчика 5 в блок 7 непосредственно, а в

блок 8 - через блоки 16, 18. За одну строку тактовые импульсы блока 1 успевают обнулить все ячейки блоков 7 и 8 одновременно. В изобретении достигается повышение быстродействия устройства, а также расширяется область его применения за счет использования дополнительно в системах с каналом общего пользования.. Формула изобретения Устройство для формирования маркера,.

содержащее первый и второй триггеры, элемент И, первый и второй элементы ИЛИ, блок синхронизации, первый выход которого соединен со счетным входом первого счетчика, второй выход - с входом Уст.0

первого счетчика и счетным входом второго счетчика, третий выход подключен к входу Уст,0 второго счетчика, синхровходу вто- рого триггера и управляющим входам первого и второго мультиплексоров,

информационные входы первых групп которых соединены с выходами регистра, а информационные входы вторых групп - с выходами соответственно первого и второго сче тчиков, информационные входы регистра являются адресными входами устройств ва, выходы первого мультиплексора подключены к адресным входам первого блока оперативной памяти, вход управления записью которого подключен к выходу первого элемента ИЛИ, выход второго элемента ИЛИ соединен с входом управления записью второго блока оперативной памяти, выходы первого и второго блоков оперативной памяти соединены с информационными входами формировате- ля импульсов, управляющий вход которого является входом сигнала управления-видом маркера, а выход - информационным выходом устройства, первый выход первого триг гера соединен с первым входом элемента И, выход которого является сигнальным выходом устройства, второй выход первого триггера подключен к информационному входу второго триггера, первый выход которого соединен с вторым входом элемента И и входом Уст.0 первого триггера, установоч-

ный вход которого является установочным входом устройства, второй выход второго триггера соединен с первыми входами первого и второго элементов ИЛИ, вторые входы которых являются входами сигналов управления записью устройства, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит элемент запрета; первый и второй блоки элементов ИЛИ и блок элементов И, выходы которого соединены с адресными входами второго блока оперативной памяти, а входы

- с выходами первого и второго блоков элементов ИЛИ, входы которых подключены соответственно к второму и первому выхог дам второго триггера, а входы группы - к выходам соответственно первого и второго мультиплексоров, выходы элемента запрета подключены к информационным входам

-первого и второго блоков оперативной памяти, информационные входы элемента запрета являются информационными входами устройства, а управляющий вход соединен с вторым выходом второго триггера, вход Уст.0 которого подключен к второму выходу блока синхронизации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Устройство для формирования маркера | 1987 |

|

SU1444877A1 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| Устройство для формирования маркера | 1988 |

|

SU1541664A2 |

| Запоминающее устройство с многоформатным доступом к данным | 1986 |

|

SU1336108A1 |

| Устройство для отображения информации | 1984 |

|

SU1354182A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1354242A1 |

| Устройство для отображения информации на экране видеоконтрольного блока | 1987 |

|

SU1495780A1 |

| Устройство для ввода информации | 1990 |

|

SU1702382A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1352477A1 |

Использование: область автоматики и вычислительной техники, системы вывода информации из-.ЭВМ. Сущность изобретения: устройство содержит два триггера, один блок синхронизации, один регистр, два счетчика, один элемент И, два элемента ИЛИ, один элемент запрета, два мультиплексора, два блока оперативной памяти, два блока элементов И, один блок элементов ИЛИ, один формирователь импульсов. 1 ил.

| Устройство для формирования маркера | 1987 |

|

SU1444877A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Устройство для формирования маркера | 1988 |

|

SU1541664A2 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1993-04-07—Публикация

1991-03-25—Подача