Изобретение относится к измерительной технике и предназначено для автоматического цифрового измерения электрических параметров асинхронных двигателей при приемо-сдаточных испытаниях.

Целью изобретения является повышение функциональной возможности устройства за счет обеспечения дополнительной функции измерения напряжения сети и фазных токов.

На фиг.1 представлена блок-схема предлагаемого устройства.

Устройство содержит сумматоры 1-9, причем входы сумматоров 1 и 2 соединены с первыми входами сумматоров 3 и 6 и подключены к шинам линейных напряжений UAC и DBC, а вторые входы сумматоров 1 и 2 соединены со вторыми входами сумматоров

5 и 8 и подключены к шинам линейных токов соответственно.

Источник 10 эталонного напряжения, выход которого соединен со вторыми входами сумматоров 3-9, компараторы 11-17, первые входы которых соединены соответственно с выходами сумматоров 3-9, нуль- органа 18, вход которого соединен с шиной напряжения UBC, умножителя 19 частоты, вход которого соединен с выходом нуль-органа 18, логический элемент 20 И, первый вход которого соединен с выходом умножителя 19частоты, функциональный генератор 21 напряжения параболической формы, управляющий вход которого соединен с выходом логического элемента 20 И, а выход - со вторыми входами компараторов 11-17, двоичный счетчик 22, вход которого соединен с выходом логического элемента 20 И, тригге00

-л

ел

XI

ю ю

ры 23-29, причем первый вход триггера 23 соединен с выходом двоичного счетчика 22, а второй вход - с шиной запускающих импульсов, блок 31 обработки и заполнения временных интервалов, входы которых сое динены с выходами триггеров 24-30, первые входы которых соединены с выходами компараторов 11-17, а вторые входы - с выходом логического элемента 20 И, реверсивный счетчик 32 и двоичные счетчики 33- 36, входы которых соединены с выходами блока 31 обработки и заполнения временных интервалов и при этом выходы сумматоров 1 и 2 соединены с первыми входами сумматоров 4 и 7 соответственно, а первый вход сумматора 9 подключен к шине Uic.

Блок обработки и заполнения временных интервалов (фиг.2) содержит дешифратор 37, элемент ИЛИ-НЕ 38, элементы ИЛИ 39-45, элементы И 46-60, элемент И-НЕ 61, генератор 62 опорной частоты, счетчик 63.

Устройство работает следующим образом: преобразуемые сигналы L)Ac(t), UiA(t), UBc(t), UieW пропорциональные линейным напряжениям и фазным токам измеряемой трехфазной цепи, по соответствующим шинам подаются на входы соответствующих сумматоров (см.фиг.1), при этом на выходах сумматоров 1 и 2 формируются сигналы UAc(t)+UiA(t) и UBc(t)+UiB(t), которые поступают на первые входы сумматоров 4 и 7. На вторые входы 3-9 сумматоров от источника 10 эталонного напряжения поступает постоянное напряжение Uo смещения для получения однополярных сигналов. Поэтому на первых входах компараторов 11-17 действуют напряжения, соответственно:

Ui(t)UAc(t}HJo

U2{T)UAc(t)+UiA(t)4Uo

U3(t)UiA(t)+Uo

l)4(t)UBC(t)+Uo (1)

U5(t)UBc(t)+UiB(t)+Uo

U6(t)UlB(t)+Uo

U7(t)Uic(t)+Uo

На вторые входы компараторов 11-17 подается напряжение от функционального генератора 21 напряжения параболической формы, запускаемого выходным сигналом логического элемента 20 И в моменты вре- кТ

-

и

мени Хк

М

При поступлении сигнала Пуск на вход логического элемента 20 И запускают функциональный генератор 21 напряжения параболической формы.

Т

55

kn UBc(tk}+UiB(tkHUof

U.BfrkHJo 2

k2n

Tk6

U62(tk) -L

Kn

В течение шага квантования At -JrTk7 72 u(tk) -j lUicfrkHUo 2

MKn Kn

5

10

15

20

25

30

35

лам времени между элементами запуска функционального генератора 21 и срабатывания компараторов 11-17 соответственно. Эти сигналы подаются на входы блока 31 обработки и заполнения временных интервалов. В результате обработки получаются импульсы длительности:

ATk(Tk2+Tk5HTki+Tk3+Tk4+Tk6) (2) пропорциональной мгновенному значению мощности трехфазной цепи.

Интервалы времени Tk. Ти, Tk3, Tk6. Tk7. ,М в БОЗВИ подвергаются число-импульсному кодированию заполнением их импульсами эталонной частоты f0. Результаты ATk число-импульсного кодирования временных интервалов ATk, пропорциональны мгновенному значению мощности трехфазной цепи и в зависимости от знака этой мощности поступают на шину сложения или вычитания реверсивного счетчика PC.

Результаты Nki f0Tki, Nk2 foTk3, Nk3 foTk6, Nk4 foTk7 число-импульсного кодирования временных интервалов Ти, Ткз, Tk6, Tk пропорциональны мгновенному значению квадратов действующих значений UAc(t), UiA(t), UieW и Uic(t) поступают на соответствующие двоичные счетчики 33-36.

Длительность входных сигналов Ти, Tk2, Tk3, Tk4, Tk5. Tk6, Tk определяются из условия динамической компенсации соответствующих напряжений Ui(t), U2(t), U3(t), U4(t), Us(t), .Uefr), U(t) развертывающим напряжением параболической Un(t)kn VFor ФГ где: Кп - коэффициент развертывающего напряжения.

1 ,. 2,. ч 1

Tki - Ui2(tk}

Кп

kn

40

45

50

55

Tk2 -«k2,

JL t2

Kp

Tk3

UAcftkJ+Uo 2

Кп

U22(tk UAc((tkKU0f

-1 U32(tk)4 UlAfrkJ+Uo 2

knkn

Tk4 U42(tk)4 UBc(tk}+Uof

kfikfi %

U52(tk)

kn UBc(tk}+UiB(tkHUof

U.BfrkHJo 2

k2n

Tk6

U62(tk) -L

Kn

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь активной мощности трехфазной электрической цепи в цифровой код | 1988 |

|

SU1621176A1 |

| Преобразователь активной мощности трехфазной электрической цепи в цифровой код | 1987 |

|

SU1684709A1 |

| Преобразователь активной мощности трехфазной электрической цепи в цифровой код | 1979 |

|

SU855518A1 |

| Способ управления приводом регулирующего органа ядерного реактора и устройство для его осуществления | 1990 |

|

SU1785043A1 |

| МНОГОРЯДНЫЙ ПОДШИПНИК КАЧЕНИЯ И УЗЕЛ ПОДШИПНИКА СТУПИЦЫ КОЛЕСА С УПОМЯНУТЫМ ПОДШИПНИКОМ КАЧЕНИЯ | 2007 |

|

RU2442036C2 |

| БЕСТРАНСФОРМАТОРНЫЙ НЕПОСРЕДСТВЕННЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ | 2018 |

|

RU2691968C1 |

| НЕПОСРЕДСТВЕННЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ БЕСТРАНСФОРМАТОРНЫЙ | 2022 |

|

RU2787121C1 |

| ТРЕХФАЗНЫЙ БЕСТРАНСФОРМАТОРНЫЙ НЕПОСРЕДСТВЕННЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ | 2020 |

|

RU2758443C1 |

| НЕПОСРЕДСТВЕННЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ И НАПРЯЖЕНИЯ | 2021 |

|

RU2784879C1 |

| Способ регулирования напряжения звена постоянного тока преобразователя частоты с широтно-импульсной модуляцией выходного напряжения | 1989 |

|

SU1697225A1 |

Изобретение относится к цифровой электроизмерительной технике и предназначено для преобразования активной мощности линейного напряжения и фазных токов трехфазной электрической цепи в цифровой код. Цель изобретения - расширение функциональных возможностей за счет обеспечения дополнительной функции измерения напряжения сети и фазных токов. Устройство содержит девять сумматоров, семь компараторов, восемь триггеров, источник опорного напряжения, умножитель частоты, элемент И, функциональный генератор напряжения параболической формы, блок обработки и заполнения временных интервалов, один реверсивный счетчик и пять двоичных счетчиков. Новым является введение в устройство дополнительно пяти сумматоров, трех компараторов, трех триггеров, четырех двоичных счетчиков.Раскрыто выполнение блока обработки и заполнение временных интервалов. 1 з.п.ф- лы, 2 ил. ел С

на выходах триггеров 24-30 получаются импульсы соответствующих TKI, Тк2, Ткз. Тк4, TKS, Тке, Тк7 длительности, равной интерваС учетом (1) и (3). а также, что:

P(tk)UAC(tk)U|A(tk)+UBC(tk)UlB(tkHUAc(tk)+

7

На выходах 7, 11,13,14 дешифратора 37 формируются сигналы: cdef, cdef, cdef, cdef,

Длительность этих сигналов соответствует:

T(cdef)lnf(Tk3,Tk4,Tk5)-inf(Tk3,TH,Tk5,Tk6)

T(cdef)inf(Tk3,Tk4,Tk6)-inf(Tk3,Tk ,Tk5,Tk6)

T(cdefHnf(Tk3,Tk4,Tk5)-inf(,Tk4,Tk5,Tk6)

T(cdef)inf(Tk4,Tk5,Tk6)-lnf(Tk3,Tk4,Tk5,Tk6)

Эти сигналы поступают на логический элемент ИЛИ 42, на выходе которого формируется сигнал y cdefvcdef v cdef vcdef

Длительность сигнала у определяется следующим образом;

T(y)(cdef), T(cdef), T(cdef), T(cdef)

И, наконец, на выходе 15 дешифратора 37 формируется сигнал с длительностью T(cdef)inf(Tk3,Tk4,Tk5,Tk6) Полученные на выходах элемента И 47 и элемента ИЛИ 40 сигналы (av b)/ (a A b) и V посредством элементов И 48 и 50 заполняются импульсами частотой fo/12, которые поступают на вторые входы логических элементов И 48 и 50. При этом на выходах этих элементов формируются серии импульсов, количество которых определяется выражением:

N48 -|| ITk1-Tk2l И N50 Т(У)

Сигналь ab и х, поступающие на первые входы элементов И 49 и 51 заполняются импульсами частоты f0/6. На выходах элементов И 49 и 51 также получается серия импульсов/количество которых определяет ° 6

ся выражением: N49

inf(Tk1,Tk2)

fo

2inf(Tici-Tk2)

fo

N51 f T(x) 2T(x)

Посредством логических элементов И 52 и 53 сигналы у и cdef поступающие на первые входы этих элементов, заполняются импульсами с частотами f0/4 и W3, соответственно. Поэтому на выходах элементов И 52 и 53 формируются импульсы с количест8ом№2 Ј Т(у) (у N53 у T(cdef)

4lnfCTk3,Tk4,Tk5.Tk6)

При этом на выходах элементов ИЛИ 43 и 44 получаются:

N44-- N50+N51+N5 +N53

7998

{j{T(v)+2T(x)+3T(y)+4inf(Tk3,Tk4,Tk5,Tk6)

Учитывая, что:

T(v)+2T(x)f3T(y)+4lnf(Tk3,Tk4,Tk5Jk6)Tk3+ Tk4+Tk5+Tk6, для N.M получим:

N44 -|| Tk3+Tk4+Tk5+Tk6

Таким образом, на выходах элемента И 55 и 56 формируются импульсы, количество которых будет определяться следующим образом:

1(Тн+ТК2)- У Tkil

1

N55 npH(Tki+Tk2) О, при (Tki+Tk2) ч

TKI

TKI

20

{| (Tki+Tk2)Тм

N56 при (Tki+Tk2) 6

TKI

О, при

Ткк (Tkl+Tk2)

0

5

0

5

Кроме этого, посредством элементов И 57, 58, 59 и 60 сигналы cdf и g заполняются импульсами частотой f0/12. Тогда на выходах элементов И 57, 58, 59 и 60 получаются импульсы в следующих количествах:

N57 fo/12Tk3

N58 fo/12Tk4 N59 fo/12Tk5 N60 fo/12Tk7

Таким образом, на выходах элементов И 55, 56 получаются последовательные коды, эквивалентные по значению и знаку мгновенной мощности, а на выходах элементов И 57, 58, 59 и 60 мгновенным значениям квадратов действующих значений линейного напряжения и фазных токов.

Импульсы с частотой f0/12, f0/6, fo/4, : fo/З формируются с помощью счетчика/де- 7Гйтёл й763,1 оторый представляет собой набор счетчиков с соответствующими коэффициентами деления частоты.

Импульсы частоты f0 вырабатываются генератором 62 опорной частоты (ГОЧ).

Используя рассмотренный БОЗВИ можно осуществить обработку и заполнение временных интервалов и тем самым реализовать цифровые измерения всех параметров АД одним преобразователем, Таким образом, применение предлагаемого устройства позволяет измерять все необходимые электрические параметры трехфазной электрической цепи, что позволяет расширить его функциональные возможности и область применения.

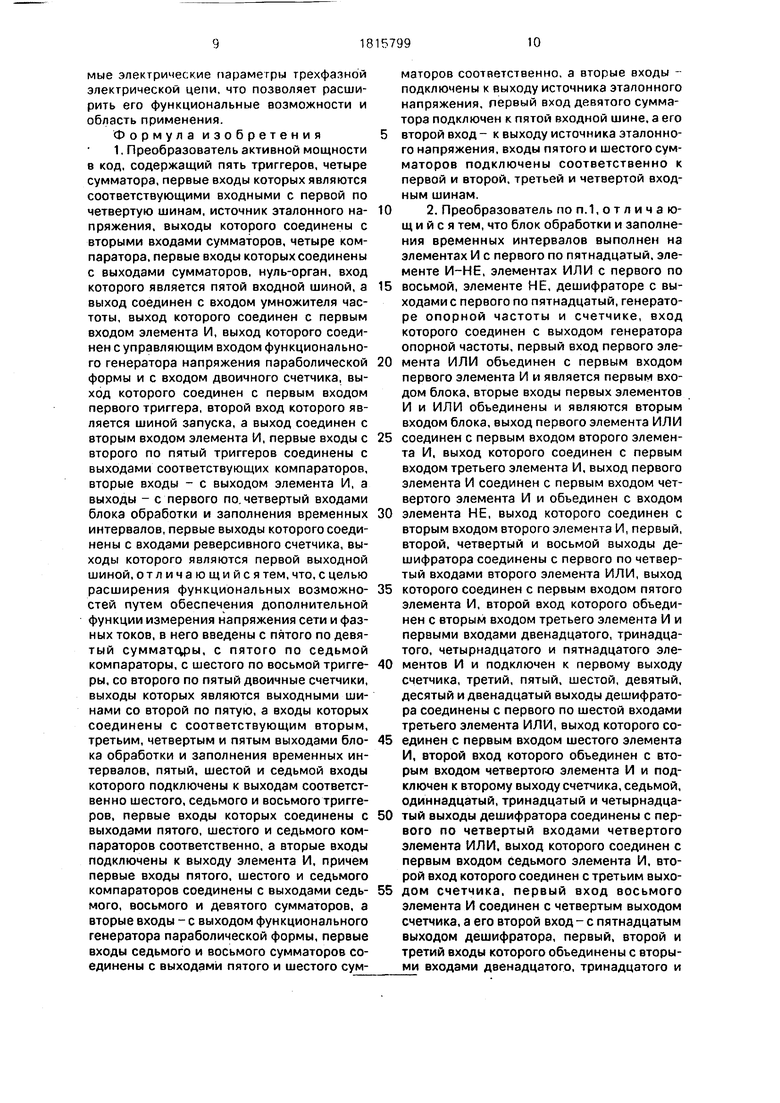

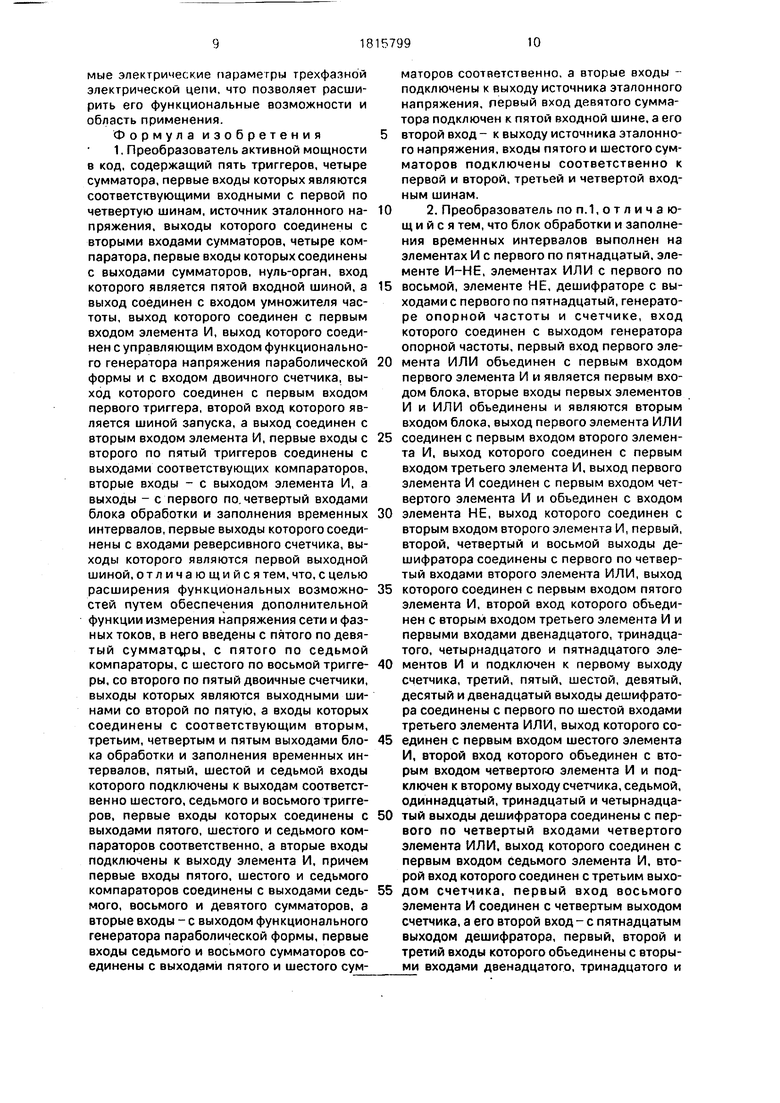

Формула изобретения 1, Преобразователь активной мощности в код, содержащий пять триггеров, четыре сумматора, первые входы которых являются соответствующими входными с первой по четвертую шинам, источник эталонного напряжения, выходы которого соединены с вторыми входами сумматоров, четыре компаратора, первые входы которых соединены с выходами сумматоров, нуль-орган, вход которого является пятой входной шиной, а выход соединен с входом умножителя частоты, выход которого соединен с первым входом элемента И, выход которого соединен с управляющим входом функционального генератора напряжения параболической формы и с входом двоичного счетчика, выход которого соединен с первым входом первого триггера, второй вход которого является шиной запуска, а выход соединен с вторым входом элемента И, первые входы с второго по пятый триггеров соединены с выходами соответствующих компараторов, вторые входы - с выходом элемента И, а выходы - с первого по. четвертый входами блока обработки и заполнения временных интервалов, первые выходы которого соединены с входами реверсивного счетчика, выходы которого являются первой выходной шиной, отличающийся тем, что, с целью расширения функциональных возможностей путем обеспечения дополнительной функции измерения напряжения сети и фазных токов, в него введены с пятого по девятый сумматоры, с пятого по седьмой компараторы, с шестого по восьмой триггеры, со второго по пятый двоичные счетчики, выходы которых являются выходными шинами со второй по пятую, а входы которых соединены с соответствующим вторым, третьим, четвертым и пятым выходами блока обработки и заполнения временных интервалов, пятый, шестой и седьмой входы которого подключены к выходам соответственно шестого, седьмого и восьмого триггеров, первые входы которых соединены с выходами пятого, шестого и седьмого компараторов соответственно, а вторые входы подключены к выходу элемента И, причем первые входы пятого, шестого и седьмого компараторов соединены с выходами седьмого, восьмого и девятого сумматоров, а вторые входы - с выходом функционального генератора параболической формы, первые входы седьмого и восьмого сумматоров соединены с выходами пятого и шестого сумматоров соответственно, а вторые входы - подключены к выходу источника эталонного напряжения, первый вход девятого сумматора подключен к пятой входной шине, а его

второй вход - к выходу источника эталонного напряжения, входы пятого и шестого сумматоров подключены соответственно к первой и второй, третьей и четвертой входным шинам.

0 2. Преобразователь по п.1, о т л и ч а ю- щ и и с я тем, что блок обработки и заполнения временных интервалов выполнен на элементах И с первого по пятнадцатый, элементе И-НЕ, элементах ИЛИ с первого по

5 восьмой, элементе НЕ, дешифраторе с выходами с первого по пятнадцатый, генераторе опорной частоты и счетчике, вход которого соединен с выходом генератора опорной частоты, первый вход первого эле0 мента ИЛИ объединен с первым входом первого элемента И и является первым входом блока, вторые входы первых элементов И и ИЛИ объединены и являются вторым входом блока, выход первого элемента ИЛИ

5 соединен с первым входом второго элемента И, выход которого соединен с первым входом третьего элемента И, выход первого элемента И соединен с первым входом четвертого элемента И и объединен с входом

0 элемента НЕ, выход которого соединен с вторым входом второго элемента И, первый, второй, четвертый и восьмой выходы дешифратора соединены с первого по четвертый входами второго элемента ИЛИ, выход

5 которого соединен с первым входом пятого элемента И, второй вход которого объединен с вторым входом третьего элемента И и первыми входами двенадцатого, тринадцатого, четырнадцатого и пятнадцатого эле0 ментов И и подключен к первому выходу счетчика, третий, пятый, шестой, девятый, десятый и двенадцатый выходы дешифратора соединены с первого по шестой входами третьего элемента ИЛИ, выход которого со5 единен с первым входом шестого элемента И, второй вход которого объединен с вторым входом четвертого элемента И и подключен к второму выходу счетчика, седьмой, одиннадцатый,тринадцатый и четырнадца0 тый выходы дешифратора соединены с первого по четвертый входами четвертого элемента ИЛИ. выход которого соединен с первым входом седьмого элемента И, второй вход которого соединен с третьим выхо5 дом счетчика, первый вход восьмого элемента И соединен с четвертым выходом счетчика, а его второй вход- с пятнадцатым выходом дешифратора, первый, второй и третий входы которого объединены с вторы- ми входами двенадцатого, тринадцатого и

четырнадцатого элементов И соответственно и являются третьим, четвертым и шестым входами блока, выходы третьего и четвертого элементов И соединены с первым и вторым входами пятого элемента ИЛИ, выход которого соединен с первыми входами элемента И-НЕ, седьмого элемента ИЛИ и десятого элемента И, выходы пятого, шестого, седьмого и восьмого элементов И соединены с первого по четвертый входами шестого элемента ИЛИ, выход которого соединен с вторыми входами элемента И-НЕ, седьмого элемента ИЛИ и первым входом одиннадцаб с .

того элемента И, выходы элемента И-НЕ и седьмого элемента ИЛИ соединены с первым и вторым входами девятого элемента И, выход которого соединен с вторыми входами десятого и одиннадцатого элементов И, при этом четвертый вход дешифратора является пятым входом блока, седьмым входом которого является второй вход пятнадцатого элемента И, а выходы с десятого по пятнадцатый элементов И являются соответствующими первым, вторым, третьим, четвертым и пятым выходами блока.

| Аракелов М.А., Манагадзе И.П | |||

| Автоматическая система допускового контроля мощности и тока при производстве электродвигателей | |||

| Измерительная техника, 1977, № 1 | |||

| Преобразователь активной мощности трехфазной электрической цепи в цифровой код | 1988 |

|

SU1621176A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1993-05-15—Публикация

1990-12-04—Подача