Изобретение относится к вычислительной технике и может найти применение в различных системах для ввода информации в ЭВМ от аналоговых датчиков . Известны устройства для сопряжения вычислительной машины с аналоговыми датчиками, содержащие узлы запуска преобразователя, включающие ис точник образцового напряжения, масштабирующий усилитель и реле времени, ксзмпараторы, генераторы эталонных напряжений, формирователи импуль сов, шифратор номера датчика, узел согласования, коммутаторы, выходной регистр и счетчик времени l. Недостатки этих устройств состоят в больших аппаратурных затратах и низ ком быстродействии. Наиболее близким к предлагаемому по технической сущности является уст ройство для ввода информации от аналогового датчика, содержащее четыре элемента коммутации и выходной преобразователь Время-код, управляющие входы которых подключены к соответствующим выходам узла синхронизации, первьм входом соединенного с вы ходом генератора тактовых импульсов инф01 лационные входы первых трех эле ментов 1-оммутации соединены соответственно со входом устройства, выходом источника образцового напряжения и нулевой шиной, а выходы - через соответствующие ограничительные резисторы с инвертирующим входом первого операционного усилителя и через интегрирующий конденсатор с инвертирующим входом второго операционного усилителя и выходом первого операционного усилителя, прямьм входом подк.гаоченного через запоминаю иий конденсатор к нулевой шине, а через «етвертый элемент коммутации - к втррсму входу узла синхронизации и выходу втррого операционного усилителя, прям1л входом соединенного с нулевой шиной. Формируемый на выходе преобразователя Вретля-код код пропорционален величине входного напряжения f2. Недостатками данного устройства являются низкая точность, обусловленная наличием коммутирующих элементов в цепях входного иобразцового напряжения и общей нулевой шины, а также низкое быстродействие, определяемое наличием второго такта преобразованияЦель изобретения - повыдение точ/10СТИ и быстродействия устройства.

Поставленная цель достигается тем, что устройство, содержащее источник образцового напряжения, два ограничительных резистора, первый и второй элементы коммутации, подключенные управляющими входами к первому выходу узла синхронизации, второй выход которого соединен с управляющим входом третьего элемента коммутации, третий выход - через узел преобразования временных интервалов в код с выходом устройства, а первый вход с выходом генератора тактовых импульсов, а второй вход - через третий элемент коммутации с прямым входом первого операционного усилителя, инвертирующий вход которого соединен через первый интегрирующий конденсатор с инвертирукицим входом второго операционного усилителя, прямым входом и: выходом подключенного соответственно к нулевой шине и второму входу узла синхронизации, а инвертирующим -входом - к выходу первого операционного усилителя, прямой вход которого соединен через первый запоминающий конденсатор с прямым входом второго операционного усилителя, введены вторые интегрирующий и запоминающий конденсаторы и третий и четвертый операционные усилители, причем выход источника образцового напряжения через первый ограничительный -резистор подключен к инвертирующему входу первого операционного усилителя, выход третьего, операционного/ усилителя соединен с инвертирующим входом четвертого операционного усилителя и через второй интегрирующий конденсатор со входом первого элемента коммутации, подключенного выходом с инвертирующим входом первого операционного усилителя, инвертирующий вход третьего операционного усилителя подключен ко входу первого элемента коммутации и через второй ограничительный резистор ко входу устройства, а прямой вход через второй запоминающий конденсатор - к прямым входам втррого и четвертого операционных усилителей, выход которого через второй элемент коммутации соединен с прямым входом третьего операционного усилителя.

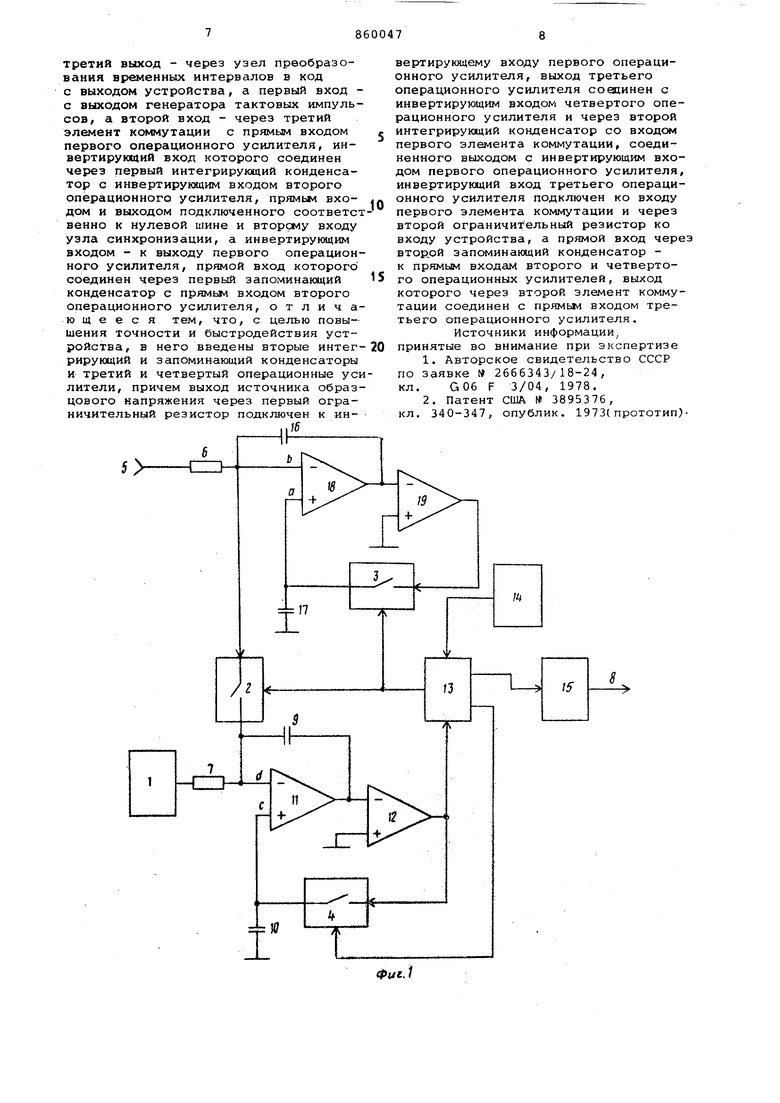

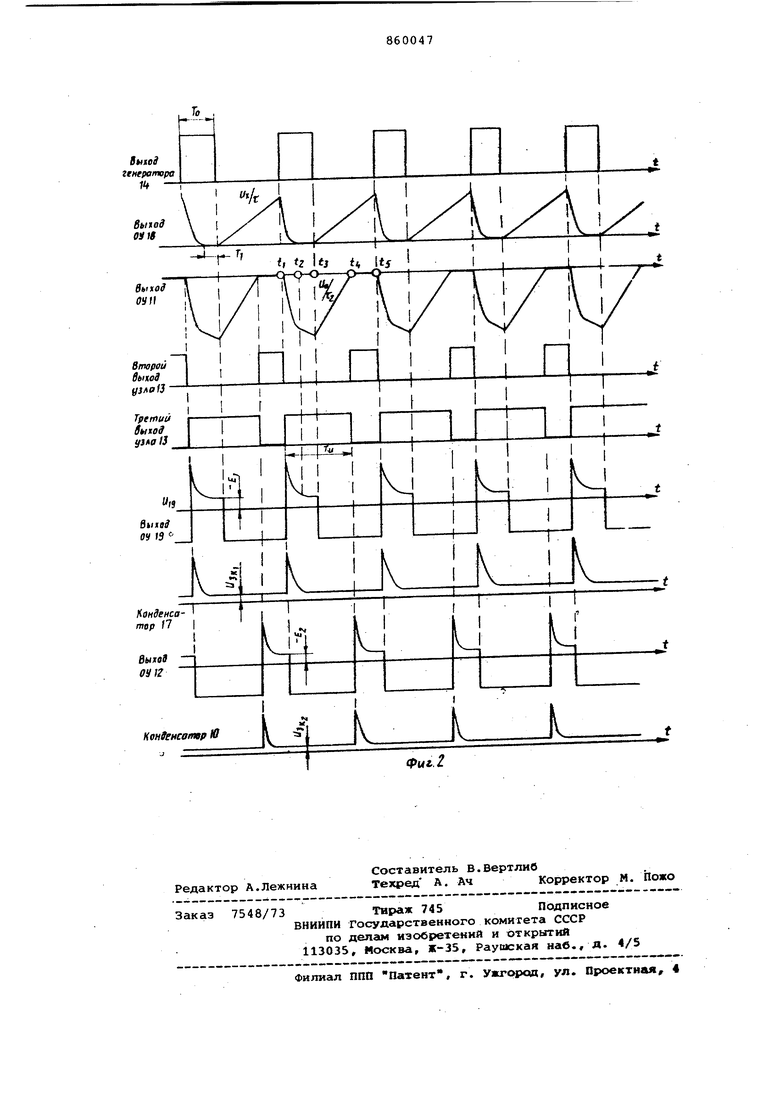

На фиг, 1 представлена блок-схема предлагаемого устройства; на фиг.. 2 - временные диаграммы работы элементов устройства.

Устройство содержит с фиг. 1) источник 1 образцового напряжения, элементы 2-.4 коммутации (ключи), вход 5 устройства, второй и-первый ограничительные резисторы 6 и 7, выход В устройства, первые интегрирующий 9 и запоминающий 10 конденсаторы, первый 11 и второй 12 операционные усилители, узел 13 син сронизации, гене- ратор 14 тактовых импульсов, .

преобразования временных интервалов в код, вторые интегрирующий 16 и заминающий 17 конденсаторы, третий 18 и четвертый 19 операционные усилители.

На временных диаграммах показаны эпюры напряжений на выходах операционных усилителей ( ОУ ) 11, 12, 18 и 19, выходе генератора 14, выходах узла 13 и на конденсаторах 10 и 17.

Устройство работает следующим образом.

Пусть на вход 5 подано напряжение и X . В момент времени t по переднему фронту импульса генератора 14 замыкаются ключи 2 и 3. В результате напряжение на конденсаторе 17, сформированное на конденсаторе 16 за время (Т-Т) в предыдущем такте, начинает снижаться до нуля. Последнее вызвано тем, что при замыкании ключей 2 и 3 происходит практически мгновенное (так как постоянная времени заряда конденсатора 17 много меньше Re,,) изменение знака потенциала точки а за счет образования 100%-ной отрицательной обратной спязи через ключ 3 и за счет поддержания потенциала тОчки -fe близким к нулю - Е,+Uciob где U(o - напряжение на конденсаторе 10) .

В результате конденсатор 16 начинает разряжаться до нуля эквивалентньм током разряда 1 (-t) . Процесс его разряда описывается уравнением.

Ux-(E;,tUc,)

1эД).

(Т-Т„)R,C. Ci 6 1Ь

Одновременно за счет образования связи через ключ 2 конденсатор 9 начинает заряжаться эквивалентным током заряда 1з2 - 1э1 - В это же время конденсатор 9 заряжается током, обусловленным входным напряжением (U)t/R,) , током, зависящим от (Jo I RT ), и током, определяемым (EU- . Таким образом, в течение времени Ci2-t/i) на конденсаторе 9 сформируется интегральное значение.

W Uc

9a

Т,, U)

,

где Е приведенное ко входу значение напряжения смещения и дрейфа нуля операционного усилителя 11; С о емкость конденсатора 9, R- - сопротивление резистора 7. После окончания разряда конденсатора 16 на конденсаторе 17 за счёт действия 100%-ной отрицательной обратной связи через ключ 3 установится потенциал / равный по значению и противоположный по знаку Е течение оставшегося времени (Тд-Т) после разряда конденсатора 16 конденсатор 9 продолжает заряжаться теми же токами, за исключением

()

В результате за время(. j-t) л

92

на конденсаторе 9 сформируется интегральное значение

Uo..

Е2

о г

В момент времени tj задним фронтом тактового импульса размыкаются ключи 2 и 3, в результате чего на к денсаторе 16 происходит накопление нового заряда - соответствующему измеряемому напряжению, а конденсатор 9 начинает разряжаться образцовьм напряжением U. В момент времени t выходное напряжение операционного усилителя 11 достигает нуля. По этому сигналу-признаку операционного усилителя 12 узел 13 замкнет ключ 3, что приведет к образованию 100%-ной отрицательной обратной связи и тем caiMHM к поддержанию выходного напряжения операционного усилителя 11 равным (2+Ocio) при хода очередного тактового импульса. За интервал времени (-t4.-1 %) а ко денсаторе 9 сформируется интегральн значение H - -Ucio %т.-.„) - , В течение оставшегося времени на ко денсаторе 9 сформируется ()-г За счет действия 100%-ной отрица тельной обратной связи, образованной через ключ 4, начиная с момента вре мени t4 , на конденсаторе 10 установится потенциал 1)равный. по начению и противоположный по знаку Ел практически мгновенно, так как постоянная времени заряда конденсатора 10 много меньше , 00-В момент времени t происходит очередной тактовый импульс. Цикл работы устройства повторяется. Информативный интервал времени Т можно определить, исходя из следующ

(8)

После подстановки в (8 значений напряжений из (1) и (2) и простейших преобразований получим

v, W

где К - коэффициент кодирования; 15 NJ,- информативный код. Окончательно имеем сооораженик. Процесс формированияинтегральных значений на конденсато ре 9 характеризуется равенством нулю их суммы в течение, периода преобразования Т, т.е. RT Ux Т у 7 их 1 и RTTJIIT (о) ь Из (10) следует, что сформированный узлом 15 по значению, подава-емому на его вход из узла 13, инфО 1ативный код пропорционален среднему за время Т преобразования значению измеряемого напряжения U и не зависит от значений Е и Е И полностью совпадает с функцией преобразования известного устройства. Причем в каждом текущем такте преобразования информативный код пропорционален среднему значению U за предыдущий такт. Таким образом, быстродействие предлагаемого устройства характеризуется временем Т одного фиксированного такта вместо двух характерных для известного устройства, что и обуславливает повышение быстродействия. Непрерывное интегрирование U;, осуществляемое в нем, исключает необходимость переключения в цепях измеряемого и образцового напряжения, что обуславливает значительно более высокую точность преобразования по сравнению с известным устройством. Кроме того вследствие непрерывного интегрирования Uj в предлагаемом устройстве исключается пропуск информации об измеряемом напряжении, что также выгодно отличает его от известного. Формула изобретения Устройство для ввода информации от аналогового датчика в вычислительную машину, содержащее источник образцового напряжения, два ограничительнь1х резистора, первый и. второй элементы коммутации, подключенные управляющими входами к первому выходу узла синхронизации, второй выход которого соединен с управляющим входом третьего злемента коммутации, третий выход - через узел преобразования временных интервалов в код с выходом устройства, а первый вход с выходом генератора тактовых импульсов, а второй вход - через третий элемент коммутации с прямым входом первого операционного усилителя, инвертирующий вход которого соединен через первый интегрирующий конденсатор с инвертирующим входом второго операционного усилителя, прямым входом и выходом подключенного соответс венно к нулевой шине и второму входу узла синхронизации, а инвертирующим входом - к выходу первого операцион ного усилителя, прямой вход которого соединен через первый запоминакядий конденсатор с прямьм входом второго операционного усилителя, отлича ющееся тем, что, с целью повышения точности и быстродействия устройства, в него введены вторые интег рирующий и запоминающий конденсаторы И третий и четвертый операционные уси лители, причем выход источника образ цового напряжения через первый ограничительный резистор подключен к инвертирующему входу первого операционного усилителя, вьлход третьего операционного усилителя соединен с инвертирующим входом четвертого операционного усилителя и через второй интегрирующий конденсатор со входом первого элемента коммутации, соединенного выходом с инвертирующим входом первого операционного усилителя, инвертирующий вход третьего операционного усилителя подключен ко входу первого элемента коммутации и через второй ограничительный резистор ко входу устройства, а прямой вход через ВТОР.ОЙ запоминающий конденсатор к прямым входам второго и четвертого операционных усилителей, выход которого через второй злемент коммутации соединен с прямьм входом третьего операционного усилителя. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР по заявке 2666343/18-24, кл. G06 F 3/04, 1978. 2.Патент США № 3895376, кл. 340-347, опублик. 1973( прототип)8nuiztHtpamopa Щ

вы од ОШВ -.«- Г1I 1 1 Третий iuxoff yjKO 13 Канденсаmop /7 I KoHfeHcomf Л К I I

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь напряжение-временной интервал | 1981 |

|

SU991605A1 |

| Аналоговый перемножитель | 1984 |

|

SU1166143A1 |

| Источник калиброванных напряжений | 1985 |

|

SU1283726A1 |

| Устройство для логарифмирования отношения сигналов | 1982 |

|

SU1112374A1 |

| Интегрирующий преобразователь напряжения в код | 1986 |

|

SU1410275A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1132357A1 |

| Устройство для измерения параметров R @ С @ двухполюсников,входящих в состав трехполюсной замкнутой электрической цепи | 1986 |

|

SU1364999A1 |

| Устройство для логарифмирования отношения сигналов | 1982 |

|

SU1112375A1 |

| Калибратор напряжения | 1984 |

|

SU1191892A1 |

| Интегратор | 1986 |

|

SU1401485A2 |

Авторы

Даты

1981-08-30—Публикация

1979-10-04—Подача