Изобретение относится к вычислитель- нэй технике и предназначено для решения З Щач цифровой обработки сигналов, вклю- члощее выполнение алгоритма быстрого преобразования (БПФ).

Недостатком процессора по заявке № 41815953/24 является низкая производи ЛЬНОСТЬ.

Целью изобретения является повышение производительности процессора цифровой обработки сигналов.

Сущность изобретения состоит в повышении производительности процессора цифровой обработки сигналов за счет разбиения входного потока отсчетов на два потока и организации их параллельной обработки, что позволяет использовать процессор с тактовой частотой, вдвое меньшей, чем частота поступления входных сигналов.

Сущность изобретения реализуется введением в каждый вычислительный блок пятого, шестого, седьмого и восьмого регистров входных отсчетов и второго вычислительного модуля.

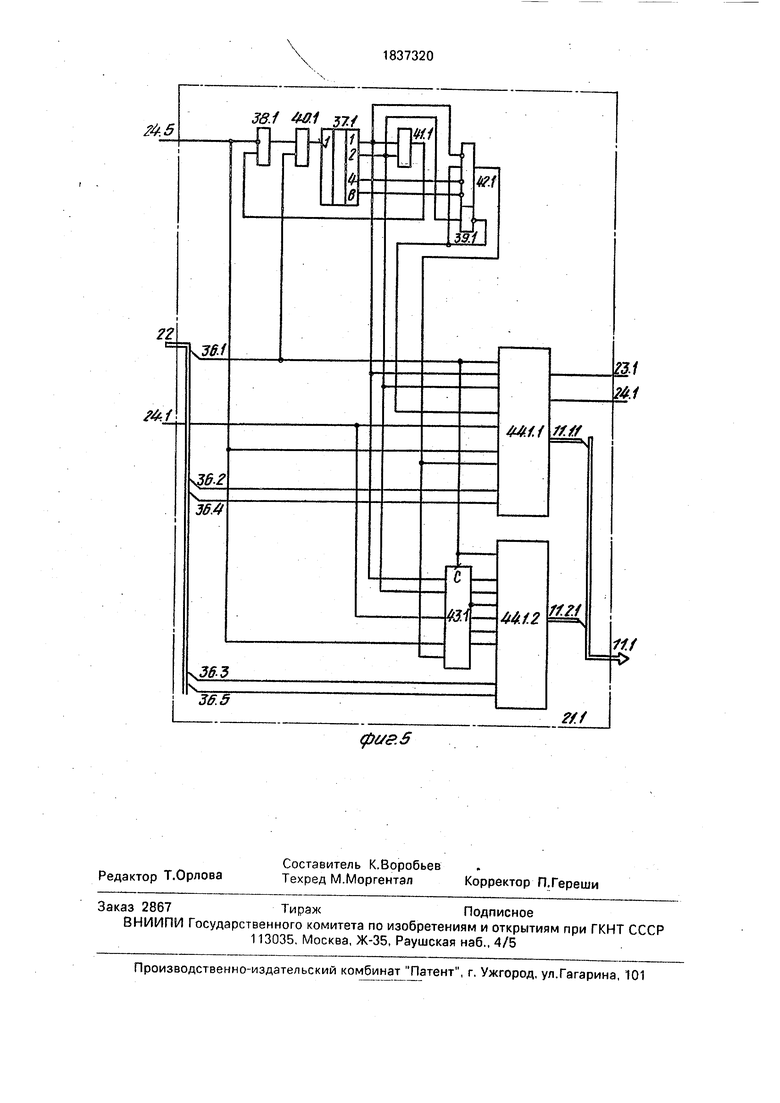

На фиг. 1 приведена структурная схема процессора цифровой обработки сигналов; на фиг. 2 приведена функциональная схема вычислительного блока; на фиг. 3 и 4 - временные диаграммы выходных сигналов устройства управления; на фиг. 5 - граф-схема реализуемого процессором алгоритма.

Процессор (фиг. 1) содержит аналого- цифровой преобразователь 1, блок 2 регист- ров, устройство 3 управления, вычислительных модулей 4, вход 5 обрабатываемого аналогового сигнала, вход 6 синхронизации, выход 7 АЦП1, первый 8 и второй 9 групповые выходы блока 2 регистров, первый 10 и второй 11 групповые выходы устройства 3 управления, первые 12.1.,.12.8, вторые 13.1...13,8, третьи 14.1...14,8, четвертые 15.1...15.8 и пятые 16.1... 16.8 выходы вычислительных модулей 4.1,..4.8,

: Каждый вычислительный блок (фиг. 2) (для примера раскрыт первый 4.1) содержит первый 32,1, второй 33.1, третий 34.1, четвертый 35.1, пятый 36.1, шестой 37.1, седьмой 38.1 и восьмой 39.1 регистры входных отсчетов, первый коммутатор 40.1 блок 41.1 формирования весовых коэффициентов, первый 42.1 и второй 43.1 блоки умножителей, первый 44.1.1 и второй 44.1.2 вычислительные модули.

Вычислительный блок4.1 служит для выполнения 1-той базовой операции над входными отсчетами А и В. Рассмотрим работу вычислительного блока при выполнении базовой операции.

Базовая операция алгоритма БПФ заключается в вычислении по формулам:

CR BR + ARWR-AIWI;

DR BR - ARWR -f AiWi;

Ci Bi+ ARWR + AiWi;

Di Bi-ARWi-AiWR, . где (AR) + jlm(Ai), В Re(BR) + J Im(Bi) исходные данные для базовой операции, поступающие в вычислительный блок 4.1 с соответствующих первого 8.1 и второго 9.1 ,8 выходов блока регистров; С Re(CR) + J Im(Ci), (DR) + j lm(Di) - результаты базовой операции, выдаваемые вычислительным блоком по мере готовности на выход № 2.I и принимаемые как исходные данные А и В для базовых операций следующей итерации соответствующими блоками 4.J согласно графу алгоритма БПФ

(фиг. 5) и заданной схеме расположения шин процессора.

Таким образом:

Вз С2; вЈ D2 ;

В5+ Сз; - Оз1;

Вт 1-С-1; Вя -Ол1;

с5;: А2 +; pj;

Аз - Се; А + - Об :

°7

A7I+1 C8 ; , ,

где , 2, 3, 4 - номер итерации, нижний индекс - номер вычислительного блока, равный номеру базовой итерации. После выполнения последней итерации с номером четыре на выходы вычислительных модулей поступают результаты-коэффициенты Фурье, причем

Yi Ci4,Y2 С54 Y4 C74 Y5 C24 ( Yio D54Yii D34 Yi2 D74; Yia D24, YM D64, Yis - D44, Yie - D84. Каждый вычислительный блок выполня- ет базовую операции над входными отсчетами обоих потоков во всех итерациях одинаково. Исключение состоит лишь в том, что в первой итерации исходные данные А и В поступают из регистров 32 и 34 или 33 и 35 соответственно для первого и второго вычислительных модулей, а в остальных итерациях - соответственно из регистров 36 и 38 или 37 и 39.

Коммутатор 40 предназначен для фор- мирования на своих двух выходах информации, поступающей на его первый и второй, третий и четвертый, пятый и шестой или седьмой и восьмой входы соответственно.

Блок 41 предназначен для формирова- ния весовых коэффициентов Wl Re(WRc) + jlm(W(i), где ,2,3,4 - номер итерации.

Вычислительный модуль 44.,2 предназначен для выполнения следующих рпе- раций над соответствующими входными отсчетами:

1)BR - ARWR - KR; B|-A|WR K|

2)KR + AiWi DR; K| - ARW| D| 3) BR + ARWR - LR; BI + ARWR - LI

4) LR - AiWi - CR; Li + AiW} - Ci. о

Рассмотрим порядок функционирования вычислительного блока. По импульсу со

входа 17,2 в регистр 32 заносится входной отсчет А п, а по импульсу со входа 17.4 в регистр 34 заносится значение входного отсчета В . Реальная ARI и мнимая Ailn части первого отсчета поступят на первый и

второй информационные входы коммутатоPC 40, реальная Вя1 и мнимая В|1 части второго отсчета поступят на первый и второй входы первого 44.1 вычислительного модуля. По импульсу со входа 17.5 в регистр 3; заносится отсчет , а по импульсу со 36.3 в регистр 35 заносится отсчет В . Реальная и мнимая части отсчета поступят на пятый и шестой коммутатора 84 соответственно, pear ьная Вр1 п+1 и мнимая части В|1-п+ второ- гс отсчета поступят на первый и второй второго 44.2 вычислительного блока. По импульсу на входе 30.1 в регистр 36 заносится значение А (где ,2,3- номер итерации), а по импульсу со входа 23.1 в регистре 38 заносится , 2,3). Реальная и мнимая части отсчета поступают на третий и четвертый входы кс ммутатора 40, а реальная BR и мнимая В части второго отсчета поступают на Tf етий и четвертый информационные входы первого вычислительного 44.1 модуля. По инпульсу со входа 30.2 отсчет А|+1 п заносится в регистр 37, а по импульсу со входа .2 отсчет заносится в регистр 39. Реальная ARl+1 n+1 и мнимая АГ1 П+1 части отсчета поступают на седьмой и восьмой в) оды коммутатора 40, а реальная Вц|+1 п+1 и мнимая BI + п+ части второго отсчета поступают на третий и четвертый входы второ- г( 44.2 вычислительного модуля. По е/ иничному сигналу на входе 25.1 на пер- вс м и втором выходах коммутатора 40 формируется реальная ARI- и мнимая AI чг сти входного отсчета, поступающие на пирвые входы первого 42 и второго 43 блоке в умножителей соответственно. На вто- pi ix их входах формируются реальная WR и мнимая Wi части весового коэффициента. В результате на выходе первого умножите- л$ формируется произведение AR , а на выходе второго Ai1-nWR ; Во втором такте первый умножитель 42 формирует произведение AR1 nWi1, а второй-Ai1-nWi1. В треть- en такте на первые входы умножителей поступают AR1-n+1 и А|1 соответственно, а на вторые WRI,- по которым они сформируют произведение ARtn+1WR1 и А|1-П+%Л в четвертом такте умножители формируют произведения AR1 n+1Wi1 и для второго вычислительного модуля 44.2 одинаково. Вычислительные модули функционируют со сдвижкой во времени на 2 такта. В последующих итераци- як порядок работы вычислительного блока не изменяется, только в этом случае входные отсчеты на входы умножителей поступают из регистров 36, 37, 38 и 39, куда заносятся по импульсам со в

содов 30.1, 30.2, 23.1, 23.2.

Формула изобретения Процессор цифровой обработки сигналов, содержащий N вычислительных блоков (где N - размерность преобразования), блок

регистров и блок синхронизации, N групп выходов которого соединены с группами управляющих входов соответствующих N вычислительных блоков, первый информационный вход К-го (, N/1) вычислитель0 ного блока соединен с первыми информационными входами 2К-го и (2К-1)- го вычислительных блоков, первый информационный выход M-ro ( + 1,N) вычислительного блока соединен с вторыми

5 информационными входами (2M-N/2)-ro и (2M-N/2+1)-ro вычислительных блоков, причем каждый вычислительный блок содержит узел формирования коэффициентов, четыре входных регистра, три коммутатора, два ум0 ножителя, два сумматора-вычитателя, два выходных регистра и шесть буферных регистров, причем информационные входы первого и второго входных регистров являются соответственно первым и вторым информа5 ционными входами вычислительного блока, первые выходы второго и третьего входных регистров соединены соответственно с первым и вторым информационными входами первого коммутатора, первый выход которо0 го соединен с первым входом первого умножителя, выход которого соединен с информационным входом первого буферного регистра, первые выходы первого и четвертого входных регистров соединены

5 соответственно с первым и вторым информационными входами второго коммутатора, первый выход которого соединен с первым информационным входом первого сумматора-вычитателя, выход которого соединен с

0 информационным входом второго буферного регистра, выход которого соединен с третьим информационным входом второго коммутатора, входы синхронизации с первого по четвертый входных регистров, пер5 вого и второго буферных регистров, соединенные между собой управляющий вход первого коммутатора и первый управляющий вход второго коммутатора, второй управляющий вход второго коммутатора и

0 управляющий вход первого сумматора-вычитателя являются соответственно с первого по девятый управляющими входами группы вычислительного блока, информационный вход блока регистров подключен к

5 информационному входу процессора, пер- . вый и второй входы синхронизации блока регистров подключены соответственно к первому и второму выходам блока синхронизации, первый и второй выходы блока регистров подключены соответственно к

третьему и четвертому информационным входам вычислительных блоков, второй и третий информационные выходы которых образуют группу информационных выходов процессора, третий и четвертый информационные входы каждого вычислительного блока подключены к информационным входам соответственно третьего и четвертого входных регистров, выходы первого и второго сумматоров-вычитателей образуют первый информационный выход вычислительного блока, второй и третий информационные выходы которого являются соответственно выходами первого и второго выходных регистров, информационные входы которых подключены к выходам соответственно первого и второго сумматоров- вычитателей, кроме того, выход второго сумматора-вычитателя подключен к информационному входу третьего буферного регистра, выход которого соединен с четвертым информационным входом второго коммутатора, пятый и шестой информационные входы которого подключены к вторым выходам соответственно первого и четвертого входных регистров, второй выход второго коммутатора соединен с первым информационным входом второго сумматора-вычитателя, вторые информационные входы первого и второго сумматоров-вычи- тателёй соединены соответственно с первым и вторым выходами третьего коммутатора, второй выход первого коммутатора соединен с первым входом второго умножителя, выход которого соединен с информационными входами четвертого и пятого буферных регистров, выходы которых соединены соответственно с первым и вторым информационными входами третьего коммутатора, третий и четвертый информационные входы которого соединены с выходами соответственно первого и шестого буферных регистров, информационный вход шестого буферного регистра соединен с выходом первого умножителя, третий и четвертый информационные входы первого коммутатора соединены с вторыми выходами соответственно второго и третьего входных регистров, вторые входы первого и второго умножителей соединены соответственно с первым и вторым выходами узла формирования коэффициентов преобразования, вход синхронизации третьего буферного регистра,соединен с шестым управляющим входом группы вычислительного блока, соединенные между собой управляющий вход узла формирования коэффициентов преобразования, вход синхронизации третьего буферного регистра соединены с шестым управляющим входом группы вычислительного блока, соединенные между собой управляющий вход узла формирования коэффициентов преобразования, первый управляющий вход третьего коммутатора, входы выборки первого, четвертого, пятого и шестого буферных регистров и управляющий вход второго сумматора-вычитателя являются десятым управляющим входом группы вычислигель0 ного блока, соединенные между собой первый вход синхронизации узла формирования коэффициентов преобрази-. вания и входы синхронизации пятого и шестого буферных регистров являются

5 одиннадцатым управляющим входом группы вычислительного блока, второй управляющий вход третьего коммутатора подключен к восьмому управляющему входу группы вычислительного блока, вход синх0 ррнизации четвертого буферного регистра подключен к пятому управляющему входу группы вычислительного блока, двенадцатый управляющий вход группы которого подключен к второму входу синхронизации

5 узла формирования коэффициентов преобразования, входы выборки и входы синхронизации первого и второго выходных регистров являются соответственно с тринадцатого по шестнадцатый управляющими

0 входами группы вычислительного блока, входы пуска и останова блока синхронизации являются одноименными входами процессора, отличающийся тем, что, с целью повышения производительности,

5 каждый вычислительный блок дополнительно содержит пятый, шестой, седьмой, восьмой буферные регистры и второй вычислительный модуль, причем информационный вход пятого буферного регистра

0 соединен с первым информационным входом вычислительного блока, информационный вход шестого регистра соединен с четвертым информационным входом вычислительного блока, информационный вход

5 седьмого регистра соединен с третьим информационным входом вычислительного блока, информационный вход восьмого регистра соединен с шестым информационным входом вычислительного блока, с

0 семнадцатого по двадцать шестой управляющие входы группы вычислительного блока соединены с соответствующими входами второго вычислительного модуля, с двадцать седьмого по тридцатый управляющие

5 входы группы вычислительного блока соединены с синхровходами соответственно пятого, шестого, седьмого и восьмого регистров, выходы которых соединены соответственно с третьим, четвертым, пятым, шестым информационными входами вычисnv тельного модуля, первый и второй информационные входы второго вычислительного модуля соединены с выходами соответственно второго и первого блоков умножителей, п« рвый и второй выходы вычислительного модуля соединены соответственно с третьим и четвертым входами вычислительного блока, третий выход вычислительного модуля соединен с вторым входом пятого группового вычислительного блока.

////

Й зв; TJj i 37 uuu

tfT.f.2

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор цифровой обработки сигналов | 1990 |

|

SU1789991A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1989 |

|

SU1619300A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Устройство для реализации быстрого преобразования Фурье | 1989 |

|

SU1672469A1 |

| Устройство для быстрого преобразования Фурье | 1983 |

|

SU1130872A1 |

| Процессор для цифровой обработки сигналов | 1985 |

|

SU1257662A1 |

| Устройство для реализации быстрого преобразования Фурье | 1988 |

|

SU1672468A1 |

| Анализатор спектров | 1982 |

|

SU1023341A1 |

| Устройство быстрого преобразования сигналов по Уолшу с упорядочением по Адамару | 1990 |

|

SU1784996A1 |

| Арифметическое устройство для процессоров быстрого преобразования Фурье | 1983 |

|

SU1116434A1 |

срае. г

11 t I i I i i t I II i I I I I I i И I I I I M i i I I i I

i и и пни пи п m и

wi

ПЛ

«л

t

«,l С I МтШШШИШтштШИШШШШШШШПШаШШ r

«tI I I I I 1 I 1 д

JOut.l

Me Biflio п паи ип onn i пи in im и t

им П П П П П П П- П П П П П П П П , K.uJ

WJ4l

Ш. LJL

JEJl

wu 1 Ifi fli iВIIi rl

t

«n eo.u

(Ml

«r.e ti.i.l I

5l.i|

1 п п п п п п п пч 1 п п п п п п п rl

Ifl 1 i Г Г I I ,t

M.«J tI iП ,t

IT.5 89.H

-t

CDut.4

-t

/45

т

22

г&1

ОТ

в

Ш

ш

ff.tf

MA

Ш2

fl.1

2f.f

pt/a 5

Авторы

Даты

1993-08-30—Публикация

1990-06-12—Подача