/if

VI

00 ЧЭ Ю 45

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор цифровой обработки сигналов | 1990 |

|

SU1837320A1 |

| Устройство быстрого преобразования сигналов по Уолшу с упорядочением по Адамару | 1990 |

|

SU1784996A1 |

| Процессор для цифровой обработки сигналов | 1985 |

|

SU1257662A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Процессор быстрого преобразования уолша-адамара | 1989 |

|

SU1795471A1 |

| Процессор быстрого преобразования Фурье | 1986 |

|

SU1388892A1 |

| ПРОЦЕССОР БЫСТРОГО ПРЕОБРАЗОВАНИЯ СИГНАЛОВ ПО УОЛШУ С УПОРЯДОЧЕНИЕМ ПО АДАМАРУ | 1992 |

|

RU2072554C1 |

| Устройство для реализации быстрого преобразования Фурье | 1988 |

|

SU1672468A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1989 |

|

SU1619300A1 |

| Вычислительное устройство для цифровой обработки сигналов | 1985 |

|

SU1295414A1 |

Изобретение относится к вычислительной технике и предназначено для решения задач цифровой обработки сигналов, включающих выполнение алгоритма быстрого преобразования Фурье (БПФ). Целью изобретения является повышение быстродействия процессора цифровой обработки сигналов за счет распараллеливания алгоритма выполнения базовой операции вычислительными блоками, что позволяет формировать одновременно реальную и мнимую части выходного отсчета и значительно сократить длительность реализации базовой операции. При этом время обработки группы входных отсчетов сопоставимо со временем их формирования, что позволяет предлагаемому процессору цифровой обра .ttj у t

otf

15

ffj

Р

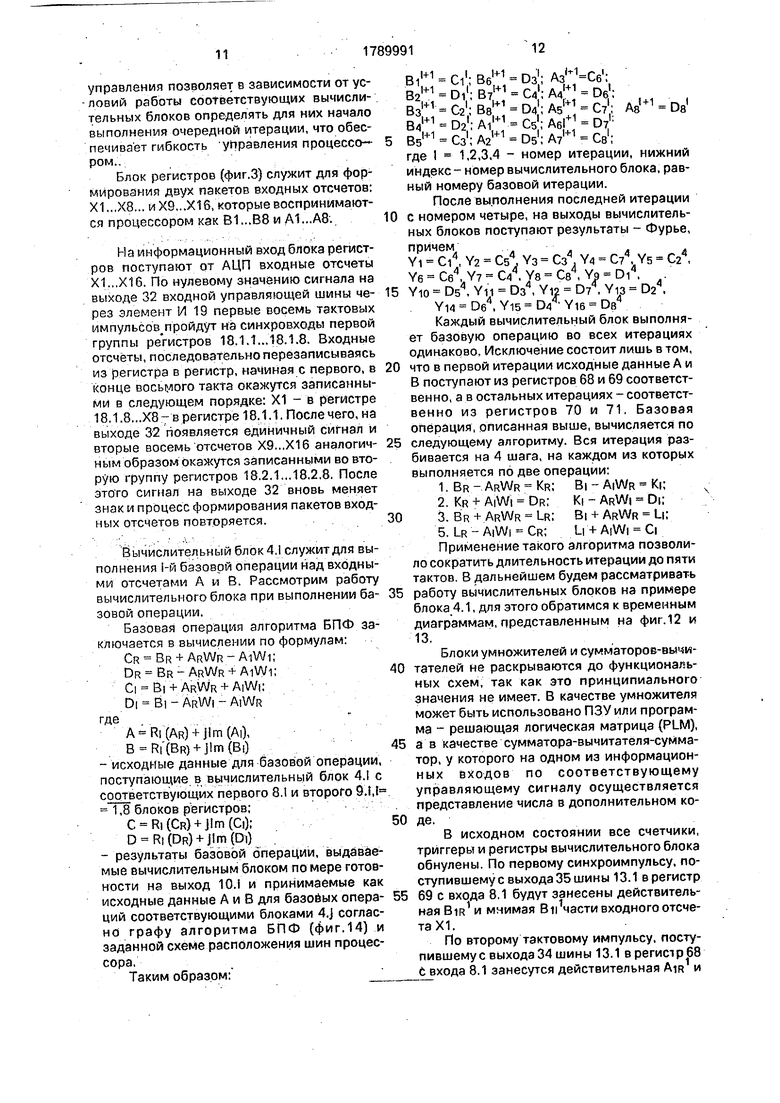

а

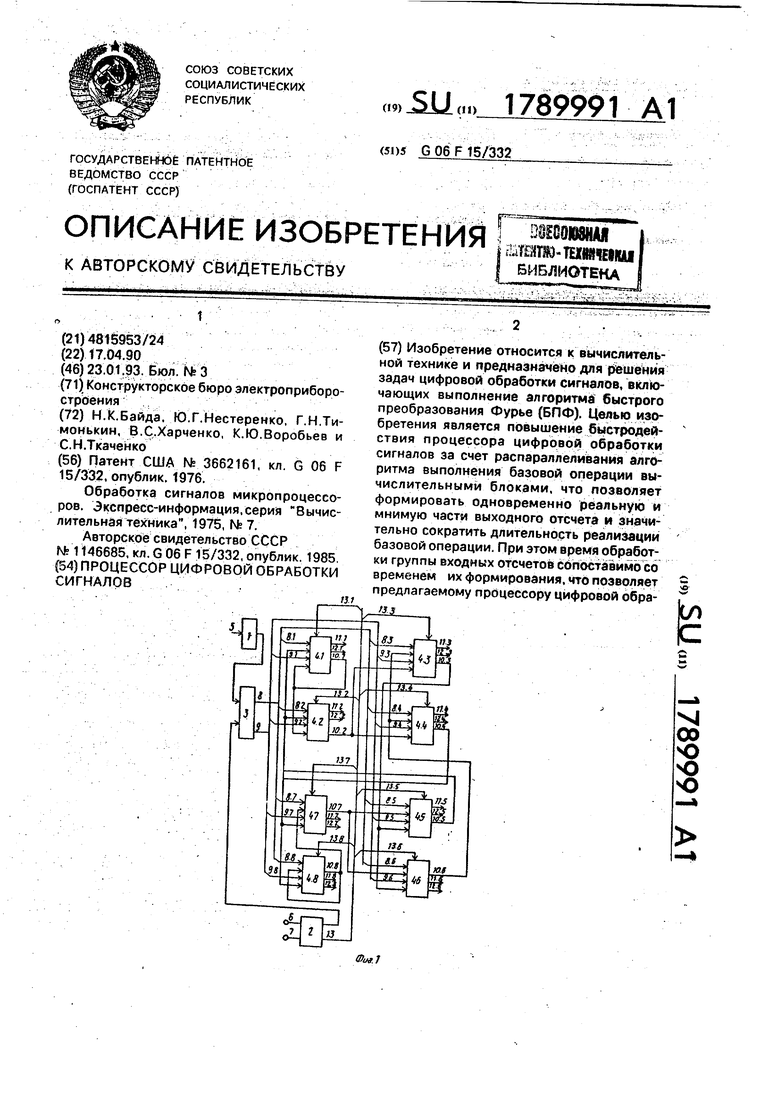

ботки сигналов работать в реальном масштабе времени. Процессор цифровой обработки сигналов содержит аналого-цифровой преобразователь 1, блок 2 синхронизации, блок 3 регистров, вычислительные блоки 4.1...4.8, вход 5 обрабатываемого аналогового сигнала, вход 6 сигнала Пуск, вход 7 сигнала Стоп, первый 8 и второй 9 групповые выходы блока 3 регистров, первые 10.1, 10.8, вторые 11У1...11.8 и третьи 12.1...12.8 выходы вычислительных модулей 4.1,..4.8, групповой еыход 13 блока 2 синхронизации и соответствующие связи. Блок 3 регистров содержит первую 18.1 и вторую 18.2 группы регистров, каждая из групп регистров состоит Из N 8 регистров 18.1.N и 18.2.N соответственно, первый 19 и второй 20 элементы И и их связи. Модуль синхронизации содержит RS-триггер 21, генератор 22 тактовых импулъсЬв, счетчик 23, первый 24, второй 25, третий 26, четвертый 27, пятый 28 и шестой 29 элементы И, триггер 30 и их связи. Каждый модуль управления (для примера раскрыт первый 15.1) содержит счетчик 37, счетчик 38, первый 39, второй 40 триггеры, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 41 .элемент ИЛИ 42, первый 43, второй 44, третий 45, четвертый 46, пятый 47, шестой 48, седьмой 49, восьмой 50, девятый 51, десятый 52 и одиннадцатый 53 элемент И, первый 54 и второй 55 триггеры и их связи, группу 56...65 входов группового выхода модуля управления. Все вычислительные блоки 4 идентичИзобретение относится к вычислительной технике и предназначено для решения задач цифровой обработки сигналов, включающих выполнение алгоритма быстрого преобразования Фурье (БПФ).

Известен процессор для цифровой обработки сигналов, содержащий N процессорных модулей и блок управления, соединенный с управляющими входами

процессорных модулей.

. ; .

Недостатков процессора является низкая производительность.

Известен процессор для цифровой обработки сигналов, содержащий блок ввода, N шин, N процессорных модулей, первыми входами соединенных с выходом блока ввода, устройство управления, выходом соединенное с управляющими входами процессорных модулей.

Недостатком процессора является низкая производительность, обусловленная большой длительностью интервала обмена

ны. Для примера рассмотрим 4,1, он содержит первый 68, второй 69, третий 70 и четвертый 71 регистры, первый 72 и второй 73 вычислительные модули, первый 74 и второй 75 регистры результата и их связи. Первый вычислительный модуль содержит узел 76 формирования коэффициентов, первый 87 коммутатор, третий 88 коммутатор, первый 89 и второй 90 блоки умножения, регистр 93, регистр 94, регистр 95, регистр 96, узел формирования коэффициентов содержит счетчик 95, блок 96 памяти, регистр 97, первый 98, второй 99, элемент 2И-ИЛИ, первый коммутатор содержит первый 10 и второй 101 элементы 2И-ИЛИ, третий коммутатор содержит первый 102, второй 103 и третий 104 элементы 2И-ИЛИ. Второй вычислительный модуль содержит второй 106 коммутатор (первый 110, второй 111, третий 112 и четвертый 113 элементы 2И-ИЛИ), первый 106 и второй 107 сумматоры-вычита- тели, пятый 108, шестой 109 регистры промежуточныхрезультатов и соответствующие связи. Новым в процессоре цифровой обработки сигналов является введение в вычислительных блоках вторых умножителей и сумматоров-вычитателей, блока регистров, второго, третьего и четвертого регистров промежуточных результатов, регистров выходных отсчетов, третьего коммутатора, узла формирования коэффициентов преобразования и обусловленных ими связей. 1 з.п. ф-лы, 14 ил.

данными между процессорными модулями.

Наиболее близким к изобретению по технической сущности является процессор

для цифровой обработки сигналов, содержащий N вычислительных блоков (где IM - размерность преобразования) и блок синхронизации, N групп выходов которого соединены с группами управляющих входов

соответствующих N вычислительных блоков, первый информационный выход К-го (К 1, N/2) вычислительного блока соединены с первыми информационными входами 2К- го и (2К-1) вычислительных блоков/первый

информационный выход M-го (М N/2 + 1,N) вычислительного блока соединен с вторыми информационными входами (2M-N/2)-ro и (2M-N/2 + 1)-го вычислительных блоков, причем каждый вычислительный блок содержит четыре входных регистра, два коммутатора, первый умножитель, первый сумматор-вычитатель и два буферных регистра, причем информационные входы первого и второго входных регистров являются соответственно первым и вторым информационными входами вычислительного блока, первые выходы второго и третьего входных регистров соединены соответственно с первым и вторым информационными входами первого коммутатора, первый выход которого соединен с информационным входом первого буферного регистра, первые выходы первого и четвертого входных регистров соединены соответственно с первым и вторым информационными входами второго коммутатора, первый выход которого соединен с первым информационным входом первого сумматора-вычитателя, выход которого соединен с информационным входом второго буферного регистра, выход которого соединен с третьим информационным входом .второго коммутатора, входы синхронизации с первого по четвертый входных регистров, первого и второго буферных регистров, соединенные между собой управляющий вход первого коммутатора и первый управляющий вход второго коммутатора, второй управляющий вход второго коммутатора и управляющий вход первого сумматора-вычитателя являются соответственно с первого по девятый управляющими входами группы вычислительного блока.

Время обработки группы входных отсчетов этим процессором значительно больше времени формирования этой группы, вследствие чего входные отсчеты должны накапливаться в узлах регистров. Таким образом, существенным недостатком этого процессора является низкая производительность и невозможность использования его для цифровой обработки сигналов в реальном масштабе времени.

Цель изобретения - повышение производительности.

Сущность изобретения состоит в повышении быстродействия процессора цифровой обработки сигналов за счет распараллеливания алгоритма выполнения базовой операции вычислительными блоками, что позволяет формировать одновременно реальную и мнимую части выходного отсчета, и значительно сократить длительность реализации базовой операции. При этом время обработки группы входных отсчетов сопоставимо со временем их формирования, что позволяет предлагаемому процессору цифровой обработки сигналов работать в реальном масштабе времени.

Введение в вычислительных блоках вторых умножителей и сумматоров-вычитате- лей позволило одновременно формировать действительную и мнимую части входных отсчетов.

Введение блока регистров позволяет формировать поток входных отсчетов в виде групп по 2N отсчетов в каждой.

Введение второго, третьего и четверто- 5 го регистров промежуточных результатов позволяет фиксировать результаты промежуточных вычислений выходных отсчетов.

Введение регистров выходных отсчетов позволило учесть разбег во времени фор0 мирования вычислительными блоками коэффициентов Фурье.

Введение третьего коммутатора позволило организовать распределение результатов промежуточных распределений

5 между сумматорами-вычитателями таким образом, чтобы обеспечить выполнение параллельного алгоритма реализаций базовой операции.

Введение узла формирования коэффи0 циентов преобразования обеспечивает формирование весовых коэффициентов преобразования в соответствии с алгоритмом реализации базовых операций.

Таким образом, заявляемый объект со5 ответствует критерию существенные отличия, поскольку в известных технических решениях не достигалось повышения быстродействия за счет распараллеливания алгоритма реализации базовой операции

0 вычислительными блоками. Это достигается благодаря введению указанной выше совокупности признаков, отсутствующих в известных аналогах и прототипе. При использовании предлагаемого техническо5 го решения может быть получен положительный эффект, состоящий в повышении быстродействия почти в два раза.

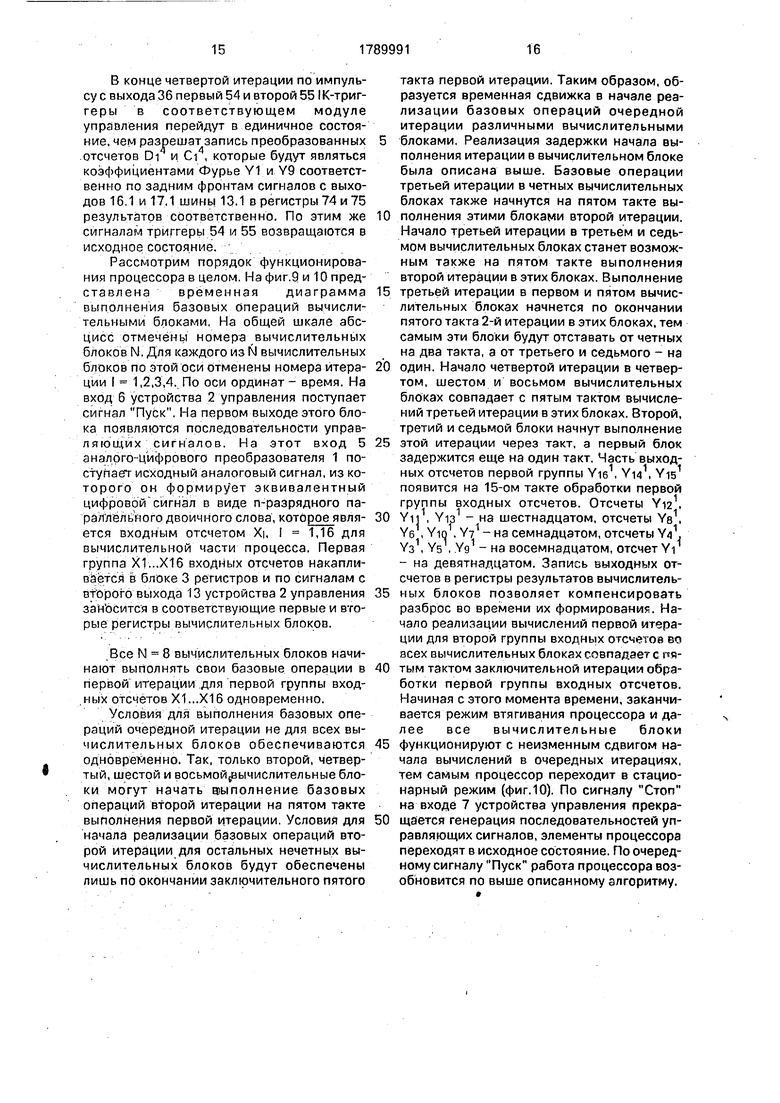

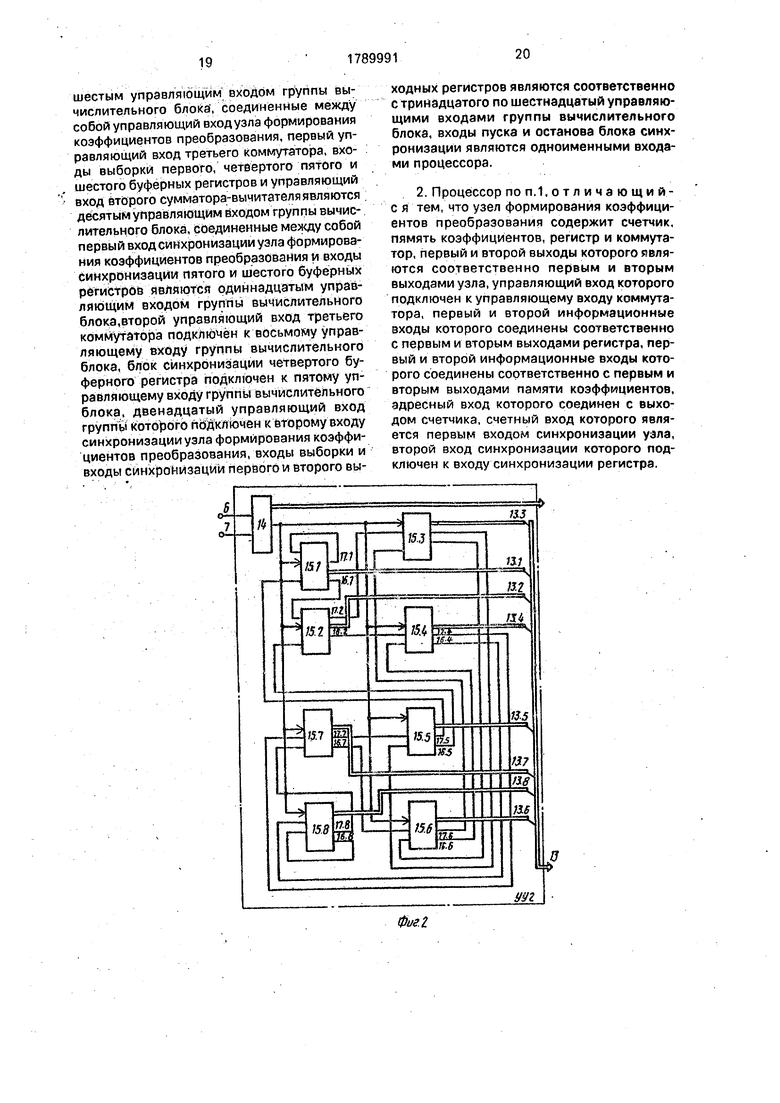

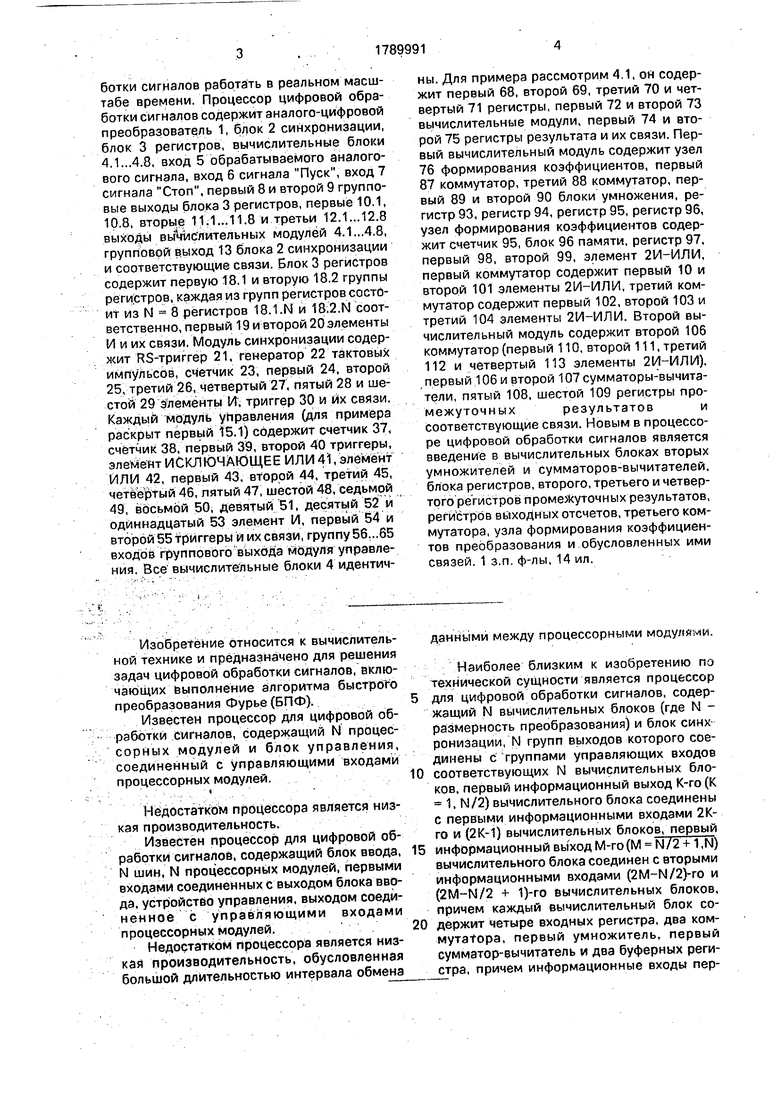

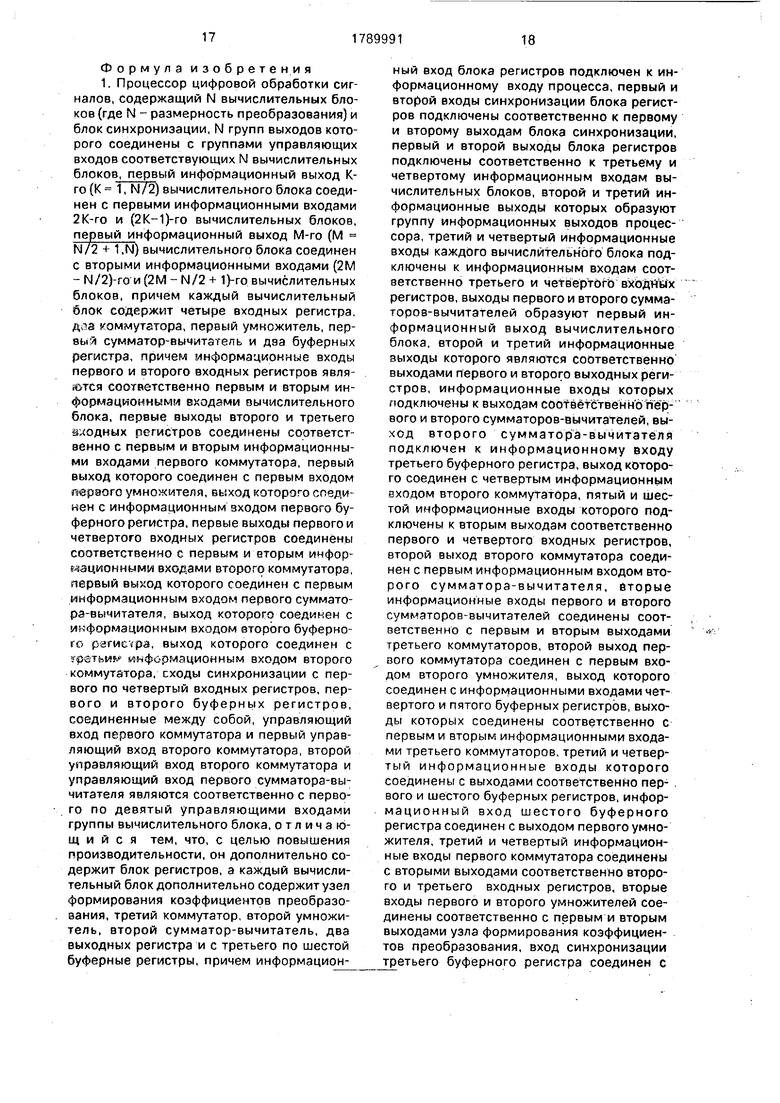

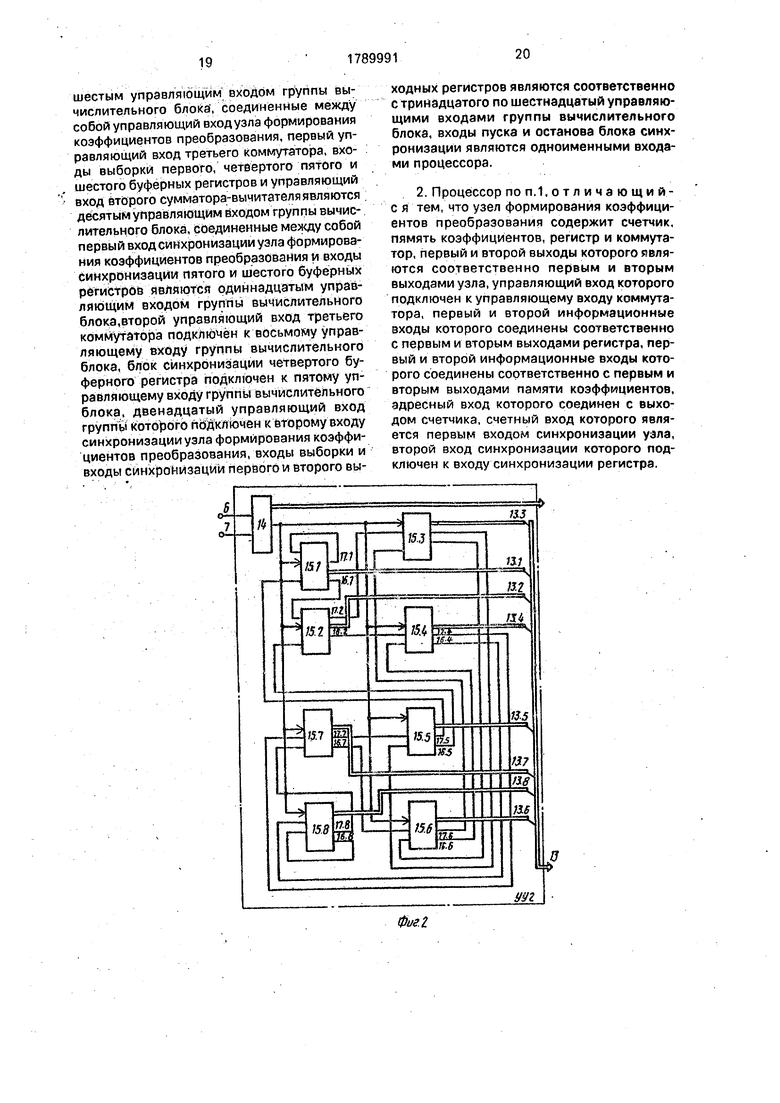

На фиг.1 изображена структура процессора цифровой обработки сигналов; на

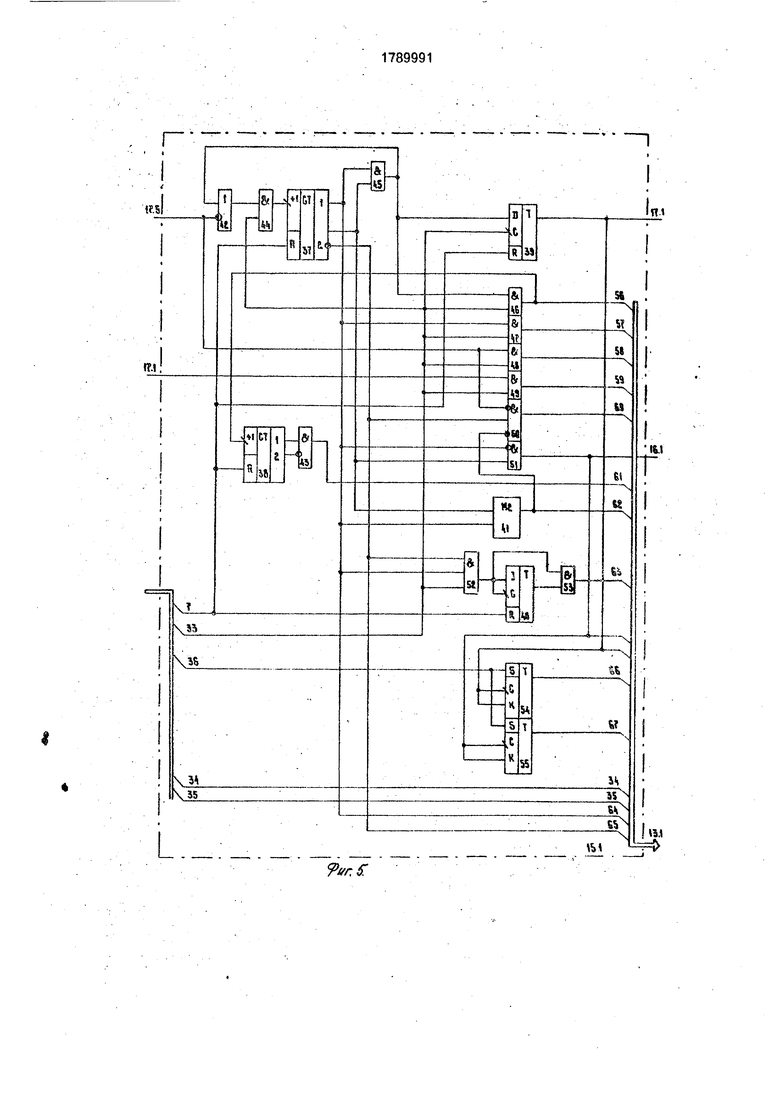

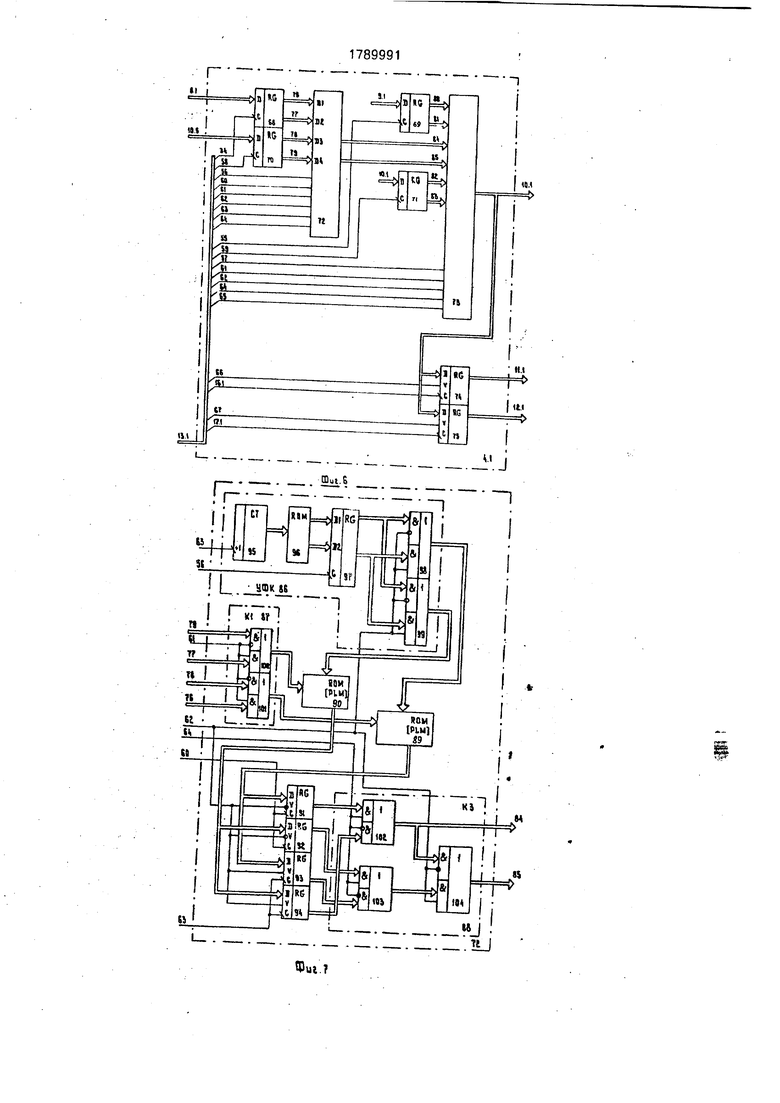

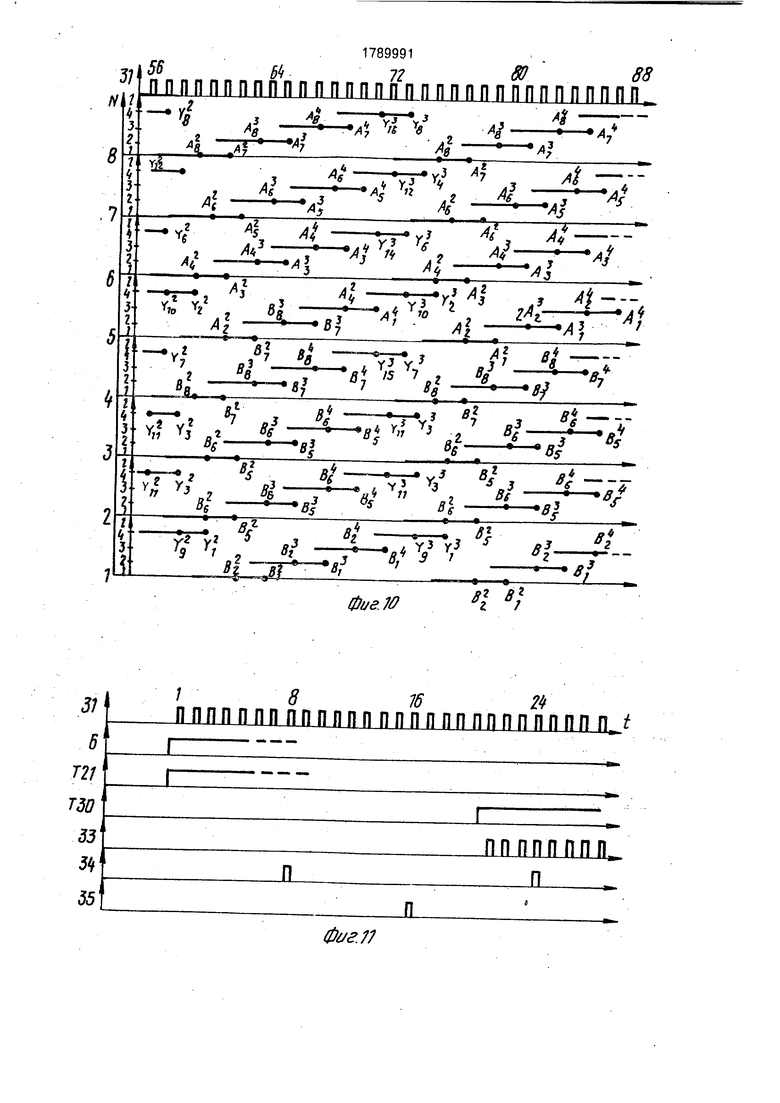

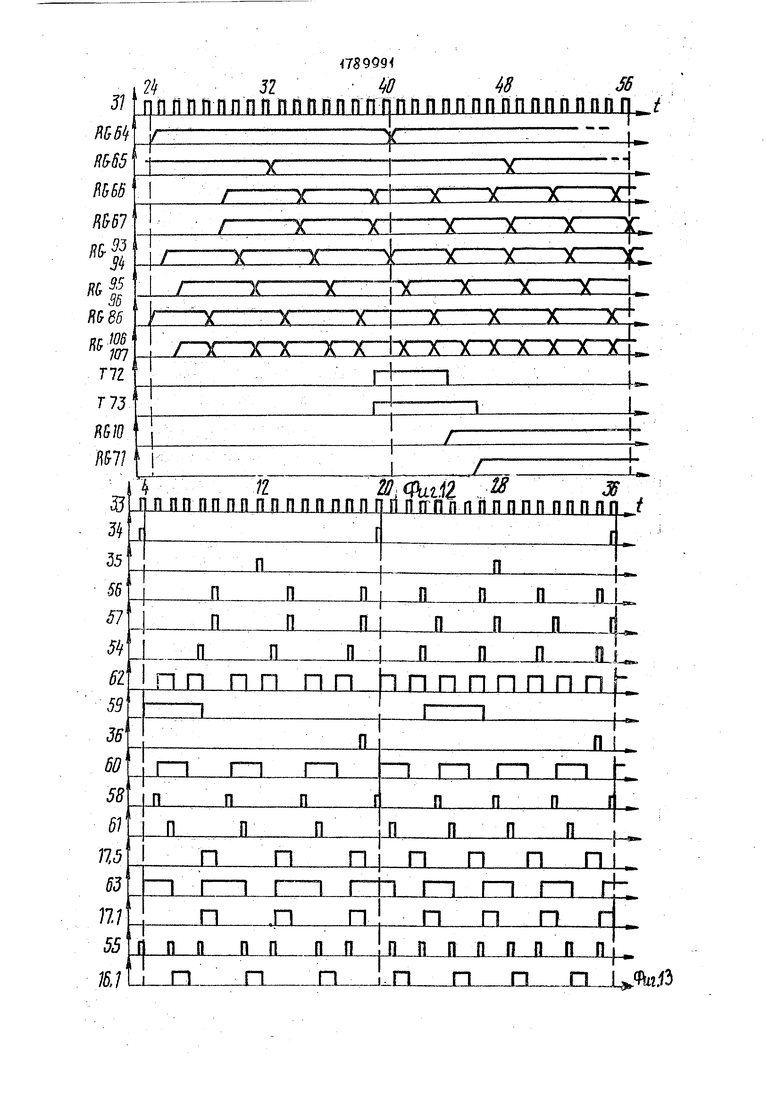

0 фиг.2 - структура блока синхронизации; на фиг.З -функциональная схема блока регистров; на фиг.4 - функциональная схема модуля синхронизации блока синхронизации: на фиг.5 - функциональная схема модуля уп5 равления; на фиг.б - структура вычислительного блока модуля; на фиг.7 - функциональная схема первого; на фиг.8 - второго вычислительных модулей соответственно; на фиг.9-13 представлены времен0 ные диаграммы функционирования процессора; на фиг. 14 - граф-схема алгоритма БПФ, реализуемого процессором.

Процессор (фиг.1) содержит аналого- цифровой преобразователь 1, блок 2 синх5 ронизации, блок 3 регистров, N 8 вычислительных блоков 4.1...4.8, вход 5 обрабатываемого аналогового сигнала, вход 6 сигнала Пуск, вход 7 сигнала Стоп, первый 8 и второй 9 групповые выходы блока 3 регистров, первые 10.1, 10.8, вторые

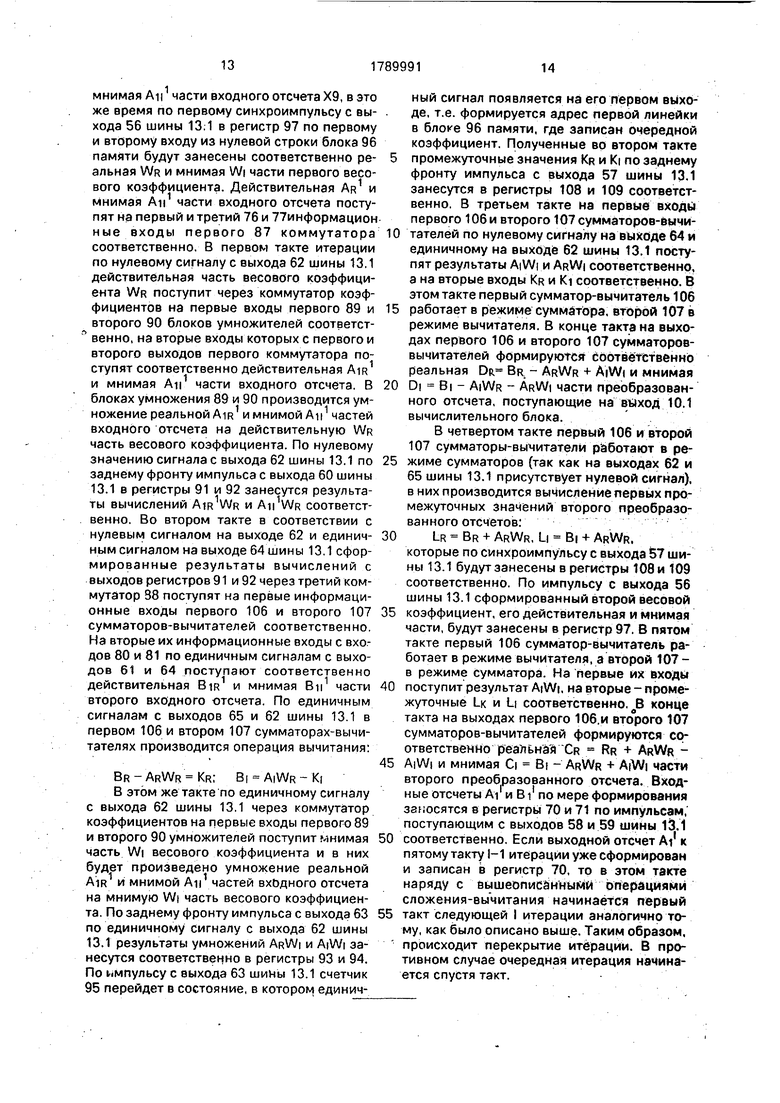

Блок 3 регистров (фиг.З) содержит первую 18.1 и вторую 18.2 группы регистров, каждая из групп регистров состоит из N 8 регистров 18.1 N и 18.2 N соответственно, первый 19 и второй 20 элементы И.

Модуль синхронизации (фиг.4) содержит RS-триггер 21, генератор 22 тактовых импульсов, счетчик 23, первый 24, второй 25, третий 26, четвертый 27, пятый 28 и шестой 29 элементы И, триггер 30.

Каждый модуль управления (для примера раскрыт первый 15,1 из них) (фиг.5) содержит счетчик 37, счетчик 38, первый 39, второй 40 триггеры, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 41, элемент ИЛИ 42, первый 43, второй 44, третий 45, четвертый 46, пятый 47, шестой 48, седьмой 49, восьмой 50, девятый 51, десятый 52 и одиннадцатый 53 элемент И, первый 54, второй 55 триггеры, группу 56...65 входов группового выхода модуля управления.- .

Все вычислительные блоки идентичны. Каждый из них содержит первый 4.1 (фиг.6), он содержит первый 68, второй 69, третий 70 и четвертый 71 регистры, первый 72 и второй 73 вычислительные модули, первый 74 и второй 75 регистры результата первый 76 и второй 77 выходы первого 68 регистра, первый 80 и второй 81 выходы второго 69 регистра, первый 78 и второй 79 выходы третьего 70 регистра, первый 82 и второй 83 выходы четвертого 71 регистра, первый 84 и второй 85 выходы первого 72 вычислительного модуля....

Первый вычислительный модуль (фиг.7) содержит узел 86 формирования коэффициентов, первый 87 коммутатор, третий 88 коммутатор, первый 89 и второй 90 блоки умножения, первый 91, второй 92, третий 93 и четвертый 94 регистры, узел формирования коэффициентов содержит счетчик 95, блок 96 памяти, регистр 97, первый 98 и второй 99 элементы 2Й-ИЛИ, первый коммутатор содержит первый 100 и второй 101 элементы 2И-ИЛИ, первый 102, второй 103 и трерй 104 элементы 2И-ИЛИ.

Второй вычислительный модуль (фиг,8) содержит второй 105 коммутатор, первый 106 и второй 107 сумматоры-вычитатели, пятый 108 и шестой 109 регистры промежуточ- ных результатов, второй коммутатор содержит первый 110, второй 111, третий 112 и четвертый 113 элементы 2И-ИЛИ.

На фиг,9-13 использованы обозначения, введенные на фиг,1-8.

На фиг. 14 символами Х1,Х2,...,Х1 б обозначены элементы входной последовательности, символами Y1, Y2,...,Y16 - элементы выходной последовательности коэффициентов Фурье.

Рассмотрим назначение основных узлов процессора. Аналого-цифровой преобразователь (АЦП) 1 предназначен для приема аналогового сигнала с амплитудой, лежащей в пределах заданного диапазона, и формирования эквивалентного цифрового

0 сигнала; т.е. n-разрядного параллельного двоичного сигнала, т.е. n-разрядного параллельного вдвоичного слова, представляющего этот сигнал. Взятые в фиксированные дискретные моменты времени они пред5 ставляют собой последовательность входных отсчётов процессора. Цепи управления и синхронизации АЦП не показаны.

. Устройство 2 управления предназначено для формирования последовательности

0 сигналов для управление и синхронизации работы блока 3 регистров и групп 4.1...4.8 вычислительных блоков.

Рассмотрим порядок работы блока синхронизации.

5 В исходном положении все триггеры и счетчики находятся в нулевом состоянии.

По сигналу Пуск, поступающему на вход 6, триггер 21 переходит в единичное состояние (временная диаграмма функцио0 нирования блока 14 синхронизации представлена на фиг. 11).

По единичному сигналу с его прямого выхода генератор 22 тактового ммпульса начинает генерировать последовательность

5 синхроимпульсов.v

Изменение состояний счетчиковдригге- ров с синхровходами и регистров процессора происходит по заднему фронту соответствующего тактового импульса.

0 Счетчик 23 на выходе первого разряда делит входную последовательность синхроимпульсов на два, на выходе второго - на четыре, на выходе третьего - на восемь, на выходе четвертого - на шестнадцать, на вы5 ходе пятого - на тридцать два.

Элемент И 25 служит для выделения синхроимпульсов, порядковый номер которых равен А п 8, где п 1,2,3,... Таким образом, восьмой импульс из синхропосле0 довательности через элемент И 26 поступит на вход 35, а шестнадцатый через элемент И 27 - на вход 34, двадцать четвертый импульс поступит вновь на вход 35 первой шины и т.д. Элемент И 24 служит для выде5 ления синхроимпульса с порядковым номером двадцать. По этому импульсу триггер 30 переводится в единичное состояние и разрешает прохождение синхропоследова- тельности с выхода генератора 22, начиная с 21-го импульса через элемент И 28 на вход

33 первой выходной шины. Элемент И 29 служит для выделения последовательности синхроимпульсов с порядковыми номерами G 7 + п 16, п 0,1,..., которая поступает на вход 36 первой шины. По сигналу Стоп, 5 поступающему на вход 7 процессора, триггеры 21 и 30 переводятся в нулевое состояние. Генератор 22 тактовых импульсов прекращает работы, счетчик 23 обнуляется. Блок синхронизации переходит в исходное 10 состояние. По запускающему сигналу на входе 6 процессора работа блока возобновится, как описано выше.

. Каждый 15.1 из группы 15.1...15.8 управляющих модулей предназначен для форми- 15 рования последовательности сигналов, управляющих работой соответствующего 4.1, I 1,8 вычислительного блока. Рассмотрим порядок работы модуля на примере первого 15.1. В исходном состоянии счетчи- 20 «и 37 и 38, триггеры 39 и 40 обнулены. Первый импульс, поступающий с выхода 33 входной шины через элемент И 44 на первый синхровход счетчика 37, переводит его в очередное состояние, в котором единич- 25 ный сигнал появляется на его первом выходе, по второму импульсу - на втором, по третьему - на первом и втором, по четвертому импульсу счетчик 37 обнуляется. По очередному импул ьсу, проходящему на син- 30 хровход счетчика 37, порядок его работы повторяется, как описано выше. Исключение составляет ситуация, если в момент когда счетчик 37 обнулен, на входе 17.5 появляется единичный сигнал, то очередной 35 импульс гасится и счетчик остается в нулевом состоянии до смены значения сигнала на выходе 17.5. Нулевое состояние счетчика 37 яляется идентификатором начала оче: редной итерации. Гашение импульса приво- 40 дит к тому, что появляется возможность управлять временем начала итерации.

. Когда на выходе первого разряда счетика 37 присутствует единичный сигнал, а на втором - нулевой, через элемент И 52 на 45 - и С-входы триггера 40 поступит импульс, который переведет его в единичное состоя,- ( ние. Единичный сигнал с прямого выхода риггера 40 разрешит прохождение синхромпульсов в моменты, когда счетчик 37 бу: 50 ет находиться в описанном состоянии на вход 61 шины 13.1.

При единичном сигнале с выхода элеента И 45, поступающему на D-вход триггера 39, по синхроимпульсу с выхода 33 55 входной шины триггер 39 перейдет в единичное состояние, по этому же импульсу четчик 37 перейдет в следующее состояние на D-входе триггера 39 появится нулевой игнал, таким образом по очередному импульсу с выхода 33 входной шины триггер 39 возвратится в исходное состояние. Обозначим через А последовательность сигналов с первого выхода, через В - последовательность с второго прямого выхода счетчика 37 - а В - инверсного, последовательность импульсов с выхода 33 входной шины обозначим как С. Тогда элемент И 46 реализует функцию Fi ABC. Счетчик 38 по первому импульсу последовательности FI перейдет в состояние, когда единичный сигнал появится на первом его выходе, по второму - на втором, по третьему на первом и втором, по четвертому он перейдет в исходное состояние и т.д.

При этом единичный сигнал на выходе элемента И 49 будет присутствовать только в тот момент, когда на первом выходе счётчика 38 присутствует единичный, а на втором - нулевой сигнал.

Элемент И 47 реализует функцию Fa AC. Элемент И 51 реализует функцию Fa AB.

Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 41 реализует функцию F4 А фВ, где символом ф обозначается операция суммирования .по модулю два.

По единичному сигналу с выхода 7 входной шины счетчик 37, счетчик 38, триггер 39, триггер 40 перейдет в исходное состояние.

Рассмотрим порядок работы блока синхронизации в целом. Каждый 15.1 из модулей управления по сигналам, поступающим на их первые входы с первого выхода блока 14 синхронизации, формирует на своем первом групповом выходе 13.1 последовательность управляющих сигналов для соответствующего 4.1.1 1,8 вычислительного блока. Начало выполнения базовой операции в данном 4.I вычислительном блоке определяется исходя из наличия условий для ее выполнения Такими условиями считаются:

а) наличие в данный момент исходного отсчета AI , где I - номер итерации.

б) с начала (Ы)-й итерации прошло не менее четырех тактов. Наличие отсчета At1 определяется по1 единичному сигналу на втором выходе 17.J соответствующего 15.J модуля управления, (j определяется из алгоритма БФП реализуемого процессором). Второе условие реализуется переходом счетчика 37 в исходное состояние).

Если первое условие реализуется на пятом такте (1-1)-й итерации, то за счет гашения тактового импульса на бйнхров ходё счетчика 37, как было описано выше, происходит задержка на один такт начала 1-й ите- рацйи. Таким образом, устройство

управления позволяет а зависимости от ус- ловий работы соответствующих вычислительных блоков определять для них начало выполнения очередной итерации, что обеспечивает гибкость управления процессором..

Блок регистров (фиг.З) служит для формирования двух пакетов входных отсчетов: Х1...Х8... и Х9...Х1 б, которые воспринимаются процессором как В1...В8 и А1...А8..

На информационный вход блока регистров поступают от АЦП входные отсчеты Х1...Х16. По нулевому значению сигнала на выходе 32 входной управляющей шины через элемент И 19 первые восемь тактовых импульсов пройдут на синхровходы первой группы регистров 18.1.1...18.1.8. Входные отсчёты, последовательно перезаписываясь из регистра в регистр, начиная с первого, в конце восьмого такта окажутся записанными в следующем порядке: Х1 - в регистре 18.1.8...Х8-в регистре 18.1.1. После чего, на выходе 32 появляется единичный сигнал и вторые восемь отсчетов Х9...Х16 аналогичным образом окажутся записанными во вторую группу регистров 18.2.1...18,2.8. После этого сигнал на выходе 32 вновь меняет знак и процесс формирования пакетов входных отсчетов повторяется.

бычислительный блок 4.1 служит для выполнения i-й базовой операции над входными отсчетами А и В. Рассмотрим работу вычислительного блока при выполнении базовой операции.

Базовая операция алгоритма БПФ заключается в вычислении по формулам:

CR BR +ARWR-AiWi;

DR BR-ARWR +AiWi;

Ci Bi + ARWR + AiWi:

Di Bi-ARW|-AiWR где .

A Ri(AR) + j1m(Ai),

B Ri(BR) + jlm(Bi)

- исходные данные для базовой операции, поступающие в вычислительный блок 4.1 с соответствующих первого 8.1 и второго 9.1,1 1,8 блоков регистров;

C Ri(CR) + (Ci);

D Rt(DR) + jlm(Di)

- результаты базовой операции, выдаваемые вычислительным блоком по мере готовности на выход ЮЛ и принимаемые как исходные данные А и В для базовых операций соответствующими блоками 4.J согласно графу алгоритма БПФ (фиг.14) и заданной схеме расположения шин процессора.

Таким образом:

Bi Ci iBe Da1; В2|+1 Di ; В7М С/; АГ De1: Вз +г С2 ;В81+1 04X 07 ; Aj+1-Da В4|+1 D2 ; AiM Cs1; A6I+1 D7I:

B5I+1 - C3 ; A2I+1 D5 ; A7 +1 Ce ;

где I 1,2,3,4 - номер итерации, нижний индекс - номер вычислительного блока, равный номеру базовой итерации.

После выполнения последней итерации

0 с номером четыре, на выходы вычислительных блоков поступают результаты - Фурье, причем

YI СГ, Y2 С54 Y3 Сз4 Y4 - , Y5 С24, Ye Се4, Y С44, Y8 С84, YQ Di4. .

5 Yio D54, YH D34, Yi2 DT . Yi3 D24. Yi4 D64, De4 Каждый вычислительный блок выполняет базовую операцию во всех итерациях одинаково. Исключение состоит лишь в том,

0 что в первой итерации исходные данные А и В поступают из регистров 68 и 69 соответственно, а в остальных итерациях - соответст- венно из регистров 70 и 71. Базовая операция, описанная выше, вычисляется по

5 следующему алгоритму. Вся итерация разбивается на 4 шага, на каждом из которых выполняется по две операции:

0 3. BR + ARWR LR; BI + ARWR Li; 5. LR - AiWi CR; LI + AiWi Ci Применение такого алгоритма позволило сократить длительность итерации до пяти тактов. В дальнейшем будем рассматривать

5 работу вычислительных блоков на примере блока 4.1, для этого обратимся к временным диаграммам, представленным на фиг.12 и 13.

Блоки умножителей и сумматоров-вычи0 тателей не раскрываются до функциональных схем, так как это принципиального значения не имеет. В качестве умножителя может быть использовано ПЗУ или программа - решающая логическая матрица (PLM),

5 а в качестве сумматора-вычитатёля-сумма- тор, у которого на одном из информационных входов по соответствующему управляющему сигналу осуществляется представление числа в дополнительном ко0 де.

В исходном состоянии все счетчики, триггеры и регистры вычислительного блока обнулены. По первому синхроимпульсу, поступившему с выхода 35 шины 13.1 в регистр

5 69 с входа 8.1 будут занесены действительная BIR и мнимая В и части входного отсчета Х1.

По второму тактовому импульсу, поступившему с выхода 34 шины 13.1 в pernci p 68 с входа 8.1 занесутся действительная AiR1 и

мнимая An1 части входного отсчета Х9, в это же время по первому синхроимпульсу с вы- . хода 56 шины 13.1 в регистр 97 по первому и второму входу из нулевой строки блока 96 памяти будут занесены соответственно ре- 5 альная WR и мнимая Wi части первого весового коэффициента. Действительная ARI и мнимая Ац1 части входного отсчета поступят на первый и третий 76 и 77информацион ные входы первого 87 коммутатора 10 соответственно, В первом такте итерации по нулевому сигналу с выхода 62 шины 13.1 действительная часть весового коэффициента WR поступит через коммутатор коэффициентов на первые входы первого 89 и 15 второго 90 блоков умножителей соответст- венно, на вторые входы которых с первого и второго выходов первого коммутатора поступят соответственно действительная AIR и мнимая Ац1 части входного отсчета. В 20 блоках умножения 89 и 90 производится умножение реальной AIR и мнимой Ац1 частей входного отсчета на действительную WR часть весового коэффициента. По нулевому значению сигнала с выхода 62 шины 13.1 по 25 заднему фронту импульса с выхода 60 шины 13.1 в регистры 91 и 92 занесутся результаты вычислений AIR WR и An WR соответственно. Во втором такте в соответствии с нулевым сигналом на выходе 62 и единич- 30 ным сигналом на выходе 64 шины 13.1 сформированные результаты вычислений с выходов регистров 91 и 92 через третий коммутатор 38 поступят на первые информационные входы первого 106 и второго 107 35 сумматоров-вычитателей соответственно. На вторые их информационные входы с вхо.- дов 80 и 81 по единичным сигналам с выходов 61 и 64 поступают соответственно действительная Вт1 и мнимая Вц1 части 40 второго входного отсчета. По единичным сигналам с выходов 65 и 62 шины 13.1 в первом 106 и втором 107 сумматорах-вычи- тателях производится операция вычитания:

45

BR-ARWR KR; B| A|WR-K| В этом же такте по единичному сигналу с выхода 62 шины 13.1 через коммутатор коэффициентов на первые входы первого 89 и второго 90 умножителей поступит мнимая 50 часть Wi весового коэффициента и в них будет произведено умножение реальной AiR1 и мнимой Ац частей входного отсчета на мнимую Wi часть весового коэффициента. По заднему фронту импульса с выхода 63 55 по единичному сигналу с выхода 62 шины 13.1 результаты умножений ApWi и AiWi занесутся соответственно в регистры 93 и 94. По ьмпульсу с выхода 63 шины 13.1 счетчик 95 перейдет в состояние, в котором единичный сигнал появляется на его первом выходе, т.е. формируется адрес первой линейки в блоке 96 памяти, где записан очередной коэффициент. Полученные во втором такте промежуточные значения KR и К| по заднему фронту импульса с выхода 57 шины 13.1 занесутся в регистры 108 и 109 соответственно. В третьем такте на первые входы первого 106 и второго 107 сумматоров-вычитателей по нулевому сигналу на выходе 64 и единичному на выходе 62 шины 13.1 поступят результаты AiWi и ApWi соответственно, а на вторые входы KR и Ki соответственно. В этом такте первый сумматор-вычитатель 06 работает в режиме сумматора, второй 107 в режиме вычитателя. В конце такта на выходах первого 106 и второго 107 сумматоров- вычитателей формируются соответственно реальная DR BR - ARWR + AiWi и мнимая DI Bi - AiWR - ARWI части преобразованного отсчета, поступающие на выход 10.1 вычислительного блока.

В четвертом такте первый 106 и второй 107 сумматоры-вычитателй работают в режиме сумматоров (так как на выходах 62 и 65 шины 13.1 присутствует нулевой сигнал), в них производится вычисление первых промежуточных значений второго преобразованного отсчетов:

LR BR + ARWR, LI В| + . которые по синхроимпульсу с выхода 57 шины 13.1 будут занесены в регистры 108 и 109 соответственно. По импульсу с выхода 56 шины 13.1 сформированный второй весовой коэффициент, его действительная и мнимая части, будут занесены в регистр 97. В пятом такте первый 106 сумматор-вычитатель работает в режиме вычитателя, а второй 107 - в режиме Сумматора. На первые их входы поступит результат AiWi. на вторые - промежуточные LK и LI соответственно. В конце такта на выходах первого Юб.и второго 107 сумматоров-вычитателей формируются соответственно реал ьна я Ср RR + ARWR - AiWi и мнимая Ci BI - + A|W| части второго преобразованного отсчета. Входные отсчеты Ai и В1 no мере формирования заносятся в регистры 70 и 71 по импульсам, поступающим с выходов 58 и 59 шины 13.1 соответственно. Если выходной отсчет At к пятому такту 1-1 итерации уже сформирован и записан в регистр 70, то в этом такте наряду с вышеописанными операциями сложения-вычитания начинается первый такт следующей I итерации аналогично тому, как было описано выше. Таким образом, происходит перекрытие итерации. В противном случае очередная итерация начинается спустя такт.

В конце четвертой итерации по импульсу с выхода 36 первый 54 и второй 55 IK-триг- геры в соответствующем модуле управления перейдут в единичное состояние, чем разрешат запись преобразованных .отсчетов D-f и Ci4, которые будут являться коэффи1диентами Фурье Y1 и Y9 соответственно по задним фронтам сигналов с выходов 16.1 и 17..1.шины, 13.1 в регистры 74 и 75 результатов соответственно. По этим же сигналам триггеры 54 и 55 возвращаются в исходное состояние.

Рассмотрим порядок функционирования процессора в целом. На фиг.9 и 10 представлена временная диаграмма выполнения базовых операций вычислительными блоками, На общей шкале абсцисс отмечены номера вычислительных блоков N. Для каждого из N вычислительных блоков по этой оси отменены номера итерации I 1,2,3,4. По оси ординат - время. На вход б устройства 2 управления поступает сигнал Пуск. На первом выходе этого блока появляются последовательности управляющих сигналов. На этот вход 5 анэлрго-цифрового преобразователя 1 поступает исходный аналоговый сигнал, из которого он формирует эквивалентный цифровой сигнал в виде n-разрядного па- рэллелйюго двоичного слова, которое явля- ется входным отсчетом.Х|, I 1,16 для вычислительной части процесса. Первая группа Х1...Х16 входных отсчетов накапливается в блоке 3 регистров и по сигналам с второго выхода 13 устройства 2 управления заносится в соответствующие первые и вторые регистры вычислительных блоков.

Все N 8 вычислительных блоков начинают выполнять свои базовые операции в первой итерации .для первой группы входных отсчетов Х1...Х16 одновременно.

Условия для выполнения базовых операций очередной итерации не для всех вычислительных блоков обеспечиваются одновременно. Так, только второй, четвертый, шестой и восьмой вычислительные блоки могут начать выполнение базовых операций второй итерации на пятом такте выполнения первой итерации. Условия для начала реализации базовых операций второй итерации для остальных нечетных вычислительных блоков будут обеспечены лишь по окончании заключительного пятого

такта первой итерации. Таким образом, образуется временная сдвижка в начале реализации базовых операций очередной итерации различными вычислительными

блоками. Реализация задержки начала выполнения итерации в вычислительном блоке была описана выше. Базовые операции третьей итерации в четных вычислительных блоках также начнутся на пятом такте выпол нения этими блоками второй итерации. Начало третьей итерации в третьем и седьмом вычислительных блоках станет возможным также на пятом такте выполнения второй итерации в этих блоках. Выполнение

третьей итерации в первом и пятом вычислительных блоках начнется по окончании пятого такта 2-й итерации в этих блоках, тем самым эти блоки будут отставать от четных на два такта, а от третьего и седьмого - на

один. Начало четвертой итерации в четвертом, шестом и восьмом вычислительных блоках совпадает с пятым тактом вычислений третьей итерации в этих блоках. Второй, третий и седьмой блоки начнут выполнение

этой итерации через такт, а первый блок задержится еще на один такт. Часть выходных отсчетов первой группы Yie , Yi4 , Yts1 появится на 15-ом такте обработки первой группы входных отсчетов. Отсчеты Yi21,

YII , Yi3 - на шестнадцатом, отсчеты Ye1, Ye , Yin , Yy1 - на семнадцатом, отсчеты . Ya1, Ys , Yg1 - на восемнадцатом, отсчет Yr - на девятнадцатом/Запись выходных отсчетов в регистры результатов вычислительных блоков позволяет компенсировать разброс во времени их формирования. Начало реализации вычислений первой итерации для второй группы входных отсчетов во асех вычислительных блоках совпадаете пятым тактом заключительной итерации обработки первой группы входных отсчетов. Начиная с этого момента времени, заканчивается режим втягивания процессора и далее все вычислительные блоки

функционируют с неизменным сдвигом начала вычислений в очередных итерациях, тем самым процессор переходит в стационарный режим (фиг. 10). По сигналу Стоп на входе 7 устройства управления прекращается генерация последовательностей управляющих сигналов, элементы процессора переходят в исходное состояние. Поочередному сигналу Пуск работа процессора возобновится по выше описанному алгоритму.

Формула изобрете ни я 1. Процессор цифровой обработки сигналов, содержащий N вычислительных блоков (где N - размерность преобразования) и блок синхронизации, N групп выходов которого соединены с группами управляющих входов соответствующих N вычислительных блоков, первый информационный выход К- го (К 1, N/2) вычислительного блока соединен с первыми информационными входами 2К-го и (2К-1)-го вычислительных блоков, первый информационный выход M-го (М N/2 + 1.N) вычислительного блока соединен с вторыми информационными входами (2М -N/2)-ron(2M -N/2 + 1)-го вычислительных блоков, причем каждый вычислительный блок содержит четыре входных регистра, доз коммутатора, первый умножитель, первый сумматор-вычитатепь и дэа буферных регистра, причем информационные входы первого и второго входных регистров явля- ЕОТСЯ соответственно первым и вторым информационными входами вычислительного блока, первые выходы второго и третьего входных регистров соединены соответственно с первым и вторым информационными входами первого коммутатора, первый выход которого соединен с первым входом лераого умножителя, вьгход которого соединен с информационным входом первого буферного регистра, первые выходы первого и четвертого входных регистров соединены соответственно с первым и вторым информационными входами второго коммутатора, первый выход которого соединен с первым информационным входом первого суммато- ра-вычитателя, выход которого соединен с информационным входом второго буферного регистра, выход которого соединен с ifpSTMw информационным входом второго коммутатора, сходы синхронизации с первого по четвертый входных регистров, первого и второго буферных регистров, соединенные между собой, управляющий вход первого коммутатора и первый управляющий вход второго коммутатора, второй управляющий вход второго коммутатора и управляющий вход первого сумматора-вы- читателя являются соответственно с первого по девятый управляющими входами группы вычислительного блока, отличающийся тем, что, с целью повышения производительности, он дополнительно содержит блок регистров, а каждый вычислительный блок дополнительно содержит узел формирования коэффициентов преобразования, третий коммутатор, второй умножитель, второй сумматор-вычитатель, два выходных регистра и с третьего по шестой буферные регистры, причем информационный вход блока регистров подключен к информационному входу процесса, первый и второй входы синхронизации блока регистров подключены соответственно к первому и второму выходам блока синхронизации, первый и второй выходы блока регистров подключены соответственно к третьему и четвертому информационным входам вычислительных блоков, второй и третий информационные выходы которых образуют группу информационных выходов процессора, третий и четвертый информационные входы каждого вычислительного блока подключены к информационным входам соответственно третьего и четвёртого входных регистров, выходы первого и второго сумматоров-вычитателей образуют первый информационный выход вычислительного блока, второй и третий информационные выходы которого являются соответственно выходами первого и второго выходных регистров, информационные входы которых подключены к выходам соответственно первого и второго сумматоров-вычитателей, выход второго сумматора-вычитатёля подключен к информационному входу третьего буферного регистра, выход которого соединен с четвертым информационным входом второго коммутатора, пятый и шестой информационные входы которого подключены к вторым выходам соответственно первого и четвертого входных регистров, второй выход второго коммутатора соединен с первым информационным входом второго сумматора-вычитатёля, вторые информационные входы первого и второго сумматоров-вычитателей соединены соответственно с первым и вторым выходами третьего коммутаторов, второй выход первого коммутатора соединен с первым входом второго умножителя, выход которого соединен с информационными входами четвертого и пятого буферных регистров, выходы которых соединены соответственно с первым и вторым информационными входами третьего коммутаторов, третий и четвер- тый информационные входы которого соединены с выходами соответственно пер- . вого и шестого буферных регистров, информационный вход шестого буферного регистра соединен с выходом первого умножителя, третий и четвертый информационные входы первого коммутатора соединены с вторыми выходами соответственно второго и третьего входных регистров, вторые входы первого и второго умножителей соединены соответственно с первым и вторым выходами узла формирования коэффициентов преобразования, вход синхронизации третьего буферного регистра соединен с

шестым управляющим входом группы вычислительного блока , соединённые между собой управляющий вход узла формирования коэффициентов преобразования, первый управляющий вход третьего коммутатора, входы выборки первого, четвертого пятого и шестого буферных регистров и управляющий вход второго сумматора;вычитателяявляются ; десятым управляющим входом группы вычислительного блока, соединенные между собой первый вход синхронизации узла формирования коэффициентов преобразования и входы синхронизации пятого и шестого буферных регистров являются одиннадцатым управляющим входом группы вычислительного блока,второй управляющий вход третьего коммутатора подключён к восьмому управляющему входу группы вычислительного блока, блок синхронизации четвертого буферного регистра подключен к пятому управляющему входу группывычислительного блока, двенадцатый управляющий вход группы которого подключен к второму входу синхронизации узла формирования коэффициентов преобразования, входы выборки и входы синхронизации первого и второго выходных регистров являются соответственно с тринадцатого по шестнадцатый управляющими входами группы вычислительного блока, входы пуска и останова блока синхронизации являются одноименными входами процессора.

3}

4J/

in

Ш.8

ш

фие.З

9tfr.$:

L. .

16668U

Is

8 Web iet

Г jfc в.-.-™

4

7 A- & , „

t a fg,,,........ .. fcI с .

4Jif -- j,I5.JE | rir-

«a----------,--------- --.---1----------:-----

Sp Ztf

It

Јfe--« --- 8g | ,Ј-y«---в--- -у

л&Тг1Г : Л12г}г- 1,

. jr. +.,. & Jy i y..:... - v

tfrir17 : Фг- v f.

,v

&

-I---fK. i f v--i----Av- &

j fcJbrV

-yjL-- У .и44гт /,

irtaoyuiiuuuuuuinnnrinruuuuuuinn

jiT

Я 9 Jn0l Zf

Г и:

m

Sp Ztf

It

,v

/f If

«

iЈ

1

1666811

Я 6

т

ТдО

зз

3

35

1 8 16 24 ПППППППППППППППППППППППППППМ

1

I

JL

JL

ппппдппп, п

Фи г. 11

ппппдппп, п

JL

31

ЛШ Ш5 ЯШ Ш1

Ж1

я&

95

35 №86

№

№ 107

ГЦ Т 7J

явю. mi

и

35

56

51

И 61

59

36

60 58 61 Ш 63

т

55

75,7

Фиг. И

| Патент США № 3662161, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Обработка сигналов микропроцессоров | |||

| Экспресс-информация,серия Вычислительная техника, 1975, № 7 | |||

| Авторское свидетельство СССР №1146685, кл.СОб F 15/332, опублик | |||

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

Авторы

Даты

1993-01-23—Публикация

1990-04-17—Подача