которых соединены с выходами соот- . ветственно первого и второго блоков постоянной памяти, третьи входа первого и Второго коммутаторов соединены с выходами соответственно второго и третьегб блоков оперативной памяти, четвертые.входа первого и второго коммутаторов соединены с выходами соответственно первого блока оперативной памяти и первого регистра, управляющие входы кс 1мутаторов соединены с восьмым выходом регистра микрокоманд и объединены с входами первого и второго элементов И, выходаа первого и второго коммутаторов соединены с информационными входами соответственно первого и второго сдвигателей, входы числа сдвигов которых соединены с седьмым выходом регистра микрокоманд, выходы первого и второго сдвигателей соединены с первыми информационными входами соот ветственно первого и второго сумматоров-вычитателей, вторые информационные входы которых соединены с выходами соответственно второго и третьего регистров, выходы знакового разряда результаты первого и второго сумматоров-вычитателей соединены с входами соответственно первого и второго регистров сдвига, исполнительные входы которых соединены соответственно с пятым и шестым выходами формирователя управляющих импульсов, седьмой выход которого соединен с входами: записи четвертого и пятого регистров, а шестой, седьмой, восьмой входы формирователя управляюиих импульсов соединены с . девятым, (есятым и одиннадцатым выходом регистра микрокоманд, двенадцатый и тринадцатый выходы которого соединены с первыми входами соответственно первого и второго формирователей адреса, выход переполнения второго формирователя адреса соединен с входом установки единицы первого триггера блокировки, а выход переполнения первого счетчика соединен с входом установки единицы второго триггера блокировки, входы установки нуля обоих триггеров блокировки соединены с первым управляющим входом устройства, выходы первог и второго триггеров блокировки соединены с блокирующими входами соответственно первого и второго элементов И, выход второго элемента И соединен с входом записи-считывания второго и третьего блоков оперативной памяти/ выход первого элемента И соединен с входом записи-считывания первого блока оперативной памяти, при этом информационные входаа четвертого и пятого регистров соединены с информационными входами соот-ветственно третьего и второго регистров, выходы первого и последнегоразрядов пер- . вого и второго регистров сдвига соединены соответственно с пе15вым, вторым, третьим и четвертым входами блока формирования кода операций, пятый вход-которого соединен с четырнадцатым выходом регистра микрокоманд, а первый и второй выходы блока формирования кода операций соединены с кодовыми входами соответственно первого и второго сумматоров-вычитателей, кроме того, выход первого счетчика соединен с вторыми входами форютрователей адреса и пятым входом формирователя кода операций.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для быстрого преобразования Фурье | 1988 |

|

SU1524066A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU883897A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Параллельный процессор | 1985 |

|

SU1315989A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Арифметическо-логическое устройство для обработки десятичных данных | 1984 |

|

SU1244660A1 |

| Устройство для интерпретации выражений языков программирования | 1982 |

|

SU1078432A1 |

| Процессор | 1986 |

|

SU1332328A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

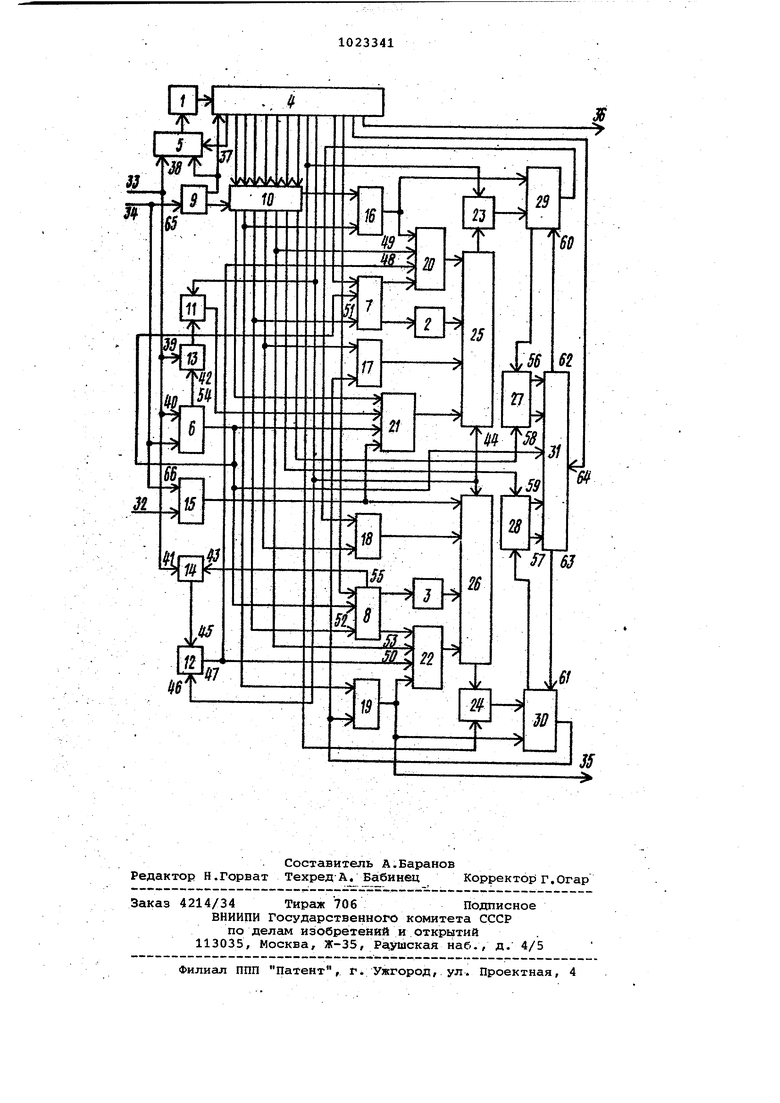

АНАЛИЗАТОР СПЕКТРОВ, содержащий первый регистр, информационный .вход которого является информационным входом устройства, выход первого регистра соединен с информационным входом первого блока onieративной памяти, адресный вход которого, соединен с выходом первого счетчика,второй и третий блоки оперативной памяти, информационные входы . которых соединены с выходами соот-. ветственно второго и третьего регистров , адресные входы второго и третьего блоков оперативной памяти соединены с первыми выходами соответственно йервого и второго форми- . рователей адреса, вторые выходы которых соединены с входами соответственно первого и второго блоков постоянной пад1яти, первый и второй сумматоры- вычитатели , выходы которых соединены с информационными входами соответственно второго и третзьего регистров, второй счетчик выход которого соединен с входом третьего блока постоянной памяти, выход которого соединен с входом регистра микрокоманд, первый выход котррого соединен с первым входом установки нуля второго счетчика, вход записи регистра микрокоманд соединен со счетным входом второго счетчика и с перяьам выходом генератора рабочих частот, второй выход которого соединен с первым входом формирователя управляющих импульсов, второй, третий,- четвертый и пятый входы которого соединены соответственно с: вторым - третьим, четвертым и пятым выходами регистра микрокоманд, первый выход формирователя управляющих им.пульсов соединен с исполнительным входом nepBoriD блока оперативной памяти, второй выход формирователя управляющих импульсов соединен с входами записи второго и третьего регистров, третий выход формирователя управляющих импульсов соединен с исполнительными входами первого и второго формирователей адреса, четвертый выход форьшрователя упт равляювдих импульсов соединен с исО) полнительными входами второго и ; , третьего блоков оперативной памяти, при этом первый управляющий . устройства соединен с входом уста. новки нуля первого счетчика и с . вторым входом установки нуля второго счетчика, второй управляющий вход устройства соединен с входом записипервого регистра, со счетным входом первого счетчика и входом запуска генератора рабочих частот, выход третьего регистра является йнформационньш выходом устройства, а шестой выход регистра микрокоманд является , выходом сопровождения информации, :Р т л и ч а ю щи и с я тем, что, :С целью упрощения устройства и расширения функциональных возможностей за счет вычисления амплитудного-и фазового спектра и весовой обработки, в него введены два сдвигателя, два коммутатора, два регистра сдвига, два триггера блокировки, два элемента И, блок формирования кода операций , четвертый и ПЯ.ТЫЙ регистры, ВЫХОДЫ которых соединены с первыми входами соответственно первого и второго коммутаторов, вторые входы

. - Изобретение относится к средствам цифровой вычислительной техники, предназначено для получения амплитудного и фазового спектра Фурье на скользяйгел отрезке времени и может использоваться при. решении задач первичной обработки низкочастотных дискретных сигналов.

Известно устройство для выполнения прямого преобразования Фурье, осуществляющее вычисление комплексного спектра между вводрм отдельных дискретных значений преобразующего сигнала. Это устройство содержит аналого-цифровой преобразователь, три блока памяти, предназначенных для накопления исходных отсчетов и хранения синусной и косинусной компонент спектра, умножитель и сумматор комплексных чисел . .:

Наиболее близким к предлагаемому является анализатор спектра , который после каждой новой выборки дискретного значения преобразуемого исходного сигнала обновляет коэффициенты Фурье. Составляющие части

(элементы) ЭТОГО устройства представлены двумя группами. . Первая группа содержит первый регистр, информационный вход которого является информационным входом устройства, выход первого регистра .

соединен с йнформационн:ым входом

первого блока оперативной памйти, 1 адресный вход которого.соединение выходом первого счетчика, второй и третий блоки оперативной памяти информационные входы которых соединены с выходами соответстбенно второго и третьего регистров, адресные входы - с первым выходом соответственно первого и второго формировате лей адреса, вторые выходы которых соединены со входами соответственно первого и второго блоков постоян ной памяти, первый и второй сумматор вычитатель, выходы которых соединены с информационными входами соответственно второго и третьего регистро второй счетчик, соединенный выходом с третьим блоком постоянной памяти, выход которого соединен с регистром микрокоманд, первый выход которого соединен с первым входом установки нуля второго счетчика, вход записи регистра микрокоманд соединен со счетным входом вт.ррого счетчика и с первым, выходом генератора рабочих ча тот, второй выход которого соединен с первым входом формирователя управляющих импульсов , второй , третий, Четвертый.и пятый входэ которого сое динены с соответствующими выходами регистра микрокоманд, первый выход формирователя управляющих импульсов соединен с исполнительньм входом первого блока оперативной памяти, второй выход - со входами записи вто рого и третьего регистров, третий выход - с исполнительными входами, первого и второго формирователей адреса, четвертый выход -.с исполнительными входами второго и третьего блоков оперативной памяти, при этом первый управляющий вход устройства соединен с входом установки нуля первого счетчика и со вторым входом установки нуля второго счетчика. Второй управляющий вход устройства соединен со входом записи первого .регистра, со счётньам входом первого счетчика и входом запуска генератор а рабочих частот, выход третьего регистра является информационным Выходом устройства, а шестой выход регистра микрокоманд - выходом сопровождения информации. Вторая группа содержит два сумматора-вычитателя и четыре умножителя . выход первого умножителя соединен с первым входом первого сумматоравычитателя, выход второго - с вторым входом того же сумматор.а-вычитателя выходы третьего и четвертого - соответственно с первым и вторым входами второго сумматора-вьлчитателя, выход первого блока постоянной памяти соединен с первыми входами первого и четвёртого умножителей, выход второго блока постоянной памяти - с первыми входами второго и третьего умножителей, вторые входы первого и Третьего умножителей соединён с выходом трет ьего- сумматора-вычитателя, первый и второй входы которого соединены с выходами соответственно первого блока оперативной памяти и четвертого сумматора-вычитателя, первый и второй входы последнего в свою очередь соединены с выходами соответственно первого блока оперативной памяти и первого регистра, при этом выход второго регистра является вторым информационным выходом устройства 2... : Известные устройства характеризую ются невозможностью получать с их помощью амплитудный и фазовый спектры, проводить весовую обработку и сложностью. Жроме того, устройства ограничиваются вычислением только комплексного спектра Фурье,, хотя для многих приложений требуется выполнять весь комплекс вычислений. Целью изобретения является упро- щение устройства и расширение функциональных возможностей за счет вы-, числения с1мплитудного и фазового . . спектра и весовой обработки. Поставленная цель достигается тем, что в анализатор спектров, содержащий первый регистр, информационный вход которого является информационным входом ус-тройства, выход первого регистра соединен с информационным в.ходом первого блока оперативной памяти, адресный вход которого соединен с выходом первого счетчика, второй и третий блоки оперативной памяти, информационные входы которых соединены с выходами соответственно второго и третьего регистров, адресные входы второго и третьего блоков оперативной памяти соединены с первыми выходами соответственно первого и второго формирователей адреса, вторые выходы которых соединены с входами соответственно первого и второго блоков постоянной памяти, первый и второй су1« аторы-вычитатели, выхода KOTOfftJX. соединены с информационными входами соответственно второго И третьего регистров, второй счетчик, выход которого соединен с входом третьего блока постоянной памяти, выход которого соединен со входом регистра микрокоманд, первый выход которого соединён с первым входом установки нуля втсфого счетчика, вход записи регистра Микрокоманд соединен со счетным входом второго счетчика и с первым выходом генератора рабочих частот, второй выход которого соединен с первым входом формирователя управляющих импульсов, второй, третий, четвертый и пятый входы которого соединены соотватетвённо с вторым, третьим, четвертым и пятым.выходами регистра микрокоманд, первый выход формирователя управляющих импульсов соединен с исполнительным входом пер вого блока операт.ивной памяти, второй выход формирователя управляющих ИМПУЛЬСОВ соединен с входами записи второго и третьего регистров, третий выход формирователя управляющих иМ пульсов.соединен с исполнительными входами первого и второго формирователей адреса, четвертый выход фор мирователя управляющих импульсов соединен с исполнительными входами второго и третьего блоков оперативной памяти, при этом первый управ-, ляющий вход устройства соединен с входом установки нуля первого счетчику и с вторым входом установки ну ля второго счетчика, второй управляющий вход устройства соединен с входом записи первого регистра, со счетным входом первоз о счетчика и входом запуска генератора рабочих частот, выход третьего регистра является информационным выходом уст ройства, а шестой выход регистра микрокоманд является. Выходом сопровождения информации, введены два сдвигателя, два коммутатора, два регистра сдвига, два триггера блокировки, два элемента И, блок формирования кода операций, четвертый и пятый регистры, выходыкоторых : соединены с первыми входами соответственно первого и ВТОРОГО коммутаторов, вторые входы которых соеди нены с выходами соответственно первого и второго блоков постоянной памяти, третьи входы первого и втор го коммутаторов соединены с выхода и соответственно второго и третьего блоков оперативной памяти четверты входыпервого и второго коммутаторов соединены с выходами соответственно первого блока оперативной памяти и первого регистра, управляющие входы коммутаторов соединены с восьми выходами регистра микрокоманд и объединены с в содами первого и второго элементов И,выходы первого и втрро го коммутаторов соединены с информационными входами соответственно первого и второго сдвигателей, входаг числа сдвигов которых соединены с седьмым выходом регистра микрокоманд выходы первого и второго сдвигате-. лей соединены с первыми информационмыми входами соответственно первргб и второго сумматоров-вычитателей, вторые инфррмационные входы которых соединены с выходами соответственно Второго и третьего регистров, выходы знакового разряда результата первого и второго сумматоров-вычитателе соединены с входами соответственно первого и второго регистров сдвига, исполнительные входы которых соединены соответственно с пятым и шестым выходами формирователя управляющих импульсов, седьмой выход которого соединен с входами записи четвертого и пятого регистров, а шестой, седьмой, восьмой входы формирователя управляющих импульсов соединены с девятым, десятым и одиннадцатым выхо дом регистрамикрокоманд, двенадцатый и тринадцатый выходы которого соединены с первыми входами соответственно первого и второго формирователей .адреса, выход переполнения второго формирователя адреса, соединен с входсми устсшовки -единицы первого триггера блокировки, а выход переполнения первого счетчика соединен с входом установки единицы второго триггера блокировки, ,..., входы установки нуля обоих триггеров блокировки соединены с первым управляющим входс)м устройства, выходы первого и второго триггеров блокиров-. ки соединены с блокир пощими входами соответственно первого и второго элементов И, выход второго элемента И соединен с входом записи - считывания второго и третьего блоков оперативной памяти, выход первого элемента И соединен с входом записисчитывания первого блока оперативной памяти, ,при этом информационные входы четвертого и пятого регистров соединены: с информационными входами соответственно третьего и второго регистров, вьгходы первого и последнего разрядов первого и второго регистров сдвига соединены соотнетственно с первым, вTOptaM, третьим и четвертазм входами блока формирования кода операций , пятгай вход которого соединен с че-шрнадцахьам выходом регистра микрокоманд, а первый и второй выходы блока формирования кода операций соединены с кодовыми входами соответственно первого и второго сумма- торов-вычитателей, кроме того, выход. первого счетчика соединен со вторыми входами формирователей адреса и с шестым входом формирователя кода ойёраций. . На чертеже представлен анализатор спектров. .. Анализатор состоит из блоков постоянной памяти 1-3 ,регистра микрокоманд 4, счетчиков 5 и 6, формирователей адреса 7 и 8, генератора, рабочих частот 9, формирователя уп рйвляющих импульсов 1C , элементов И 11, 12,триггеров блокировки 13 и 14 1 егистров 15, 19, блоков оперативной памяти 20 - 22, сдвигателей 23 и 24, коммутаторов 25 и 26, регистров сдвига 27 и 28iсумматоров-вычитателей 29 и 30, блока формирования. кода операций 31, информационного входа устройства 32, управляющих входов устройства 33 и 34, инфо мационного в лхода устройства 35, вы хода сопровождения информации 36, входов установки иуля 37, 41, входов установки единй1;ы 42 и 43/ управляющих входов косвиутаторов 44, блокирукмцих входов элементов И 45, входов элементов И 46, выходов эле ментов И 47, входов записи-считывания 48 и 49, исполнительных входов 50 - 53, выходов переполнения 54 и 55, выхода первых р азрядов сдвига щих регистров 56 и 57, выходов последних разрядов регистров сдвига 58 и 59, кодовых входов суидалатороввычитателей 60 и 61, выходов блока формирования кода операции 62 и 63, кодового входа блока формирования кода операций 64, входа запуска 65, входа записи 66. Анализатор .спектров представляет собой специализированное вычислительное устройство с микропрограммным управлением, ориентированное на выполнение следующей, совокупности задач первичной спектральной обработки . Накопление и хранение N текущих значений дискретного действительного входного сигнала x(n-t ),х (п-2 х(п-К) в блоке оперативной памяти 21, где VI - TeKsmw отсчет времени..,, Хранение иобновление N/2 комплек ных значений дискретного преобразов ния Фурье (ДПФ)У,Ло),Хи11),...,Ху,Ш2-О в блоках оперативной памяти 20 и 21 , ЗначенияX ijji о ЩГ Ьвязаны со входными значениями входного сигнал соотношениями }-j.( И , на основе которого работает известный аналог. Значение ДПФ после получения по информационному входу 32 в регис 15 нового значения Xi. и)обновляет Xyj по известной рекуррентной формуле (1)-Сх(у,)-х(у,-м)ехр (i } i о,и Проведение весовой обработки вхо ной прследрвательностИ с помо11 ьЮ ок на Хэммирга ... /тг9 -.- l)-o,.(),,N, что оеуйаствляется та спектральной обларти над совокупностью храни1ьалх щ- блоках оперативной памяти коэффи , Фурье по .е Vi 1)05х„ ДО о., (1И) riX (IM ),М 0,-1; при этом применяется: ЧмН)--Х,(0,Х«,(н|2)-Х;,{Н|4-11), исходя из свойств спектра действительного сигнала. Над Хь,-(1)проводится ойерация выделения 1и|одуля и фазы с Помощыб Волдеровских процедур. При этом текущая фаза вследствие с принятым преобразованием Фурье вычисляется с известной методической ошибкой, связанной с периодическим смещением базисных функций (см. аналог, что. не мешает однако дальнейшему использованию фазового спектра в большинстве приложений. Возможность реализовать-в одном специализированном устройстве, практически, всех задач спектральной обработки удается без применения умножителей, что существенно уменьшает оборудование. Все возникакицие операции умножения выполняются с помощью сдвигателей и сумматоров. Эти же блоки используются и при вычислении модуля и аргумента комплексных чисел с привлечением Волдеровской процедуры вычисления функций: . ,. fcorct (,U)/./ Анализатор спектров- работает следукчцим образом. Все устройство включает функциональную часть и управлякнцую часть. В функциональИую часть входят регистр, счетчик, блоки памяти, сдви-гатели, сумматоры-вычитатели, KONtt«yтаторы, блоки формирования адреса и кодов операций. В управляющую часть входят блок постоянной памяти, где хранятся микpoKcoKiaHjts;), счетчик адреса, регистр микрокоманд, генератор рабочих частот и формирователь управляющих импульсов . Сюда же входят два триггера блокировки и вентильные схемы. В начале работы устройства, после его включения, подается сигнал по управляющему входу 33, который устанавливает в ноль счетчики 5 6 и триггеры блокировки -l и 14. Устройство работает циклич€ ски. В каждом цикле выполняется вс.я после- довательность перечисленных алгоритмов . За начало, цикла принимается сигнал по управлякнцему входу 34, по которому происходит запись нового дискретного значения. X(i) поступаю-, щего.по информационному входу устройства 32 в регистр 15. Далее увеличивается значение счётчикаб на-единицу, и по входу запуска 65 включается генератор рабочих частот 9. В самом начале работы устройства на входах счетчика 6 действуют сигнал установки нуля 40 и сигнал ПО счетному входу счетчика. Счетчи в этом случае устанавливается в нул и не реагирует на сигнал со счетного входа. В процессе работы устройства посл довательво изменяется содержимое счетчика 5 и из блока постоянной памяти 1 в регистр микрокоманд 4 . переписываются очередные микрокоман Отдельные, выходы регистра микрокоманд 4 непосредственно доносят до функциональных частей управляющие коды 1колы операций в сумматоры-вычитатели, число сдвигов, коды коммутаторов , коды формирователей адре сов . Другие выходы регистра 4 управляют отдельными выходами формиро вателя управляющих импульсов 10, который представляет собой набор . элементов:И, которые пропускают, ли не пропускают соответствующие им- . пульсные сигналы с выходов генерато ра рабочих частот. С помощью импуль сов , пропускаемых на нужные выходы формирователя управляющих сигналов/ осуществляется запись в регистры 16-19, исполнение записи считывания в блоках оперативной памяти, изменение адресов формирователей ад реса 7 и 8, сдвиг информации в регистрах 27 и 28. Блок оперативной памятки 21 хранит .N текущих значений входных отсчетов записывая новое значение -на самое старое в этих М отсчетах, т.е. ) на место ). Это осуществляется ци1 личным изменением адреса, который формируется.счетчиком 6. На Н перио дов работы устройства до первого переполнения счетчика считывание ин формации из блока оперативной памяти 21 осуществлять нельзя, в него только можно записывать. Это обеспечивается подачей на вход запись-считывание блока оперативной памяти -только низкого уровня /кoд записи с вьзхода элемента И 11, ввиду присутствия на одном из ее входов низкого запрещающего сигнала с выхода триггера блокировки 13. Как только после N циклов работы счетчик б пере полнится, Т1 иггер установится в еди ничное состояние и элемент И 11 открывается. Код считывания (.высоки уровень элемента 11) образуется в случае, когда на управляющем входе коммутатора установлен номер входа, куда подключен выход блока оперативной памяти 21, например, номер один. В этом.случае, всегда, когда в первом разряде номеравхода коммутатора единица .и этот разряд под- ключен к входу элемента и 11,можно производить считывание из блока опе ративной памяти 21. Блокировка считывания из этой памяти необходима на N периодов, ввиду того, что пос ле включения питания в ней хранится ложная информация. Формирователи адреса 7 и 8 для блоков оперативной памяти 20 и 21 представляют из себя постоянную память, подключенную к установочным входам счетчиков адреса. Можно либо считать из постоянной памяти адрес, записав его в счетчик, либо увеличить ранее установленный адрес на единицу. Устанавливаемые адреса зависят как от номера цикла ( ,-)), так и кода, поступающего из регистра 4 микрокоманд. Для реального анализатора спектров при N 32 объем постоянной памяти не превыиает 2К бит (одна интегральная схема). Блоки оперативной памяти 20 и 22 имеют также как и блок 21 блокировку Считывания, только на один первый цикл работы устройства, триггер блокировки 14 устанавливается в единич-ное состояние и открывает тем салвлм элемент И 12, который срабатывает, когда на его входах 46 появляется номер входа коммутатора, к которому подключены блоки 20 и 21, например, третий номер - первый и второй двоичный разряд номера равен единице. Необходимость блокировки считывания та же, что упоминалась ранее. Сумматорыг-вычитатели 29 и 30 для выполнения всех указанных алгоритмов должны осуществлять следующие операции; сложение, вычитание двух чисел, сложение с нулем, обнуление выхода. Сумматоры-вычитатели управляются подачей соответствующих кодов на кодовые входы 60 и 61, куда они поступают H3i блока формирования кода операций 31. Этот блок 31 представляет собой ко 1бинационную схему с постоянной памятью. Из регистра микрокоманд 4 по входу 64 поступают коды операций для каждого сумматора.вычитателя и код варианта исполнения, который либо может в зависимости от номера цикла работы устройства, поступающего с выхода счетчика 6, считать из постоянной памяти свои коды операций для сумматоров-вычитателей, хранимьлх в постоянной памяти по адресу номера счетчика 6, либо инвертировать поступившие коды из регистра микрокоманд, если в коде варианта исполнения по указанному номеру выхода 56-59 поступает единица из сдвиговых регистров 27 и 28. В регистрах 27 и 28 при. выполнении задачи вычисления модуля комплексных чисел по формулам Волдеровских процедур запоминается набор знаков промежуточных результатов которые используются как для этой задачи, так и для следующей - вычигление фазы (.аргумента- кс тлексного числа). Объем постоянной памяти бл формирователя кода операций не пре вышает для Н 32 2К битт. . Особенности работы устройства при выполнении отдельных алгоритмо Текущие значения спектраУ),(0хранят в блоках оперативной памяти: в бл ке 20 - мнимая часть спектра, в бл ке 22 - действительная часть спект ра. В регистр 15 записывается ново значение Xtvi) и поступает на первый вход коммутатора 26, значение У (и считывается из блока оперативной памяти 21 н поступает также на пер вый вхрд только другого коммутатора 25. Операция yмнoжeнияi(.v -7 0; -нlle%p(-i в прямую не выполняется. Чтобы существенно уменьшить объем вычислеНИИ косвенного умножения, указанно произведение можно записать следз ю щим образом : ,)co6((--X-i/ tWsi«(2ft:-)-jtif AX(siV(2K («.) .) V.V,.V..,H; ; З.-Ц целая часть числа, «a-N- tN,- - -Т2.ПНГ J ТГ L -М А;|И . Принимают различные значения не считая нуля и значения N/4. В устройстве сначала формируются Н|4-1 значения произведения ХЫИ«(|5).И7ЕЗ, , которые заносятся, целиком в блоки оперативной памяти 20 и 22. Далее путем назначения адреса А и Aj / знака V.-l) и ( всегда можно считать из них требуемое произведение либоf01uin () ч /1 MU)sih(); , Адреса и знаки С операция сложёния, либо вычитания для сумматоров вычитателей) формируются соответственно на выходах формирователей адресов 7 и 8 и блока формирования кода операций 31 в зависимости от ( номера цикла VI , поступающего из счет чика 6, номера , поступаюиего из .регистра микрокоманд 4, по привеi денным формулам. Однако эти формулы раскрываются на этапе проектирования, когда их результаты записываются в постоянные памяти блоков формирователей адреса 7 и 8 и блока фор;мирования кода операций 31. Формирование М|4 - 1 произведений Г 7 iKO 1 (.O9i« N производится на сумматорах-вычитателях 29, 30 и сдвигателях 23 и 24. При этОм на сумматоре-вычитателе 29 и сдвигателе 23, на сумматоре-вычитателе 30 и сдвигателе 24 параллельно вычисляют4U-vsb.«(XWsi«(fJ затем на одной из групп уже определяется разность. XWsi«((,.N) Такое вычисление позволяет снизитьтребования по числу разрядов промежуточных вычислений и при этом не на|Капливэть ошибки, что важно, так как анализатор спектров работает в непрерывном режиме и внесение ошибок в рекуррентную формулу не допустимо из цикла в цикл. Для реальйых 14 W 32} можно проводить вычисления в 16-ти разрядной сетке и осуществить формирование всех семи произведений за 25 операций сложениё-вычитание-сдвиг-запись, далее за 24 операций считывание-ело-жение-вычитание-запись окончательное формирование, j u)C. Итого, практически, за 50 коротких операций выполнено 7 умножений, что достигается за счет последовательно параллельного умножения только на те разряды, которые отличны от нуля при эффективном кодировании. После выполнения умножений выполнить обновление спектра по рекуррентной формуле не представляет трудное-: ти; следует из блоков оперативной .памяти выбирать старое значениеЙйУу,) :йЛ1ужное проиэведение- ХС б и (( и выполнять операцию (-4) М)в сумматоре-вычитателе 30, аналогично .для мнимых частей в сумматоре-вычитателе 29. После обновления таким образом спектра устройство переходит в режим выполнения весовой обработки по Хэммингу в спектральной области. Каж;Дое полученное значение (4) остается в регистрах 16-19; в регистрах 19 и 17 ;;;: ) регистрах 18 и 16 - wiXyi., t-l)|B первс м разряде регистра 27 - знак у„ Xy,4.-iW Организуется Волде1 овская проце ура вычисления;i/n) бе коррекции деформации. Результат через требуемое число итераций получается в регистре 19 и.выдается по информационному выходу 35 из устрой ства г при одновременной выдаче по выходу сопровождения информации 36 сигнала сопровождения. После всех итераций в регистре 2 хранятся все значения знаков промежуточных вычислений, которые могут использоваться для вычисления ttytttf ч| для чего происходит , 1 суммирование хранимых в блоках постоянной памяти 2 и 3 требукясих koH CTaHTCfyxigfCft-J) / j - номер итерации Волдеровской процедуры, /j -I, j , rjcie f - число двоичных разрядов. Два блока постоянной памяти 2 и J и два регистра 27 и 28 взяты для возможности распараллеливать вычисления фазы, например, хранить все константы с frf/4 в блоке 2, а с js iTf в блоке 3, тем самым уменьшается вдвое л время вьзчисления фазы. Рассмотренный анализатор спектра в известных рамках может допускать доводку микропрограмм реализации конкретных алгоритмов. Для самых про: стейших машинных вариантов, без ухищрений весь набор алгоритмов может быть выполнен за 230 периодов . работ устройства, кото1мле складываются; обновление спектра - 100 периодов, весовая обработка - 32, вычисление амплитуды - 96. При вы-, числении фазы общее число периодов увеличится на 170. Таким образе предлагаемое устройство позволяет реализовать весь набор задач формирования спектров.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3778606, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

| ; - | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Анализатор спектра фурье | 1975 |

|

SU560232A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-06-15—Публикация

1982-01-18—Подача