00

GO

|Ы

со

Ј

|4 i

™

Предполагаемое изобретение относится к области передачи цифровой информации и может найти применение в устройствах приема телеметрической информации, поступающей в виде непрерывного потока данных с относительной фазовой манипуляцией. .

Цель изобретения - повышение точности определения частоты передачи цифровой информации,

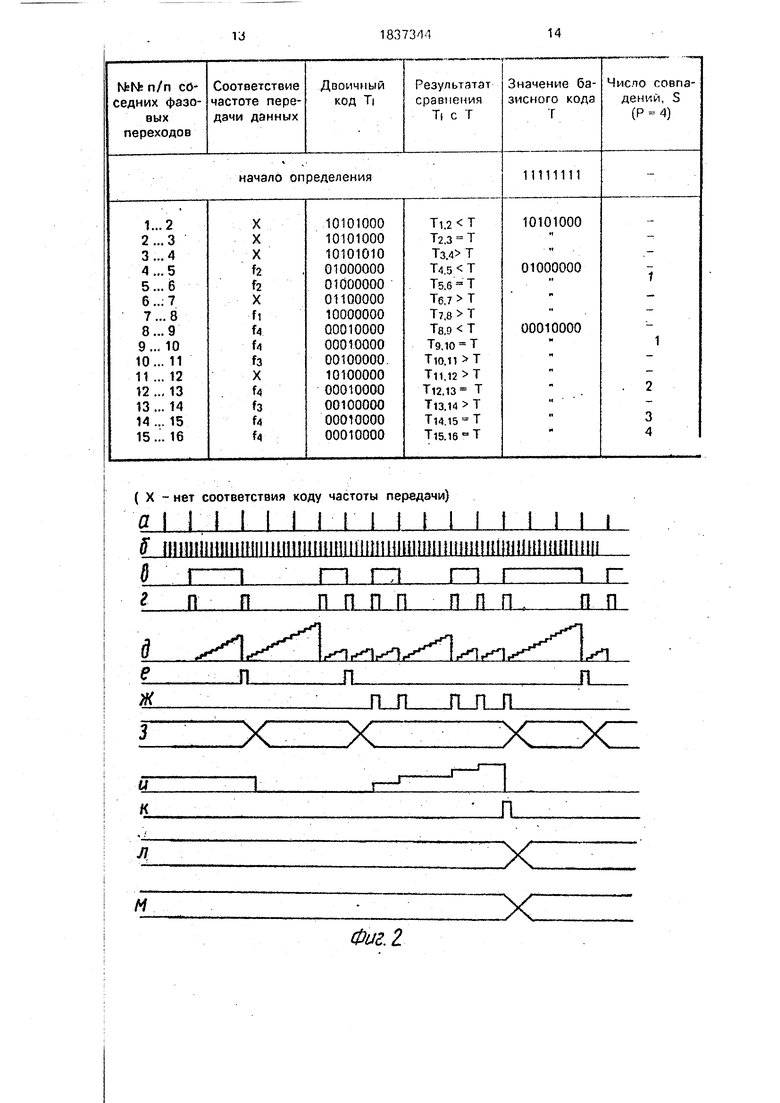

На фиг.1 приведена функциональная схема устройства для реализации предложенного способа; на фиг,2 - временные диаграммы, иллюстрирующие его работу.

Устройство для определения частоты передачи цифровой информации (фиг.1) содержит первый, второй и третий элементы 1, 2 и 3 И, первый, второй, третий и четвертый одновибраторы 4, 5, 6, 7, первый и второй элементы 8 и 9 задержки, первый, второй и третий элементы 10, 11 и 12 ИЛИ, формирователь 13 исходного базисного кода N, формирователь 14 кода порогового значения Р, генератор 15 тактовых импульсов, .триггер 16, счетчик 17 длительности, коммутатор 18, первый регистр 19, второй регистр 20, первый, второй и третий цифровые компараторы 21, 22 и 23, счетчик 24 числа совпадений S, блок 25 памяти.

Предлагаемый способ определения частоты передачи цифровой информации с от- носительной фазовой манипуляцией заключается в следующем.

В потоке данных с относительной фазовой манипуляцией фазовые переходы совпадают, с тактовой частотой следования данных перед их фазовой манипуляцией. Появление в потоке данных комбинации вида 00 вызывает появление в выходном сигнале двух фазовых переходов, временный интервал между которыми однозначно соответствует периоду тактовой частоты следования данных. Иначе говоря, в потоке данных на любой из возможных частот его передачи имеется несколько фазовых переходов, вызываемых появлением комбинации вида 00, интервал между которыми содержит информацию о частоте передаваемых данных. Предлагаемый способ основан на описанной закономерности и представляет собой совокупность операций, позволяющих найти характерные для искомой частоты интервалы между фазовыми переходами и идентифицировать полученное значение с одной из возможных частот передачи данных из заранее составленного набора.

Для этого во входном фазоманипулиро- взнном сигнале (фиг.2, в) определяют фазовые переходы путем формирования при

и

10

15

20

25

30

35

40

45

50

55

каждом изменении уровня входного сигнала (например, с уровня логической 1 на уровень лог.О, и наоборот) одиночного короткого импульса с длительностью

Т « Imin..

где rmin - длительность временного интервала между фазовыми переходами в последовательности элементов входного потока данных вида 00 на максимальной частоте.

При этом образуется импульсная последовательность, состоящая из коротких импульсов, неравномерно расположенных на временной оси (см.фиг.2,г).

В полученной импульсной последовательности измеряют временной интервал между каждыми двумя соседними импульсами путем подсчета числа импульсов тактовой частоты (фиг.2,б), расположенных между .фронтами импульсов последовательности г), фиг.2. Таким образом, по существу, измеренный временной интервал преобразует в двоичный код Т|. При этом частоту тактовых импульсов (см.фиг.2,б) выбирают из условия:

ft fmax f

где fmax - частота следоаанил символов на максимальной частоте передачи данных.

Непосредственно перед началом определения частоты передачи запоминают в качестве базисного кода Т двоичный код , где Гтах, - длительность временного интервала между фазовыми переходами е последовательности элементов входного потока вида 00 на минимальной частоте, причем гтах измеряют с использованием Fr.

Запоминание исходного базисного кода Т обеспечивает правильное определение любой из возможных частот передачи.

Полученный двоичный код Ti сравнивают с хранящимся базисным кодом Т. При этом возможны следующие соотношения:

Tj - Т

В первом случае измеренное значение Ti отбрасывается, поскольку временной интервал такой длительности не характерен даже для минимально возможной частоты.

Если Т)Т, то суммируют число совпадений Si для кода TI во избежание ложного определения частоты.

И, наконец, если , то полученный код Ti запоминают теперь в качестве базисного кода и все последующие операции сравнения с полученными Tj проводят по отношению к новому базисному коду.

Число совпадений Si двоичного кода TI . с базисным кодом Т сравнивают с некоторым пороговым значением Р, достаточным для исключения ложного вывода об истинной частоте передачи данных. В общем случае пороговое значение Р выбирают равным

p p7TiW(1)

где Pi - вероятность появления во входном потоке данных последовательности элементов вида 00, характеризующие статические свойства передаваемого потока;

2 - вероятность искажения последовательности- элементов вида 00 во входном потоке данных из-за воздействия помех в канале связи,

Вероятность Pi определяется априори на основе анализа системных параметров, обеспечивающих передачу данных (п основном из анализа структуры передаваемого потока данных). Учитывая то обстоятельст- во, что без определения частоты передачи невозможно установление тактовой, а также цикловой синхронизации (при,временном разделении каналов), данных во многих системах не передаются до установления указанных видов синхронизации. Это означает, что в линию передаются непрерывным потоком нули информации и Р) при этом равно 1. Однако предложенный способ обеспечивает определение скорости пере- дачи информации и тогда, когда по линии передается ненулевой поток данных. Тем не менее, и в этом случае всегда имеются некоторые основные характеристики потока данных, позволяющие определить Pi. На- пример, структура синхрокомбинации, которая быть выбрана такой, чтобы обеспечивать появление нескольких сочетаний элементов вида 00.

Вероятность г является системным па- раметром, определяющим качество канала связи, поэтому использование ее конкретного значения не вызывает каких-либо трудностей.

Из анализа соотношения (1) видно, что выражение, заключенное о скобки, всегда практически равно 1, учитывая реальные характеристики каналов связи ( реже . Отсюда следует, что пороговое значение Р определяется значением Pi, кото- рое при нулевом потоке данных равно 1. Таким образом, с учетом реальных характеристик и алгоритмов работы каналов передачи данных Р 2. Для других значений Pi и Р2, соответственно, изменится и Р. Напри- мер, при Р1-0,5 и РаЮ.Б.

Р

1

D3TT4I5)

Р 4 и т.д.

Таким образом, если число соипздени Si кода с базисным кодом Т, pat ным ему. fie превышает порогового значе мня Р, то процесс определения частота передачи данных продолжас- ся.

Как только для какого-либо двоичного кода TJ число его ссппадений S; оказалось рлг.жым пороговому значению Р, то это означает, что определен характерный для данной частоты передачи временной интервал. По значению указанного кода Т| (или, что то же самое, по последнему базисному коду Т) идентифицируют частоту передачи данных, поскольку заранее установлено соответствие между величинами кодов TJ и скоростями передачи информации.

Графически проиллюстрировать предлагаемый способ можно следующим образом (см.табл.1).

Как следует из табл. 1, порогового значения числа совпадений достиг код Tj, соответ- стзующий частоте передачи данных U. При этом в процессе анализа значения базисного кода изменилось трижды, было даже получено некоторое число совпадений кода Т| с Оазисным (для частоты передачи f2). По до- стнкении порогового значения РМ- была идентифицирована искомая частота передачи if,.

Для исключения ситуации, когда несмотря на полученное новое значение базисного кода Т не удается достигнуть порогового значения числа совпадений, может быть введен некоторый временной интервал анализа, по истечении которого, если пороговое значение не достигнуто, определение частоты передачи начинается с. самого начала. Указанный временной интервал, например, может быть выбран исходя из возможных частот передачи, или, исходя из конкретных, реальных характеристик систем передачи данных, упоминавшихся выше (при отсутствии синхронизации данных не передаются), может быть о:-рэничен несколькими периодами та- товой частоты для самой низкой частоты передачи. Однако такая операция не является еущестоенной, поскольку не сообщает никаких дополиительных саийс тз предлагэемому способу, хотя при необходимости и может быть использована.

На фиг.1 приведена схема устройства, реализующего вышеописанный способ. Элементы устройства могут быть выполнены с применением типовых микросхем, например, серии К564. (см.Аналоговые и цифровые интегральные микросхемы. Справочник под ред.С.В.Якубовского, М.. 1985,). Элементы 1,2,3 11 - К554ЛА7с включением нг выходе каждого элемента И- НЕ имертора 564ЛН1; одновибраторы 4...7 - 564АГ1 с подключенными к ним времяза- ающими цепочками из резисторов типа 2-23 и конденсаторов типа Б-18 (конденаторные сборки).

Элементы задержки 8, 9 могут быть выполнены на нескольких последовательно оединенных элементах К564ЛА7 (или К564ЛБ5. К564ЛН1) с четным числом эле- ентов в соединении;

элементы 10.„12 ИЛИ - К564ЛЕ5 с включением на выходе инвертора К564ЛН1;

Формирователь исходного базисного ода 13 может быть выполнен либо в виде распаянного на краю платы соединения входов коммутатора 18с контактами, уровень сигнала в которых соответствует ог.0 или 1, либо в виде набора переклюателей на два положения;

Формирователь 14 может быть выполнен аналогично формирователю 13;

генератор тактовых импульсов может быть выполнен как мультивибратор, или как последовательное соединение двух элементов типа К564АГ1 с подключением выхода второго элемента ко входу запуска первого;

триггер 16- К564ТР1;

счетчик 17 -К564ИЕ10;

коммутатор 18 - К564ЛС2;

регистры 19 и 20-К564ИР9;

цифровые .компараторы 21 ...23 - К564ИП2;

счетчик 24- К564ИЕ10;

блок 25 памяти - К573РФ20,

В исходном состоянии триггер 16 находится в положении, при котором на его выходе присутствует нулевой потенциал, закрывающий элемент 1И, счетчик длительности выведен из режима счета тактовых импульсов сигналов с выхода своего старшего разряда, регистры 19 и 20 обнулены, счётчик 24 числа совпадений обнулен, на выходах одновибраторов 4...7 присутствуют нулевые потенциалы, на выходах цифровых компараторов присутствуют нулевые потенциалы, на выходах элементов 1, 2, 3 И; 10,11,12 ИЛИ присутствуют нулевые потенциалы, на выходах формирователя 13 присутствует код порогового.числа совпадений, на адресных входах блока 25 памяти присутствует нулевой код, в соответствии с которым на выходах блока 25 памяти присутствует код, не соответствующий каком-либо коду частоты передачи данных; по остальным адресам блока 25 памяти хранятся коды частот передачи, адреса которых соответствуют кодам, пропорциональным длительности периода следования тактовой частоты передачи информации.

Устройство для определения частоты передачи цифровой информации работает следующим образом.

При подаче сигнал Пуск на вход запуска одновибратора 6 на его выходе формируетсяодиночныйимпульс, переключающий выход триггера 16 в состояние лог. 1 и устанавливающий коммутатор 18 в положение, обеспечивающее

. подключение выходов формирователя 13 исходного базисного кода ко входам параллельной записи регистра 19. Этот же импульс, задержанный посредством элемента 9 задержки во времени, проходит через элемент 11 ИЛИ на тактовый вход регистра 19. записывая в него исходный базисный код. По спаду импульса с выхода одновибратора 6 коммутатор 18 переключается в положение, обеспечивающее подключение выхода

счетчиков 17 ко входам регистра 19.

При появлении на втором входе элемента 1 А, высокого (низкого) потенциала входного фазоманипулированного (ФМ)

сигнала, на его выходе также возникает высокий (низкий) потенциал, запускающий од- новибраторы 4 или 5 (одновибратор 4 запускается фронтом импульса, одновибратор 5 - спадом импульса).

. Однако одновибраторы 4 и 5 не запускаются до тех пор, пока присутствует импульс на выходе одиовибратора б, т.е. пока не будет завершена начальная установка устройства. Одновибраторы 4 и 5 формируют

импульсы в моменты фазовых переходов во входном ФМ-сигнале с длительностью

t

где Zmin - длительность временного интервала между фазовыми переходами и последовательности элементов входного.потока данных вида 00 максимальной частоте.

Эти импульсы через элемент 10 ИЛИ поступают на вход элемента 8 задержки и на первые входы элементов 2 и 3 И. На

вторые входы элементов 2 и 3 И поступают сигналы с выходов цифровых компараторов 21 и 22, соответственно- На выходе компаратора 21 высокий потенциал появляется в том случае, если код. полученный на выходах счетчика 17 меньше, чем код, хранящийся в регистре 19, На выходе компаратора 22 высокий потенциал появляется в том случае, если код, полученный на выходах счетчика 17 длительности, равен коду, хранящемуся

в регистре 19. Таким образом, с помощью цифровых компараторов 21 и 22 производится сравнение измеренной длительности между фазовыми переходами во входном ФМ-сигнале с базисной величиной.

Задержанный импульс с выхода элеента 8 задержки воздействует на вход эроса счетчика 17 длительности, который осле каждого импульса сброса начинает акапливать импульсы с выхода генератора 5 тактовых импульсов (фиг.2,6). При каж- ом фазовом переходе во входном ФМ-сиг- але (фи.2,в) на выходе элемента 8 задержки оявляется импульс (фиг.2, г), после которо0счетчик 17 длительности накапливает не- оторое число тактовых импульсов (фиг.2 ,д). Если к моменту появления следующего азового перехода код на выходе счетчика 7 длительности оказывается меньше, чем од, хранящийся в регистре 19, то на выходе омпаратора 21 возникает высокий потен- иал, разрешающий прохождение импульса выхода элемента 10 ИЛИ через элемент 2

1(фиг.2,е). В этом случае в момент фазового ерехода в регистр 19 записывается код с ыхода счетчика 17 длительности, т.е. код, еныиий базисного. (Фиг.2.з). Содержимое четчика 24 при этом обнуляется (фиг.2,и), е. обнуляется результат накопления числа овладений для прежнего базисного кода.

Если к моменту появления базисного ерехода двоичный код на выходе счетчика 7 длительности окажется равным коду. ранящемуся в регистре 19, то высокий по- енциал появляется на выходе цифрового омпаратора 22, разрушая прохождение мпульса с выхода элемента 10 ИЛИ через лемент 3 И (фиг.2. ж). Этот импульс посту- зет на тактовый вход счетчика 24, изменяя го содержимое в сторону накопления числа овладений измеренной длительности меж- у двумя соседними фазовыми переходами базисной величиной.

Выходной код счетчика 24 поступает на ыходы цифрового компаратора 23, где равнивается с кодом порогового числасов- адений, поступающего с выхода формиро- ателя 14. При равенстве сравниваемых начений на выходе цифрового компарато- а 23 появляется высокий потенциал, запу- кающий одно-вибратор 7. Выходной мпульс одноаибратора 7 (фиг.2,к), проходя ерез элемент 12 ИЛИ, обнуляет счетчик 24 и оздействует на тактовый вход регистра 20, аписывая в него двоичный код, пропорци- нальный минимальной длительности меж- у фазовыми переходами во входном М-сигнале(фиг.2,л). При этом на выходах лока 25 памяти появляется код, соответст- ующий двоичному коду искомой частоты,, оторый является выходным сигналом уст- ойства (фиг.2. м).

Импульс с выхода одновибратора 7 воз- ействует на вход установки триггера 16 в

нулевое состояние, т.е. приводит устр во в исходное состояние.

Выходкой сигнал одновибратора 7 (спад импульса) можно использовать для за- 5 пуска одновибратора б, т.е. для организации цикличной работы устройства. При этом выход одновибратора 7 должен быть подключен ко входу запуска спадом одновибратора 6,

0 Вход запуска одновибратора 6 можно использовать для периодической установки устройства в исходное состояние по времени, по истечении которого формируется импульс ПУСК. Таймер может быть выполнен

5 в виде кольцевого счетчика, один из разрядов которого подключен к входу запуска одновибратора б, а на тактовый вход счетчика подключен дополнительный генератор тактовых импульсов, частота которых меньше

0 частоты следования символов информации на самой низкой скорости передачи информации.

Технико-экономические преимущества предполагаемого изобретения по сравне5 нию с прототипом заключаются в повышении точности определения частоты передачи цифровой информации.

Повышение точности определения скорости обусловлено тем, что исключается по

0 сравнению с прототипом возможность ложного определения скорости при различных сочетаниях двоичных элементов во входном информационном потоке.

Формула изобретения

5 1. Способ определения частоты передачи цифровой информации, заключающийся в преобразовании цифровой информации в фазоманипулированные сигналы, выделении фазовых переходов в фазоманипулиро0 ванном сигнале и идентификации частоты передачи по результатам анализа, отличающийся тем, что, с целью повышения точности определения, перед выделением фазовых переходов запоминают в качестве

5 базисного кода двоичный код гмакс, где Тмэкс - длительность временного интервала, между фазовыми переходами в последовательности элементов входного потока данных вида 00 на минимальной частоте,

0 выделение фазовых переходов во входном фазоманипулированном сигнале осуществляют путем формирования при каждом изменении уровня входного сигнала импульса

С ДЛИТеЛЬНОСТЬЮ Т Тмин . ГДе Гмин ДЛИ5 тел-jHOCTb временного интервала между фазовыми переходами в последовательности элементов входного потока данных вида 00 на максимальной частоте, измеряют временной интервал между каждыми двумя соседними импульсами, преобразуют измеренный временной интервал в двоичный код Ti. сравнивают двоичный код П с базисным кодом Т, запоминают двоичный код TV в качестве базисного кода Т при условии Ti Т, суммируют число совпадений Si двоично: го кода Ti при условии , сравнивают число совпадений Si двоичного кода Tt с пороговым значением Р, идентификацию скорости передачи данных осуществляют по коду Ti, для которого , причем поро- говое значение Р выбирают равным

р , 1 .

Pl(1-P2)

где Pi - вероятность появления во входном потоке данных последовательности элементов вида 00, характеризующая статистические свойства передаваемого потока,

Рг - вероятность искажения последовательности элементов вида 00 во входном потоке данных из-за воздействия помех или появления сбоев.

2. Устройство для определения частоты передачи цифровой информации, содержащее генератор тактовых импульсов. Счетчик длительности, первый регистр и блок памяти, отличающееся тем, что, с целью повышения точности определения скорости передачи, в него введены первый, второй и третий элементы И, коммутатор, первый, второй, третий и четвертый одновибраторы, первый и второй элементы задержки, первый, второй и третий элементы ИЛИ, формирователь исходного базисного кода, формирователь кода порогового значения, триггер, второй регистр, первый, второй и третий цифровые компараторы и счетчик числа совпадений, при этом входы запуска первого и второго одновибраторов объединены и подключены к выходу первого элемента И. первый вход которого является входом всего устройства, а второй вход соединен с выходом триггера, S-вход которого подключен к входам запрещения запуска первого и второго одновибраторов и соединен с выходом третьего одновибратора, вход запуска которого является входом запуска всего устройства, выходы первого и

второго одновибраторов подключены к соответствующим входам первого элемента ИЛИ, выход которого через первый элемент задержки соединен с входом сброса счетчика длительности, тактовый вход которого соединен с выходом генератора тактовых импульсов, выход переполнения счетчика длительности соединен с его входом разрешения, информационные выходы счетчика

длительности .подключены к первым группам входов коммутатора, первого и второго цифровых компараторов, выходы формирователя исходного базисного кода подключены к второй группе входов коммутатора,

выходы которого подключены к информационным входам параллельной записи первого регистра, информационные выходы которого подключены к вторым группам входов первого и второго цифровых компараторов и информационным входам параллельной записи второго регистра, информационными выходами подключенного к адресным входам блока памяти, выходы которого являются выходом всего

устройства, выход третьего одновибратора подключен к управляющему входу коммутатора и через второй элемент задержки к первому входу второго элемента ИЛИ, выходом подключенного к тактовому входу первого регистра, выходы первого и второго цифровых компараторов подключены к первым входам второго и третьего элементов И, вторые входы которых объединены и подключены к выходу первого элемента ИЛИ,

выход второго элемента И соединен с вторым входом второго элемента ИЛИ и с первым входом третьего элемента ИЛИ, выходом подключенного к входу сброса счетчика числа совпадений, тактовый вход

которого соединен с выходом третьего элемента VI, а информационные выходы подключены к первой группе входов третьего цифрового компаратора, вторая группа входов которого соединена с выходами формирователя кода порогового значения, а выход через четвертый одновибратор подключен к R-входу триггера, второму входу третьего элемента ИЛИ и тактовому входу второго регистра.

Авторы

Даты

1993-08-30—Публикация

1990-08-02—Подача