f

3

- ХоЗ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема сигналов с относительной фазовой модуляцией | 1990 |

|

SU1714817A1 |

| Устройство для контроля и идентификации пользователя | 1991 |

|

SU1833902A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1989 |

|

SU1651385A1 |

| Способ определения скорости передачи дискретных сигналов с фазовой манипуляцией | 1990 |

|

SU1778912A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| Способ определения частоты передачи цифровой информации и устройство для его осуществления | 1990 |

|

SU1837344A1 |

| Автокорреляционный приемник сигналов с относительной фазовой модуляцией | 1981 |

|

SU1021015A1 |

| Устройство задержки последовательности импульсов с цифровым управлением | 1985 |

|

SU1285576A1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2011 |

|

RU2460224C1 |

| УСТРОЙСТВО ПОИСКА СИГНАЛОВ | 2009 |

|

RU2422982C2 |

Изобретение относится к передаче цифровой информации и может найти примене- ние в системах связи с временным уплотнением каналов и в последовательных интерфейсах при передаче данных с относительной фазовой манипуляцией, Цель - повышение точности выделения границ посылок. Устройство содержит генератор 1 тактовых импульсов, триггер 2, блок 3 выделения фронтов импульсов, первый, второй и третий элементы задержки 4-6, первый и второй счётчики 7, 8 импульсов, блок 9 памяти, элемент ИЛИ 10, первый и второй регистры 11,12, первый и второй цифровые компараторов 13, 14, первый и второй элементы И 15, 16. Устройство обеспечивает высокую точность выделения границ гтосыЛОК. 3 ИЛ, - : - - ;..,.;.:

Пуск -э

Ю

ы ел ел ю

Изобретение относится к передаче цифровой информации и может найти применение в системах связи с временным уплотнением каналов и в последовательных интерфейсах при передаче данных с относительной фазовой манипуляцией.

Известно устройство для выделения посылок сигналов, содержащее генератор тактовых импульсов, первый и второй счетчики, блок памяти, первый регистр, первый и второй элементы И. Недостатком данного устройства является низкая точность определения скорости передачи информации с относительной фазовой манипуляцией (ОФМ), поскольку при ОФМ различные по структуре (порядку следования 1 и О в общем потоке данных) фрагменты цифровой последовательности при их передаче с различными скоростями могут иметь идентичный вид, что вызывает снижение точности выделения границ посьшок сигналов.

Наиболее близким к предлагаемому является устройство для выделения границ посылок цифровой информации, содержащее генератор тактовых импульсов, счетчик импульсов, блок памяти, триггер и элементы.И.

Недостатком известного устройства является низкая, точность выделения границ посылок цифровой информации с относительной фазовой манипуляцией (ОФМ). Этот недостаток обусловлен тем, что при обычной ФМ информацию о длительности элементарной посылки (и, соответственно, о скорости передачи информации) можно извлечь из двух любых соседних временных интервалов, ограниченных тремя фазовыми переходами, а при ОФМ: такого строгого соответствия нет. Причина здесь заключена в специфике сигнала с ОФМ, в котором появление целой последовательности одинаковых, элементарных посылок может не приводить к изменению фазы текущего колебания, т. е. результат анализа двух любых соседних временных интервалов, ограниченных тремя фазовыми переходами, немй- жет быть адекватен истинной скорости передачи, ;;;;:; : :; ;. ; .. ; : .:

Цель изобретения - повышение точности выделения границ посылок цифровой информации.

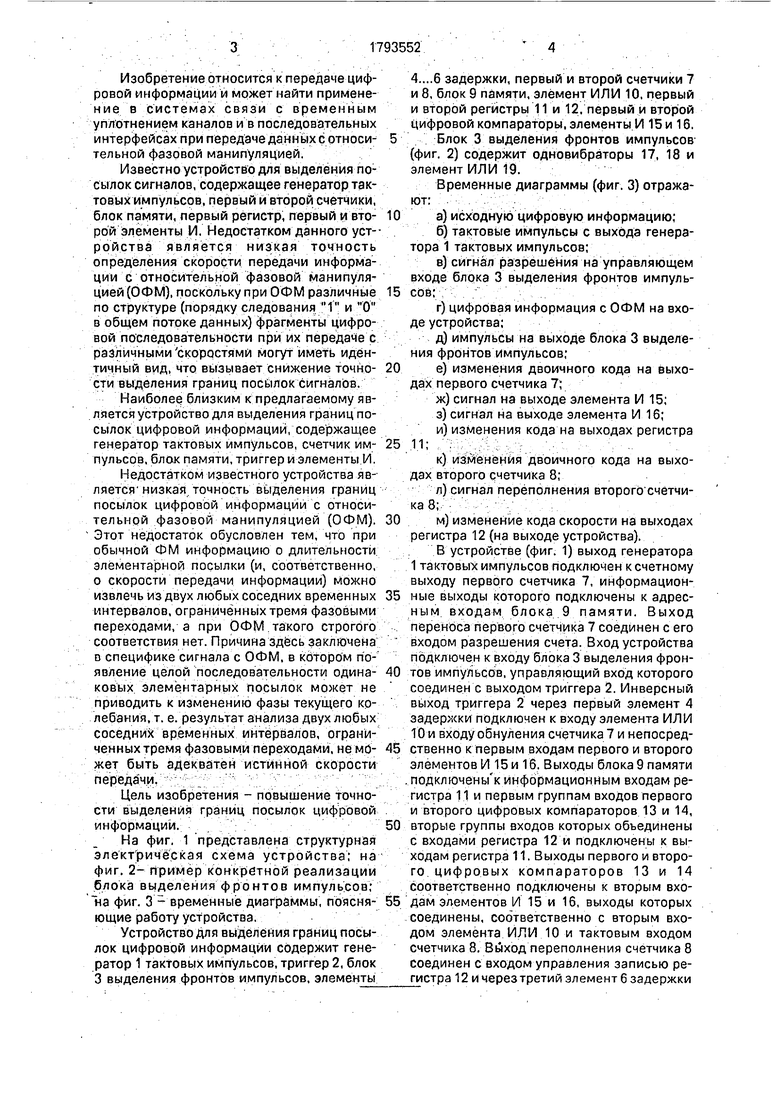

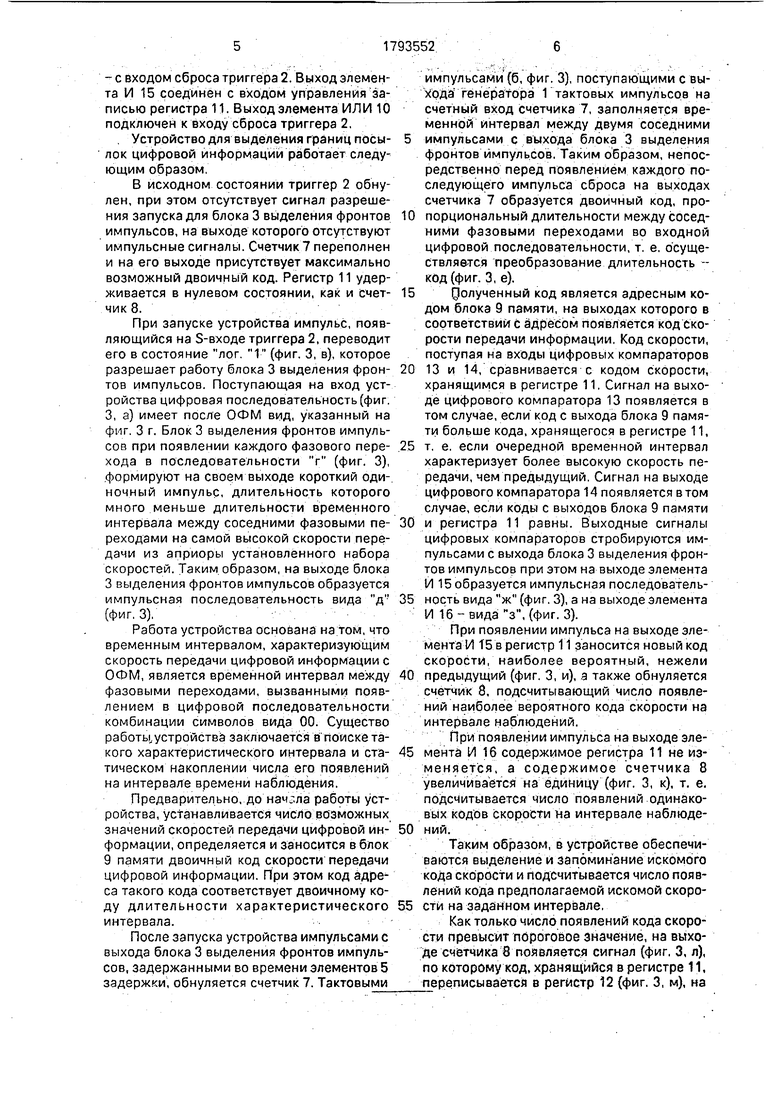

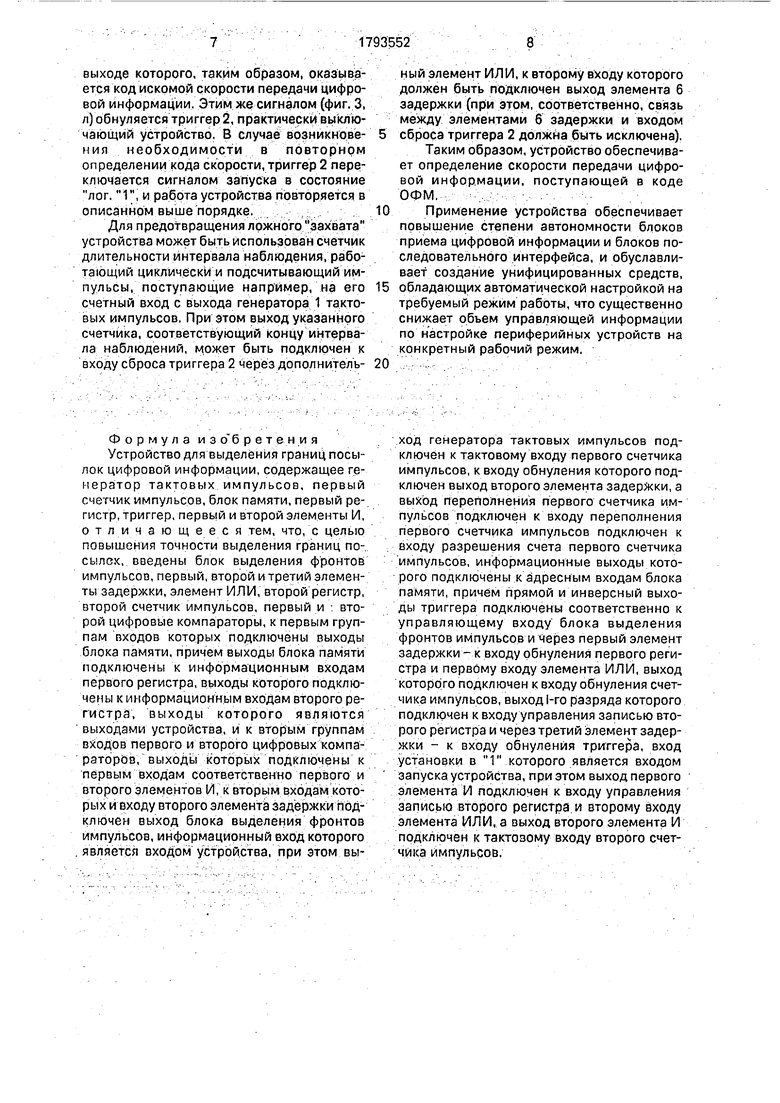

На фиг. 1 представлена структурная электрическая схема устройства; на фиг, 2- пример конкретной реализации блока выделения фронтов импульсов; на фиг. 3 - временные диаграммы, поясняющие работу устройства.

Устройство Для выделения границ посылок цифровой информации содержит генератор 1 тактовых импульсов, триггер 2, блок 3 выделения фронтов импульсов, элементы

Блок 3 выделения фронтов импульсов (фиг. 2) содержит одновибраторы 17, 18 и элемент ИЛИ 19.

Временные диаграммы (фиг. 3) отражают: .- -. . .- : .

а) исходную цифровую информацию;

б) тактовые импульсы с выхода генератора 1 тактовых импульсов;

в) сигнал разрешения на управляющем входе блока 3 выделения фронтов импуль- сов; ; . ;..

г) цифровая информация с ОФМ на входе устройства;

д) импульсы на выходе блока 3 выделения фронтов импульсов;

е) изменения двоичного кода на выходах первого счетчика 7;

ж) сигнал на выходе элемента И 15;

з) сигнал на выходе элемента И 16;

и) изменения кода на выходах регистра

11; ,:.;:;;. Д..;.-,;: , .. ..

к) изменения двоичного кода на выходах второго счетчика 8;

л) сигнал переполнения второго счетчика 8; - - -. -. ...-..

м) изменение кода скорости на выходах регистра 12 (на выходе устройства).

В устройстве (фиг. 1) выход генератора 1 тактовых импульсов подключен к счетному выходу первого счетчика 7, информационные выходы которого подключены к адресным, входам блока 9 памяти. Выход переноса первого счетчика 7 соединен с его

входом разрешения счета. Вход устройства подключен к входу блока 3 выделения фронтов импульсов, управляющий вход которого соединен с выходом триггера 2. Инверсный выход триггера 2 через первый элемент 4 задержки подключен к входу элемента ИЛИ 10 и входу обнуления счетчика 7 и непосредственно к первым входам первого и второго элементов И 15 и 16. Выходы блока 9 памяти подключены к информационным входам регистра 11 и первым группам входов первого

и второго цифровых компараторов 13 и 14,

вторые группы входов которых объединены с входами регистра 12 и подключены к выходам регистра 11. Выходы первого и второго, цифровых компараторов 13 и 14 соответственно подключены к вторым входам элементов И 15 и 16, выходы которых соединены, соответственно с вторым входом элемента ИЛИ 10 и тактовым входом счетчика 8. Выход переполнения счетчика 8 соединен с входом управления записью регистра 12 и через третий элемент 6 задержки

- с входом сброса триггера 2. Выход элемента И 15 соединен с входом управления записью регистра 11. Выход элемента ИЛИ 10 подключен к входу сброса триггера 2,

. Устройство для выделения границ посылок цифровой информации работает следующим образом,

В исходном состоянии триггер 2 обнулен, при этом отсутствует сигнал разрешения запуска для блока 3 выделения фронтов импульсов, на выходе которого отсутствуют импульсные сигналы. Счетчик 7 переполнен и на его выходе присутствует максимально возможный двоичный код. Регистр 11 удерживается в нулевом состоянии, как и счетчик 8.

При запуске устройства импульс, появляющийся на S-входе триггера 2, переводит его в состояние лог. 1 (фиг. 3, в), которое разрешает работу блока 3 выделения фронтов импульсов. Поступающая на вход устройства цифровая последовательность (фиг. 3, а) имеет после ОФМ вид, указанный на фиг. 3 г. Блок 3 выделения фронтов импульсов при появлении каждого фазового перехода в последовательности г (фиг. 3), формируют на выходе короткий оди-. ночный импульс, длительность которого много меньше длительности временного интервала между соседними фазовыми переходами на самой высокой скорости передачи из априоры установленного набора скоростей. Таким, образом, на выходе блока 3 выделения фронтов импульсов образуется импульсная последовательность вида д (фиг. 3). . Работа устройства основана на том, что временным интервалом, характеризующим скорость передачи цифровой информации с ОФМ, является временной интервал между фазовыми переходами, вызванными появлением в цифровой последовательности комбинации символов вида 00. Существо работы,устройства заключается в поиске такого характеристического интервала и статическом накоплении числа его появлений на интервале времени наблюдения.

Предварительно, до начала работы устройства, устанавливается число возможных, значений скоростей передачи цифровой информации, определяется и заносится в блок 9 памяти двоичный код скорости передачи цифровой информации. При этом код адреса такого кода соответствует двоичному коду длительности характеристического интервала.После запуска устройства импульсами с выхода блока 3 выделения фронтов импульсов, задержанными во времени элементов 5 задержки, обнуляется счетчик 7. Тактовыми

импульсами (б, фиг. 3), поступающими с вы- Уода Тенёратора 1 тактовых импульсов на счетный вход счетчика 7, заполняется временной интервал между двумя соседними

импульсами с выхода блока 3 выделения фронтов импульсов. Таким образом, непосредственно перед появлением каждого последующего импульса сброса на выходах счетчика 7 образуется двоичный код, про0 порциональный длительности между соседними фазовыми переходами во входной цифровой последовательности, т. е, осуществляется преобразование длительность - код (фиг. 3, е).

5 Полученный код является адресным кодом блока 9 памяти, на выходах которого в соответствий с адресом появляется код скорости передачи информации, Код скорости, поступая на входы цифровых компараторов

0 13 и 14, сравнивается с кодом скорости, хранящимся в регистре 11. Сигнал на выходе цифрового компаратора 13 появляется в том случае, если код с выхода блока 9 памяти больше кода, хранящегося в регистре 11,

5 т. е. если очередной временной интервал характеризует более высокую скорость передачи, чем предыдущий. Сигнал на выходе цифрового компаратора 14 появляется в том случае, если коды с выходов блока 9 памяти

0 и регистра 11 равны. Выходные сигналы цифровых компараторов стробируются импульсами с выхода блока 3 выделения фронтов импульсов при этом на выходе элемента И 15 образуется импульсная последователь5 ность вида ж (фиг. 3), а на выходе элемента И 16-вида з, (фиг. 3).

При появлении импульса на выходе элемента И t5 в регистр 11 заносится новый код скорости, наиболее вероятный, нежели

0 предыдущий (фиг. 3, и), а также обнуляется счетчик 8, подсчитывающий число появлений наиболее вероятного кода скорости на интервале наблюдений.

При появлении импульса на выходе эле5 мента И 16 содержимое регистра 11 не изменяется, а содержимое счетчика 8 увеличивается на единицу (фиг. 3, к), т. е. подсчитывается число появлений одинаковых кодов скорости на интервале наблюде0 ний.

Таким образом, в устройстве обеспечиваются выделение и запоминание искомого кода скорости и подсчитывается число появлений кода предполагаемой искомой скоро5 ст и на заданном интервале,

Как только число появлений кода скорости превысит пороговое значение, на выходе счетчика 8 появляется сигнал (фиг. 3, л), по которому код, хранящийся в регистре 11, переписывается в регистр 12 (фиг. 3, м), на

выходе которого, таким образом, оказцва- ётся код искомой скорости передачи цифровой информации. Этим же сигналом (фиг. 3, л) обнуляется триггер 2, практически выключающий устройство; В случае возникно;вё- нип необходимости в повторном определении кода скорости, триггер 2 переключается сигналом запуска в состояние лог. 1, и работа устройства повторяется в описанном выше порядке.. .

Для предотвращения ложного захвата устройства может быть использован счетчик длительности интервала наблюдения/работающий циклически и подсчитывающий импульсы, поступающие например, на его счетный вход с выхода генератора 1 тактовых импульсов. При этом выход указанного счетчика, соответствующий концу интервала наблюдений, может быть подключен к входу сброса триггера 2 через дополнительФормула изобретения Устройство для выделения границ посылок цифровой информации, содержащее генератор тактовых импульсов, первый счетчик импульсов, блок памяти, первый ре- гист р, триггер, первый и второй элементы И, отличающееся тем, что, с целью повышения точности выделения границ по-, сылсх, введены блок выделения фронтов импульсов, первый, второй и третий элементы задержки, элемент ИЛИ, второй регистр, второй счетчик импульсов, первый и : второй цифровые компараторы, к первым группам входов которых подключены выходы блока памяти, причем выходы блока памяти подключены к информационным входам первого регистра, выходы которого подключены к информационным входам второго регистра, выходы которого являются выходами устройства, и к вторым группам входов первого и второго цифровых компараторов, выходы которых подключены к первым входам соответственно первого и второго элементов И, к вторым входам которых и входу второго элементе задержки подключен выход блока выделения фронтов импульсов, информационный вход которого .является входом устройства, при этом выный элемент ИЛИ, к второму входу которого должен быть подключен выход элемента 6 задержки (при этом, соответственно, связь между элементами б задержки и входом

сброса триггера 2 должна быть исключена). Таким образом, устройство обеспечивает определение скорости передачи цифровой информации, поступающей в коде ОФМ. : -, j.:--:. .

Применение устройства обеспечивает повышение степени автономности блоков приема цифровой информации и блоков последовательного интерфейса, и обуславливает создание унифицированных средств,

обладающих автоматической настройкой на требуемый режим работы, что существенно снижает объем управляющей информации по настройке периферийных устройств на конкретный рабочий режим.

;;;u., .. , .; . .

ход генератора тактовых импульсов подключен к тактовому входу первого счетчика импульсов, к входу обнуления которого подключен выход второго элемента задержки, а выход переполнения первого счетчика импульсов подключен к входу переполнения первого счетчика импульсов подключен к входу разрешения счета первого счетчика импульсов, информационные выходы которого подключены к адресным входам блока памяти, причем прямой и инверсный выходы триггера подключены соответственно к управляющему входу блока выделения фронтов импульсов и через первый элемент задержки - к входу обнуления первого регистра и первому входу элемента ИЛИ, выход которого подключен к входу обнуления счетчика импульсов, выход 1-го разряда которого подключен к входу управления записью второго регистра и через третий элемент задержки - к входу обнуления триггера, вход установки в 1 которого является входом запуска устройства, при этом выход первого элемента И подключен к входу управления записью второго регистра, и второму входу элемента ИЛИ, а выход второго элемента И подключен к тактовому входу второго счетчика импульсов.

§ lllllinillilllillllinillllflillllllllinilllllHIllllllllillllllHIIIIIIIIIIIIIIIIIIIKIIIIIIIIHl

i - -.: -У-;: ; - -У.-----г --;: fi n fi fl

3L

3

П fl

LL

/

ЮС

II п.. 1

П П

па

| Устройство для выделения границ элементарных посылок фазоманипулированного сигнала | 1978 |

|

SU764144A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1993-02-07—Публикация

1990-08-31—Подача