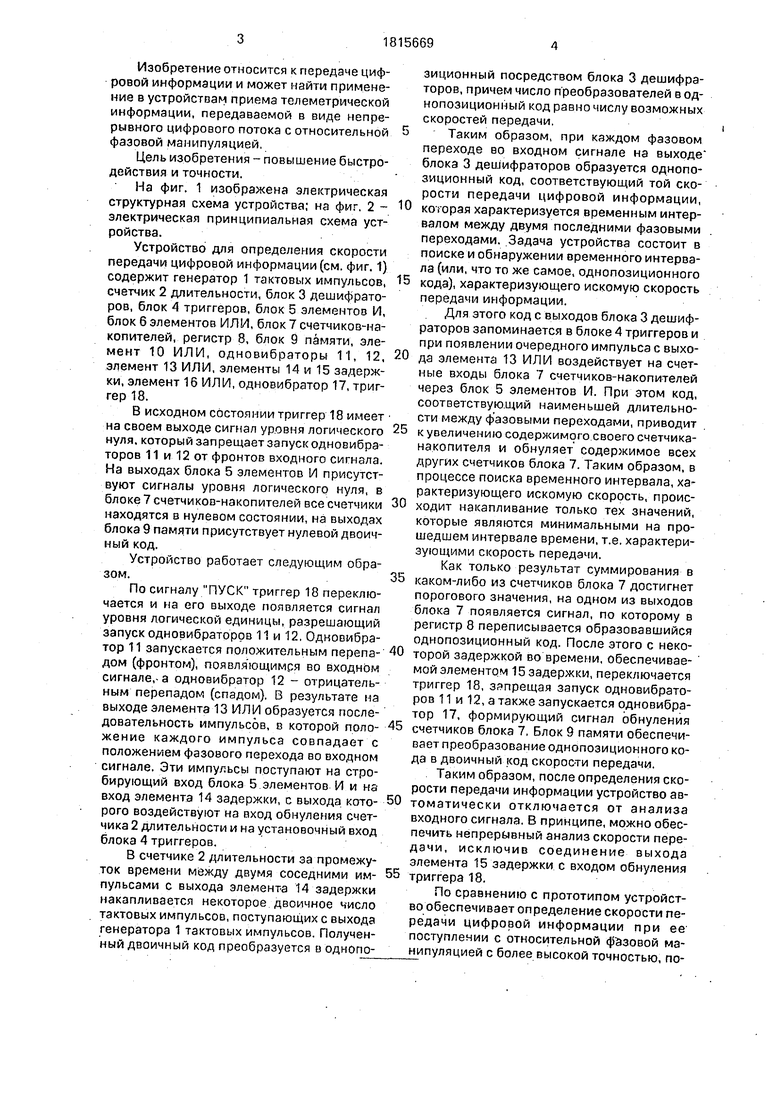

Фиг1

Изобретение относится к передаче цифровой информации и может найти применение в устройствам приема телеметрической информации, передаваемой в виде непрерывного цифрового потока с относительной фазовой манипуляцией.

Цель изобретения - повышение быстродействия и точности.

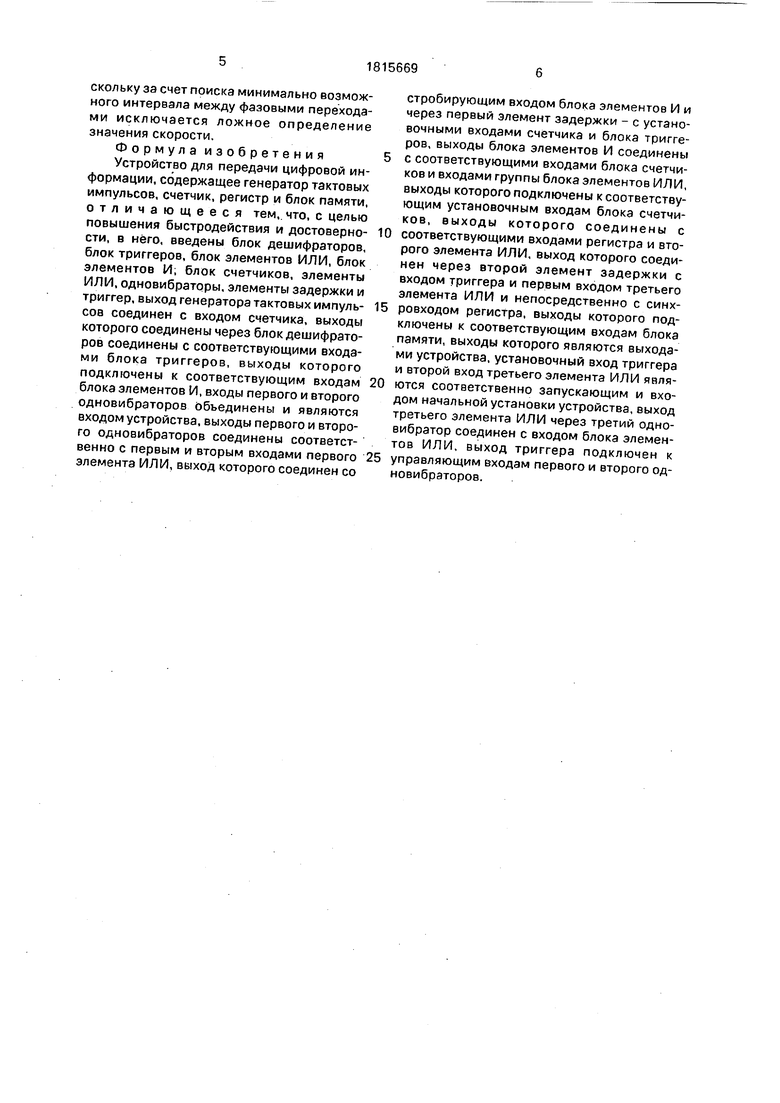

На фиг. 1 изображена электрическая структурная схема устройства; на фиг, 2 - электрическая принципиальная схема устройства.

Устройство для определения скорости передачи цифровой информации (см. фиг. 1) содержит генератор 1 тактовых импульсов, счетчик 2 длительности, блок 3 дешифраторов, блок А триггеров, блок 5 элементов И, блок б элементов ИЛИ, блок 7 счетчиков-накопителей, регистр 8, блок 9 памяти, элемент 10 ИЛИ, одновибраторы 11, 12, элемент 13 ИЛИ, элементы 14 и 15 задержки, элемент 16 ИЛИ, одновибратор 17, триггер 18.

В исходном состоянии триггер 18 имеет на своем выходе сигнал ур.овня логического нуля, который запрещает запуск одновибра- торов 11 и 12 от фронтов входного сигнала. На выходах блока 5 элементов И присутствуют сигналы уровня логического нуля, в блоке 7 счетчиков-накопителей все счетчики находятся в нулевом состоянии, на выходах блока 9 памяти присутствует нулевой двоичный код.

Устройство работает следующим образом.

По сигналу ПУСК триггер 18 переключается и на его выходе появляется сигнал уровня логической единицы, разрешающий запускодновибраторов 11 и 12. Одновибратор 11 запускается положительным перепадом (фронтом), появля ющимря во входном сигнале,-а одновибратор 12 - отрицательным перепадом (спадом), В результате на выходе элемента 13 ИЛИ образуется последовательность импульсов, в которой положение каждого импульса совпадает с положением фазового перехода во входном сигнале. Эти импульсы поступают на стро- бирующий вход блока 5 элементов И и на вход элемента 14 задержки, с выхода которого воздействуют на вход обнуления счетчика 2 длительности и на установочный вход блока 4 триггеров..

В счетчике 2 длительности за промежуток времени между двумя соседними импульсами с выхода элемента 14 задержки накапливается некоторое двоичное число тактовых импульсов, поступающих с выхода генератора 1 тактовых импульсов. Полученный двоичный код преобразуется в однопозиционный посредством блока 3 дешифраторов, причем число преобразователей вод- нопозиционный код равно числу возможных скоростей передачи.,

Таким образом, при каждом фазовом переходе во входном сигнале на выходе блока 3 дешифраторов образуется однопо- зиционный код, соответствующий той скорости передачи цифровой информации,

которая характеризуется временным интервалом между двумя последними фазовыми . переходами. Задача устройства состоит в поиске и обнаружении временного интервала (или, что то же самое, однопозиционного

5 кода), характеризующего искомую скорость передачи информации.

Для этого код с выходов блока 3 дешифраторов запоминается в блоке 4 триггеров и при появлении очередного импульса с выхо0 да элемента 13 ИЛИ воздействует на счетные входы блока 7 счетчиков-накопителей через блок 5 элементов И. При этом код, соответствующий наименьшей длительности между фазовыми переходами, приводит

5 к увеличению содержимого своего счетчика- накопителя и обнуляет содержимое всех других счетчиков блока 7. Таким образом, в процессе поиска временного интервала, рактеризующего искомую скорость, проис0 ходит накапливание только тех значений, которые являются минимальными на прошедшем интервале времени, т.е. характеризующими скорость передачи.

Как только результат суммирования в

5 каком-либо из счетчиков блока 7 достигнет порогового значения, на одном из выходов блока 7 появляется сигнал, по которому в регистр 8 переписывается образовавшийся однопозиционный код. После этого с неко0 торой задержкой во времени, обеспечиваемой элементом 15 задержки, переключается триггер 18, запрещая запуск одновибраторов 11 и 12, а также запускается одновибратор 17, формирующий сигнал обнуления

5 счетчиков блока 7, Блок 9 памяти обеспечивает преобразование однопозиционного кода в двоичный код скорости передачи.

Таким образом, после определения скорости передачи информации устройство ав0 тематически отключается от анализа входного сигнала. В принципе, можно обеспечить непрерывный анализ скорости передачи, исключив соединение выхода элемента 15 задержки с входом обнуления

5 триггера 18.

По сравнению с прототипом устройство обеспечивает определение скорости передачи цифровой информации при ее поступлении с относительной фазовой манипуляцией с более высокой точностью, поскольку за счет поиска минимально возможного интервала между фазовыми переходами исключается ложное определение значения скорости.

Формула изобретения Устройство для передачи цифровой информации, содержащее генератор тактовых импульсов, счетчик, регистр и блок памяти, отличающееся тем., что, с целью повышения быстродействия и достоверности, в него, введены блок дешифраторов, блок триггеров, блок элементов ИЛИ, блок элементов И; блок счетчиков, элементы ИЛИ, одновибраторы, элементы задержки и триггер, выход генератора тактовых импульсов соединен с входом счетчика, выходы которого соединены через блок дешифраторов соединены с соответствующими входами блока триггеров, выходы которого подключены к соответствующим входам блока элементов И, входы первого и второго одновибраторов объединены и являются входом устройства, выходы первого и второго одновибраторов соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого соединен со

стробирующим входом блока элементов И и через первый элемент задержки - с установочными входами счётчика и блока триггеров, выходы блока элементов И соединены

с соответствующими входами блока счетчиков и входами группы блока элементов ИЛИ, выходы которого подключены к соответствующим установочным входам блока счетчиков, выходы которого соединены с

соответствующими входами регистра и второго элемента ИЛИ, выход которого соединен через второй элемент задержки с входом триггера и первым входом третьего элемента ИЛИ и непосредственно с синхровходом регистра, выходы которого подключены к соответствующим входам блока памяти, выходы которого являются выходами устройства, установочный вход триггера и второй вход третьего элемента ИЛИ являются соответственно запускающим и входом начальной установки устройства, выход третьего элемента ИЛИ через третий одно- вибратор соединен с входом блока элементов ИЛИ, выход триггера подключен к

управляющим входам первого и второго одновибраторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ определения частоты передачи цифровой информации и устройство для его осуществления | 1990 |

|

SU1837344A1 |

| СИСТЕМА ДЛЯ ШИФРАЦИИ И ДЕШИФРАЦИИ КОМАНД | 1991 |

|

RU2043699C1 |

| Способ определения скорости передачи дискретных сигналов с фазовой манипуляцией | 1990 |

|

SU1778912A1 |

| Устройство для обучения операторов | 1991 |

|

SU1785026A1 |

| Устройство для контроля многоканального аппарата магнитной записи | 1986 |

|

SU1420615A1 |

| Устройство для выделения границ посылок цифровой информации | 1990 |

|

SU1793552A1 |

| Устройство для ввода аналоговой информации | 1984 |

|

SU1188744A1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА РАЗМАХОВ КОЛЕБАНИЙ НАПРЯЖЕНИЯ | 1993 |

|

RU2075752C1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Устройство для передачи и приема дискретной информации | 1980 |

|

SU886295A1 |

Изобретение относится к передаче цифровой информации, может найти применение в устройствах приема телеметрической информации, передаваемой в виде непрерывного цифрового потока с относительной фазовой манипуляцией. Цель - повышение быстродействия и достоверности. Устройство содержит генератор 1 тактовых импульсов, счетчик 2, блок 3 дешифраторов, блок 4 триггеров, блок 5 элементов И, блок 6 элементов ИЛИ, блок 7 счетчиков, регистр 8, блок 9 памяти, элементы ИЛИ 10, 13, 16, элементы задержки 14, 15, одновибраторы 11, 12,17, триггер 18. Устройство обеспечивает определение скорости передачи цифровой информации при ее поступлении с относительной фазовой манипуляцией за счет поиска минимально возможного интервала между фазовыми переходами. 2 ил.

| Устройство для компенсации задержки информационных сигналов | 1974 |

|

SU511618A1 |

Авторы

Даты

1993-05-15—Публикация

1990-08-02—Подача