Изобретение относится к вычислитель- й и электроизмерительной технике и пр еднззначетно для аналого-цифрового пре- оС разования быстроизменяющихся элект- pi/

ческих сигналов.

Целью изобретения является повышени

е точности.

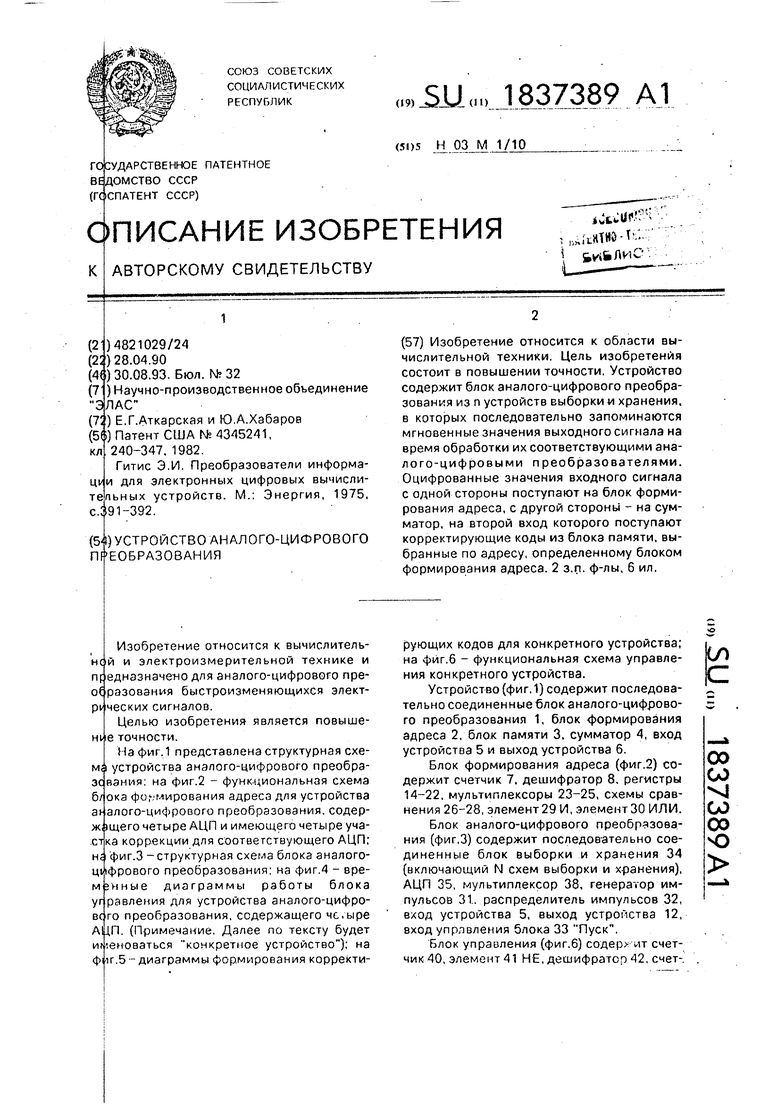

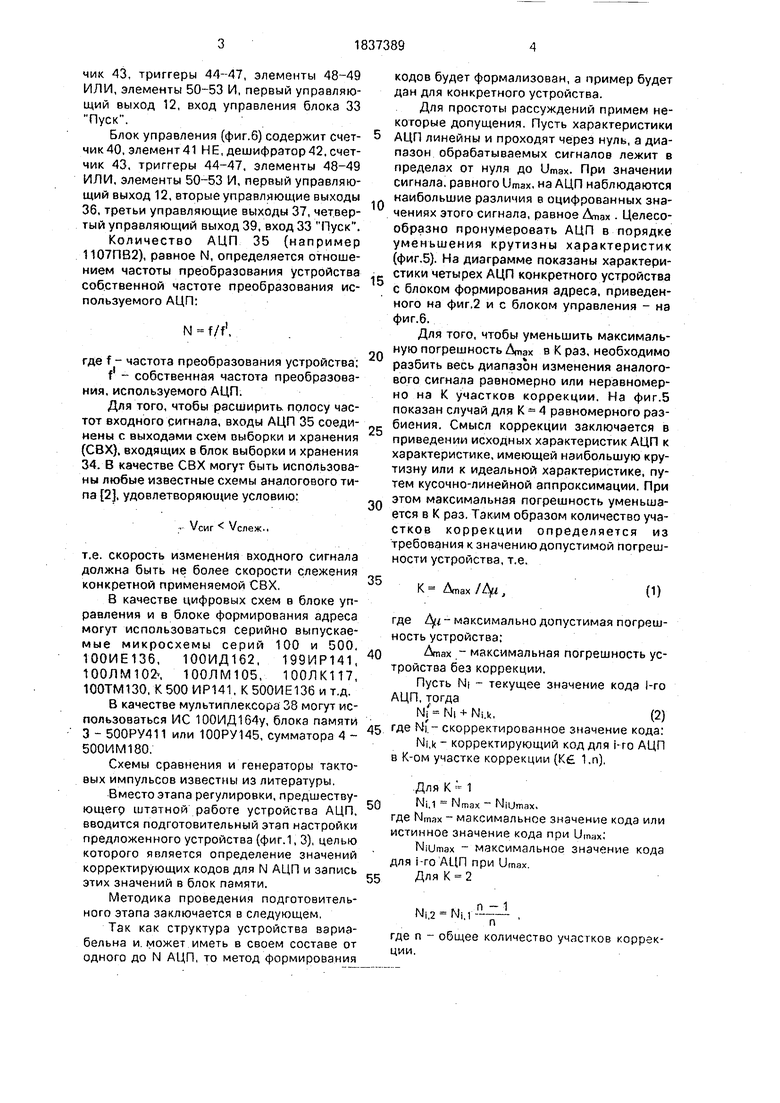

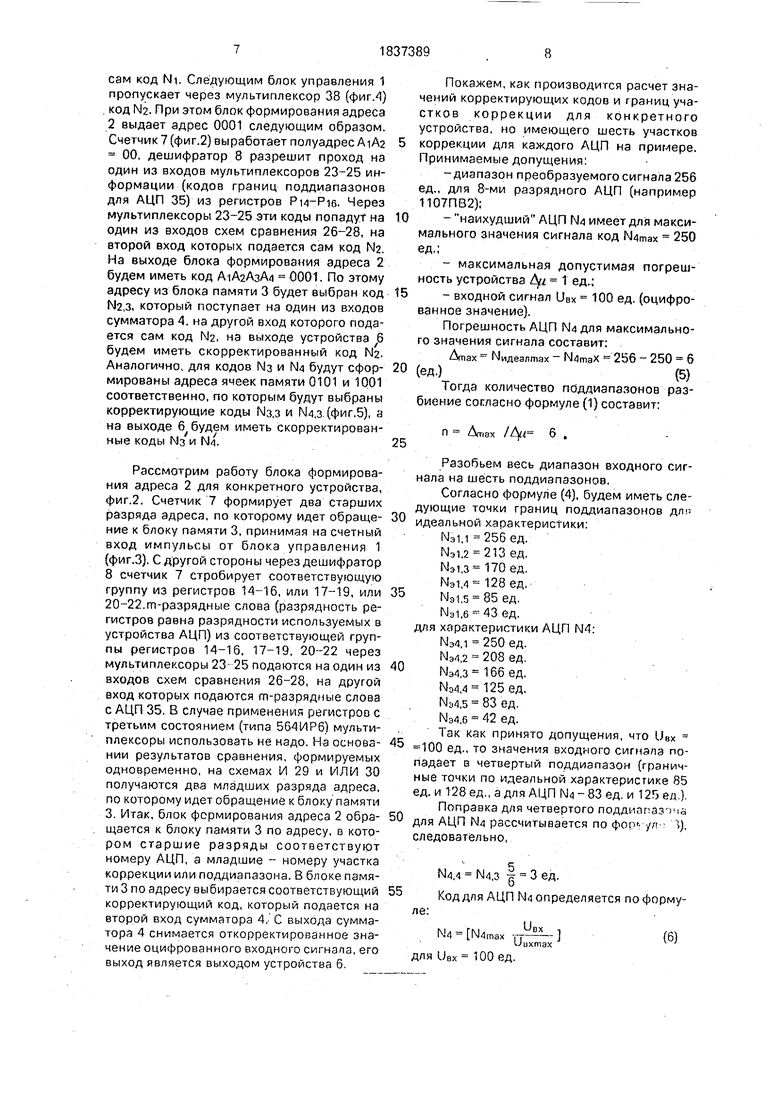

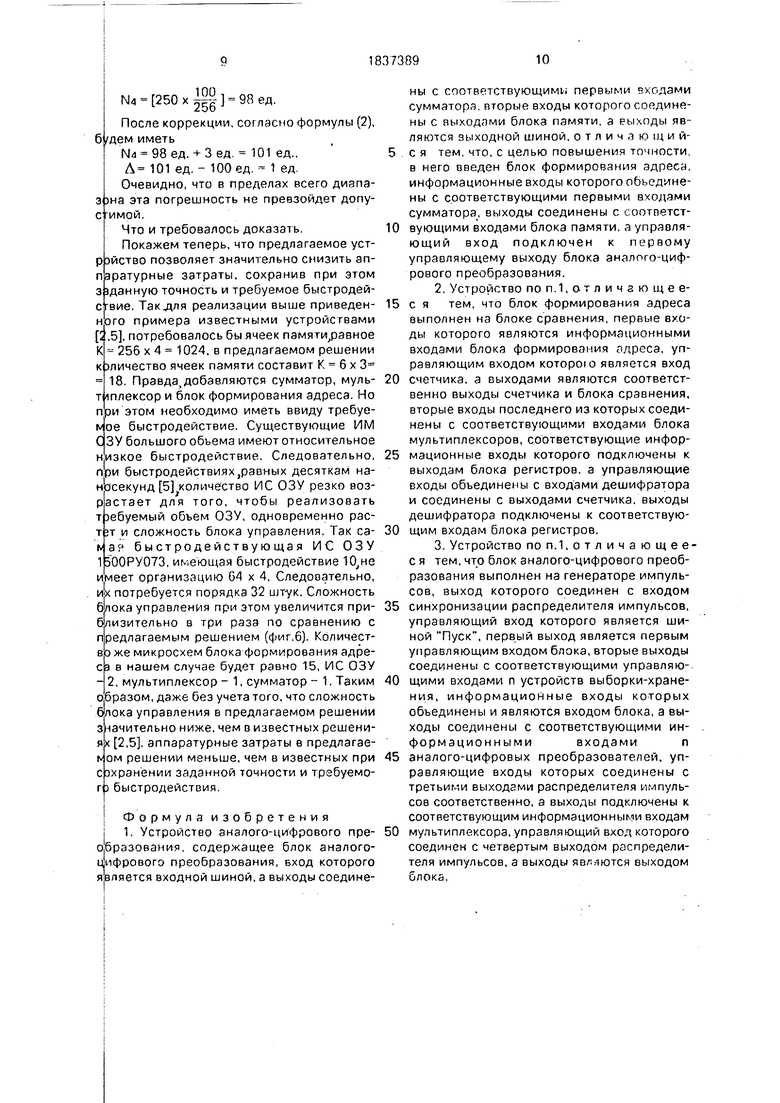

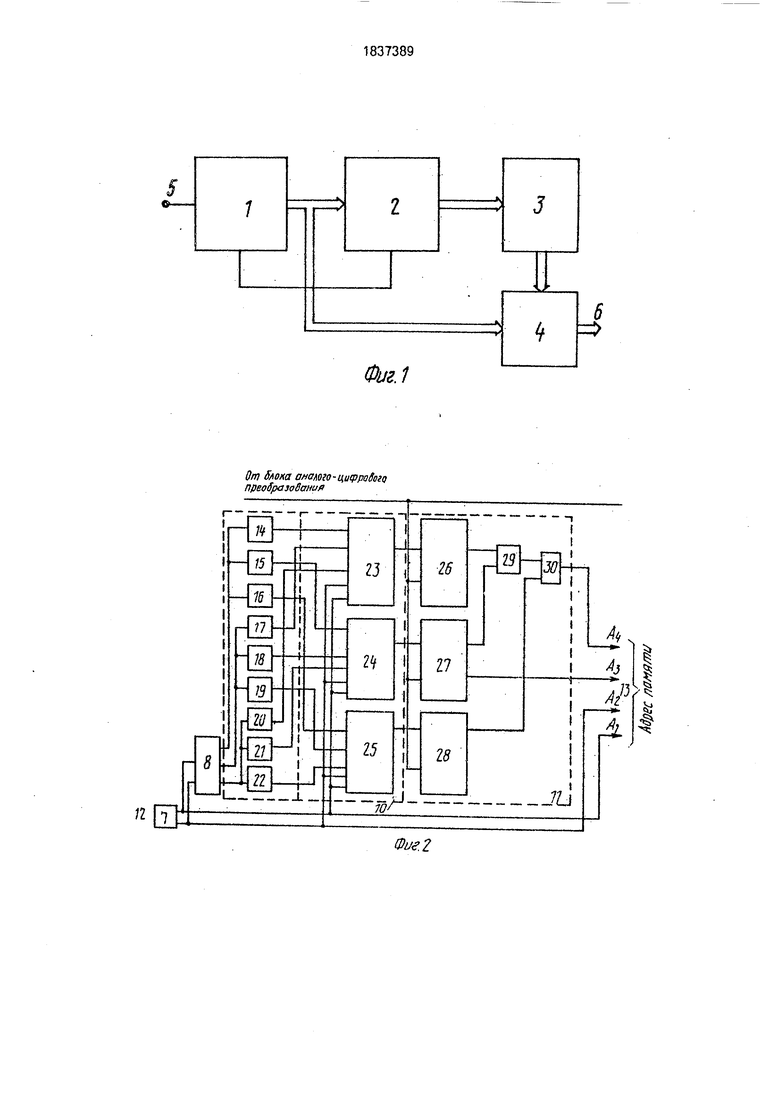

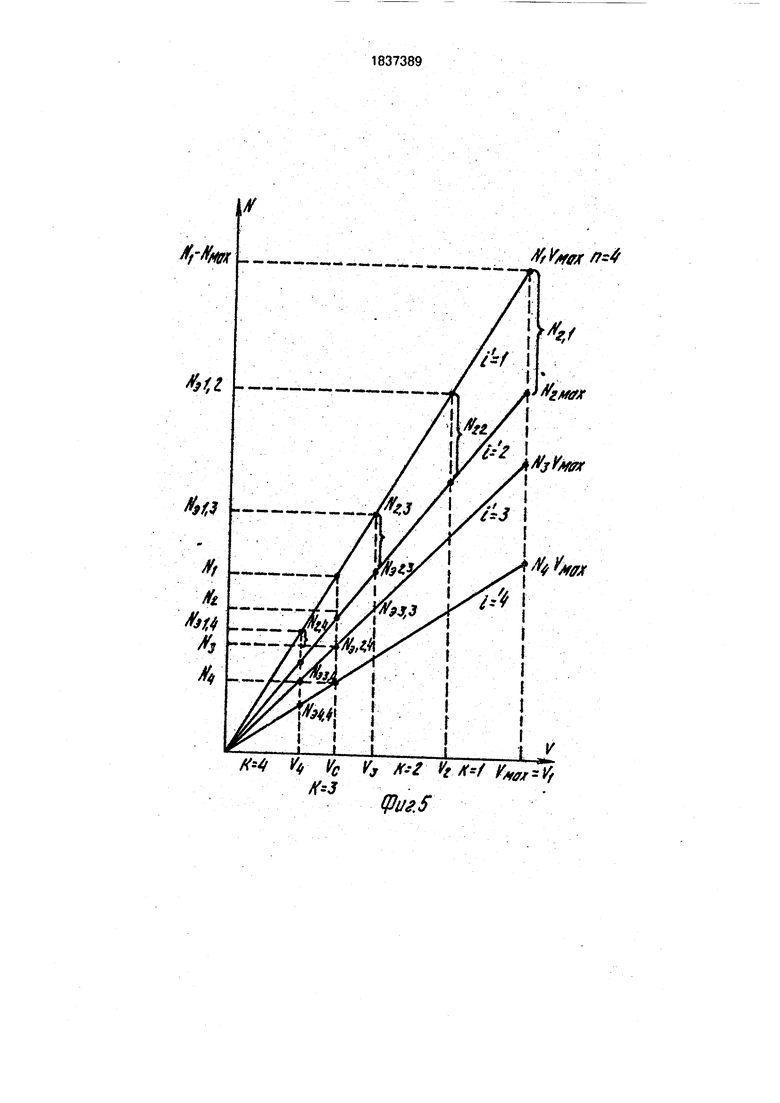

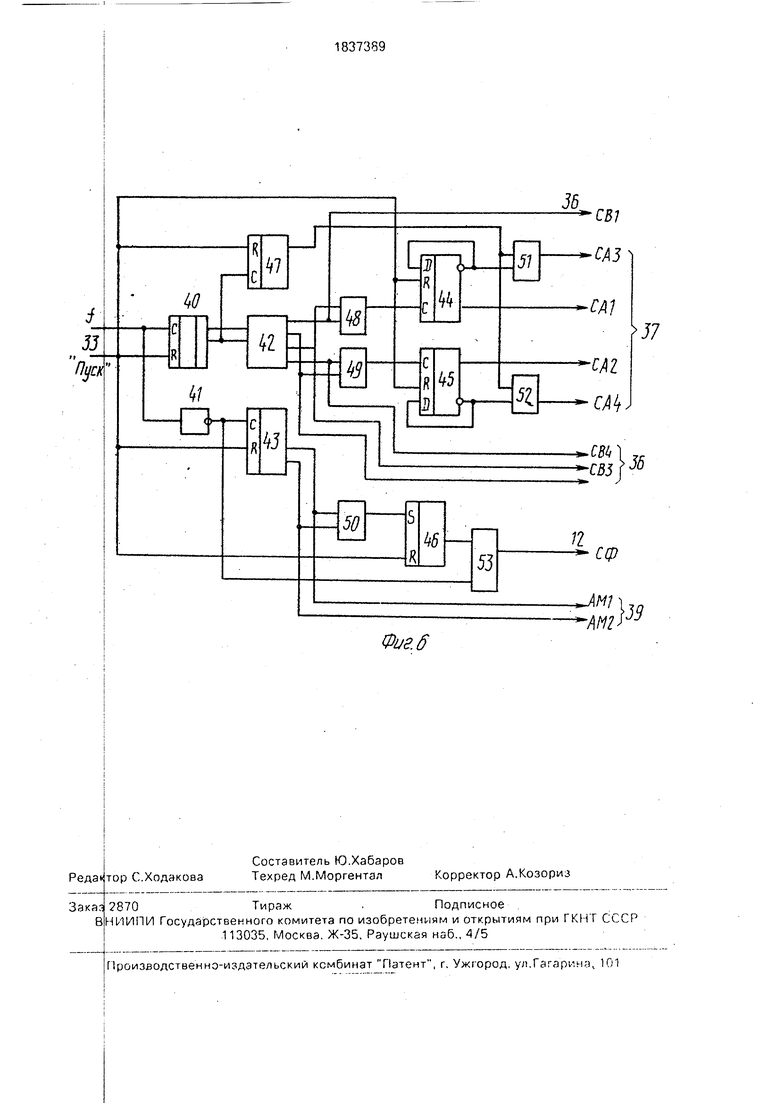

На фш.1 представлена структурная схема устройства аналого-цифрового преобразования, на фиг.2 - функциональная схема б/ ока формирования адреса для устройства аналого-цифрового преобразования, содержащего четыре АЦП и имеющего четыре участка коррекции для соответствующего АЦП; фиг.З -структурная схема блока аналого- ц фрового преобразования: на фиг.4 - вре- мзнные диаграммы работы блока угравления для устройства аналого-цифро- вс го преобразования, содержащего чс.ыре АЦП. (Примечание. Далее по тексту будет именоваться конкретное устройство); на ф( г.5 -диаграммы формирования корректирующих кодов для конкретного устройства;

на фиг.6 - функциональная схема управле- v/l

ния конкретного устройства.Г

Устройство (фиг. 1) содержит последова- л тельно соединенные блок аналого-цифрово- с го преобразования 1, блок формирования адреса 2, блок памяти 3, сумматор 4, вход устройства 5 и выход устройства 6.

Блок формирования адреса (фиг.2) со- держит счетчик 7. дешифратор 8, регистры СлЗ 14-22, мультиплексоры 23-25, схемы срав- нения 26-28, элемент29 И, элемент 30 ИЛИ. СО

Блок аналого-цифрового преобрязова- QQ ния (фиг.З) содержит последовательно сое- sQ диненные блок выборки и хранения 34 (включающий N схем выборки и хранения), АЦП 35, мультиплексор 38, генератор импульсов 31. распределитель импульсов 32, вход устройства 5, выход устройства 12, вход упрлвления блока 33 Пуск.

Блок управления (фиг.6) содер ит счетчик 40, элемент 41 НЕ, дешифратор 42, счетчик 43, триггеры 44-47, элементы 48-49 ИЛИ, элементы 50-53 И, первый управляющий выход 12, вход управления блока 33 Пуск.

Блок управления (фиг.б) содержит счетчик 40, элемент 41 НЕ, дешифратор 42, счетчик 43, триггеры 44-47, элементы 48-49 ИЛИ, элементы 50-53 И, первый управляющий выход 12, вторые управляющие выходы 36, третьи управляющие выходы 37, четвертый управляющий выход 39, вход 33 Пуск.

Количество АЦП 35 (например 1107ПВ2), равное N, определяется отношением частоты преобразования устройства собственной частоте преобразования используемого АЦП:

N f /f1,

где f - частота преобразования устройства;

f1 - собственная частота преобразования, используемого АЦП.

Для того, чтобы расширить, полосу частот входного сигнала, входы АЦП 35 соединены с выходами схем выборки и хранения (СВХ), входящих в блок выборки и хранения 34. В качестве СВХ могут быть использованы любые известные схемы аналогового типа 2, удовлетворяющие условию:

- Vcnr Vcnexo,

т.е. скорость изменения входного сигнала должна быть не более скорости слежения конкретной применяемой СВХ.

В качестве цифровых схем в блоке управления и в блоке формирования адреса могут использоваться серийно выпускаемые микросхемы серий 100 и 500. 100ИЕ136, 100ИД162, 199ИР141, 100ЛМ102, 100ЛМ105, 100ЛК117, 100ТМ130, К 500 ИР141, К 500ИЕ136 и т.д.

В качестве мультиплексора 38 могут использоваться ИС 100ИД164у, блока памяти 3 - 500РУ411 или 100РУ145, сумматора 4 - 500ИМ180.

Схемы сравнения и генераторы тактовых импульсов известны из литературы.

Вместо этапа регулировки, предшествующего штатной работе устройства АЦП, вводится подготовительный этап настройки предложенного устройства (фиг.1, 3), целью которого является определение значений корректирующих кодов для N АЦП и запись этих значений в блок памяти.

Методика проведения подготовительного этапа заключается в следующем.

Так как структура устройства вариабельна и может иметь в своем составе от одного до N АЦП, то метод формирования

кодов будет формализован, а пример будет дан для конкретного устройства.

Для простоты рассуждений примем некоторые допущения. Пусть характеристики

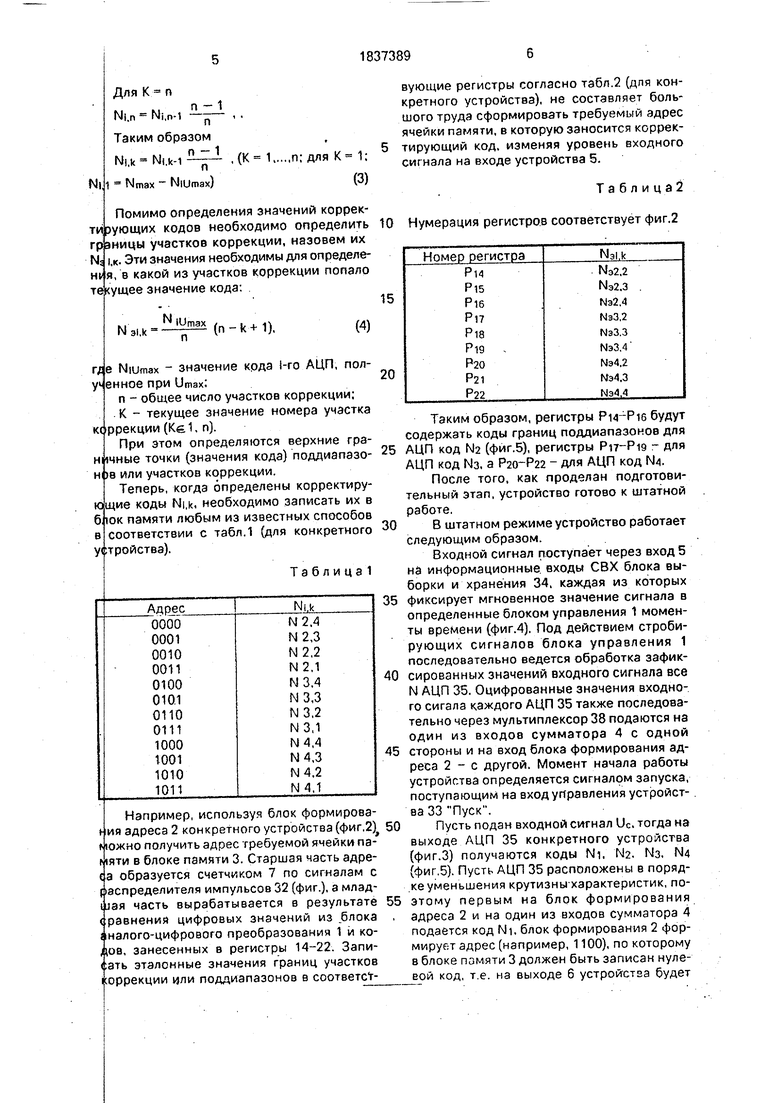

АЦП линейны и проходят через нуль, а диапазон обрабатываемых сигналов лежит в пределах от нуля до Umax. При значении сигнала, равного Umax, на АЦП наблюдаются наибольшие различия в оцифрованных значениях этого сигнала, равное Лпзх . Целесообразно пронумеровать АЦП в порядке уменьшения крутизны характеристик (фиг.5). На диаграмме показаны характеристики четырех АЦП конкретного устройства с блоком формирования адреса, приведенного на фиг,2 и с блоком управления - на фиг.б.

Для того, чтобы уменьшить максимальную погрешность Дпах в К раз, необходимо

f

разбить весь диапазон изменения аналогового сигнала равномерно или неравномерно на К участков коррекции. На фиг.5 показан случай для К - 4 равномерного разбиения. Смысл коррекции заключается в приведении исходных характеристик АЦП к характеристике, имеющей наибольшую крутизну или к идеальной характеристике, путем кусочно-линейной аппроксимации. При

этом максимальная погрешность уменьшается в К раз. Таким образом количество участков коррекции определяется из требования к значению допустимой погрешности устройства, т.е.

35

К Anax /fy.,

О)

где Ьц - максимально допустимая погрешность устройства;

ах - максимальная погрешность устройства без коррекции.

Пусть N - текущее значение кода 1-го АЦП, тогда

Ni Ni + Ni.k,(2)

где NI - скорректированное значение кода:

Ni,k - корректирующий код для 1-го АЦП в К-ом участке коррекции (КЈ 1,п),

Для К - 1

Nj.1 Nmax - NiUmax,

где Nmax - максимальное значение кода или истинное значение кода при Umax;

NiUmax максимальное значение кода

ДЛЯ iTO АЦП ПрИ Umax.

Для К 2

Ni.2 Nu--- - ,

где п - общее количество участков коррекции.

,(K 1n; для К 1;

(3)

Помимо определения значений корректирующих кодов необходимо определить границы участков коррекции, назовем их Ns I,K. Эти значения необходимы для определена я, в какой из участков коррекции попало текущее значение кода:

вующие регистры согласно табл.2 (для конкретного устройства), не составляет большого труда сформировать требуемый адрес ячейки памяти, в которую заносится коррек- тирующий код. изменяя уровень входного сигнала на входе устройства 5.

Таблица2 Нумерация регистров соответствует фиг.2

15

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство корреляционной обработки широкополосных сигналов | 1988 |

|

SU1619414A1 |

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

| Устройство для измерения температуры | 1986 |

|

SU1394063A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1988 |

|

SU1640710A1 |

| Устройство преобразования информации | 1989 |

|

SU1676099A1 |

| Устройство для обхода узлов сеточной модели | 1985 |

|

SU1322332A1 |

| Устройство корреляционной обработки широкополосных сигналов | 1989 |

|

SU1741274A2 |

| Устройство для передачи телеметрической информации | 1984 |

|

SU1231529A1 |

| Устройство для съема информации с сеточной электромодели | 1980 |

|

SU962985A1 |

| СПОСОБ И УСТРОЙСТВО СИНТЕЗА, ПЕРЕДАЧИ, ПРИЕМА, АНАЛИЗА И ОЦЕНКИ МНОГОВАРИАНТНЫХ ПО ФОРМЕ, МНОГОПОЗИЦИОННЫХ И ЛОКАЛЬНЫХ ПО СПЕКТРУ СИГНАЛОВ | 2000 |

|

RU2160509C1 |

Изобретение относится к области вычислительной техники. Цель изобретения состоит в повышении точности, Устройство содержит блок аналого-цифрового преобразования из п устройств выборки и хранения, в которых последовательно запоминаются мгновенные значения выходного сигнала на время обработки их соответствующими ана- лого-цифровыми преобразователями. Оцифрованные значения входного сигнала с одной стороны поступают на блок формирования адреса, с другой стороны - на сумматор, на второй вход которого поступают корректирующие коды из блока памяти, выбранные по адресу, определенному блоком формирования адреса. 2 з.п. ф-лы, 6 ил.

N

(Umax

П

(n - k + 1),

где Niumax - значение кода 1-го АЦП, пол- енное при Umax:

n - общее число участков коррекции: К - текущее значение номера участка

коррекции (Кб 1. n).

При этом определяются верхние гра- (Чные точки (значения кода) поддиапазо- )в или участков коррекции.

Теперь, когда определены корректиру- кЖцие коды Ni,k, необходимо записать их в

б,

ок памяти любым из известных способов соответствии с табл.1 (для конкретного

устройства).

Та б л и ц а 1

Например, используя блок формирования адреса 2 конкретного устройства (фиг.2) ожно получить адрес требуемой ячейки па- h яти в блоке памяти 3. Старшая часть адре- са образуется счетчиком 1 по сигналам с распределителя импульсов 32 (фиг.), а млад- иая часть вырабатывается в результате равнения цифровых значений из .блока (талого-цифрового преобразования 1 и кодов, занесенных в регистры 14-22. Запивать эталонные значения границ участков коррекции или поддиапазонов в соответст20

Таким образом, регистры Рщ-Pie будут содержать коды границ поддиапазонов для

АЦП код Na (фиг.5), регистры Pu-Pi9 - для АЦП код N3, a P2Q-P22 - для АЦП код N4.

После того, как проделан подготовительный этап, устройство готово к штатной работе.

В штатном режиме устройство работает следующим образом.

Входной сигнал поступает через вход 5 на информационные входы СВХ блока выборки и хранения 34, каждая из которых

фиксирует мгновенное значение сигнала в определенные блоком управления 1 моменты времени (фиг.4). Под действием строби- рующих сигналов блока управления 1 последовательно ведется обработка зафиксированных значений входного сигнала все N АЦП 35. Оцифрованные значения входного сигала каждого АЦП 35 также последовательно через мультиплексор 38 подаются на один из входов сумматора 4 с одной

стороны и на вход блока формирования адреса 2-е другой. Момент начала работы устройства определяется сигналом запуска, поступающим на вход управления устройства 33 Пуск.

Пусть подан входной сигнал Uc. тогда на выходе АЦП 35 конкретного устройства (фиг.З) получаются коды NI, N2. N3, N4 (фиг.5). Пусть АЦП 35 расположены в порядке уменьшения крутизныхарактеристик, поэтому первым на блок формирования адреса 2 и на один из входов сумматора 4 подается код , блок формирования 2 формирует адрес (например, 1100), по которому в блоке памяти 3 должен быть записан нуле- еой код, т.е. на выходе 6 устройства будет

сам код NI. Следующим блок управления 1 пропускает через мультиплексор 38 (фиг.4) код N2. При этом блок формирования адреса 2 выдает адрес 0001 следующим образом. Счетчик 7 (фиг.2) выработает полуадрес А-|А2 00, дешифратор 8 разрешит проход на один из входов мультиплексоров 23-25 информации (кодов границ поддиапазонов для АЦП 35) из регистров . Через мультиплексоры 23-25 эти коды попадут на один из входов схем сравнения 26-28, на второй вход которых подается сам код N2. На выходе блока формирования адреса 2 будем иметь код А1А2АзА4 0001. По этому адресу из блока памяти 3 будет выбран код N2,3. который поступает на один из входов сумматора 4. на другой вход которого подается сам код N2, на выходе устройства 6 будем иметь скорректированный код N2. Аналогично, для кодов Мз и N4 будут сформированы адреса ячеек памяти 0101 и 1001 соответственно, по которым будут выбраны корректирующие коды ,з и N4,3 (фиг.5), а на выходе 6 будем иметь скорректированные коды N3 и N4.

Рассмотрим работу блока формирования адреса 2 для конкретного устройства, фиг.2. Счетчик 7 формирует два старших разряда адреса, по которому идет обращение к блоку памяти 3, принимая на счетный вход импульсы от блока управления 1 (фиг.З). С другой стороны через дешифратор 8 счетчик 7 стробирует соответствующую группу из регистров 14-16, или 17-19, или 20-22.m-рззрядные слова (разрядность регистров равна разрядности используемых в устройства АЦП) из соответствующей группы регистров 14-16. 17-19, 20-22 через мультиплексоры 23 25 подаются на один из входов схем сравнения 26-28, на другой аход которых подаются m-разрядные слова с АЦП 35. В случае применения регистров с третьим состоянием (типа 564ИР6) мультиплексоры использовать не надо. На основании результатов сравнения, формируемых одновременно, на схемах И 29 и ИЛИ 30 получаются два младших разряда адреса, по которому идет обращение к блоку памяти 3. Итак, блок формирования адреса 2 обращается к блоку памяти 3 по адресу, в котором старшие разряды соответствуют номеру АЦП, а младшие - номеру участка коррекции или поддиапазона. В блоке памяти 3 по адресу выбирается соответствующий корректирующий код, который подается на второй вход сумматора 4. С выхода сумматора 4 снимается откорректированное значение оцифрованного входного сигнапа, его выход является выходом устройства 6

Покажем, как производится расчет значений корректирующих кодов и границ участков коррекции для конкретного устройства, но имеющего шесть участков коррекции для каждого АЦП на примере. Принимаемые допущения:

-диапазон преобразуемого сигнала 256 ед., для 8-ми разрядного АЦП (например 1107ПВ2);

- наихудший АЦП N4 имеет для максимального значения сигнала код Kl4max 250 ед.;

- максимальная допустимая погрешность устройства Aft 1 ед.; - входной сигнал UBX 100 ед. (оцифрованное значение).

Погрешность АЦП N4 для максимального значения сигнала составит:

Алах Мидеалтах - N4maX 256 - 250 6 (ед.)(5)

Тогда количество поддиапазонов разбиение согласно формуле (1) составит:

25

п Дтах //V 6

Разобьем весь диапазон входного сигнала на шесть поддиапазонов.

Согласно формуле (4), будем иметь следующие точки границ поддиапазонов дл идеальной характеристики:

N31,1 256ед.

Мэ1.2 213ед.

№и 170 ед.

НЭ1,4 128ед, Not.s - 85 ед,

N3i.6 -43efl. для характеристики АЦП N4:

N34,1 250 ед.

МЭ4.2 208 ед. N34, ед.

Мэ4,4 125 ед.

N34,5 83 ед.

N34,6 42 ед.

Так как принято допущения, что Hex ЮО ед., то значения входного сигнала попадает в четвертый поддиапазон (граничные точки по идеальной характеристике 85 ед. и 128 ед., а для АЦП N4-83 ед и 125 ед )

Поправка для четвертого поддиагазчча для АЦП N4 рассчитывается по фон , /л ), следовательно,

55

N4,4 N4,3 -Q 3 ед.

Код для АЦП N4 определяется по формуле:

М4 М4тах ,Т-

и„

-

(б)

для ивх 100 ед.

N4 - 250 х -с - 98 ед.

После коррекции, согласно формулы (2), дем иметь

Nd 98efl.+ 3 ед 101 ед..

Л 101 ед. - 100 ед. 1 ед

Очевидно, что в пределах всего дизпа- эта погрешность не превзойдет допу- имой.

Что и требовалось доказать.

Покажем теперь, что предлагаемое устройство позволяет значительно снизить аппаратурные затраты, сохранив при этом з сданную точность и требуемое быстродействие. Так для реализации выше приведенного примера известными устройствами ,5, потребовалось бы ячеек памяти,равное

256 х 4 1024, в предлагаемом решении

количество ячеек памяти составит К б х 3 18. Правда,добавляются сумматор, мультиплексор и блок формирования адреса. Но при этом необходимо иметь ввиду требуемое быстродействие. Существующие ИМ ОЗУ большого объема имеют относительное низкое быстродействие. Следовательно, при быстродействиях }равных десяткам наносекунд 5 количество ИС ОЗУ резко возрастает для того, чтобы реализовать тзебуемый объем ОЗУ, одновременно рас- тзт и сложность блока управления. Так са- t а быстродействующая ИС ОЗУ 1 эООРУ073, имеющая быстродействие 10,не имеет организацию 64 х 4. Следовательно, их потребуется порядка 32 штук. Сложность шока управления при этом увеличится приблизительно в три раза по сравнению с предлагаемым решением (фиг.6). Количество же микросхем блока формирования адреса в нашем случае будет равно 15, ИС ОЗУ - 2, мультиплексор - 1, сумматор - 1. Таким образом, даже без учета того, что сложность блока управления в предлагаемом решении значительно ниже, чем в известных решениях 2,5, аппаратурные затраты е предлагаемом решении меньше, чем в известных при сэхрзнении заданной точности и трзбуемо- го быстродействия.

Формула изобретения I 1. Устройство аналого-цифрового пре- о.бразования, содержащее блок аналого- цифрового преобразования, вход которого является входной шиной, а выходы соединены с соотвртствующимь первыми входами сумматора, вторые входы которого соединены с выходами блока памяти, а еычоды являются зыходной шиной, отличающийс я тем, что, с целью повышения точности в него введен блок формирования адреса, информационные входы которого объединены с соответствующими первыми входами сумматора, выходы соединены с соответствующими входами блока памяти, а управляющий вход подключен к первому управляющему выходу блока аналого-цифрового преобразования.

выполнен на блоке сравнения, первые входы которого являются информационными входами блока формирования адреса, управляющим входом которою является вход

счетчика, а выходами являются соответственно выходы счетчика и блока сравнения, вторые входы последнего из которых соединены с соответствующими входами блока мультиплексоров, соответствующие информационные входы которого подключены к выходам блока регистров, а управляющие входы объединены с входами дешифратора и соединены с выходами счетчика, выходы дешифратора подключены к соответствующим входам блока регистров.

синхронизации распределителя импульсов, управляющий вход которого является шиной Пуск, первый выход является первым управляющим входом блока, вторые выходы соединены с соответствующими управляющими входами п устройств выборки-хранения, информационные входы которых объединены и являются входом блока, а выходы соединены с соответствующими информационнымивходамип

аналого-цифровых преобразователей, управляющие входы которых соединены с третьими выходами распределителя импульсов соответственно, а выходы подключены к соответствующим информационными входам

мультиплексора, управляющий вход которого соединен с четвертым выходом распределителя импульсов, а выходы являются выходом блока.

От блока аналога-цифрового преобразованоч

6

fc

Фиг.1

Фиг.З

tifffftitx

tyt

htf

1

r

fft

t /J

4

АЧ fy VC У У М

s3

Wtfffx

MffX

Фие.б

Авторы

Даты

1993-08-30—Публикация

1990-04-28—Подача