о

vj О О О 4D

стемы. В зависимости от диапазона преобразования сигнала по каналу на предыдущем цикле обработки массивов и от расположения его кода в одной из зон шкалы аналого-цифрового преобразователя 5 из алгоритма преобразования сигнала может быть исключен шаг определения диапазона, что сокращает время обработки сигнала. В зависимости от соотношения диапазонов преобразования сигналов по выбранному и предыдущему каналам, коды которых занесены в регистры 14 и 15, дешифратор 16 управляет блоком 17, который формирует импульс запуска аналого-цифрового преобразователя 5, оптимально задержанный на время переходного процесса блока 4 масштабирования, что при обработке массивов информации приводит к существенному сокращению времени обработки, 2 з.п.ф-лы, 13 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговая система сбора и обработки информации | 1986 |

|

SU1363271A1 |

| УСТРОЙСТВО СБОРА И РЕГИСТРАЦИИ ИНФОРМАЦИИ | 1998 |

|

RU2125239C1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ИНФОРМАЦИИ | 1996 |

|

RU2097703C1 |

| УСТРОЙСТВО ДЛЯ ИССЛЕДОВАНИЯ АМПЛИТУДНО-ЧАСТОТНЫХ ХАРАКТЕРИСТИК ЧЕТЫРЕХПОЛЮСНИКА | 1992 |

|

RU2065667C1 |

| ТЕЛЕВИЗИОННАЯ СИСТЕМА ВЫСОКОГО РАЗРЕШЕНИЯ | 1996 |

|

RU2127961C1 |

| СПОСОБ ГЕОЭЛЕКТРОРАЗВЕДКИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2006886C1 |

| Устройство для ввода информации от аналоговых датчиков | 1985 |

|

SU1298734A1 |

| СПОСОБ И УСТРОЙСТВО СЕЛЕКЦИИ СИГНАЛОВ НАДВОДНОЙ ЦЕЛИ В МОНОИМПУЛЬСНОЙ РЛС | 2004 |

|

RU2278397C2 |

| Устройство для передачи и приема информации | 1986 |

|

SU1399797A1 |

| МЕТЕОРОЛОГИЧЕСКАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 1991 |

|

RU2084922C1 |

Изобретение относится к вычислительной технике и может быть использовано в автоматических системах преобразования иобработки информации и при проектировании гибридных управляющих и вычислительных комплексов. Изобретение позволяет повысить быстродействие. Это достигается тем, что синхронизатор 8 под управлением блока 13 разворачивает различные временные диаграммы работы си

Изобретение относится к вычислительной технике и может быть использовано в автоматических системах преобразования и обработки информации и при проектировании гибридных управляющих и вычислительных комплексов.

Целью изобретения является повышение быстродействия.

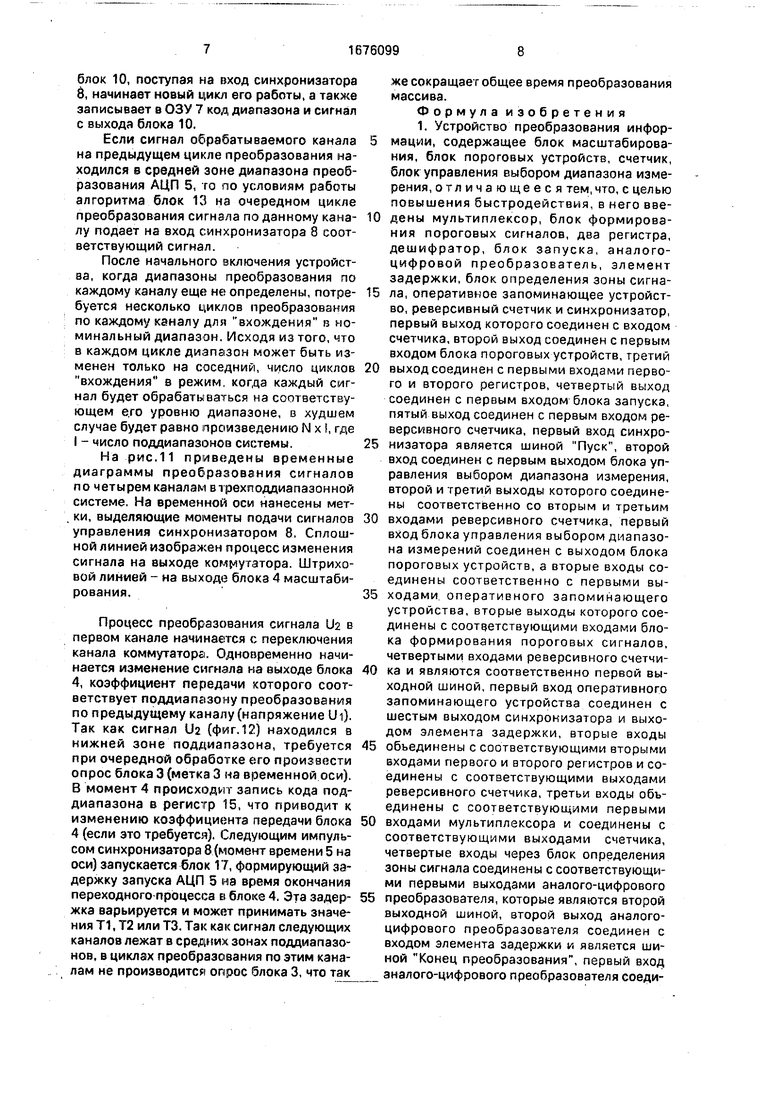

На фиг.1 приведена функциональная схема устройства; на фиг.2 - то же, блока пороговых устройств; на фиг.З - то же, блока масштабирования; на фиг.4 -тоже, синхронизатора; на фиг.5 - то же, блока определения зоны сигнала; на фиг.б - то же, блока формирования пороговых сигналов; на фиг.7 - то же, блока управления выбором диапазона измерения; на фиг.8 - то же, блока запуска; на фиг.9 - то же, кодирующего блока; на фиг. 10 - то же, нормализатора кода; на фиг.11 - то же, блока формирования двоичного кода; на фиг.12 - временные диаграммы работы устройства; на фиг.13 --алгоритм разбиения сигналов на диапазоны.

Устройство (фиг.1) содержит N шин 1 входных аналоговых сигналов, мультиплексор 2, блок 3 пороговых устройств, блок 4 масштабирования, аналого- цифровой преобразователь 5, элемент 6 задержки, оперативное запоминающее устройство 7 (ОЗУ), синхронизатор 8, шина 9 подключения к ЭВМ, блок 10 определения сигнала, реверсивный счетчик 11, блок

12формирования пороговых сигналов, блок

13управления выбором диапазона измерения, регистры 14 и 15, дешифратор 16, блок 17 запуска, счетчик 18, шину 19 Пуск.

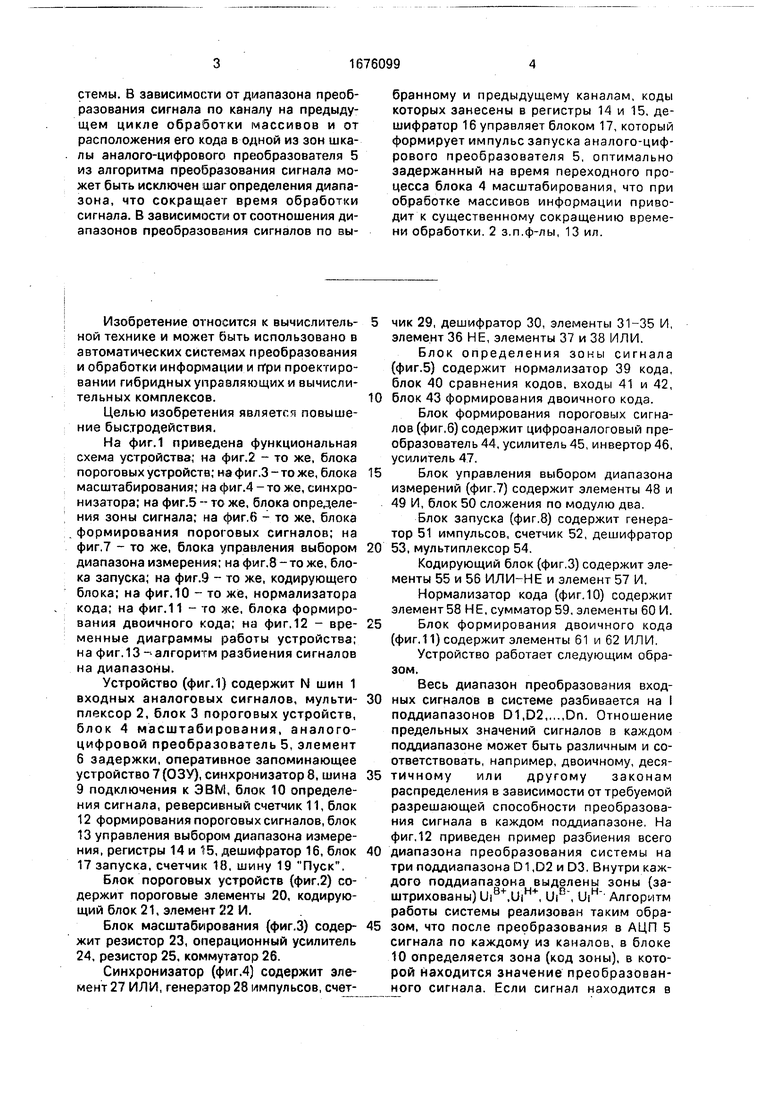

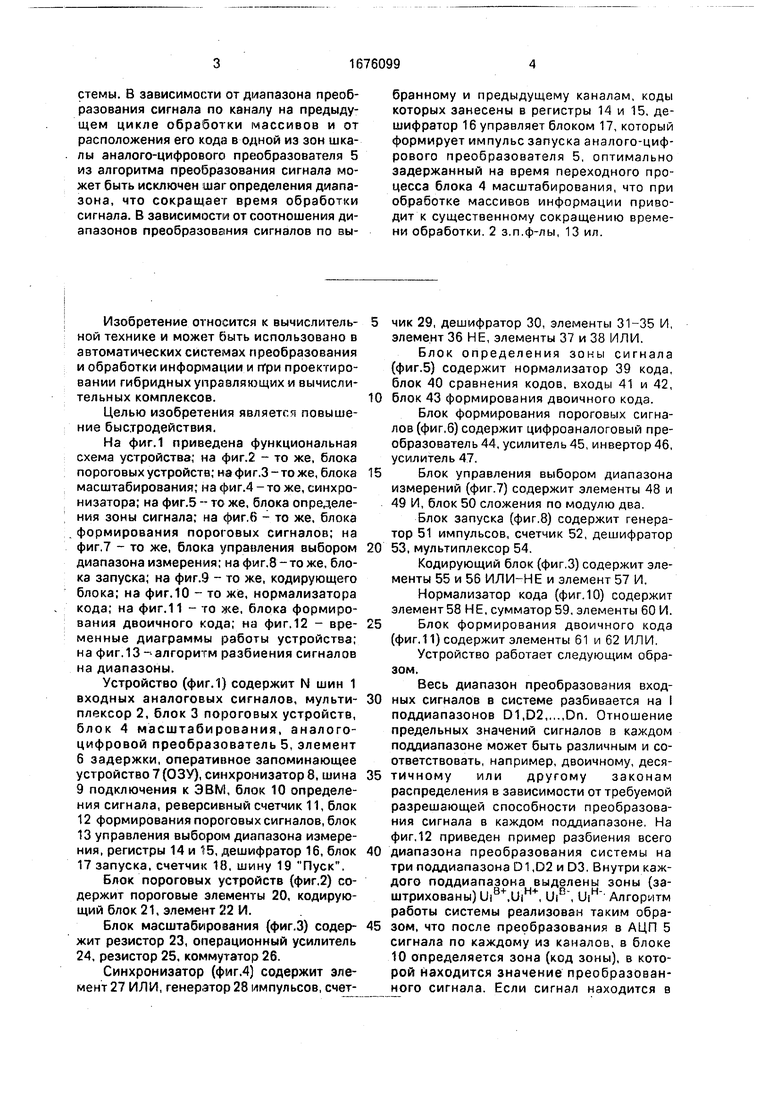

Блок пороговых устройств (фиг.2) содержит пороговые элементы 20, кодирующий блок 21, элемент 22 И.

Блок масштабирования (фиг.З) содержит резистор 23, операционный усилитель 24, резистор 25, коммутатор 26.

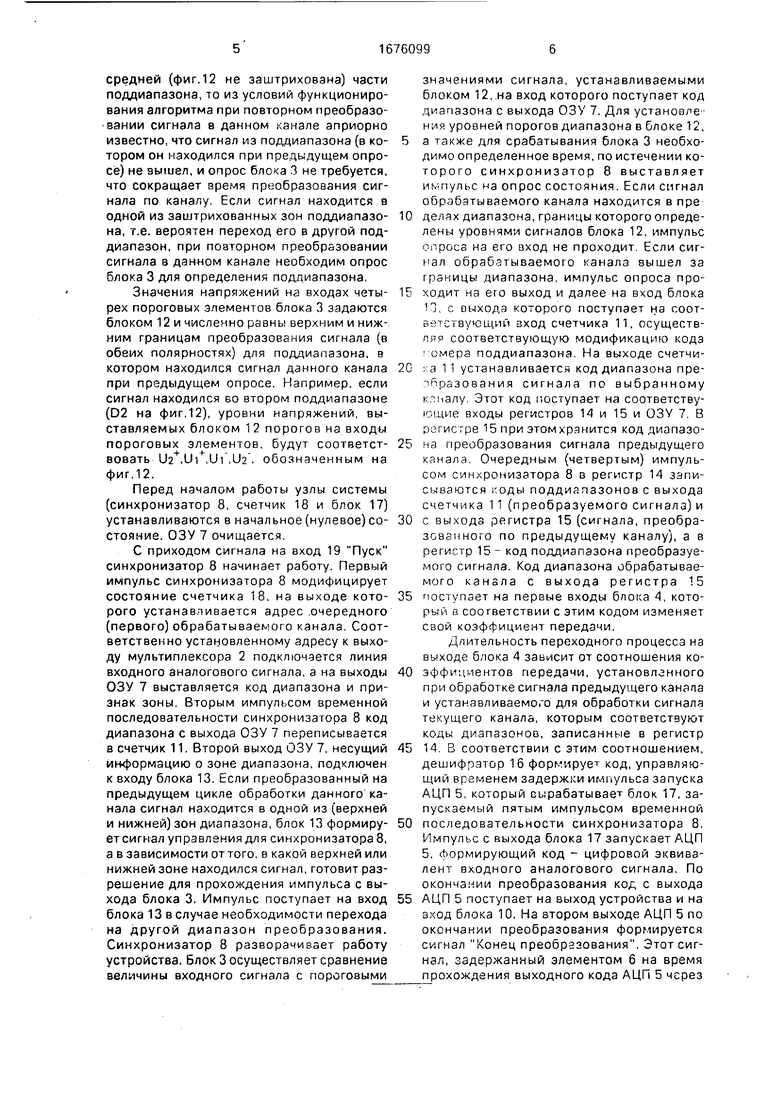

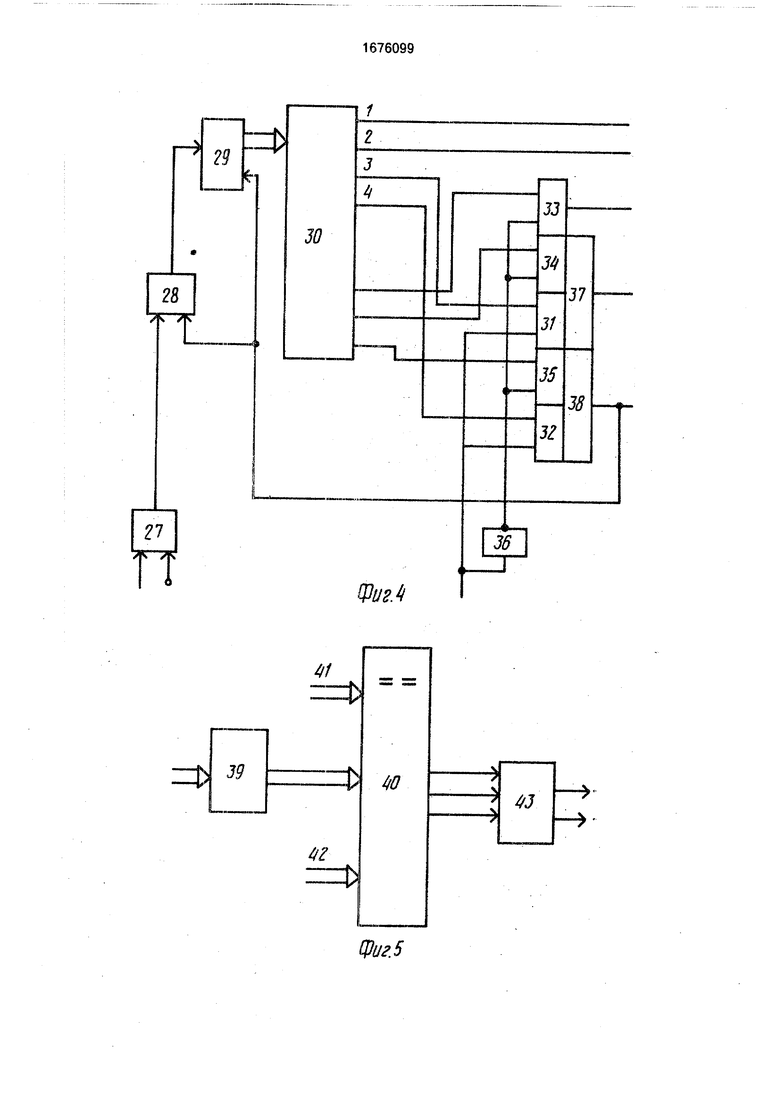

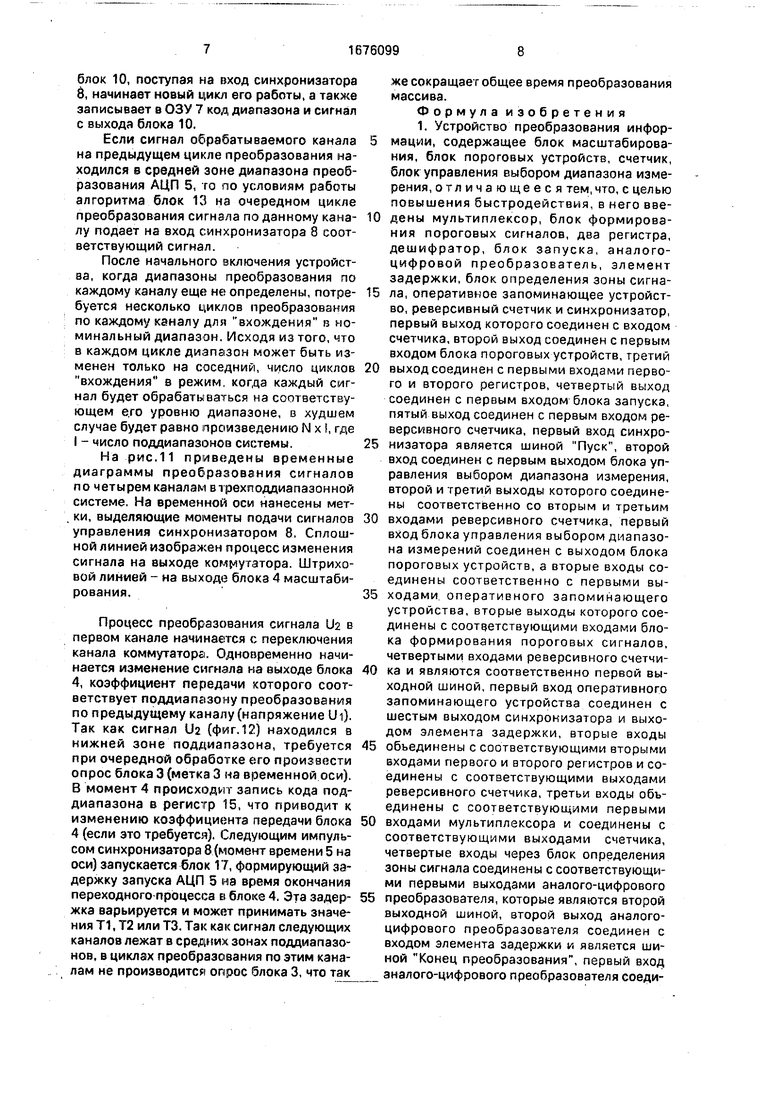

Синхронизатор (фиг.4) содержит элемент 27 ИЛИ, генератор 28 импульсов, счетчик 29, дешифратор 30, элементы 31-35 И, элемент 36 НЕ, элементы 37 и 38 ИЛИ.

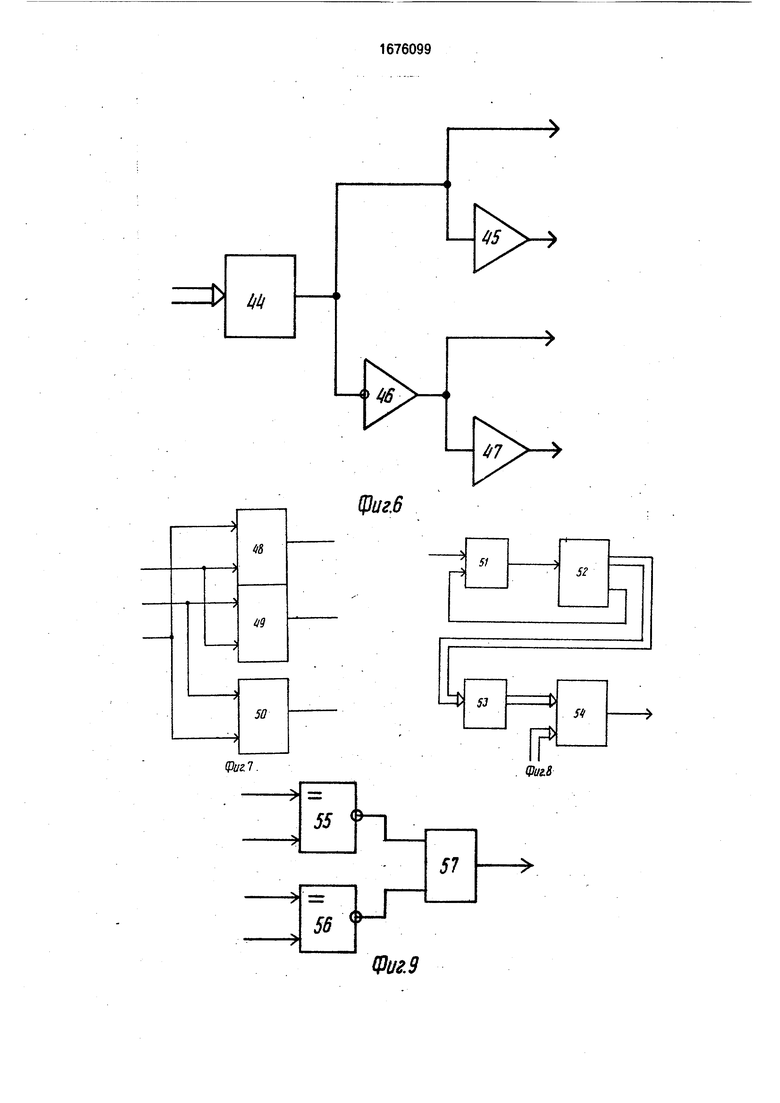

Блок определения зоны сигнала (фиг.5) содержит нормализатор 39 кода, блок 40 сравнения кодов, входы 41 и 42,

блок 43 формирования двоичного кода.

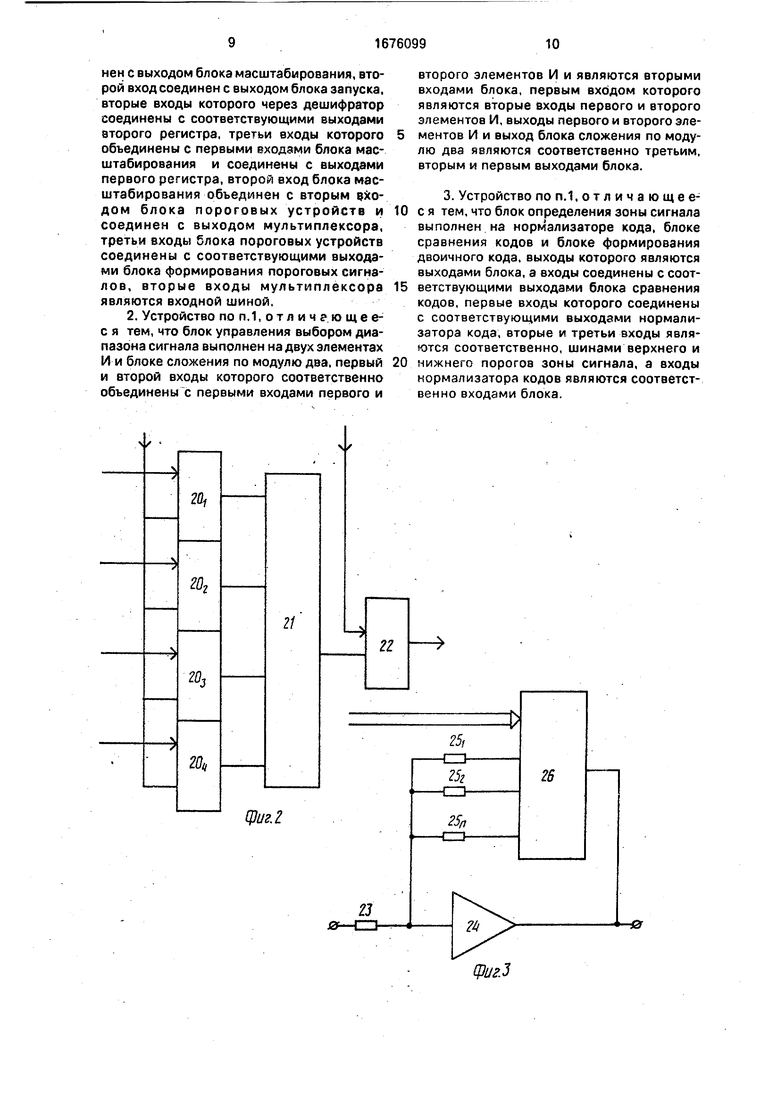

Блок формирования пороговых сигналов (фиг.б) содержит цифроаналоговый преобразователь 44, усилитель 45, инвертор 46, усилитель 47.

Блок управления выбором диапазона

измерений (фиг.7) содержит элементы 48 и 49 И, блок 50 сложения по модулю два.

Блок запуска (фиг.8) содержит генератор 51 импульсов, счетчик 52, дешифратор

53, мультиплексор 54.

Кодирующий блок (фиг.З) содержит элементы 55 и 56 ИЛИ-НЕ и элемент 57 И.

Нормализатор кода (фиг. 10) содержит элемент 58 НЕ, сумматор 59, элементы 60 И.

Блок формирования двоичного кода (фиг.11) содержит элементы 61 и 62 ИЛИ.

Устройство работает следующим образом.

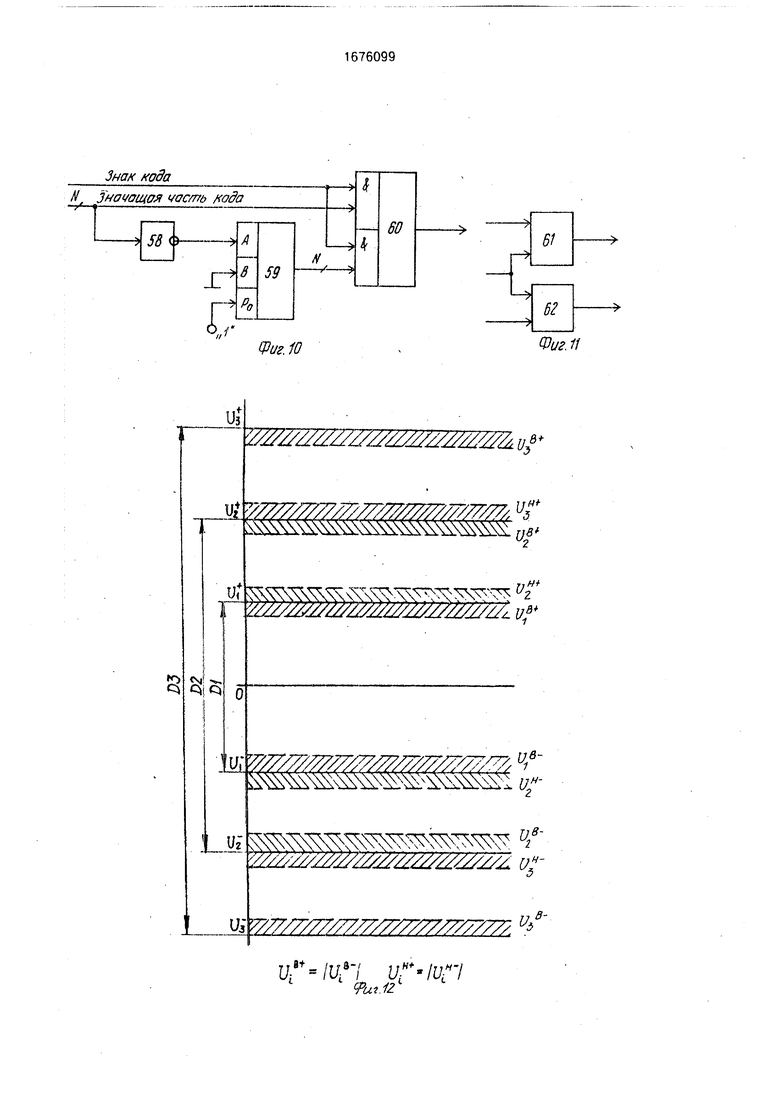

Весь диапазон преобразования входных сигналов в системе разбивается на I поддиапазонов D1,D2,...,Dn. Отношение предельных значений сигналов в каждом поддиапазоне может быть различным и соответствовать, например, двоичному, десятичному или другому законам распределения в зависимости от требуемой разрешающей способности преобразования сигнала в каждом поддиапазоне. На фиг.12 приведен пример разбиения всего

диапазона преобразования системы на три поддиапазона D1.D2 и D3. Внутри каждого поддиапазона выделены зоны (заштрихованы) UiB+,U)H4, UIB, UIH Алгоритм работы системы реализован таким образом, что после преобразования в АЦП 5 сигнала по каждому из каналов, в блоке 10 определяется зона (код зоны), в которой находится значение преобразованного сигнала. Если сигнал находится в

средней (фиг.12 не заштрихована) части поддиапазона, то из условий функционирования алгоритма при повторном преобразовании сигнала в данном канале априорно известно, что сигнал из поддиапазона (в котором он находился при предыдущем опросе) не вышел, и опрос блока 3 не требуется, что сокращает время преобразования сигнала по каналу. Если сигнал находится в одной из заштрихованных зон поддиапазона, т.е. вероятен переход его в другой поддиапазон, при повторном преобразовании сигнала в дан+ном канале необходим опрос блока 3 для определения поддиапазона.

Значения напряжений на входах четырех пороговых элементов блока 3 задаются блоком 12 и численно равны верхним и нижним границам преобразования сигнала в обеих полярностях) для поддиапазона, э котором находился сигнал данного канала при предыдущем опросе. Например, если сигнал находился во втором поддиапазоне (D2 на фиг.12), уровни напряжений, выставляемых блоком 12 порогов на входы пороговых элементов, будут соответствовать U2+,Ui+,Ui ,1)2 , обозначенным на фиг.12.

Перед началом работы узлы системы (синхронизатор 8, счетчик 18 и блок 17) устанавливаются в начальное (нулевое) состояние. ОЗУ 7 очищается.

С приходом сигнала на вход 19 Пуск синхронизатор 8 начинает работу. Первый импульс синхронизатора 8 модифицирует состояние счетчика 18, на выходе которого устанавливается адрес очередного (первого) обрабатываемого канала. Соответственно установленному адресу к выходу мультиплексора 2 подключается линия входного аналогового сигнала, а на выходы ОЗУ 7 выставляется код диапазона и признак зоны. Вторым импульсом временной последовательности синхронизатора 8 код диапазона с выхода ОЗУ 7 переписывается в счетч.ик 11. Второй выход ОЗУ 7, несущий информацию о зоне диапазона, подключен к входу блока 13. Если преобразованный на предыдущем цикле обработки данного канала сигнал находится в одной из (верхней и нижней) зон диапазона, блок 13 формиру- етсигнал управления для синхронизатора 8, а в зависимости от того, в какой верхней или нижней зоне находился сигнал, готовит разрешение для прохождения импульса с выхода блока 3, Импульс поступает на вход блока 13 в случае необходимости перехода на другой диапазон преобразования. Синхронизатор 8 разворачивает работу устройства. Блок 3 осуществляет сравнение величины входного сигнала с пороговыми

значениями сигнала, устанавливаемыми блоком 12, на вход которого поступает код диапазона с выхода ОЗУ 7. Для установле ния уровней порогов диапазона в блоке 12,

а также для срабатывания блока 3 необходимо определенное время, по истечении ко- торого синхронизатор 8 выставляет импульс иа опрос состояния. Если сигнал обрабатываемого канала находится в пре

0 делах диапазона, границы которого определены уровнями сигналов блока 12, импульс опроса на его вход не проходит. Если сигнал обрабатываемого канала вышел за границы диапазона, импульс опроса про5 ходит на его выход и далее на вход блока 13, с выхода которого поступает на соответствующий вход счетчика 11, осуществляя соответствующую модификацию кода омера поддиапазона. На выходе счетчи0 ; .а 11 устанавливается код диапазона пре- Рразования сигнала по выбранному клкалу. Этот код поступает на соответствующие входы регистров 14 и 15 и ОЗУ 7. В регистре 15 при этом хранится код диапазо5 на преобразования сигнала предыдущего канала. Очередным (четвертым) импульсом синхронизатора 8 в регистр 14 записываются коды поддиапазонов с выхода счетчика 11 (преобразуемого сигнала) и

0 с выхода регистра 15 (сигнала, преобразованного по предыдущему каналу), а в регистр 15 - код поддиапазона преобразуемого сигнала. Код диапазона обрабатываемого канала с выхода регистра 15

5 поступает на первые входы блока 4, который в соответствии с этим кодом изменяет свой коэффициент передачи.

Длительность переходного процесса на выходе блока 4 зависит от соотношения ко0 эффициентов передачи, установленного при обработке сигнала предыдущего канапа и устанавливаемого для обработки сигнала текущего канала, которым соответствуют коды диапазонов, записанные в регистр

5 14. В соответствии с этим соотношением, дешифратор 16 формирует код, управляющий временем задержки импульса запуска АЦП 5, который вырабатывает блок 17, запускаемый пятым импульсом временной

0 последовательности синхронизатора 8. Импульс с выхода блока 17 запускает АЦП 5, формирующий код - цифровой эквивалент входного аналогового сигнала. По окончании преобразования код с выхода

5 АЦП 5 поступает на выход устройства и на вход блока 10, На втором выходе АЦП 5 по окончании преобразования формируется сигнал Конец преобразования. Этот сигнал, задержанный элементом б на время прохождения выходного кода АЦП 5 через

блок 10, поступая на вход синхронизатора 8, начинает новый цикл его работы, а также записывает в ОЗУ 7 код диапазона и сигнал с выхода блока 10.

Если сигнал обрабатываемого канала на предыдущем цикле преобразования находился в средней зоне диапазона преобразования АЦП 5, то по условиям работы алгоритма блок 13 на очередном цикле преобразования сигнала по данному каналу подает на вход синхронизатора 8 соответствующий сигнал.

После начального включения устройства, когда диапазоны преобразования по каждому каналу еще не определены, потребуется несколько циклов преобразования по каждому каналу для вхождения в номинальный диапазон. Исходя из того, что в каждом цикле диапазон может быть изменен только на соседний, число циклов вхождения в режим, когда каждый сигнал будет обрабатываться на соответствующем его уровню диапазоне, в худшем случае будет равно произведению N х I, где I - число поддиапазонов системы.

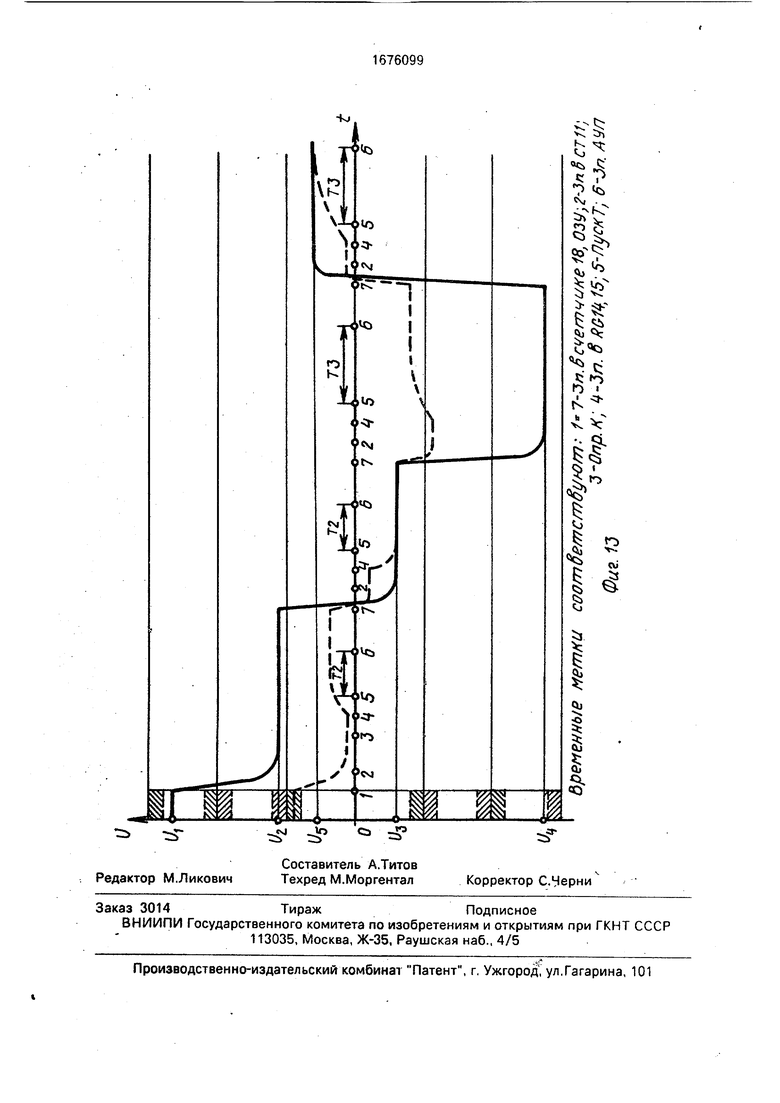

На рис.11 приведены временные диаграммы преобразования сигналов по четырем каналам втрехподдиапазонной системе. На временной оси нанесены метки, выделяющие моменты подачи сигналов управления синхронизатором 8, Сплошной линией изображен процесс изменения сигнала на выходе коммутатора. Штриховой линией - на выходе блока 4 масштабирования.

Процесс преобразования сигнала в первом канале начинается с переключения канала коммутатора. Одновременно начинается изменение сигнала на выходе блока 4, коэффициент передачи которого соответствует поддиапазону преобразования по предыдущему каналу (напряжение Ui). Так как сигнал Da (фиг. 12) находился в нижней зоне поддиапазона, требуется при очередной обработке его произвести опрос блока 3 (метка 3 на временной оси). В момент 4 происходит запись кода поддиапазона в регистр 15, что приводит к изменению коэффициента передачи блока 4 (если это требуется). Следующим импульсом синхронизатора 8 (момент времени 5 на оси) запускается блок 17, формирующий задержку запуска АЦП 5 на время окончания переходного-процесса в блоке 4. Эта задержка варьируется и может принимать значения Т1, Т2 или ТЗ. Так как сигнал следующих каналов лежат в средних зонах поддиапазонов, в циклах преобразования по этим каналам не производится опрос блока 3, что так

же сокращает общее время преобразования массива.

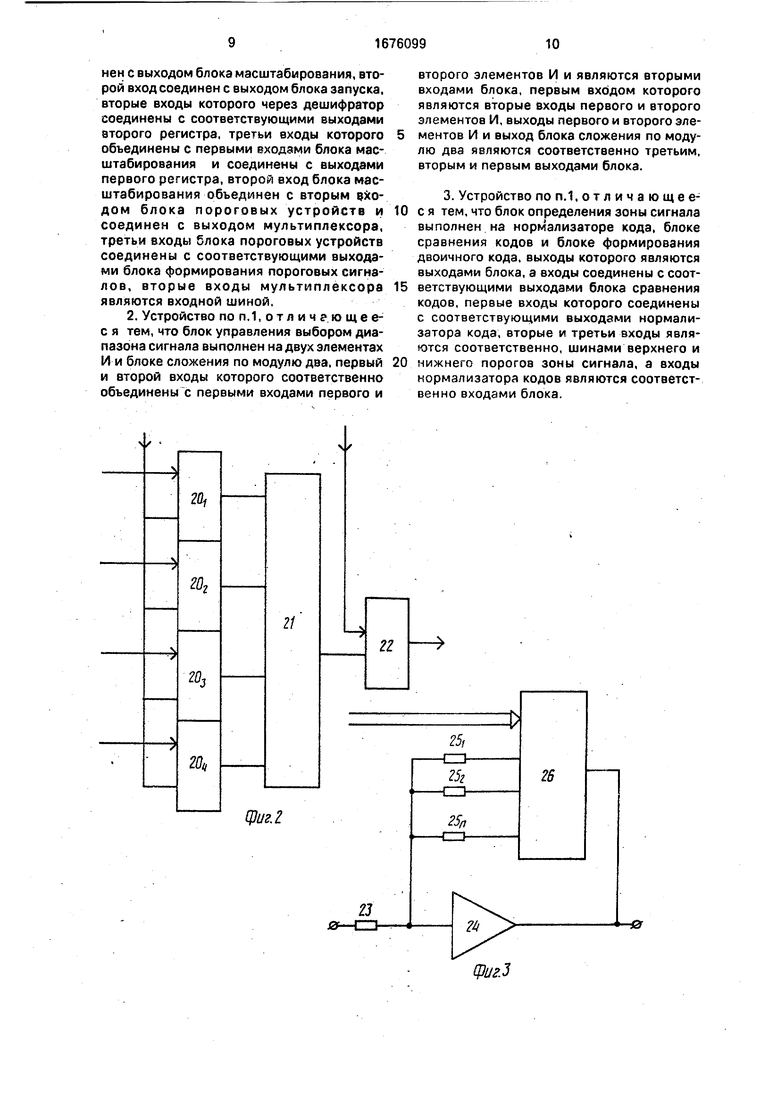

Формула изобретения

0 выход соединен с первыми входами первого и второго регистров, четвертый выход соединен с первым входом блока запуска, пятый выход соединен с первым входом реверсивного счетчика, первый вход синхро5 низатора является шиной Пуск, второй вход соединен с первым выходом блока управления выбором диапазона измерения, второй и третий выходы которого соединены соответственно со вторым и третьим

0 входами реверсивного счетчика, первый вход блока управления выбором диапазона измерений соединен с выходом блока пороговых устройств, а вторые входы соединены соответственно с первыми вы5 ходами, оперативного запоминающего устройства, вторые выходы которого соединены с соответствующими входами блока формирования пороговых сигналов, четвертыми входами реверсивного счетчи0 ка и являются соответственно первой выходной шиной, первый вход оперативного запоминающего устройства соединен с шестым выходом синхронизатора и выходом элемента задержки, вторые входы

5 объединены с соответствующими вторыми входами первого и второго регистров и соединены с соответствующими выходами реверсивного счетчика, третьи входы обь- единены с соответствующими первыми

0 входами мультиплексора и соединены с соответствующими выходами счетчика, четвертые входы через блок определения зоны сигнала соединены с соответствующими первыми выходами аналого-цифрового

5 преобразователя, которые являются второй выходной шиной, второй выход аналого- цифрового преобразователя соединен с входом элемента задержки и является шиной Конец преобразования, первый вход аналого-цифрового преобразователя соединем с выходом блока масштабирования, второй вход соединен с выходом блока запуска, вторые входы которого через дешифратор соединены с соответствующими выходами второго регистра, третьи входы которого объединены с первыми входами блока масштабирования и соединены с выходами первого регистра, второй вход блока масштабирования объединен с вторым эхо- дом блока пороговых устройств и соединен с выходом мультиплексора, третьи входы блока пороговых устройств соединены с соответствующими выходами блока формирования пороговых сигналов, вторые входы мультиплексора являются входной шиной.

$иг2

J0второго элементов И и являются вторыми входами блока, первым входом которого являются вторые входы первого и второго элементов И, выходы первого и второго элементов И и выход блока сложения по модулю два являются соответственно третьим, вторым и первым выходами блока.

25г

26

25п

+-&

-

29

ьц

28

/4VV

П

41

D

t

39

41 Й

L 2

L 4

зз

37

31

Фиг.4

40

-

43

-

Фиг. 5

t

м

nt

W

ФигЛ

55

-

56

US

Щиг.6

QttiS

Фиг. 9

Фиг. 10

V- -IVf l

Фиг. 11

| Способ автоматического выбора диапазона аналого-цифрового преобразования и устройство для его осуществления | 1982 |

|

SU1092721A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Измерения в электронике | |||

| Справочник./Под ред | |||

| В.А.Кузнецова | |||

| М.: Энерго- атомиздат, 1988, с.77, | |||

Авторы

Даты

1991-09-07—Публикация

1989-06-12—Подача