делители, второй 8, третий 9, четвертый 10 и пятый 11 блоки памяти, счетчик 41 адресов, цифроаналоговый преобразователь 42 и блок 43 микропрограммного управленияс Сущность изобретения заключается в том,что увеличивается точность фильтрации во всем диапазоне анализируемых частот за счет умножения последовательности спектральных отсчетов обрабатываемого сигнала на

последовательность корректирующих множителей, которая формируется при вычислении корректирующих множителей из спектральных отсчетов изменяющегося во всем диапазоне анализируемых частот гармонического сигнала, формируемого генератором гармонического (тестового) сигнала при подключении его к входу устройства,, 1 табл,, 3 ил0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления спектра сигналов | 1988 |

|

SU1649566A1 |

| Устройство для вычисления спектра сигналов | 1989 |

|

SU1667102A1 |

| Устройство для вычисления спектра сигналов | 1986 |

|

SU1363244A1 |

| Устройство для быстрого преобразования Фурье | 1983 |

|

SU1130872A1 |

| Устройство для цифровой фильтрацииНА OCHOBE диСКРЕТНОгО пРЕОбРАзОВА-Ния фуРьЕ | 1979 |

|

SU840922A1 |

| Устройство корреляционной обработки широкополосных сигналов | 1988 |

|

SU1619414A1 |

| Устройство корреляционной обработки широкополосных сигналов | 1989 |

|

SU1741274A2 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| Анализатор спектра Фурье | 1984 |

|

SU1226486A1 |

| Устройство для реализации двумерного быстрого преобразования фурье | 1983 |

|

SU1142845A1 |

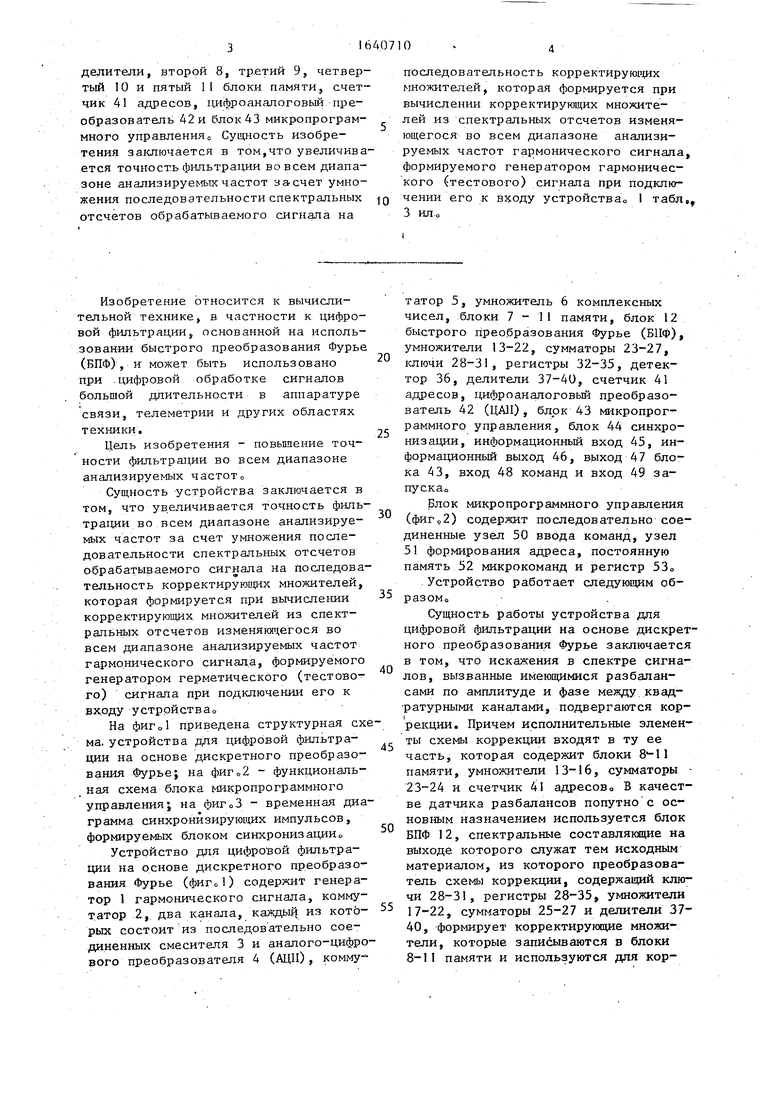

Изобретение относится к вычислительной технике, в частности к цифровой фильтрации, основанной на использовании быстрого преобразования Фурье. Целью изобретения является повышение точности фильтрации во всем диапазоне анализируемых частот Цель достигается тем, что в устройство для цифровой фильтрации на основе дискретного преобразования Фурье, содержащее генератор 1 гармонического (тестового) сигнала, коммутатор 2, два канала, каждый из которых состоит из последовательно соединенных смесителя 3 и АЦП 4, коммутатор 5, умножитель 6 комплексных чисел, первый блок 7 памяти, блок БНФ 12, четыре умножителя 13 - 1Ь, пять сумматоров 23 - 27, четыре ключа 28-31, четыре регистра 32-35, детектор 36, блок 44 синхронизации, введены пятый 17, шестой 18, седьмой 19, восьмой 20, девятый 21 и десятый 22 умножители, первый 37, второй 38, третий 39 и четвертый 40 (О (Л С оэ Јь Фиг. /

Изобретение относится к вычислительной технике, в частности к цифровой фильтрации, основанной на использовании быстрого преобразования Фурье (БПФ), и может быть использовано при цифровой обработке сигналов большой длительности в аппаратуре связи, телеметрии и других областях техники.

Цель изобретения - повышение точности фильтрации во всем диапазоне анализируемых частот0

Сущность устройства заключается в том, что увеличивается точность фильтрации во всем диапазоне анализируе- мых частот за счет умножения последовательности спектральных отсчетов обрабатываемого сигнала на последовательность корректирующих множителей, которая формируется при вычислении корректирующих множителей из спектральных отсчетов изменяющегося во всем диапазоне анализируемых частот гармонического сигнала, формируемого генератором герметического (тестового) сигнала при подключении его к входу устройствао

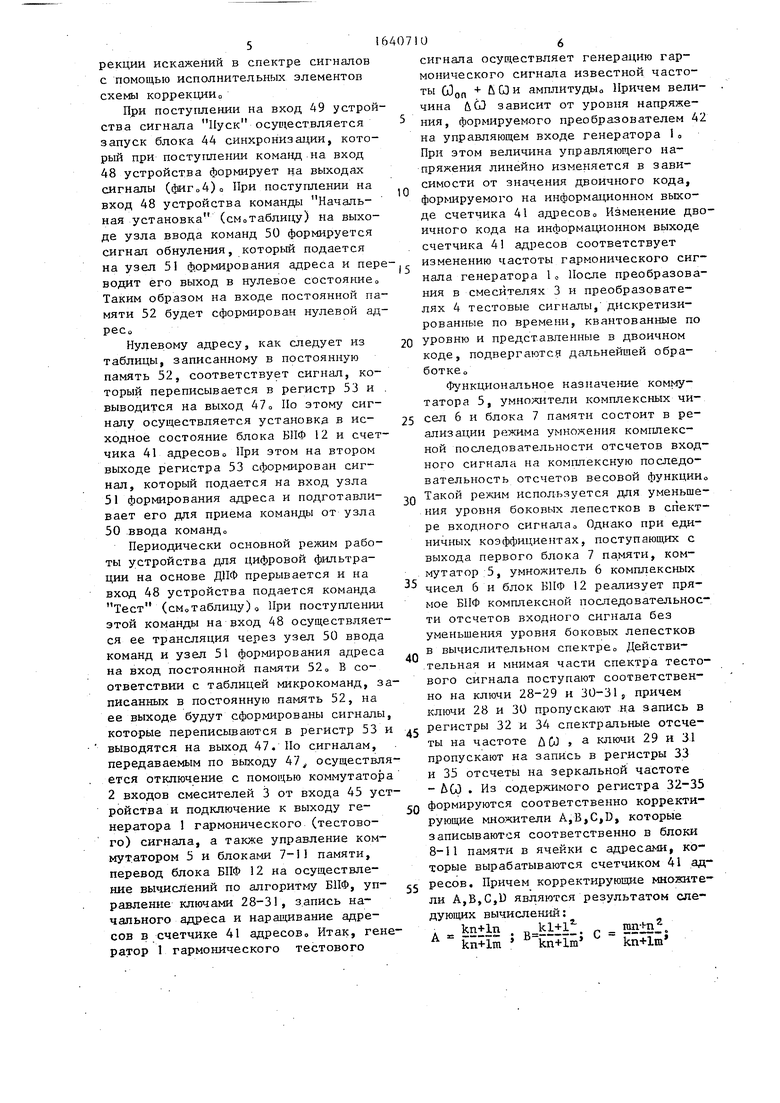

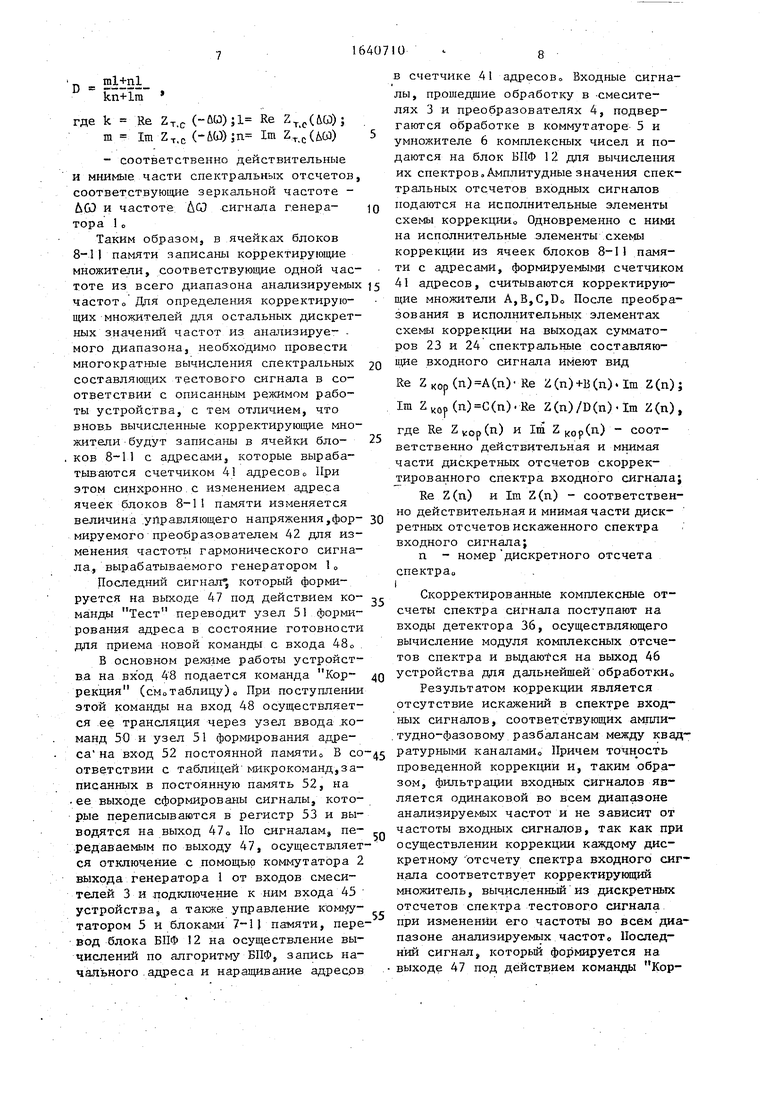

На фиг приведена структурная схма, устройства для цифровой фильтрации на основе дискретного преобразования Фурье; на - функционалъ- ная схема блока микропрограммного управления; на фигоЗ - временная диаграмма синхронизирующих импульсов, формируемых блоком синхронизации Устройство для цифровой фильтрации на основе дискретного преобразования Фурье (фиг) содержит генератор 1 гармонического сигнала, коммутатор 2, два канала, каждый из кото- рых состоит из последовательно соединенных смесителя 3 и аналого-цифрового преобразователя 4 (АЦП), комму0

5

5

5

татор 5, умножитель 6 комплексных чисел, блоки 7-11 памяти, блок 12 быстрого преобразования Фурье (БПФ), умножители 13-22, сумматоры 23-27, ключи 28-31, регистры 32-35, детектор 36, делители 37-40, счетчик 41 адресов, цифроаналоговый преобразователь 42 (ЦА11), блок 43 микропрограммного управления, блок 44 синхронизации, информационный вход 45, информационный выход 46, выход 47 блока 43, вход 48 команд и вход 49 запуска

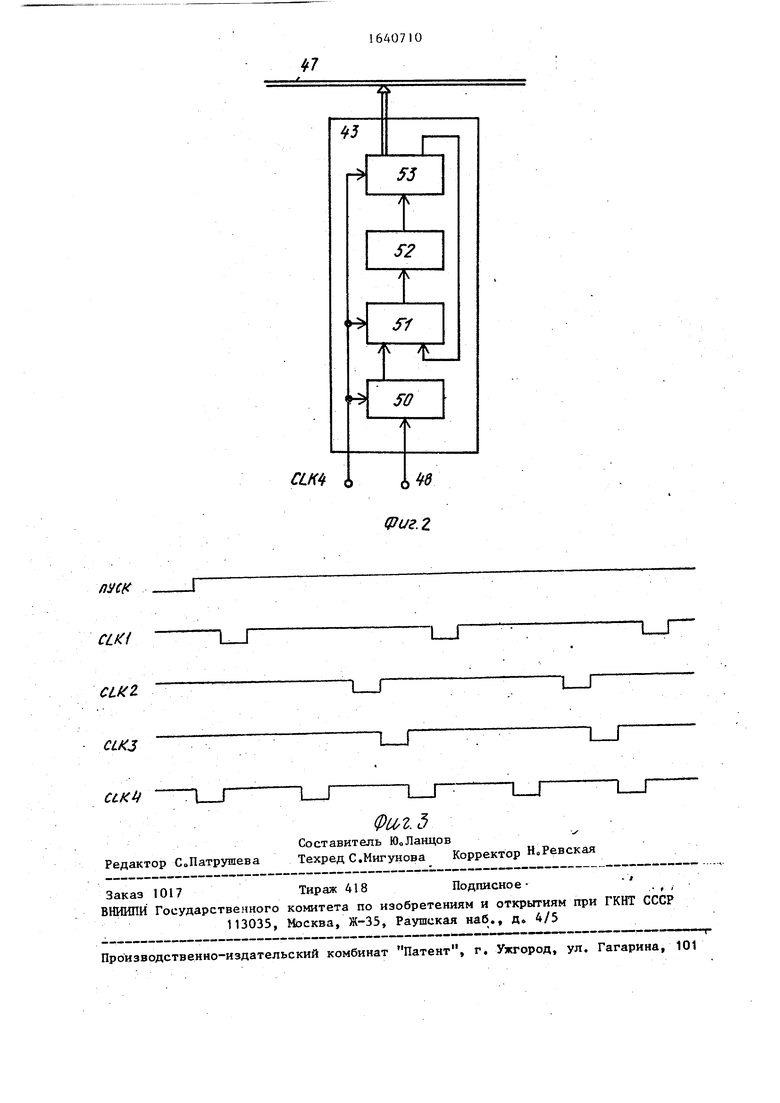

Блок микропрограммного управления (фиг02) содержит последовательно соединенные узел 50 ввода команд, узел 51 формирования адреса, постоянную память 52 микрокоманд и регистр 53 0

Устройство работает следующим об- разомо

Сущность работы устройства для цифровой фильтрации на основе дискретного преобразования Фурье заключается в том, что искажения в спектре сигналов, вызванные имеющимися разбалансами по амплитуде и фазе между квадратурными каналами, подвергаются коррекции. Причем исполнительные элементы схемы коррекции входят в ту ее часть, которая содержит блоки 8W11 памяти, умножители 13-16, сумматоры 23-24 и счетчик 41 адресов,, В качестве датчика разбалансов попутно с основным назначением используется блок БПФ 12, спектральные составляющие на выходе которого служат тем исходным материалом, из которого преобразователь схемы коррекции, содержащий ключи 28-31, регистры 28-35, умножители 17-22, сумматоры 25-27 и делители 37- 40, формирует корректирующие множители, которые записываются в блоки 8-11 памяти и используются для кор

рекции искажении в спектре сигналов с помощью исполнительных элементов схемы коррекциио

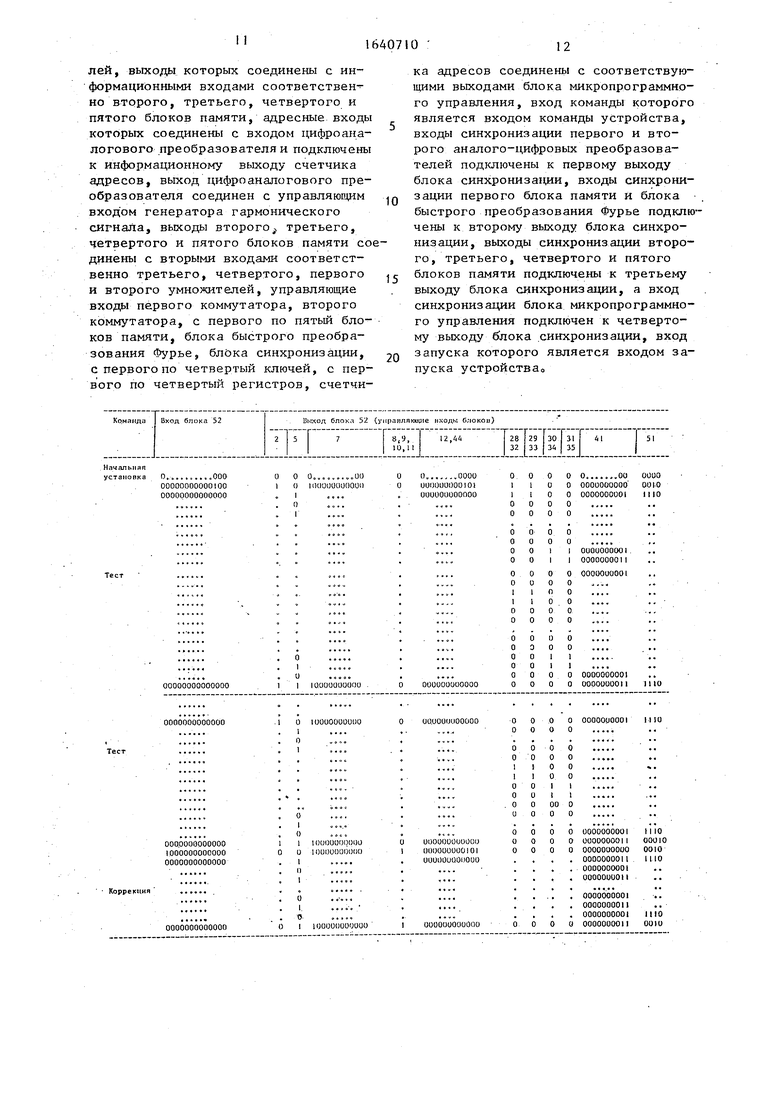

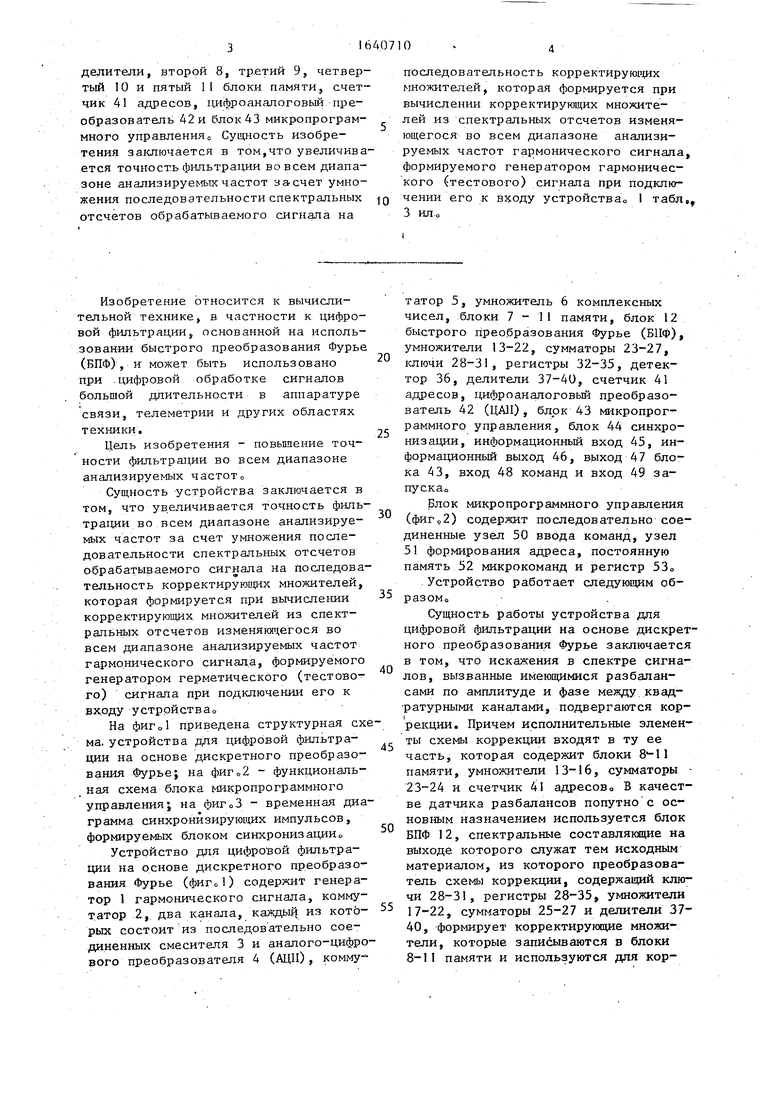

При поступлении на вход 49 устройства сигнала Пуск осуществляется запуск блока 44 синхронизации, который при поступлении команд на вход 48 устройства формирует на выходах сигналы ()о При поступлении на вход 48 устройства команды Начальная установка (см„таблицу) на выходе узла ввода команд 50 формируется сигнал обнуления, который подается на узел 51 формирования адреса и переводит его выход в нулевое состояние Таким образом на входе постоянной памяти 52 будет сформирован нулевой адрес

Нулевому адресу, как следует из таблицы, записанному в постоянную память 52, соответствует сигнал, который переписывается в регистр 53 и выводится на выход 47„ По этому сигналу осуществляется установка в ис- ходное состояние блока БПФ 12 и счетчика 41 адресов При этом на втором выходе регистра 53 сформирован сигнал, который подается на вход узла 51 формирования адреса и подготавли- вает его для приема команды от узла 50 ввода команде

Периодически основной режим работы устройства для цифровой фильтрации на основе ДПФ прерывается и на вход 48 устройства подается команда Тест (смотаблицу)о При поступлении этой команды на вход 48 осуществляется ее трансляция через узел 50 ввода команд и узел 51 формирования адреса на вход постоянной памяти 52„ В соответствии с таблицей микрокоманд, записанных в постоянную память 52, на ее выходе будут сформированы сигналы, которые переписываются в регистр 53 и выводятся на выход 47. Но сигналам, передаваемым по выходу 47, осуществляется отключение с помощью коммутатора 2 входов смесителей 3 от входа 45 устройства и подключение к выходу ге- нератора 1 гармонического (тестового) сигнала, а также управление коммутатором 5 и блоками 7-11 памяти, перевод блока БПФ 12 на осуществление вычислений по алгоритму БПФ, уп- равленне ключами 28-31, запись начального адреса и наращивание адресов в счетчике 41 адресов. Итак, генератор 1 гармонического тестового

16407106

сигнала осуществляет генерацию гар0

5

0 5 Q

c Q

0

монического сигнала известной частоты (Jon + ЬОи амплитуды,, Причем величина &G3 зависит от уровня напряжения, формируемого преобразователем 42 на управляющем входе генератора 10 При этом величина управляющего напряжения линейно изменяется в зависимости от значения двоичного кода, формируемого на информационном выходе счетчика 41 адресов0 Изменение двоичного кода на информационном выходе счетчика 41 адресов соответствует изменению частоты гармонического сигнала генератора 1„ После преобразования в смесителях 3 и преобразователях 4 тестовые сигналы, дискретизи- рованные по времени, квантованные по уровню и представленные в двоичном коде, подвергаются дальнейшей обра- ботке0

Функциональное назначение коммутатора 5, умножители комплексных чисел 6 и блока 7 памяти состоит в реализации режима умножения комплексной последовательности отсчетов входного сигнала на комплексную последовательность отсчетов весовой функции0 Такой режим используется для уменьшения уровня боковых лепестков в спектре входного сигналао Однако при единичных коэффициентах, поступающих с выхода первого блока 7 памяти, коммутатор 5, умножитель 6 комплексных чисел 6 и блок БПФ 12 реализует прямое БПФ комплексной последовательное ти отсчетов входного сигнала без уменьшения уровня боковых лепестков в вычислительном спектре0 Действительная и мнимая части спектра тестового сигнала поступают соответственно на ключи 28-29 и 30-31, причем ключи 28 и 30 пропускают на запись в регистры 32 и 34 спектральные отсчеты на частоте ДСО , а ключи 29 и 31 пропускают на запись в регистры 33 и 35 отсчеты на зеркальной частоте - UGJ . Из содержимого регистра 32-35 формируются соответственно корректирующие множители A,B,C,D, которые записываются соответственно в блоки 8-11 памяти в ячейки с адресами, которые вырабатываются счетчиком 41 адресов. Причем корректирующие множители A,B,C,D являются результатом следующих вычислений:

kn+ln kn+lm

kl+l. raninf. kn+lm kn+lm

D

ral+nl kn+lin

где k Re ZT.C (-ЛО);1 Re ZTiC(&Q);

m Im ZT.C (-&O);n Im гт.с(ыз)

- соответственно действительные и мнимые части спектральных отсчетов, соответствующие зеркальной частоте - UQ и частоте AQ сигнала генера- тора 1 о

Таким образом, в ячейках блоков 8-1J памяти записаны корректирующие множители, соответствующие одной частоте из всего диапазона анализируемых частот о Для определения корректирующих множителей для остальных дискретных значений частот из анализируемого диапазона3 необходимо провести многократные вычисления спектральных составляющих тестового сигнала в соответствии с описанным режимом работы устройства, с тем отличием, что вновь вычисленные корректирующие множители будут записаны в ячейки бло- ков 8-11 с адресами, которые вырабатываются счетчиком 41 адресов о При этом синхронно с изменением адреса ячеек блоков 8-11 памяти изменяется величина управляющего напряжения,фор- мируемого преобразователем 42 для изменения частоты гармонического сигнала, вырабатываемого генератором 10

Последний сигнал который формируется на выходе 47 под действием ко- манды Тест переводит узел 51 формирования адреса в состояние готовности для приема новой команды с входа 48„

В основном режиме работы устройства на вход 48 подается команда Кор- рекция (смотаблицу)о При поступлении этой команды на вход 48 осуществляется ее трансляция через узел ввода команд 50 и узел 51 формирования адреса на вход 52 постоянной памяти0 В со ответствии с таблицей микрокоманд,записанных в постоянную память 52, на .ее выходе сформированы сигналы, которые переписываются в регистр 53 и выводятся на выход 47о По сигналам пе- редаваемым по выходу 47, осуществляется отключение с помощью коммутатора 2 выхода генератора 1 от входов смесителей 3 и подключение к ним входа 45 устройства,, а также управление комму- татором 5 и блоками 7-1} памяти, перевод блока БПФ 12 на осуществление вычислений по алгоритму БПФ, запись начального адреса и наращивание адресов

в счетчике 41 адресов Входные сигналы, прошедшие обработку в смесителях 3 и преобразователях 4, подвергаются обработке в коммутаторе 5 и умножителе 6 комплексных чисел и подаются на блок БПФ 12 для вычисления их спектров. Амплитудные значения спектральных отсчетов входных сигналов подаются на исполнительные элементы схемы коррекции Одновременно с ними на исполнительные элементы схемы коррекции из ячеек блоков 8-11 памяти с адресами, формируемыми счетчиком 41 адресов, считываются корректирующие множители А,В,С,Do После преобразования в исполнительных элементах схемы коррекции на выходах сумматоров 23 и 24 спектральные составляющие входного сигнала имеют вид

Re ZKOp(n)A(n)- Re Z (n)+B (n) Im Z(n); Im ZKQp(n)C(n).Re Z(n)/D(n) Im Z(n),

где Re ZKOp(n) и Im Z кор(п.) - соответственно действительная и мнимая части дискретных отсчетов скоррек- тированного спектра входного сигнала;

Re Z(n) и Im Z(n) - соответственно действительная и мнимая части дискретных отсчетов искаженного спектра входного сигнала;

n - номер дискретного отсчета

спектра I

Скорректированные комплексные отсчеты спектра сигнала поступают на входы детектора 36, осуществляющего вычисление модуля комплексных отсчетов спектра и выдаются на выход 46 устройства для дальнейшей обработки0

Результатом коррекции является отсутствие искажений в спектре входных сигналов, соответствующих амплитудно-фазовому разбалансам между квадратурными каналамио Причем точность проведенной коррекции и, таким образом, фильтрации входных сигналов является одинаковой во всем диапазоне анализируемых частот и не зависит от частоты входных сигналов, так как при осуществлении коррекции каждому дискретному отсчету спектра входного сигнала соответствует корректирующий множитель, вычисленный из дискретных отсчетов спектра тестового сигнала при изменении его частоты во всем диапазоне анализируемых частот,, Последний сигнал, который формируется на выходе 47 под действием команды Коррекция, переводит узел 51 формирования адреса в состояние готовности для приема новой команды с входа 48 ,

Использование изобретения позволяет увеличить точность цифровой фильт- рации во всем диапазоне анализируемых частот путем использования при коррекции дискретных спектральных отсчетов входного сигнала набора дискрет- ных корректирующих множителей, каждый из которых ставится в соответствие дискретному отсчету спектра0

Формула изобретения

Устройство для цифровой фильтрации на основе дискретного преобразова ния Фурье, содержащее генератор гармо нического сигнала, два коммутатора, блок синхронизации, два смесителя, два аналого-цифровых преобразователя, умножитель комплексных чисел, блок памяти, блок быстрого преобразования Фурье, четыре умножителя, пять сумматоров, четыре ключа, четыре регистра и детектор, причем выход генератора гармонического сигнала подключен к первому информационному входу первого коммутатора, второй информационный вход которого является информационным входом устройства, первые входы смесителей подключены к выходу первого коммутатора, выходы второго коммутатора соединены с входами операндов умножителя комплексных чисел, входы задания коэффициентов которого подключены к выходам первого блока памяти, выходы умножителя комплексных чисел соединены с информационными входами блока быстрого преобразования Фурье, выходы первого и второго смесителей соединены с информационными входами соответственно первого и второго аналого-цифровых преобразователей, выходы первого и второго умножителей подключены соответ7 ственно к первым входам первого и второго сумматоров, выходы третьего и четвертого умножителей подключены соответственно к вторым входам первого и второго сумматоров, первый выход блока быстрого преобразования Фурье подключен к информационным входам первого и второго ключей, второй выход блока быстрого преобразования Фурье подключен к информационным входам третьего и четвертого ключей, выходы с первого по четвертый ключей

- Q

5

0

5

0

5

0

5

0

5

соединены соответственно с информационными входами с первого по четвертый регистров, выходы первого и второго регистров соединены соответственно с первым и вторым входами третьего сумматора, а выходы третьего и четвертого регистров соединены соответственно с первым и вторым входами четвертого сумматора, вторые входы смесителей подключены соответственно к первому и второму входам опорных частот устройства, выходом которого является выход детектора, отличающее с я тем, что, с целью повышения точности фильтрации во всем диапазоне анализируемых частот, в него введены с пятого по десятый умножители, первый, второй, третий, и четвертый делители, второй, третий, четвертый и пятый блоки памяти, счетчик адресов, цифрозналоговый преобразователь, блок микропрограммного управления, причем выходы первого и второго аналого-цифровых преобразователей подключены соответственно к первому и второму информационным входам второго коммутатора, первый выход блока быстрого преобразования Фурье подключен к первым входам первого и второго умножителей, второй выход блока быстрого преобразования Фурье подключен к первым входам третьего и четвертого умножителей, выходы первого и второго сумматоров соединены соответственно с первым и вторым входами детектора, первые входы пятого, седьмого и восьмого умножителей подключены к выходу первого регистра, первые входы шестого, девятого и десятого умножителей подключены к выходу третьего регистра, вторые входы пятого и шестого умножителей соединены соответственно с выходами четвертого и второго регистров, выходы пятого и шестого умножителей подключены соответственно к первому и второму входам пятого сумматора, выход которого соединен с первыми входами с первого по четвертый делителей, вторые входы седьмого и девятого умножителей подключены к выходу третьего Сумматора, вторые входы восьмого и десятого умножителей подключены к выхо-. ду четвертого -сумматора, выходы седьмого, восьмого, девятого и десятого умножителей соединены соответственно с втор ыми входами первого, вто- , рого, третьего и четвертого делителей, выходы которых соединены с информационными входами соответственно второго, третьего, четвертого и пятого блоков памяти, адресные входы которых соединены с входом цифроана- логового преобразователя и подключены к информационному выходу счетчика адресов, выход цифроаналогового преобразователя соединен с управляюпщм входом генератора гармонического сигнала, выходы второгоf третьего, четвертого и пятого блоков памяти содинены с вторыми входами соответственно третьего, четвертого, первого и второго умножителей, управляющие входы первого коммутатора, второго коммутатора, с первого по пятый блоков памяти, блока быстрого преобразования Фурье, блока синхронизации, с первого по четвертый ключей, с первого по четвертый регистров, счетчи

0

ка адресов соединены с соответствующими выходами блока микропрограммного управления, вход команды которого является входом команды устройства, входы синхронизации первого и второго аналого-цифровых преобразователей подключены к первому выходу блока синхронизации, входы синхронизации первого блока памяти и блока быстрого преобразования Фурье подключены к второму выходу блока синхронизации, выходы синхронизации второго, третьего, четвертого и пятого блоков памяти подключены к третьему выходу блока синхронизации, а вход синхронизации блока микропрограммного управления подключен к четвертому выходу блока синхронизации, вход запуска которого является входом запуска устройства,,

CLM I

CLK3

Фиг. г

ЛГ

| Высоцкий Ф0Б„ и дро Цифровые фильтры и устройства обработки сигналов на интегральных микросхемах,, М0: Радио и связь, 1984, с022, Авторское свидетельство СССР № 840922, кло G 06 F 15/332, 19800 |

Авторы

Даты

1991-04-07—Публикация

1988-06-20—Подача