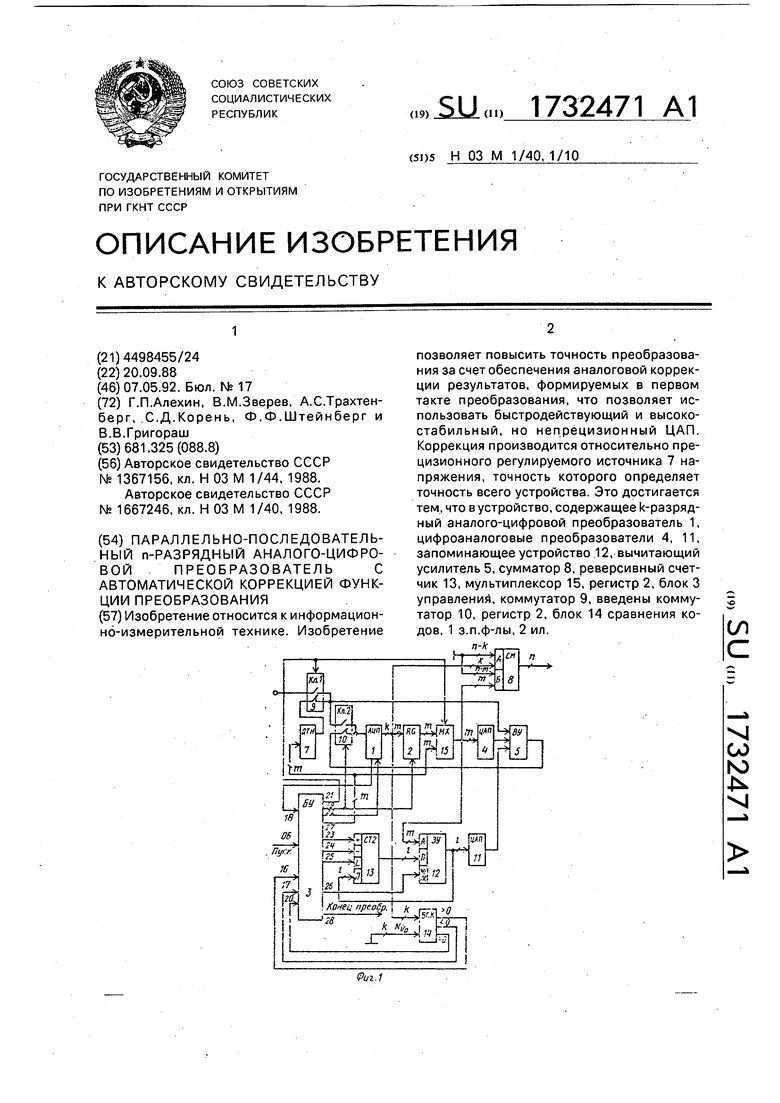

Изобретение относится к информационно-измерительной технике.

Цель изобретения - повышение быстродействия.

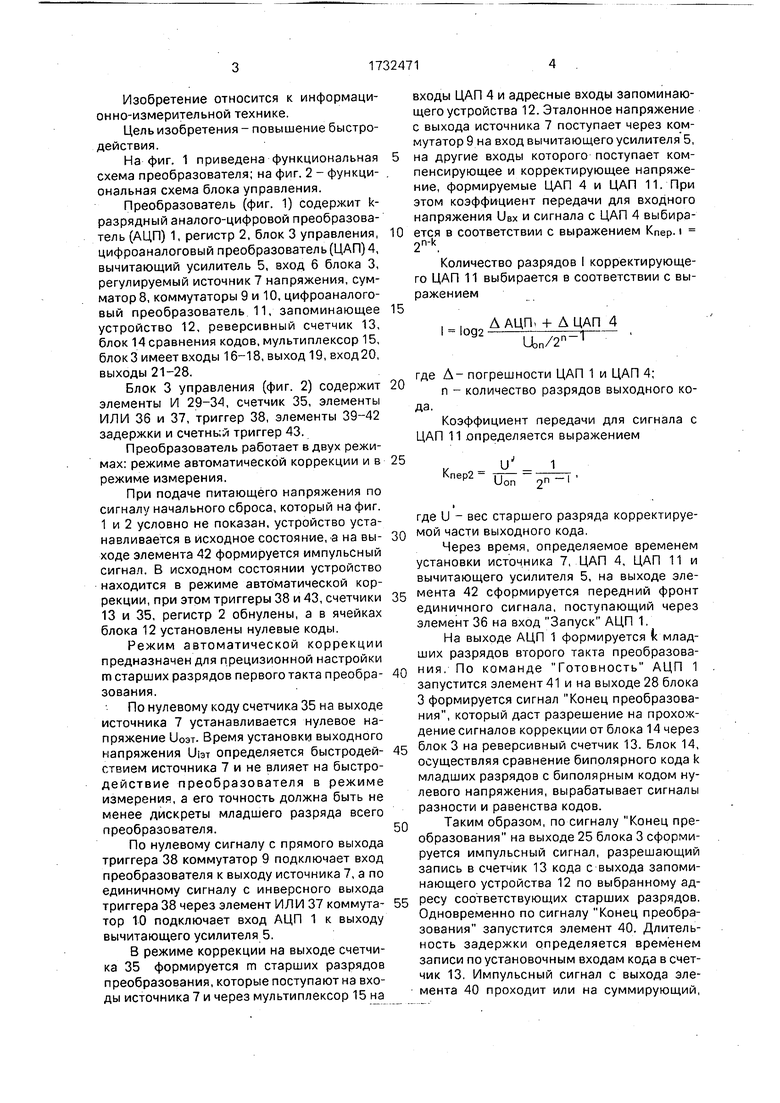

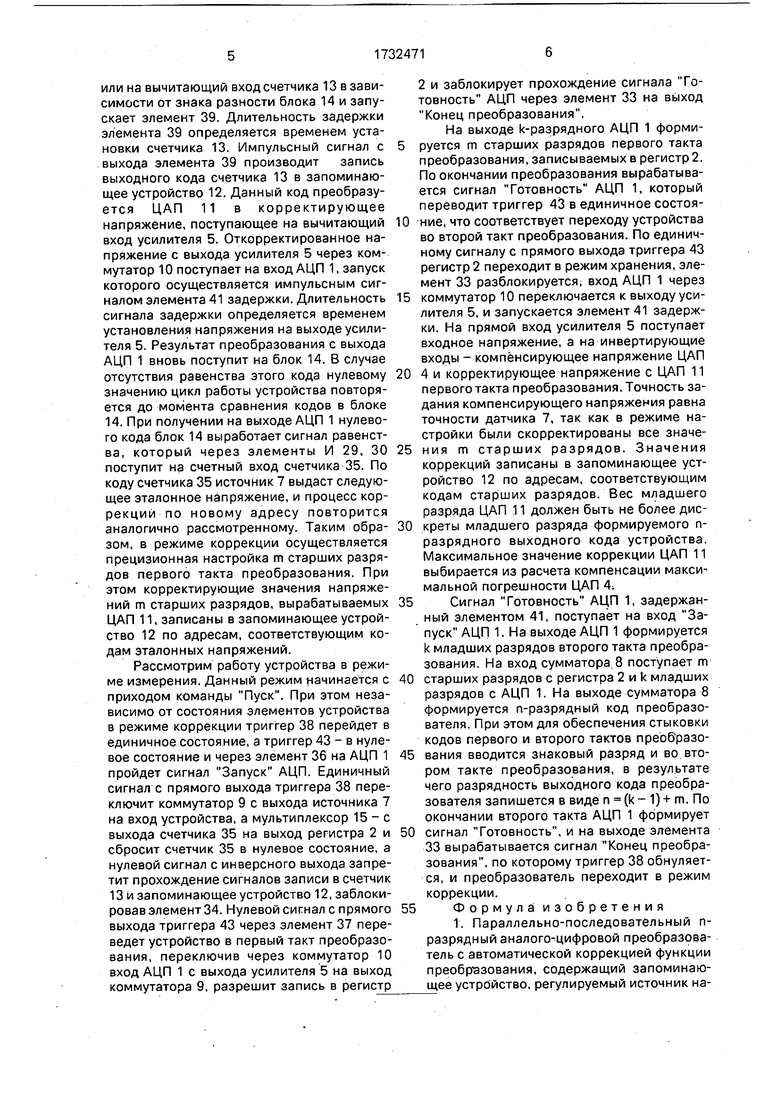

На фиг. 1 приведена функциональная схема преобразователя; на фиг. 2 - функциональная схема блока управления.

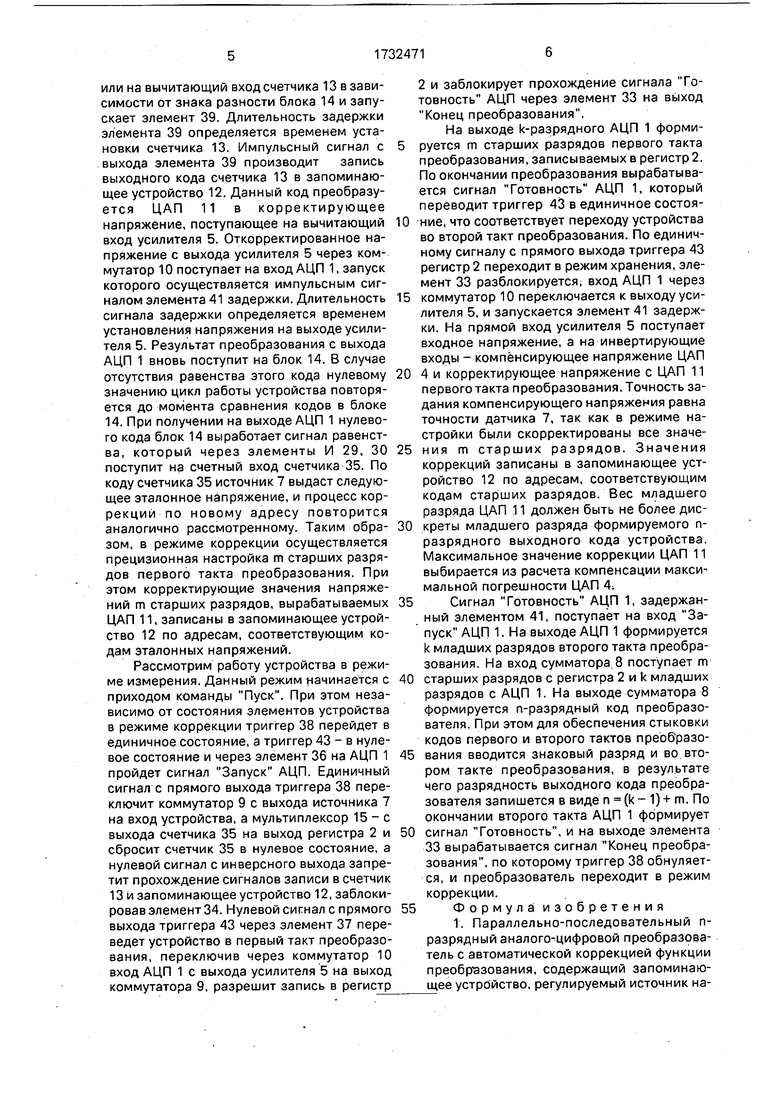

Преобразователь (фиг. 1) содержит к- разрядный аналого-цифровой преобразователь (АЦП) 1, регистр 2, блок 3 управления, цифроаналоговый преобразователь (ЦАП) 4, вычитающий усилитель 5, вход б блока 3, регулируемый источник 7 напряжения, сумматор 8, коммутаторы 9 и 10, цифроаналоговый преобразователь 11, запоминающее устройство 12, реверсивный счетчик 13, блок 14сравнения кодов, мультиплексор 15, блокЗ имеет входы 16-18, выход 19, вход 20, выходы 21-28.

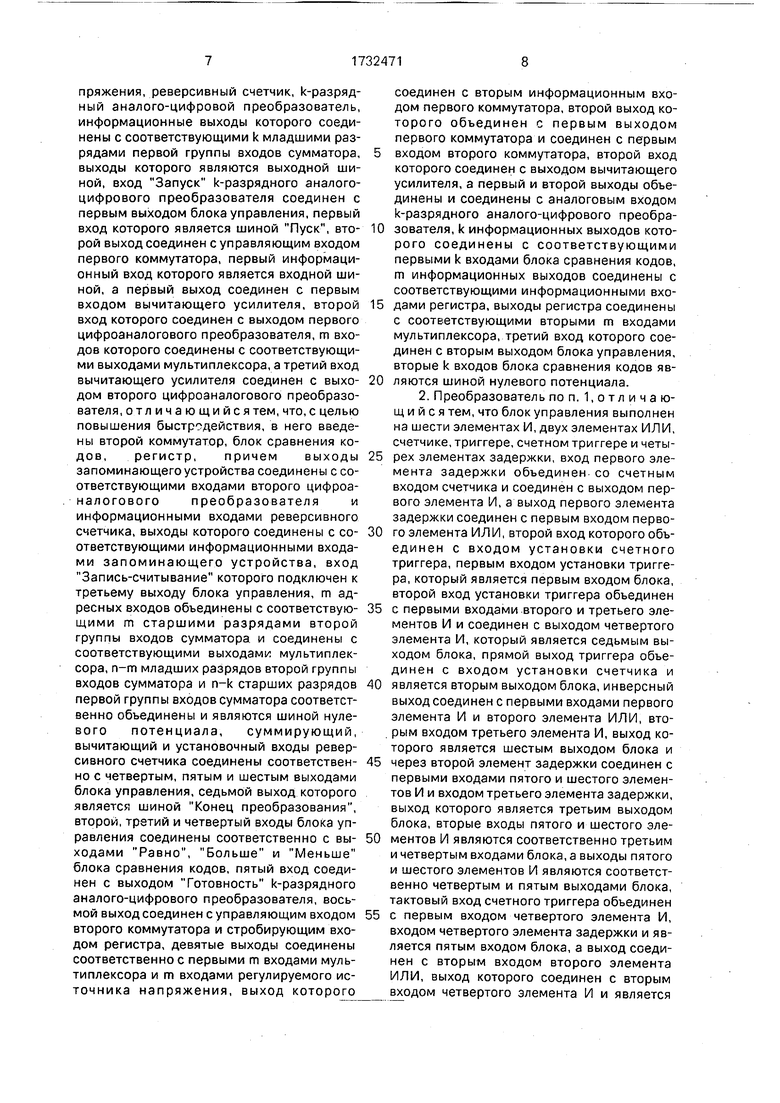

Блок 3 управления (фиг. 2) содержит элементы И 29-34, счетчик 35, элементы ИЛИ 36 и 37, триггер 38, элементы 39-42 задержки и счетный триггер 43.

Преобразователь работает в двух режимах: режиме автоматической коррекции и в режиме измерения.

При подаче питающего напряжения по сигналу начального сброса, который на фиг. 1 и 2 условно не показан, устройство устанавливается в исходное состояние, а на вы- ходе элемента 42 формируется импульсный сигнал. В исходном состоянии устройство находится в режиме автоматической коррекции, при этом триггеры 38 и 43, счетчики 13 и 35, регистр 2 обнулены, а в ячейках блока 12 установлены нулевые коды.

Режим автоматической коррекции предназначен для прецизионной настройки m старших разрядов первого такта преобра- зования.

По нулевому коду счетчика 35 на выходе источника 7 устанавливается нулевое напряжение UOST. Время установки выходного напряжения Uiar определяется быстродей- ствием источника 7 и не влияет на быстродействие преобразователя в режиме измерения, а его точность должна быть не менее дискреты младшего разряда всего преобразователя.

По нулевому сигналу с прямого выхода триггера 38 коммутатор 9 подключает вход преобразователя к выходу источника 7, а по единичному сигналу с инверсного выхода триггера 38 через элемент ИЛИ 37 коммута- тор 10 подключает вход АЦП 1 к выходу вычитающего усилителя 5.

В режиме коррекции на выходе счетчика 35 формируется m старших разрядов преобразования, которые поступают на входы источника 7 и через мультиплексор 15 на

входы ЦАП 4 и адресные входы запоминающего устройства 12. Эталонное напряжение с выхода источника 7 поступает через коммутатор 9 на вход вычитающего усилителя 5, на другие входы которого поступает компенсирующее и корректирующее напряжение, формируемые ЦАП 4 и ЦАП 11. При этом коэффициент передачи для входного напряжения UBx и сигнала с ЦАП 4 выбирается в соответствии с выражением Кпер. 2n-k

Количество разрядов I корректирующего ЦАП 11 выбирается в соответствии с выражением

I IOQ2

А АЦП- + Д Un/2n

где А- погрешности ЦАП 1 и ЦАП 4;

п - количество разрядов выходного кода.

Коэффициент передачи для сигнала с ЦАП 11 определяется выражением

гт

и

1

on

ш -I

где U - вес старшего разряда корректируемой части выходного кода.

Через время, определяемое временем установки источника 7, ЦАП 4, ЦАП 11 и вычитающего усилителя 5, на выходе элемента 42 сформируется передний фронт единичного сигнала, поступающий через элемент 36 на вход Запуск АЦП 1.

На выходе АЦП 1 формируется k младших разрядов второго такта преобразования. По команде Готовность АЦП 1 запустится элемент 41 и на выходе 28 блока 3 формируется сигнал Конец преобразования, который даст разрешение на прохождение сигналов коррекции от блока 14 через блок 3 на реверсивный счетчик 13. Блок 14, осуществляя сравнение биполярного кода k младших разрядов с биполярным кодом нулевого напряжения, вырабатывает сигналы разности и равенства кодов.

Таким образом, по сигналу Конец преобразования на выходе 25 блока 3 сформируется импульсный сигнал, разрешающий запись в счетчик 13 кода с выхода запоминающего устройства 12 по выбранному адресу соответствующих старших разрядов. Одновременно по сигналу Конец преобразования запустится элемент 40. Длительность задержки определяется временем записи по установочным входам кода в счетчик 13. Импульсный сигнал с выхода элемента 40 проходит или на суммирующий,

или на вычитающий вход счетчика 13 в зависимости от знака разности блока 14 и запускает элемент 39. Длительность задержки элемента 39 определяется временем установки счетчика 13. Импульсный сигнал с выхода элемента 39 производит запись выходного кода счетчика 13 в запоминающее устройство 12. Данный код преобразуется ЦАП 11 в корректирующее напряжение, поступающее на вычитающий вход усилителя 5. Откорректированное напряжение с выхода усилителя 5 через коммутатор 10 поступает на вход АЦП 1, запуск которого осуществляется импульсным сигналом элемента 41 задержки. Длительность сигнала задержки определяется временем установления напряжения на выходе усилителя 5. Результат преобразования с выхода АЦП 1 вновь поступит на блок 14. В случае отсутствия равенства этого кода нулевому значению цикл работы устройства повторяется до момента сравнения кодов в блоке 14. При получении на выходе АЦП 1 нулевого кода блок 14 выработает сигнал равенства, который через элементы И 29, 30 поступит на счетный вход счетчика 35. По коду счетчика 35 источник 7 выдаст следующее эталонное напряжение, и процесс коррекции по новому адресу повторится аналогично рассмотренному. Таким образом, в режиме коррекции осуществляется прецизионная настройка m старших разрядов первого такта преобразования. При этом корректирующие значения напряжений m старших разрядов, вырабатываемых ЦАП 11, записаны в запоминающее устройство 12 по адресам, соответствующим кодам эталонных напряжений.

Рассмотрим работу устройства в режиме измерения. Данный режим начинается с приходом команды Пуск. При этом независимо от состояния элементов устройства в режиме коррекции триггер 38 перейдет в единичное состояние, а триггер 43 - в нулевое состояние и через элемент 36 на АЦП 1 пройдет сигнал Запуск АЦП. Единичный сигнал с прямого выхода триггера 38 переключит коммутатор 9 с выхода источника 7 на вход устройства, а мультиплексор 15 - с выхода счетчика 35 на выход регистра 2 и сбросит счетчик 35 в нулевое состояние, а нулевой сигнал с инверсного выхода запретит прохождение сигналов записи в счетчик 13 и запоминающее устройство 12, заблокировав элемент 34. Нулевой сигнал с прямого выхода триггера 43 через элемент 37 переведет устройство в первый такт преобразования, переключив через коммутатор 10 вход АЦП 1 с выхода усилителя 5 на выход коммутатора 9, разрешит запись в регистр

2 и заблокирует прохождение сигнала Готовность АЦП через элемент 33 на выход Конец преобразования.

На выходе k-разрядного АЦП 1 формируется m старших разрядов первого такта преобразования, записываемых в регистр 2. По окончании преобразования вырабатывается сигнал Готовность АЦП 1, который переводит триггер 43 в единичное состоя0 ние, что соответствует переходу устройства во второй такт преобразования. По единичному сигналу с прямого выхода триггера 43 регистр 2 переходит в режим хранения, элемент 33 разблокируется, вход АЦП 1 через

5 коммутатор 10 переключается к выходу усилителя 5, и запускается элемент 41 задержки. На прямой вход усилителя 5 поступает входное напряжение, а на инвертирующие входы - компенсирующее напряжение ЦАП

0 4 и корректирующее напряжение с ЦАП 11 первого такта преобразования.Точность задания компенсирующего напряжения равна точности датчика 7, так как в режиме настройки были скорректированы все значе5 ния m старших разрядов. Значения коррекций записаны в запоминающее устройство 12 по адресам, соответствующим кодам старших разрядов. Вес младшего разряда ЦАП 11 должен быть не более дис0 креты младшего разряда формируемого п- разрядного выходного кода устройства. Максимальное значение коррекции ЦАП 11 выбирается из расчета компенсации максимальной погрешности ЦАП 4.

5 Сигнал Готовность АЦП 1, задержанный элементом 41, поступает на вход Запуск АЦП 1. На выходе АЦП 1 формируется k младших разрядов второго такта преобразования. На вход сумматора 8 поступает m

0 старших разрядов с регистра 2 и k младших разрядов с АЦП 1. На выходе сумматора 8 формируется n-разрядный код преобразователя. При этом для обеспечения стыковки кодов первого и второго тактов преобразо5 вания вводится знаковый разряд и во втором такте преобразования, в результате чего разрядность выходного кода преобразователя запишется в виде n (k - 1) + т. По окончании второго такта АЦП 1 формирует

0 сигнал Готовность, и на выходе элемента 33 вырабатывается сигнал Конец преобразования, по которому триггер 38 обнуляется, и преобразователь переходит в режим коррекции.

5 Формула изобретения

1. Параллельно-последовательный п- разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования, содержащий запоминающее устройство, регулируемый источник напряжения, реверсивный счетчик, k-разряд- ный аналого-цифровой преобразователь, информационные выходы которого соединены с соответствующими к младшими разрядами первой группы входов сумматора, выходы которого являются выходной шиной, вход Запуск k-разрядного аналого- цифрового преобразователя соединен с первым выходом блока управления, первый вход которого является шиной Пуск, второй выход соединен с управляющим входом первого коммутатора, первый информационный вход которого является входной шиной, а первый выход соединен с первым входом вычитающего усилителя, второй вход которого соединен с выходом первого цифроаналогового преобразователя, m входов которого соединены с соответствующими выходами мультиплексора, а третий вход вычитающего усилителя соединен с выходом второго цифроаналогового преобразователя, отличающи йсятем, что, с целью повышения быстродействия, в него введены второй коммутатор, блок сравнения кодов, регистр, причем выходы запоминающего устройства соединены с соответствующими входами второго цифроаналогового преобразователя и информационными входами реверсивного счетчика, выходы которого соединены с соответствующими информационными входами запоминающего устройства, вход Запись-считывание которого подключен к третьему выходу блока управления, m адресных входов объединены с соответствующими m старшими разрядами второй группы входов сумматора и соединены с соответствующими выходами мультиплексора, n-m младших разрядов второй группы входов сумматора и n-k старших разрядов первой группы входов сумматора соответственно объединены и являются шиной нулевого потенциала, суммирующий, вычитающий и установочный входы реверсивного счетчика соединены соответственно с четвертым, пятым и шестым выходами блока управления, седьмой выход которого является шиной Конец преобразования, второй, третий и четвертый входы блока управления соединены соответственно с выходами Равно, Больше и Меньше блока сравнения кодов, пятый вход соединен с выходом Готовность k-разрядного аналого-цифрового преобразователя, восьмой выход соединен с управляющим входом второго коммутатора и стробирующим входом регистра, девятые выходы соединены соответственно с первыми m входами мультиплексора и m входами регулируемого источника напряжения, выход которого

соединен с вторым информационным входом первого коммутатора, второй выход которого объединен с первым выходом первого коммутатора и соединен с первым

входом второго коммутатора, второй вход которого соединен с выходом вычитающего усилителя, а первый и второй выходы объединены и соединены с аналоговым входом k-разрядного аналого-цифрового преобра0 зователя, k информационных выходов которого соединены с соответствующими первыми k входами блока сравнения кодов, m информационных выходов соединены с соответствующими информационными вхо5 дами регистра, выходы регистра соединены с соответствующими вторыми m входами мультиплексора, третий вход которого соединен с вторым выходом блока управления, вторые k входов блока сравнения кодов яв0 ляются шиной нулевого потенциала.

2. Преобразователь по п. 1, о т л и ч а ю- щ и и с я тем, что блок управления выполнен на шести элементах И, двух элементах ИЛИ, счетчике,триггере, счетном триггере и четы5 рех элементах задержки, вход первого элемента задержки объединен со счетным входом счетчика и соединен с выходом первого элемента И, а выход первого элемента задержки соединен с первым входом перво0 го элемента ИЛИ, второй вход которого объединен с входом установки счетного триггера, первым входом установки триггера, который является первым входом блока, второй вход установки триггера объединен

5 с первыми входами второго и третьего элементов И и соединен с выходом четвертого элемента И, который является седьмым выходом блока, прямой выход триггера объединен с входом установки счетчика и

0 является вторым выходом блока, инверсный выход соединен с первыми входами первого элемента И и второго элемента ИЛИ, вторым входом третьего элемента И, выход которого является шестым выходом блока и

5 через второй элемент задержки соединен с первыми входами пятого и шестого элементов И и входом третьего элемента задержки, выход которого является третьим выходом блока, вторые входы пятого и шестого эле0 ментов И являются соответственно третьим и четвертым входами блока, а выходы пятого и шестого элементов И являются соответственно четвертым и пятым выходами блока, тактовый вход счетного триггера объединен

5 с первым входом четвертого элемента И, входом четвертого элемента задержки и является пятым входом блока, а выход соединен с вторым входом второго элемента ИЛИ, выход которого соединен с вторым входом четвертого элемента И и является

восьмым выходом блока, выход четвертогосчетчика являются девятыми выходами блоэлемента задержки соединен с третьим вхо-ка, второй вход второго элемента И является

дом первого элемента ИЛИ, выход котороговторым входом блока, а выход соединен с

является первым выходом блока, выходывторым входом первого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1980 |

|

SU884127A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Аналого-цифровой преобразователь знакопеременных сигналов | 1987 |

|

SU1483641A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С КОРРЕКЦИЕЙ СЛУЧАЙНОЙ ПОГРЕШНОСТИ | 1991 |

|

RU2024193C1 |

| Система многоканального приема и преобразования в код аналоговых сигналов | 1978 |

|

SU758511A1 |

| Устройство аналого-цифрового преобразования | 1987 |

|

SU1559405A2 |

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

| Цифровой вольтметр среднеквадратического значения переменного напряжения | 1988 |

|

SU1652933A1 |

| Аналого-цифровое устройство | 1981 |

|

SU1018239A1 |

Изобретение относится к информационно-измерительной технике. Изобретение позволяет повысить точность преобразования за счет обеспечения аналоговой коррекции результатов, формируемых в первом такте преобразования, что позволяет использовать быстродействующий и высокостабильный, но непрецизионный ЦАП. Коррекция производится относительно прецизионного регулируемого источника 7 напряжения, точность которого определяет точность всего устройства. Это достигается тем, что в устройство, содержащее k-разряд- ный аналого-цифровой преобразователь 1, цифроаналоговые преобразователи 4, 11, запоминающее устройство 12, вычитающий усилитель 5, сумматор 8, реверсивный счетчик 13, мультиплексор 15, регистр 2, блок 3 управления, коммутатор 9, введены коммутатор 10, регистр 2, блок 14 сравнения кодов, 1 з.п.ф-лы, 2 ил. п-к fiCH n СП с VJ со го VI

ви

1

Режим

| Параллельно-последовательный аналого-цифровой преобразователь | 1986 |

|

SU1367156A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1667246A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-05-07—Публикация

1988-09-20—Подача