Предлагаемое изобретение относится к области радиотехники и может найти применение в широкополосных системах связи с шумоподобными сигналами.

Известны устройства синхронизации шумоподобного сигнала, описанные в книгах "Шумоподобные сигналы в системах передачи информации" /Под ред. Пестрякова В.Б., М. Сов.радио, 1973 г., Тузов Г.И. "Статистическая теория приема сложных сигналов", М., Сов.радио, 1977 г., а также в авторских свидетельствах СССР №№126580, 162245.

Недостатками всех этих устройств являются низкая помехозащищенность синхронизации в условиях многолучевости входного сигнала и, кроме того, все эти устройства не могут работать при больших расстройках частот опорных генераторов передающего и приемного устройств.

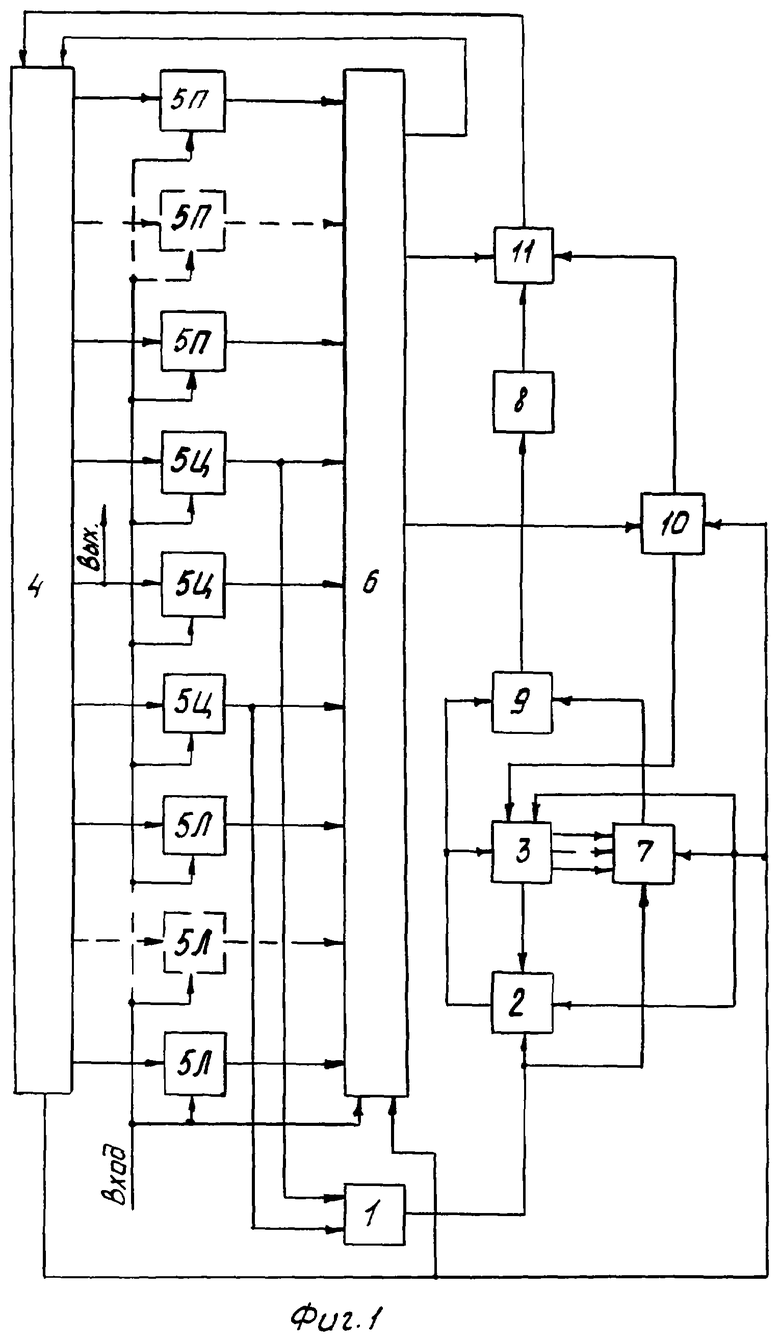

Наиболее близким по технической сущности к предлагаемому является устройство, где блок-схема этого устройства представлена на фиг.1, где обозначено:

1 - вычитающее устройство,

2 - пропорциональное звено с переключаемым коэффициентом передачи,

3 - устройство управления режимом работы точной ФАП,

4 - управляемый генератор ПСП,

5л, 5ц, 5п - корреляторы левой, центральной и правой групп,

6 - блок принятия решения,

7 - интегрирующее устройство с переключаемой постоянной времени интегрирования,

8 - управляемый генератор тактовых импульсов,

9 - сумматор,

10 - устройство управления работой точной и грубой систем ФАП,

11 - управляемый делитель грубой дискретной системы ФАП.

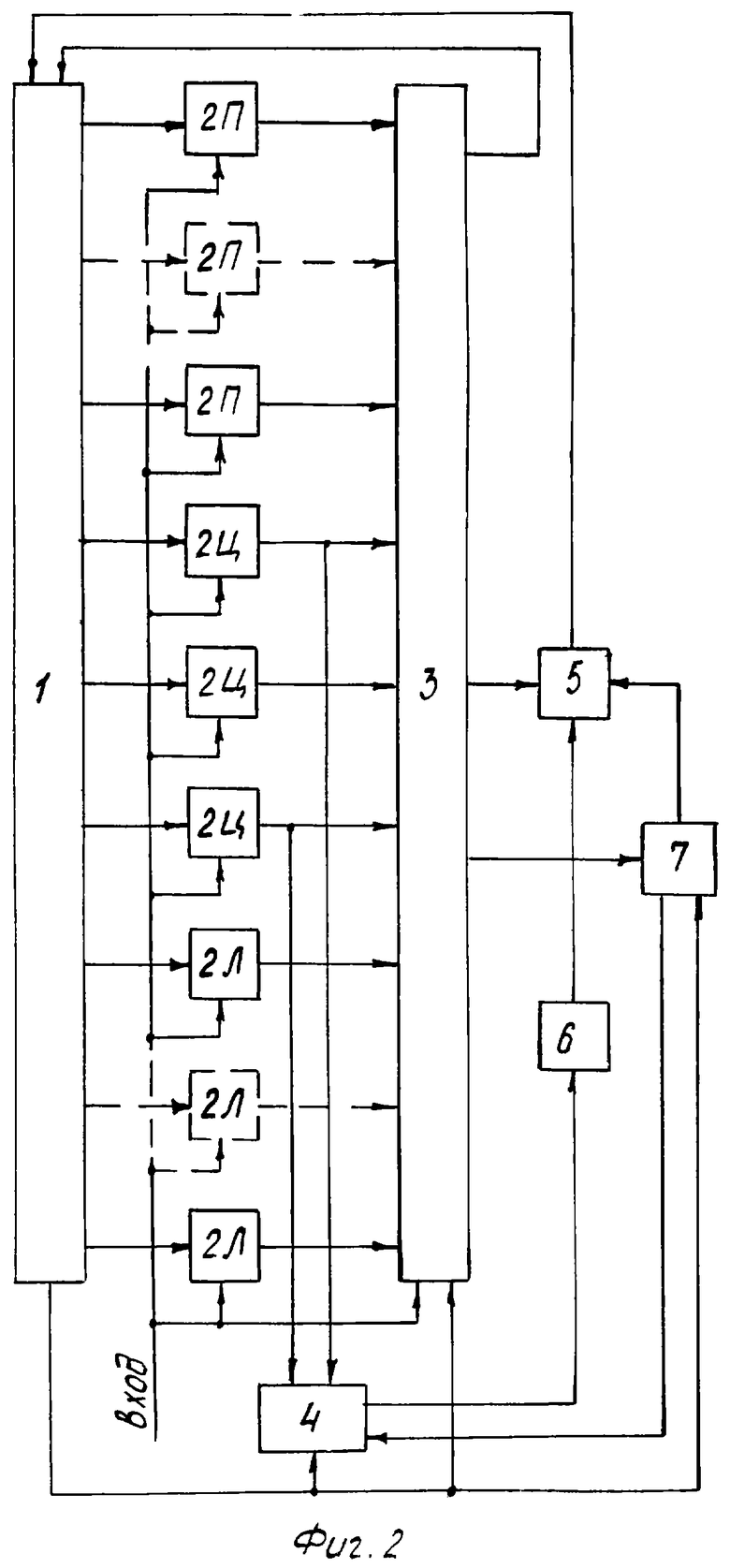

Для получения большей наглядности о работе устройства-прототипа в целом укрупним блок-схему прототипа, объединив ряд блоков воедино, с учетом выполняемых ими функций. При этом блоки 1, 2, 3, 7, 9, выполняющие функцию точной автоподстройки фазы опорных ПСП, объединены в блок 4 - устройство точной системы фазовой автоподстройки (ФАП).

Укрупненная блок-схема устройства-прототипа приведена на фиг.2, где обозначено:

1 - управляемый генератор ПСП,

2л, 2ц, 2п - корреляторы левой, центральной и правой групп,

3 - блок принятия решения,

4 - устройство точной системы ФАП,

5 - управляемый делитель грубой дискретной системы ФАП,

6 - управляемый генератор тактовых импульсов,

7 - устройство управления работой точной и грубой систем ФАП.

Выходы управляемого ГПСП 1 соединены со входами корреляторов 2л, 2ц, 2п, вторые входы которых объединены вместе и соединены с первым входом блока принятия решения 3, они же являются входом устройства. Выходы корреляторов 2л, 2ц, 2п соединены с соответствующими входами блока принятия решения 3, а выходы левого и правого корреляторов центральной группы соединены с первым и вторым входами устройства точной системы ФАП 4. Выход синхроимпульса управляемого ГПСП 1 соединен со входами блоков 3, 4, 7. Выход устройства точной системы ФАП 4 через управляемый генератор тактовых импульсов 6 соединен с первым входом управляемого делителя грубой дискретной системы ФАП 5, выход которого соединен со входом ГПСП 1. Первый выход блока принятия решения 3 соединен со входом устройства управления работой точной и грубой систем ФАП 7, второй - со входом блока 5, третий - со входом ГПСП 1. Первый выход блока 7 соединен с одним из входов блока 4, второй - с соответствующим входом блока 5.

Работает устройство следующим образом.

Управляемый генератор ПСП 1 формирует псевдослучайные последовательности, поступающие на входы корреляторов 2л, 2ц, 2п в качестве опорных сигналов. На объединенные входы корреляторов 2л, 2ц, 2п подан входной сигнал и происходит вычисление функции взаимной корреляции входного сигнала с опорным ПСП. Результаты вычисления, получаемые от каждого коррелятора, в блоке принятия решения 3 сравниваются с установленным порогом. Если сигнал не обнаружен ни в одном корреляторе 2л, 2ц, 2п, то от схемы принятия решения 3 поступает команда, по которой опорные ПСП сдвигаются на (n-1)·τ, где n - общее число корреляторов, τ - длительность одного элемента ПСП, и производится повторный поиск. При обнаружении сигнала в левой 2л или правой 2п группах корреляторов блок принятия решения 3 подает команду на делитель грубой дискретной системы ФАП 5, который производит подстройку фазы опорных ПСП, сдвигая их на τ в момент действия строб-импульса. Сдвиги опорных ПСП будут происходить до момента обнаружения сигнала в центральной группе корреляторов. Когда сигнал в центральной группе корреляторов обнаружен, блок принятия решения 3 формирует команду, по которой устройство управления 7 запрещает грубую дискретную подстройку и разрешает точную.

Основным недостатком этого устройства является низкая помехозащищенность синхронизации в условиях многолучевости входного сигнала. Действительно, то обстоятельство, что в устройстве-прототипе не происходит вычисления и анализа всей взаимокорреляционной функции входного сигнала и опорной ПСП приводит к появлению вероятности синхронизации с более слабым сигналом, что понижает помехозащищенность каналов слежения и выделения информации.

Целью предлагаемого изобретения является повышение помехозащищенности устройства поиска широкополосных сигналов в условиях многолучевости.

Поставленная цель достигается за счет введения оперативного запоминающего устройства, адресного счетчика, триггеров, коммутаторов, инвертора и их функциональных связей.

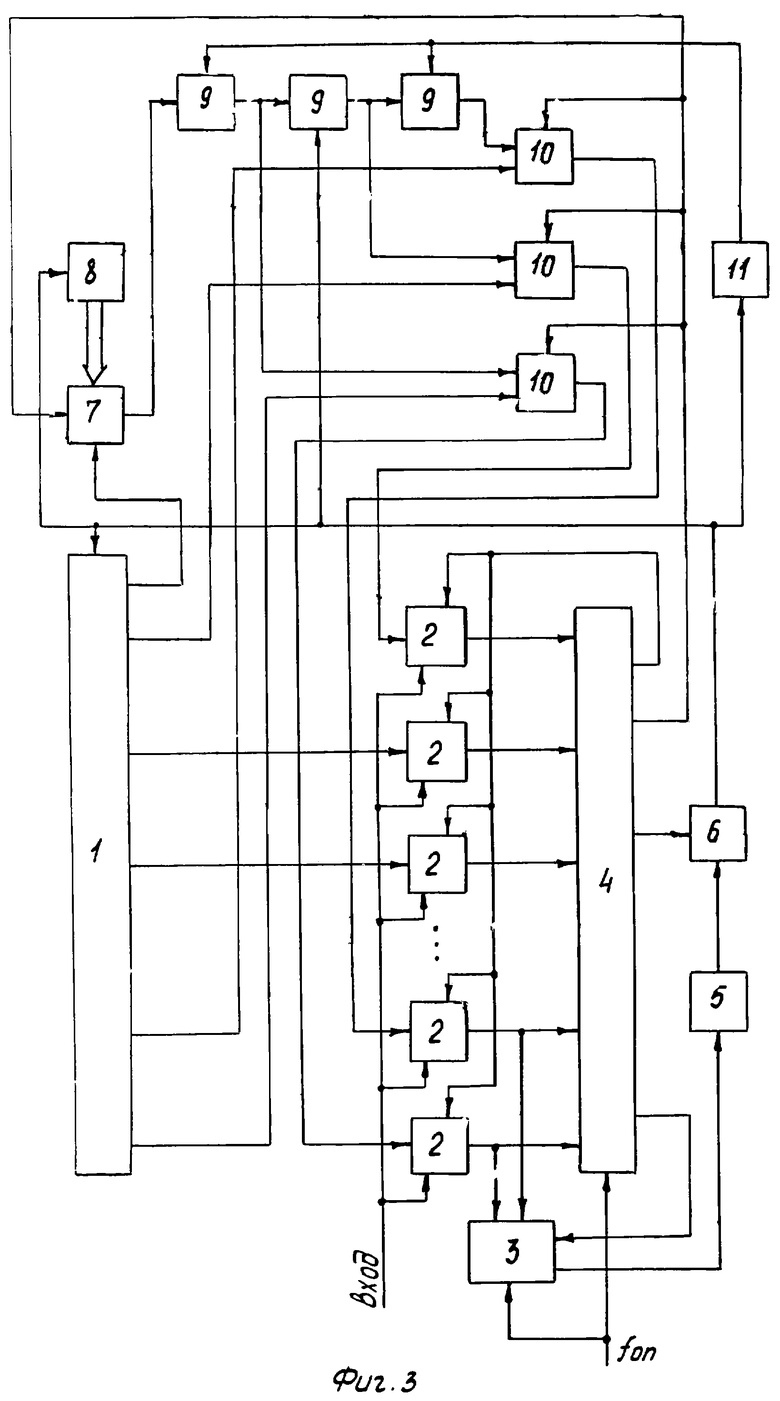

Блок-схема предлагаемого устройства представлена на фиг.3, где обозначено:

1 - управляемый генератор ПСП,

2 - коррелятор,

3 - блок точной системы ФАП,

4 - блок принятия решения,

5 - управляемый генератор тактовых импульсов,

6 - управляемый делитель грубой дискретной ФАП,

7 - оперативное запоминающее устройство (ОЗУ),

8 - адресный счетчик,

9 - триггер,

10 - коммутатор,

11 - инвертор.

Входы n корреляторов 2 объединены и являются входом устройства, а выходы соединены с соответствующими входами блока принятия решения 4, два из которых соединены со входами блока точной системы ФАП 3, выход которого через управляемый генератор тактовых импульсов 5 и управляемый делитель грубой дискретной системы ФАП 6, вход которого соединен с первым выходом блока принятия решения 4, присоединен к тактовым входам генератора ПСП 1 и второго триггера 9, ко входам инвертора 11, выход которого соединен с тактовыми входами первого и третьего триггеров 9 и адресного счетчика 8. Выход счетчика 8 соединен с первым входом ОЗУ 7, второй вход - с первым выходом ГПСП 1, с третьего по (к-2) выходы соединены со вторыми входами соответствующих корреляторов 2. Кроме того, второй, (к-1)-ый и к-ый выходы счетчика 8 соединены соответственно со вторым, третьим и первым коммутаторами 10, вторые входы которых соединены с выходами последовательно соединенных первого, второго и третьего триггеров 9. Вход первого триггера 9 соединен с выходом ОЗУ 7, третий вход которого соединен со вторым входом блока принятия решения 4 и с управляющими входами коммутаторов 10. Выходы коммутаторов 10 соединены со вторыми входами n-го, первого, и (n-1)-го корреляторов 2. При этом третий выход блока принятия решений 4 соединен с управляющими входами корреляторов 2, четвертый - с управляющим входом блока 3, вход опорной частоты которого соединен со входом опорной частоты блока принятия решения 4 и является вторым входом устройства.

Работает предлагаемое устройство следующим образом.

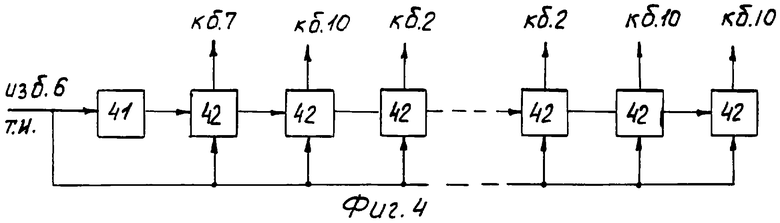

Управляемый генератор 1 формирует опорные псевдослучайные последовательности, сдвинутые друг относительно друга на τ, где τ - длительность одного элемента ПСП. Блок-схема управляемого генератора ПСП представлена на фиг.4, где:

41 - генератор ПСП,

42 - Д-триггер.

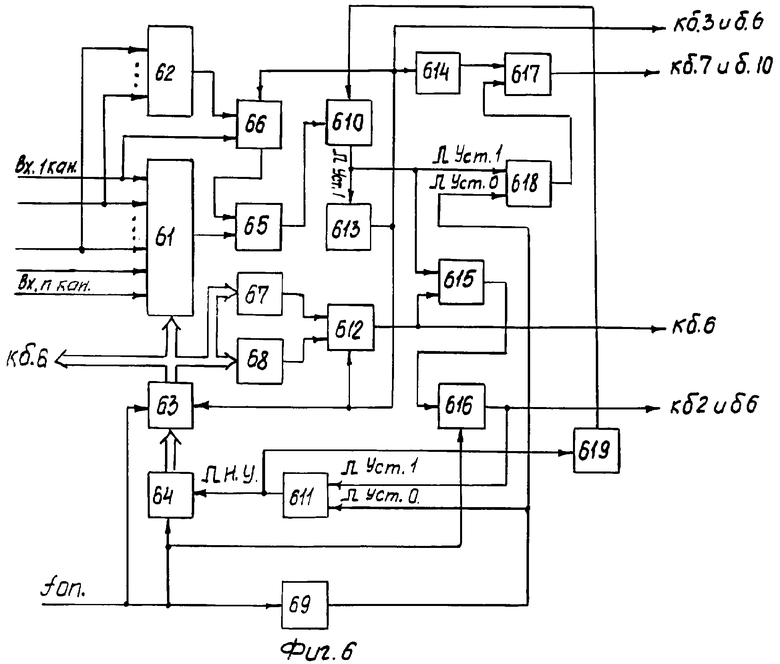

На первом этапе поиска широкополосного сигнала коммутаторы 10 подключают к опорным входам первого, (n-1)-го и n-го корреляторов 2 выходы блока 1. На объединенные входы корреляторов 2 подан входной сигнал и происходит вычисление n значений функции взаимной корреляции входного сигнала и опорной ПСП. Результаты вычислений поступают на входы блока принятия решения 4, блок-схема которого представлена на фиг.6, где обозначено:

61 - коммутатор,

62 - формирователь порога,

63 - сумматор,

64 - счетчик,

65 - компаратор,

66 - коммутатор,

67 - дешифратор состояния n,

68 - дешифратор состояния (n-2),

69 - делитель на К,

610 - схема И,

611 - R-S-триггер,

612 - коммутатор,

613 - R-S-триггер,

614 - инвертор,

615 - схема ИЛИ,

616 - Д-триггер,

617 - схема ИЛИ,

618 - R-S-триггер,

619 - инвертор.

Блок-принятия решения 4 работает следующим образом.

В результате деления опорной частоты fon на К в делителе 69 получаем последовательность импульсов с периодом Т, равным времени вычисления значения взаимокорреляционной функции. По приходу этого импульса, устанавливающего R-S-триггер 611 в нулевое состояние, разрешается работа двоичного счетчика 64, тактируемого опорной частотой, и прохождение сигнала с выхода компаратора 65 на входы блоков 613, 615, 618. Состояние счетчика 64, сложенное с сигналом в младшем разряде с выхода R-S-триггера 613, управляет коммутатором 61. На первом этапе поиска сигнал на выходе R-S-триггера 613 имеет нулевой уровень. В результате этого коммутатор 61 последовательно подключает выходы всех корреляторов 2 к компаратору 65, в котором происходит сравнение значений функции взаимной корреляции (ФВК) с порогом, формируемым в блоке 62. Если ни в одном канале сигнал не превысил порог, то на выходе коммутатора 612, подключившего вход дешифратора состояния n 67, появится сигнал. По этому сигналу, сдвинутому в Д-триггере 616 на такт опорной частоты, управляемый делитель грубой дискретной системы ФАП 6 "вырежет" n тактов тактовой частоты генератора ПСП 1, после чего происходит анализ следующих n значений ФВК.

Если в i-ом канале произойдет превышение порога, то сигнал компаратора 65 установит R-S-триггеры 613 и 618 в единичное состояние. В это время на вход управляемого делителя грубой дискретной системы ФАП 6 подаются (i-1) состояние сумматора 63, работающего в синхронном режиме, соответствующем i-му каналу, и сигналы управления с выходов триггеров 613 и 616 и коммутатора 612, по которым блок 6 "вырежет" (i-1) такт тактовой частоты. В результате этого опорный сигнал, соответствующий значению ФВК, превысившему порог, окажется в первом канале. Сигнал с выхода Д-триггера 616 также подается на управляющие входы корреляторов 2 в качестве импульсов "сброса" вычисленных значений ФВК, а также устанавливает R-S-триггер 611 в единичное состояние, которое устанавливает счетчик 64 в начальное состояние и запрещает прохождение сигнала с выхода компаратора 65. Одновременно с этим с выхода схемы ИЛИ 617 подается команда на ОЗУ 7, по которой происходит запись опорного сигнала. Такое состояние блока принятия решения продолжается до прихода импульса с выхода делителя 69, устанавливающего R-S-триггер 618 в нулевое состояние. Это состояние переключает ОЗУ 7 в режим считывания информации, а также коммутирует ко входам первого, (n-1)-го и n-го корреляторов 2 опорные сигналы с выходов Д-триггеров 9. ОЗУ 7 можно выполнить так, как показано в Справочном пособии под ред. Якубовского С.Е "Аналоговые и цифровые интегральные микросхемы, М., Радио и связь, 1984 г., гл.5, стр.246-261. В результате этого в первом корреляторе 2 будет постоянно вычисляться значение ФВК входного сигнала и опорного, в предположении находящегося в синхронизации со входным, а в (n-1)-ом и n-ом корреляторах - значения ФВК, необходимые для работы блока точной системы ФАП 3.

После этого предлагаемое устройство продолжает анализировать значения ФВК (n-3)-мя корреляторами. Алгоритм работы блока принятия решения 4 при этом отличается от работы предыдущего этапа тем, что вместо порога, вычисленного в формирователе 62, ко входу компаратора в качестве порога подключается сигнал первого коррелятора; после прихода импульса с делителя 69 начинается последовательное подключение к компаратору корреляторов, начиная со второго; сигнал отсутствия превышения порога во всех (n-3) корреляторах появляется в виде логической единицы на выходе коммутатора 612 при дешифрации (n-2)-го состояния сумматора 3, в результате чего не происходит анализ ФВК в (п-1)-ом и n-ом корреляторах.

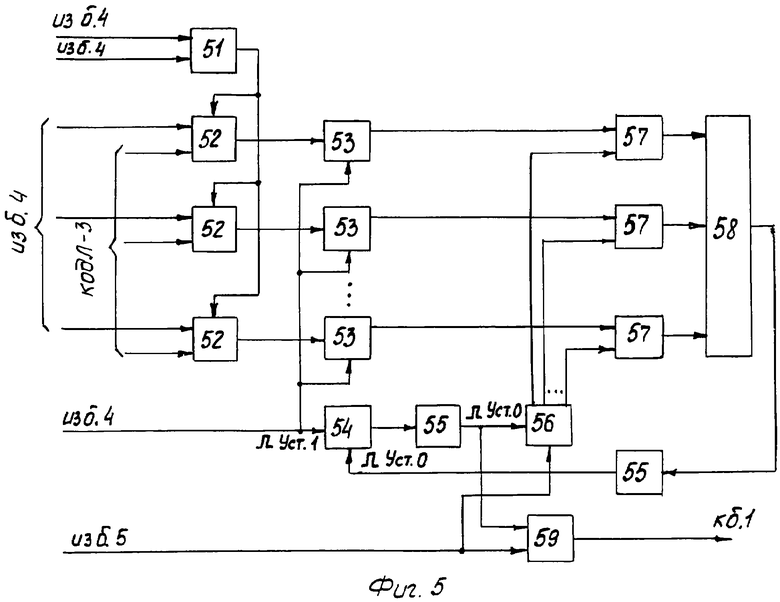

Блок-схема управляемого делителя грубой дискретной системы ФАП 6 представлена на фиг.5, где обозначено:

51 - схема И,

52 - коммутатор,

53 - Д-триггер,

54 - R-S-триггер,

55 - инвертор,

56 - счетчик,

57 - сумматор,

58 - схема ИЛИ,

59 - схема И.

На информационные входы Д-триггеров 53 с выходов коммутаторов 52 подается код двоичного состояния числа, определяющего требуемое время задержки опорного сигнала. Управление коммутаторами осуществляется конъюнкцией сигналов, поступающих из блоков 612 и 613. При отсутствии вторичного и т.д. превышения порога на управляющих входах коммутаторов возникает логическая единица, которая коммутирует двоичное состояние числа (n-3). При нулевом состоянии управляющих входов коммутаторов на информационные входы Д-триггеров поступает код числа с выхода сумматора 63. По приходу сигнала с выхода Д-триггера 616 происходит запись информации в Д-триггеры, разрешение счета двоичного счетчика 56, а также запрещение прохождения тактов на выход делителя грубой дискретной системы ФАП 5. При совпадении кодов счетчика 56 и Д-триггеров 53 устанавливается логический ноль на выходе R-S-триггера 54. В результате этого счетчик 56 устанавливается в начальное состояние, а также разрешается прохождение тактов на выход управляемого делителя грубой дискретной системы ФАП 6.

Работа и схема блока точной системы ФАП 3 полностью соответствует схеме и работе соответствующего блока в устройстве-прототипе.

В предлагаемом устройстве помехозащищенность синхронизации широкополосного сигнала в условиях многолучевости выше, чем в устройстве-прототипе. Для доказательства этого предположим, что на входе присутствуют два луча сигнала, сдвинутые друг относительно друга по времени на величину, большую, чем длительность одного элементарного импульса опорной ПСП. Наличие такого сдвига между лучами объясняется различными каналами прохождения сигнала. Это приводит к тому, что уровень сигнала одного из лучей меньше, чем другого.

Существует вероятность того, что вначале произойдет обнаружение более слабого сигнала. При этом устройство-прототип заканчивает поиск и переходит в режим слежения за слабым сигналом.

Предлагаемое же устройство продолжает анализировать функцию взаимной корреляции входного и опорного сигналов. В результате этого поиск заканчивается выбором сигнала с наибольшим уровнем, что понижает вероятность ошибки при слежении и выделении информации.

Из вышеизложенного можно сделать вывод о том, что в условиях многолучевости входного сигнала помехозащищенность синхронизации в предлагаемом устройстве выше, чем в устройстве -прототипе.

При дополнительном поиске, проведенном авторами в соответствии с п.52 ЭЗ-1-74, не обнаружены объекты со сходными признаками отличительной части. Учитывая это, авторы считают, что предлагаемое изобретение отвечает критерию "существенные отличия".

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВВОДА В СИНХРОНИЗМ СИСТЕМЫ СВЯЗИ С ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1980 |

|

SU1840128A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ | 1980 |

|

SU1840647A1 |

| УСТРОЙСТВО ПОИСКА СИСТЕМЫ СВЯЗИ С ШИРОКОПОЛОСНЫМИ СИГНАЛАМИ | 1980 |

|

SU1840267A1 |

| УСТРОЙСТВО ПОИСКА ШИРОКОПОЛОСНОГО СИГНАЛА | 1980 |

|

SU1840288A1 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНОГО СИГНАЛА | 1980 |

|

SU1840270A1 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНОГО СИГНАЛА | 1985 |

|

SU1840083A1 |

| УСТРОЙСТВО ПОИСКА И ОБНАРУЖЕНИЯ ШУМОПОДОБНОГО СИГНАЛА | 1979 |

|

SU1840447A1 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНОГО СИГНАЛА | 1979 |

|

SU1840118A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ШУМОПОДОБНОГО СИГНАЛА | 1975 |

|

SU1840645A1 |

| УСТРОЙСТВО ПОИСКА ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1981 |

|

SU1840149A1 |

Изобретение относится к области радиотехники и может быть использовано в широкополосных системах с шумоподобными сигналами. Техническим результатом является повышение помехоустойчивости в условиях многолучевости входного сигнала. Устройство содержит управляемый генератор (ПСП), n корреляторов, блок принятия решения, блок точной системы фазовой автоподстройки (ФАП), управляемый генератор тактовых импульсов, управляемый делитель грубой системы (ФАП), адресный счетчик, блок памяти, три триггера, три коммутатора и инвертор. Устройство анализирует функцию взаимной корреляции входного и опорного сигналов, в результате чего поиск заканчивается выбором сигнала с наибольшим уровнем, что понижает вероятность ошибки при слежении и выделении информации. 6 ил.

Устройство поиска шумоподобного сигнала, содержащее n корреляторов, первые входы которых объединены и являются входом устройства, управляемый генератор ПСП, выходы которого с третьего по К-2 соединены со вторыми входами корреляторов, блок принятия решения, соответствующие входы которого соединены с соответствующими выходами корреляторов, блок точной системы фазовой автоподстройки (ФАП), выход которого через последовательно соединенные управляемый генератор тактовых импульсов и управляемый делитель грубой системы фазовой автоподстройки (ФАП) подключен ко входу управляемого генератора ПСП, при этом первый и второй входы блока точной системы ФАП соединены с соответствующими выходами соответствующих корреляторов, второй вход управляемого делителя грубой системы ФАП соединен с первым выходом блока принятия решения, отличающееся тем, что, с целью повышения помехоустойчивости в условиях многолучевости входного сигнала, введены последовательно соединенные адресный счетчик, блок памяти, первый, второй и третий триггеры, а также три коммутатора и инвертор, вход которого соединен с выходом управляемого делителя грубой системы ФАП, входом адресного счетчика, вторым входом второго триггера, а выход - ко вторым входам первого и третьего триггеров, при этом соответствующий выход управляемого генератора ПСП соединен со вторым входом блока памяти, третий вход которого соединен с объединенными первыми входами трех коммутаторов и вторым выходом блока принятия решения, К-е первый и второй выходы управляемого генератора ПСП соединены со вторыми входами первого и третьего коммутаторов, второй вход второго коммутатора соединен с соответствующим выходом генератора ПСП, третьи входы первого, второго и третьего коммутаторов подключены соответственно к выходам первого, второго и третьего триггеров, выходы коммутаторов соединены со вторыми входами n, первого и (n-1)-го корреляторов, третий выход блока принятия решения соединен с управляющими входами корреляторов, четвертый его выход подключен к управляющему входу точной системы ФАП, вход опорной частоты которого соединен со входом опорной частоты блока принятия решения и является вторым входом устройства.

Авторы

Даты

2006-07-10—Публикация

1985-01-22—Подача